Перекрестная ссылка на родственные заявки

Настоящая заявка испрашивает приоритет согласно заявке на патент Китая № 201721170305.2, поданной 12 сентября 2017 года, содержание которой полностью включено в настоящую заявку посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ

Настоящее раскрытие относится к области технологий отображения и, в частности, к матричной подложке, панели отображения и устройству отображения.

УРОВЕНЬ ТЕХНИКИ

Матричная подложка обычно включает в себя базовую подложку и множество пиксельных блоков, расположенных на базовой подложке и размещенных в массиве. Каждый из пиксельных блоков включает в себя тонкопленочный транзистор (TFT) и схему пикселя, электрически соединенную с транзистором TFT.

Транзистор TFT обычно включает в себя активный слой, электрод стока, расположенный над активным слоем относительно базовой подложки, и изолирующий слой между активным слоем и электродом стока. Электрод стока может быть электрически соединен с активным слоем через сквозное отверстие в изолирующем слое. В случае жидкокристаллического дисплея схема пикселя включает в себя электрод пикселя, который формирует один из двух электродов жидкокристаллического конденсатора. В случае дисплея на органических светодиодах (OLED) схема пикселя также включает в себя электрод пикселя (например, электрод анода устройства OLED), на котором, как правило, расположен ограничивающий пиксель слой. В любом случае электрод пикселя может быть электрически соединен с электродом стока транзистора TFT через сквозное отверстие.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В соответствии с аспектом настоящего раскрытия обеспечена матричная подложка, содержащая: базовую подложку, содержащую множество пиксельных областей, размещенных в массиве; множество тонкопленочных транзисторов, распределенных в соответствующих пиксельных областях из упомянутого множества пиксельных областей, каждый из тонкопленочных транзисторов содержит: активный слой, расположенный на подложке; электрод затвора, расположенный на базовой подложке, причем активный слой и электрод затвора уложены один поверх другого; электрод истока, расположенный над электродом затвора, электрод истока электрически соединен с активным слоем через первое сквозное отверстие; и электрод стока, расположенный над электродом затвора, электрод стока электрически соединен с активным слоем через второе сквозное отверстие, электрод стока содержит первый участок, расположенный во втором сквозном отверстии; пассивирующий слой, расположенный на электродах истока и электродах стока, пассивирующий слой покрывает первые участки электродов стока; и множество электродов пикселей, распределенных в соответствующих пиксельных областях из упомянутого множества пиксельных областей и расположенных на пассивирующем слое, каждый из электродов пикселей электрически соединен с соответствующим одним из электродов стока через соответствующее третье сквозное отверстие, которое проходит через пассивирующий слой.

В некоторых вариантах осуществления электрод стока дополнительно содержит второй участок вне второго сквозного отверстия, и электрод пикселя электрически соединен со вторым участком электрода стока через третье сквозное отверстие.

В некоторых вариантах осуществления матричная подложка дополнительно содержит выравнивающий слой, расположенный на пассивирующем слое. Выравнивающий слой снабжен множеством четвертых сквозных отверстий, ортогональная проекция каждого из четвертых сквозных отверстий на базовую подложку полностью покрывает ортогональную проекцию соответствующего одного из третьих сквозных отверстий на базовую подложку. Каждый из электродов пикселей содержит первый участок, расположенный в соответствующем третьем сквозном отверстии, второй участок, расположенный в соответствующем одном из четвертых сквозных отверстий, и третий участок, расположенный на выравнивающем слое.

В некоторых вариантах осуществления ортогональная проекция каждого из четвертых сквозных отверстий на базовую подложку дополнительно полностью покрывает ортогональную проекцию соответствующего одного из вторых сквозных отверстий на базовую подложку.

В некоторых вариантах осуществления ортогональная проекция каждого из четвертых сквозных отверстий на базовую подложку имеет форму, выбранную из группы, состоящей из круга и квадрата.

В некоторых вариантах осуществления геометрический центр ортогональной проекции каждого из четвертых сквозных отверстий на базовую подложку накладывается на геометрический центр ортогональной проекции соответствующего третьего сквозного отверстия на базовую подложку.

В некоторых вариантах осуществления выравнивающий слой имеет толщину 1-4 мкм.

В некоторых вариантах осуществления ортогональная проекция третьего сквозного отверстия на базовую подложку окружает ортогональную проекцию второго сквозного отверстия на базовую подложку.

В некоторых вариантах осуществления ортогональная проекция третьего сквозного отверстия на базовую подложку имеет форму круга.

В некоторых вариантах осуществления геометрический центр ортогональной проекции третьего сквозного отверстия на базовую подложку накладывается на геометрический центр ортогональной проекции второго сквозного отверстия на базовую подложку.

В некоторых вариантах осуществления ортогональная проекция третьего сквозного отверстия на базовую подложку частично накладывается на ортогональную проекцию второго сквозного отверстия на базовую подложку.

В некоторых вариантах осуществления матричная подложка дополнительно содержит: ограничивающий пиксель слой, расположенный на множестве электродов пикселей и снабженный множеством отверстий, каждое из множества отверстий проходит через ограничивающий пиксель слой, чтобы открыть область соответствующего одного из множества электродов пикселей; множество органических светоизлучающих слоев, каждый из которых расположен в соответствующем одном из отверстий и покрывает открытую область соответствующего электрода пикселя; и дополняющий электрод пикселя, покрывающий множество органических светоизлучающих слоев и ограничивающий пиксель слой.

В некоторых вариантах осуществления ограничивающий пиксель слой имеет толщину 1-3 мкм.

В некоторых вариантах осуществления второе сквозное отверстие сужается по направлению к базовой подложке.

В некоторых вариантах осуществления второе сквозное отверстие имеет минимальную апертуру, которая больше, чем утроенная глубина второго сквозного отверстия.

В некоторых вариантах осуществления матричная подложка дополнительно содержит изолирующий слой затвора, расположенный между электродами затвора и активными слоями.

В некоторых вариантах осуществления в каждом из множества тонкопленочных транзисторов электрод затвора расположен дальше от базовой подложки, чем активный слой.

В некоторых вариантах осуществления в каждом из множества тонкопленочных транзисторов электрод затвора расположен ближе к базовой подложке, чем активный слой.

В соответствии с другим аспектом настоящего раскрытия обеспечена панель отображения, содержащая описанную выше матричную подложку.

В соответствии еще с одним аспектом настоящего раскрытия обеспечено устройство отображения, содержащее описанную выше панель отображения.

Эти и другие аспекты настоящего раскрытия будут очевидны на основе описанных далее вариантов осуществления и разъяснены со ссылкой на описанные далее варианты осуществления.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Более подробная информация, признаки и преимущества настоящего раскрытия раскрыты в следующем описании иллюстративных вариантов осуществления вместе с прилагаемыми чертежами, на которых:

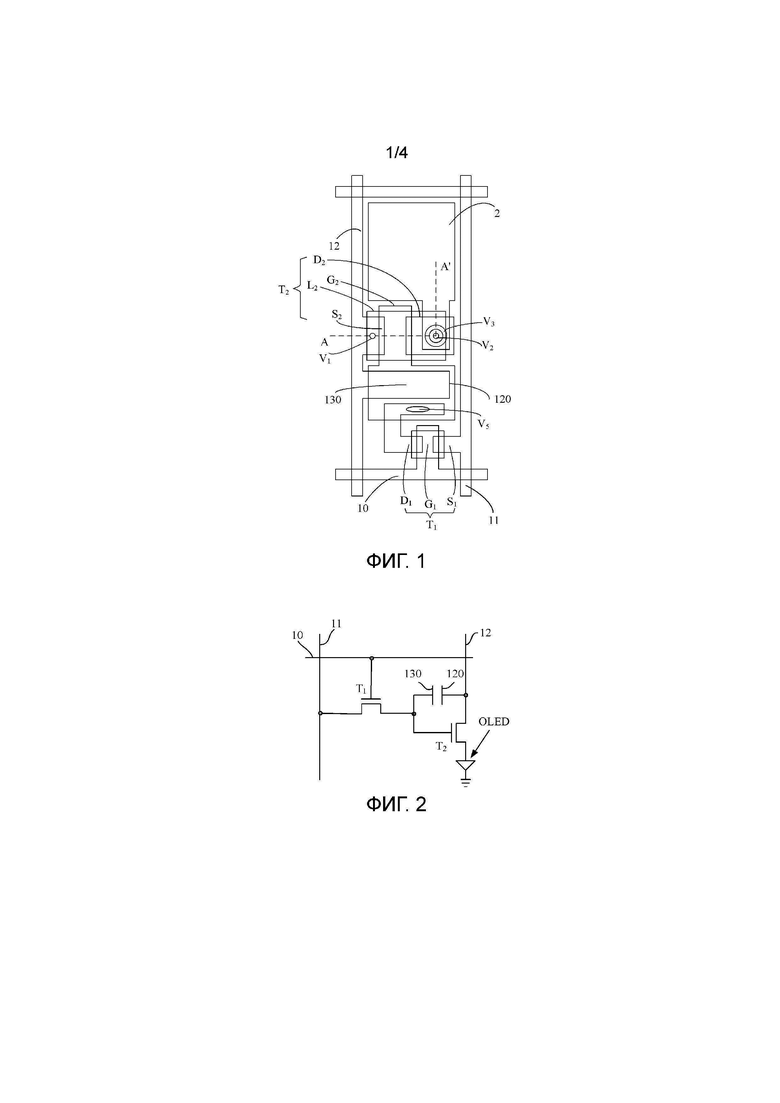

Фиг. 1 - схематический вид сверху частичной области матричной подложки в соответствии с вариантом осуществления настоящего раскрытия;

Фиг. 2 - схема соединений частичной области матричной подложки, показанной на фиг. 1;

Фиг. 3 - схематическое поперечное сечение по линии A-A' на фиг. 1, демонстрирующее иллюстративную структуру частичной области матричной подложки, показанной на фиг. 1;

Фиг. 4 - схематическое поперечное сечение по линии A-A' на фиг. 1, демонстрирующее другую иллюстративную структуру частичной области матричной подложки, показанной на фиг. 1;

Фиг. 5 - схематическое поперечное сечение по линии A-A' на фиг. 1, демонстрирующее еще одну иллюстративную структуру частичной области матричной подложки, показанной на фиг. 1;

Фиг. 6 - схематическое поперечное сечение по линии A-A' на фиг. 1, демонстрирующее еще одну иллюстративную структуру частичной области матричной подложки, показанной на фиг. 1; и

Фиг. 7 - схема устройства отображения в соответствии с вариантом осуществления настоящего раскрытия.

ПОДРОБНОЕ ОПИСАНИЕ

Следует понимать, что хотя термины "первый", "второй", "третий" и т.д., могут быть использованы в настоящем документе для описания различных элементов, компонентов, областей, слоев и/или фрагментов, эти элементы, компоненты, области, слои и/или фрагменты не должны быть ограничены этими терминами. Эти термины использованы только для того, чтобы отличать один элемент, компонент, область, слой или фрагмент от другого. Таким образом, обсуждаемый ниже первый элемент, компонент, область, слой или фрагмент можно было бы назвать вторым элементом, компонентом, областью, слоем или фрагментом без отступления от идеи настоящего раскрытия.

Термины, характеризующие относительное пространственное расположение, такие как "снизу", "нижний", "ниже", "под", "выше", "верхний" и т.п., могут быть использованы в настоящем документе для простоты изложения, чтобы описать изображенное на фигурах соотношение одного элемента или признака с другим элементом (элементами) или признаком (признаками). Следует понимать, что термины, характеризующие относительное пространственное расположение, охватывают разные ориентации устройства при использовании или функционировании в дополнение к ориентации, изображенной на фигурах. Например, если устройство на фигурах перевернуто, элементы, описанные как расположенные "ниже", "снизу" или "под" другими элементами или признаками, могут быть затем ориентированы "над" другими элементами или признаками. Таким образом, иллюстративные термины "ниже" и "под" могут охватывать обе ориентации, и выше, и ниже. Такие термины как "до" или "предыдущий" и "после" или "последующий" могут быть использованы аналогичным образом, например, для указания порядка, в котором свет проходит через элементы. Устройство может быть ориентировано иным образом (повернуто на 90 градусов или в других ориентациях), и дескрипторы относительного пространственного расположения, используемые в настоящем документе, интерпретируются соответствующим образом. Кроме того, также будет подразумеваться, что когда слой упоминается как находящийся "между" двумя слоями, это может быть единственный слой между этими двумя слоями, или также могут присутствовать один или более промежуточных слоев.

Терминология, используемая в настоящем документе, предназначена только для описания конкретных вариантов осуществления и не предназначена для ограничения раскрытия. Используемые в настоящем документе формы единственного числа предполагают также включение форм множественного числа, если контекст ясно не указывает иначе. Также следует понимать, что термины "содержит" и/или "содержащий", используемые в этом описании, определяют наличие заявленных признаков, целых чисел, этапов, операций, элементов и/или компонентов, но не исключают наличие или добавление одного или более других признаков, целых чисел, этапов, операций, элементов, компонентов и/или их групп. Используемый в настоящем документе термин "и/или" включает в себя все возможные комбинации из одного или более соответствующих перечисленных пунктов.

Следует понимать, что когда элемент или слой упоминаются как "находящийся на", ʺсоединенный сʺ, ʺприсоединенный кʺ или ʺсмежный сʺ другим элементом или слоем, он может непосредственно "находиться на", быть "соединен с", быть "присоединен к" или являться "смежным с" другим элементом или слоем, или могут присутствовать промежуточные элементы или слои. Напротив, когда элемент упоминается как "непосредственно находящийся наʺ, ʺнепосредственно соединенный сʺ, ʺнепосредственно присоединенный кʺ или ʺнепосредственно смежный сʺ другим элементом или слоем, то не имеется никаких промежуточных элементов или слоев. Однако ни в коем случае фраза "находится на" или ʺнаходится непосредственно наʺ не должна быть истолкована как требование, чтобы слой полностью покрывал нижележащий слой.

Варианты осуществления раскрытия описаны в настоящем документе со ссылкой на схематические иллюстрации идеализированных вариантов осуществления (и промежуточных структур) раскрытия. Таким образом, могут ожидаться отклонения от форм иллюстраций, например, в результате технологий производства и/или допусков. Таким образом, варианты осуществления раскрытия не должны быть истолкованы, как ограниченные конкретными формами областей, проиллюстрированными в настоящем документе, но должны включать в себя отклонения от формы, которые происходят, например, в результате изготовления. В соответствии с этим проиллюстрированные на фигурах области являются схематичными по своей природе, и их формы не предназначены для иллюстрации фактической формы области устройства и не предназначены для ограничения объема раскрытия.

Если не определено иначе, все термины (в том числе технические и научные термины), используемые в настоящем документе, имеют такое значение, которое хорошо известно специалистам в области техники, которой принадлежит это раскрытие. Также следует понимать, что термины, которые определены в общепринятых словарях, должны интерпретироваться как имеющие значения, которые согласованы с их значением в контексте релевантной области техники и/или настоящего описания, и не будут интерпретироваться в идеализированном или чрезмерно формальном смысле, если это явно не определено в настоящем документе.

Варианты осуществления настоящего раскрытия будут подробно описаны ниже со ссылкой на чертежи.

Фиг. 1 является схематическим видом сверху частичной области матричной подложки, включающей в себя иллюстративный пиксельный блок, в соответствии с вариантом осуществления настоящего раскрытия. Следует понимать, что хотя на фиг. 1 для удобства иллюстрации показана только одна пиксельная область, матричная подложка включает в себя множество таких пиксельных областей, размещенных в массиве.

Согласно фиг. 1, в показанной пиксельной области затворная шина 10 проходит в направлении рядов, шина 11 данных проходит в направлении столбцов, пересекая затворную шину 10, и шина 12 электроснабжения проходит параллельно с шиной 11 данных. Шина 12 электроснабжения включает в себя первый электрод 120, который проходит перпендикулярно ее длине. Тонкопленочный транзистор T1 расположен на пересечении затворной шины 10 и шины 11 данных и включает в себя электрод затвора G1, соединенный с затворной шиной 10, электрод истока S1, соединенный с шиной 11 данных, и электрод стока D1, электрически соединенный с электродом затвора G2 другого тонкопленочного транзистора T2 через пятое сквозное отверстие V5, которое проходит через межслойный изолирующий слой 4 и изолирующий слой 3 затвора. Электрод затвора G2 тонкопленочного транзистора T2 включает в себя вытянутый участок, образующий второй электрод 130, причем второй электрод 130 расположен напротив первого электрода 120, чтобы сформировать накопительный конденсатор. Тонкопленочный транзистор T2 дополнительно включает в себя активный слой L2, электрод стока D2, электрически соединенный с активным слоем L2 через второе сквозное отверстие V2, и электрод истока S2, соединенный с шиной 12 электроснабжения. Электрод стока D2 дополнительно электрически соединен с электродом 2 пикселя через третье сквозное отверстие V3.

Фиг. 2 показывает эквивалентную схему пиксельной области, показанной на фиг. 1, который является схемой пикселя, включающей в себя органический светодиод (OLED). В этом примере электрод 2 пикселя на в фиг. 1 может представлять собой, например, электрод анода OLED. Следует понимать, что схема пикселя на фиг. 2 является лишь иллюстративной, и что возможны другие варианты осуществления. Также будет понятно, что концепции настоящего раскрытия не ограничены матричными подложками OLED, но также могут быть применены к матричным подложкам жидкокристаллического дисплея (LCD).

Вернемся к фиг. 1, на которой тонкопленочные транзисторы T1 и T2 могут являться транзисторами TFT из аморфного кремния, поликремниевыми транзисторами TFT или транзисторами TFT из оксидного полупроводника. В тонкопленочном транзисторе T1 электрод затвора G1 также может являться частью затворной шины 10 (т.е., нет отдельного рисунка затвора, продолжающегося от затворной шины 10), и электрод истока S1 также может являться частью шины 11 данных (т.е., нет отдельного рисунка электрода истока, продолжающегося от шины 11 данных). Варианты осуществления настоящего раскрытия не ограничены транзисторами TFT конкретного вида и/или структуры. В качестве примера и без ограничения затворная шина 10, электроды затвора G1 и G2, шина 12 электроснабжения, электроды истока S1 и S2, электроды стока D1 и D2 и шина 11 данных могут быть сделаны из металлического материала, такого как Cu (медь), Al (алюминий), Мо (молибден), Ti (титан), Cr (хром) и W (вольфрам) или их сплав. Кроме того, они могут представлять собой однослойную структуру или многослойную структуру, такую как многослойная структура Mo\Al\Mo, Ti\Cu\Ti и Mo\Ti\Cu.

Фиг. 3 является схематическим поперечным сечением вдоль линия A-A' на фиг. 1, демонстрирующим иллюстративную структуру частичной области матричной подложки, показанной на фиг. 1.

Как показано в фиг. 3, матричная подложка включает в себя базовую подложку 1, на которой расположены активный слой L2 тонкопленочного транзистора T2 и изолирующий слой 3 затвора. Изолирующий слой 3 затвора находится между электродом затвора G2 тонкопленочного транзистора T2 и активным слоем L2. Активный слой L2 и электрод затвора G2 уложены один поверх другого. В примере на фиг. 3 тонкопленочный транзистор T2 является транзистором с верхним затвором, в котором электрод затвора G2 расположен дальше от базовой подложки 1, чем активный слой L2. В частности, изолирующий слой 3 затвора покрывает активный слой L2, и электрод затвора G2 расположен на изолирующем слое 3 затвора. Межслойный изолирующий слой 4 расположен на электроде затвора G2. Электрод истока S2 и электрод стока D2 тонкопленочного транзистора T2 расположены на межслойном изолирующем слое 4. Электрод истока S2 электрически соединен с активным слоем L2 через первое сквозное отверстие V1, проходящее через межслойный изолирующий слой 4 и изолирующий слой 3 затвора, и электрод стока D2 электрически соединен с активным слоем L2 через второе сквозное отверстие V2, которое проходит через межслойный изолирующий слой 4 и изолирующий слой 3 затвора. Электрод стока D2 включает в себя первый участок D2-1, расположенный во втором сквозном отверстии V2, и второй участок D2-2, расположенный вне второго сквозного отверстия V2. Пассивирующий слой 5 расположен на электроде истока S2 и электроде стока D2. Пассивирующий слой 5 включает в себя участок 51, покрывающий первый участок D2-1 электрода стока D2. В этом примере участок 51 пассивирующего слоя 5 находится непосредственно на первом участке D2-1 электрода стока D2. Электрод 2 пикселя расположен на пассивирующем слое 5 и электрически соединен с электродом стока D2 через третье сквозное отверстие V3, которое проходит через пассивирующий слой 5.

В этом варианте осуществления матричная подложка дополнительно включает в себя ограничивающий пиксель слой 6, расположенный на электроде 2 пикселя. Ограничивающий пиксель слой 6 снабжен отверстием 61, проходящим через ограничивающий пиксель слой 6, чтобы открыть область электрода 2 пикселя. Органический светоизлучающий слой 7 расположен в отверстии 61 и покрывает открытую область электрода 2 пикселя. Матричная подложка дополнительно включает в себя дополняющий электрод 8 пикселя, покрывающий органический светоизлучающий слой 7 и ограничивающий пиксель слой 6. Дополняющий электрод 8 пикселя, органический светоизлучающий слой 7 и электрод 2 пикселя формируют устройство OLED. Например, электрод 2 пикселя является анодом устройства OLED, и дополняющий электрод 8 пикселя является катодом устройства OLED. В некоторых примерах ограничивающий пиксель слой 6 может иметь толщину, например, 1-3 мкм. Это позволяет снабдить органический светоизлучающий слой 7 пространством депонирования, имеющим достаточную глубину.

Ограничивающий пиксель слой 6 обычно изготавливается из органической смолы. Во время люминесценции устройства OLED остаточные газы в смоле могут выделиться из ограничивающего пиксель слоя 6 вследствие нагревания, образуемого люминесценцией.

В отсутствие пассивирующего слоя 5 (в частности, участка 51 пассивирующего слоя) газ, выделяющийся из ограничивающего пиксель слоя 6, может пройти через структуру сквозного отверстия между электродом 2 пикселя и активным слоем L2 (например, второе сквозное отверстие V2 и третье сквозное отверстие V3) и проникнуть в активный слой L2. Это затронет стабильность активного слоя и изменит электрические характеристики тонкопленочного транзистора T2.

Напротив, благодаря наличию пассивирующего слоя 5 (в частности, участка 51 пассивирующего слоя 5) между ограничивающим пиксель слоем 6 и активным слоем L2 проникновение газа в активный слой L2 может быть заблокировано, и тем самым улучается электрическая стабильность тонкопленочного транзистора T2. Как отмечалось ранее, эта концепция одинаково применима к матричным подложкам LCD. Кроме того, другие изолирующие слои (например, изолирующий слой затвора 3 и межслойный изолирующий слой 4) также могут также функционировать, чтобы блокировать проникновение газа в активный слой L2.

Ортогональная проекция третьего сквозного отверстия V3 на базовую подложку 1 может не накладываться на ортогональную проекцию второго сквозного отверстия V2 на базовую подложку 1. Учитывая тот факт, что электрод 2 пикселя электрически соединен со вторым участком D2-2 электрода стока D2 через третье сквозное отверстие V3 (т.е., участок электрода 2 пикселя депонирован в третьем сквозном отверстии V3 и находится в прямом контакте со вторым участком D2-2 электрода стока D2), в примере, показанном на фиг. 1 и 3, ортогональная проекция третьего сквозного отверстия V3 на базовую подложку 1 окружает ортогональную проекцию второго сквозного отверстия V2 на подложку 1, тем самым обеспечивая большую область контакта между электродом 2 пикселя и вторым участком D2-2 электрода стока D2. Это может обеспечить надежность электрического контакта. В частности, в примере на фиг. 3 ортогональная проекция третьего сквозного отверстия V3 на базовую подложку 1 является круговой.

В этом варианте осуществления геометрический центр ортогональной проекции третьего сквозного отверстия V3 на базовую подложку 1 совпадает с геометрическим центром ортогональной проекции второго сквозного отверстия V2 на базовую подложку 1. В примере на фиг. 3, поскольку ортогональная проекции третьего сквозного отверстия V3 на базовую подложку 1 является круговой, геометрический центр (или центр формы) ортогональной проекции является центром обоих кругов, формирующих форму круга (центры обоих кругов совпадают друг с другом).

Фиг. 4 является схематическим поперечным сечением по линии A-A' на фиг. 1, демонстрирующим другую иллюстративную структуру частичной области матричной подложки, показанной на фиг. 1. Те же ссылочные позиции, как на фиг. 3, обозначают те же самые элементы.

Как показано на фиг. 4, ортогональная проекция третьего сквозного отверстия V3 на базовую подложку 1 накладывается на ортогональную проекцию второго сквозного отверстия V2 на базовую подложку 1. В частности, ортогональная проекция третьего сквозного отверстия V3 на базовую подложку 1 может полностью покрывать ортогональную проекцию второго сквозного отверстия V2 на базовую подложку 1. Это позволяет увеличить область контакта между электродом 2 пикселя и вторым участком D2-2 электрода стока D2, тем самым улучшая надежность электрического контакта.

В этом варианте осуществления второе сквозное отверстие V2 сужается по направлению к базовой подложке 1. Таким образом, апертура второго сквозного отверстия V2 постепенно становится меньше сверху вниз. В некоторых примерах минимальная апертура второго сквозного отверстия V2 больше, чем утроенная глубина второго сквозного отверстия V2, в результате чего металл электрода стока при депонировании во втором сквозном отверстии V2 может следовать за формой второго сквозного отверстия V2 и сформировать углубленную часть. Таким образом, участок 51 пассивирующего слоя 5, который покрывает электрод стока D2, может быть сформирован на углубленной части электрода стока D2 во втором сквозном отверстии V2, обеспечивая более хороший блокирующий эффект против проникновения газа в активный слой L2.

Фиг. 5 является схематическим поперечным сечением по линии A-A' на фиг. 1, демонстрирующим еще одну иллюстративную структуру частичной области матричной подложки, показанной на фиг. 1. Те же ссылочные позиции, как на фиг. 3, обозначают те же самые элементы.

В отличие от описанных выше вариантов осуществления относительно фиг. 3 и 4, в варианте осуществления на фиг. 5 изолирующий слой 3 затвора расположен только в области активного слоя L2, которая соответствует электроду затвора G2, то есть, изолирующий слой 3 затвора расположен только под электродом затвора G2. В этом случае, как показано на фиг. 5, электрод истока S2 соединен с активным слоем L2 через первое сквозное отверстие V1, проходящее через межслойный изолирующий слой 4, и электрод стока D2 соединен с активным слоем L2 через второе сквозное отверстие V2, которое проходит через межслойный изолирующий слой 4.

Другие конфигурации матричной подложки сходны с описанным выше вариантом осуществления относительно фиг. 3 и не будут описываться снова в настоящем документе.

Фиг. 6 является схематическим поперечным сечением по линии A-A' на фиг. 1, демонстрирующим еще одну иллюстративную структуру частичной области матричной подложки, показанной на фиг. 1. Те же ссылочные позиции, как на фиг. 3, обозначают те же самые элементы.

Как показано в фиг. 6, матричная подложка дополнительно включает в себя выравнивающий слой 9 (имеющий толщину, например, 1-4 мкм), обеспеченный на пассивирующем слое 5. Выравнивающий слой 9 снабжен четвертым сквозным отверстием V4, соответствующим третьему сквозному отверстию V3. Здесь соответствие четвертого сквозного отверстия V4 третьему сквозному отверстию V3 означает, что четвертое сквозное отверстие V4 может открыть находящееся ниже третье сквозное отверстие V3 после того, как четвертое сквозное отверстие V4 сформировано в выравнивающем слое 9 и электрод 2 пикселя еще не депонирован.

Электрод 2 пикселя расположен на выравнивающем слое 9. Электрод 2 пикселя включает в себя первый участок 21, расположенный в третьем сквозном отверстии V2, второй участок 22, расположенный в четвертом сквозном отверстии V4, и третий участок 23, расположенный на выравнивающем слое 9. Первый участок 21 электрода 2 пикселя находится в прямом электрическом контакте с электродом стока второго участка D2-2. Поскольку участок электрода 2 пикселя депонирован в третьем сквозном отверстии V3 и четвертом сквозном отверстии V4, может быть достигнуто надежное соединение между первым участком 21 электрода 2 пикселя и вторым участком D2-2 электрода стока D2.

Ограничивающий пиксель слой 6 расположен над электродом 2 пикселя. Ограничивающий пиксель слой 6 снабжен множеством отверстий 61 (только одно из них показано на фиг. 6). Каждое из множества отверстий 61 проходит через ограничивающий пиксель слой 6, чтобы открыть область соответствующего электрода 2 пикселя. В пиксельной области, показанной на фиг. 6, органический светоизлучающий слой 7 расположен внутри отверстия 61, чтобы покрыть открытую область электрода 2 пикселя, и дополняющий электрод 8 пикселя обеспечен, чтобы покрыть органический светоизлучающий слой 7 и ограничивающий пиксель слой 6. Дополняющий электрод 8 пикселя, органический светоизлучающий слой 7 и электрод 2 пикселя формируют устройство OLED.

В примере на фиг. 6 ортогональная проекция четвертого сквозного отверстия V4 на базовую подложку 1 полностью покрывает ортогональную проекцию третьего сквозного отверстия V3 на базовую подложку 1. Кроме того, ортогональная проекция четвертого сквозного отверстия V4 на базовую подложку 1 полностью покрывает ортогональную проекцию второго сквозного отверстия V2 на базовую подложку 1. Область четвертого сквозного отверстия V4 является большой и обеспечивает хорошее электрическое соединение между электродом 2 пикселя и электродом стока D2. Здесь ортогональная проекция четвертого сквозного отверстия V4 на базовую подложку 1 может быть круглой или квадратной. Кроме того, геометрический центр ортогональной проекции четвертого сквозного отверстия V4 на базовую подложку 1 накладывается на геометрический центр ортогональной проекции третьего сквозного отверстия V3 на базовую подложку 1.

В описанных выше вариантах осуществления каждый из изолирующего слоя 3 затвора, межслойного изолирующего слоя 4 и пассивирующего слоя 5 может быть сделан из нитрида кремния или оксида кремния. Каждый из них может представлять собой однослойную структуру или многослойную структуру, такую как оксид кремния и нитрид кремния, уложенные один поверх другого. Выравнивающий слой 9 может быть изготовлен с использованием органической смолы. Электрод 2 пикселя может быть изготовлен посредством использования прозрачных металлооксидных электропроводных материалов, таких как ITO (оксид индия-олова), IZO (оксид индия-цинка) и FTO (оксид олова, легированный фтором). В вариантах осуществления, в которых электрод 2 пикселя является, в частности, анодом устройства OLED, электрод 2 пикселя может быть изготовлен с использованием прозрачного металлооксидного электропроводного материала. В качестве альтернативы электрод 2 пикселя также может применять многослойную структуру из прозрачного металлооксидного электропроводного материала и металлического материала, такого как серебро (Ag). Например, электрод 2 пикселя может представлять собой трехслойную структуру ITO\Ag\ITO. Дополняющий электрод 8 пикселя может быть сделан из металлического материала, такого как алюминий (Al) и/или серебро (Ag), и может представлять собой однослойную или многослойную структуру. Также предусмотрены другие варианты осуществления.

Следует понимать, что хотя в приведенных выше вариантах осуществления тонкопленочные транзисторы показаны и описаны как транзистор с верхним затвором, каждый из них может представлять собой транзистор с нижним затвором, в котором электрод затвора расположен ближе к базовой подложке 1, чем активный слой L2.

Фиг. 7 является блок-схемой, показывающей устройство 70 отображения в соответствии с вариантом осуществления настоящего раскрытия. В качестве примера и без ограничения устройство 70 отображения может представлять собой любой продукт или компонент, имеющий функцию отображения, например, сотовый телефон, планшет, телевизор, монитор, ноутбук, цифровая рамка для фотографий, навигатор и т.п.

Согласно фиг. 7, устройство 700 отображения 70 включает в себя панель 100 отображения для отображения изображений, формирователь 200 сигналов затворов для выдачи сигналов сканирования затворов на панель 100 отображения, формирователь 300 сигналов данных для выдачи напряжения сигналов данных на панель 100 отображения и контроллер 400 синхронизации для управления формирователем 200 сигналов затворов и формирователем 300 сигналов данных.

Панель 100 отображения включает в себя матричную подложку 101 и встречную подложку 102 напротив матричной подложки 101. В случае устройства жидкокристаллического дисплея панель 100 отображения дополнительно включает в себя жидкокристаллический слой (не показан) между матричной подложкой 101 и встречной подложкой 102, и встречная подложка 102 может представлять собой подложку с цветовыми фильтрами. В случае устройства отображения на органических светодиодах встречная подложка 102 может представлять собой защитную панель.

Матричная подложка 101 включает в себя множество пиксельных областей PX, размещенных в массиве. Каждая из пиксельных областей PX расположена на соответствующем пересечении множества затворных шин GL и множества шин данных DL. Каждая пиксельная область включает в себя пиксель, который включает в себя тонкопленочный транзистор (не показан) и другие соответствующие компоненты.

Формирователь 200 сигналов затворов электрически соединен с первыми концами соответствующих затворных шин GL, тем самым последовательно прикладывая сигналы сканирования затворов к соответствующим затворным шинам GL. В некоторых иллюстративных вариантах осуществления формирователь 200 сигналов затворов может быть непосредственно установлен (например, интегрирован) в матричной подложке 101. В качестве альтернативы формирователь 200 сигналов затворов может быть соединен с панелью 100 отображения через корпус на ленточном носителе (Tape Carrier Package; TCP).

Формирователь 300 сигналов данных электрически соединен с первыми концами соответствующих шин данных DL для выдачи напряжений сигналов данных на соответствующие шины данных DL. В некоторых вариантах осуществления формирователь 300 сигналов данных может включать в себя множество микросхем формирователей сигналов данных, работающих параллельно.

Контроллер 400 синхронизации управляет работой каждого из формирователя 200 сигналов затворов и формирователя 300 сигналов данных. В частности, контроллер 400 синхронизации выдает сигналы управления данными и данные изображения, чтобы управлять работой формирователя 300 сигналов данных, и выдает сигналы управления затворами, чтобы управлять работой формирователя 200 сигналов затворов. Сигналы управления данными и данные изображения подаются в формирователь 300 сигналов данных. Сигналы управления затворами подаются в формирователь 200 сигналов затворов.

Хотя настоящее раскрытие было проиллюстрировано и подробно описано на чертежах и в предшествующем описании, иллюстрацию и описание следует считать иллюстративными, а не ограничивающими. Настоящее раскрытие не ограничено раскрытыми вариантами осуществления. Вариации раскрытых вариантов осуществления могут быть поняты и выполнены специалистами в области техники при осуществлении на практике заявленного объекта изобретения на основе изучения чертежей, описания и приложенной формулы изобретения. В пунктах формулы изобретения слово "содержит" не исключает другие элементы или этапы, и употребление единственного числа не исключает множество. Тот лишь факт, что некоторые меры описаны во взаимно различных зависимых пунктах формулы изобретения, не указывает, что эти меры не могут использоваться для получения преимуществ.

Изобретения относятся к устройствам отображения изображения. Матричная подложка содержит базовую подложку, содержащую множество пиксельных областей, множество тонкопленочных транзисторов, распределенных в соответствующих пиксельных областях, при этом каждый из тонкопленочных транзисторов содержит активный слой, расположенный на подложке; электрод затвора, расположенный на базовой подложке, причем активный слой и электрод затвора уложены один поверх другого; электрод истока, расположенный над электродом затвора, причем электрод истока электрически соединен с активным слоем через первое сквозное отверстие; электрод стока, расположенный над электродом затвора, причем электрод стока электрически соединен с активным слоем через второе сквозное отверстие, при этом электрод стока содержит первый участок, расположенный во втором сквозном отверстии; пассивирующий слой, расположенный на электродах истока и электродах стока, множество электродов пикселей, распределенных в соответствующих пиксельных областях, причем каждый из электродов пикселей электрически соединен с соответствующим одним из электродов стока через соответствующее третье сквозное отверстие, при этом электрод пикселя в каждой из пиксельных областей содержит два отдельных первых участка, расположенных в третьем сквозном отверстии, и второй участок, соединяющий два первых участка, два первых участка электрода пикселя находятся на двух противоположных сторонах второго сквозного отверстия, соответственно. В соответствии с другим аспектом настоящего изобретения обеспечены панель отображения, содержащая описанную выше матричную подложку, а также устройство отображения, содержащее эту панель отображения. 4 н. и 16 з.п. ф-лы, 7 ил.

1. Матричная подложка, содержащая:

базовую подложку, содержащую множество пиксельных областей, размещенных в массиве;

множество тонкопленочных транзисторов, распределенных в соответствующих пиксельных областях из упомянутого множества пиксельных областей, при этом каждый из тонкопленочных транзисторов содержит:

активный слой, расположенный на подложке;

электрод затвора, расположенный на базовой подложке, причем активный слой и электрод затвора уложены один поверх другого;

электрод истока, расположенный над электродом затвора, причем электрод истока электрически соединен с активным слоем через первое сквозное отверстие; и

электрод стока, расположенный над электродом затвора, причем электрод стока электрически соединен с активным слоем через второе сквозное отверстие, при этом электрод стока содержит первый участок, расположенный во втором сквозном отверстии;

пассивирующий слой, расположенный на электродах истока и электродах стока, причем пассивирующий слой покрывает первые участки электродов стока; и

множество электродов пикселей, распределенных в соответствующих пиксельных областях из упомянутого множества пиксельных областей и расположенных на пассивирующем слое, причем каждый из электродов пикселей электрически соединен с соответствующим одним из электродов стока через соответствующее третье сквозное отверстие, которое проходит через пассивирующий слой,

при этом на виде в разрезе матричной подложки электрод пикселя в каждой из пиксельных областей содержит два отдельных первых участка, расположенных в третьем сквозном отверстии, и второй участок, соединяющий два первых участка, два первых участка электрода пикселя находятся на двух противоположных сторонах второго сквозного отверстия, соответственно.

2. Матричная подложка по п. 1, в которой электрод стока дополнительно содержит второй участок вне второго сквозного отверстия, и при этом электрод пикселя электрически соединен со вторым участком электрода стока через третье сквозное отверстие.

3. Матричная подложка, содержащая:

базовую подложку, содержащую множество пиксельных областей, размещенных в массиве;

множество тонкопленочных транзисторов, распределенных в соответствующих пиксельных областях из упомянутого множества пиксельных областей, при этом каждый из тонкопленочных транзисторов содержит:

активный слой, расположенный на подложке;

электрод затвора, расположенный на базовой подложке, причем активный слой и электрод затвора уложены один поверх другого;

электрод истока, расположенный над электродом затвора, причем электрод истока электрически соединен с активным слоем через первое сквозное отверстие; и

электрод стока, расположенный над электродом затвора, причем электрод стока электрически соединен с активным слоем через второе сквозное отверстие, при этом электрод стока содержит первый участок, расположенный во втором сквозном отверстии;

пассивирующий слой, расположенный на электродах истока и электродах стока, причем пассивирующий слой покрывает первые участки электродов стока;

множество электродов пикселей, распределенных в соответствующих пиксельных областях из упомянутого множества пиксельных областей и расположенных на пассивирующем слое, причем каждый из электродов пикселей электрически соединен с соответствующим одним из электродов стока через соответствующее третье сквозное отверстие, которое проходит через пассивирующий слой; и

выравнивающий слой, расположенный на пассивирующем слое,

причем электрод стока дополнительно содержит второй участок вне второго сквозного отверстия, и при этом электрод пикселя электрически соединен со вторым участком электрода стока через третье сквозное отверстие, выравнивающий слой снабжен множеством четвертых сквозных отверстий, при этом ортогональная проекция каждого из четвертых сквозных отверстий на базовую подложку полностью покрывает ортогональную проекцию соответствующего одного из третьих сквозных отверстий на базовую подложку, и

причем каждый из электродов пикселей содержит первый участок, расположенный в соответствующем третьем сквозном отверстии, второй участок, расположенный в соответствующем одном из четвертых сквозных отверстий, и третий участок, расположенный на выравнивающем слое.

4. Матричная подложка по п. 3, в которой ортогональная проекция каждого из четвертых сквозных отверстий на базовую подложку дополнительно полностью покрывает ортогональную проекцию соответствующего одного из вторых сквозных отверстий на базовую подложку.

5. Матричная подложка по п. 4, в которой ортогональная проекция каждого из четвертых сквозных отверстий на базовую подложку имеет форму, выбранную из группы, состоящей из круга и квадрата.

6. Матричная подложка по п. 3, в которой геометрический центр ортогональной проекции каждого из четвертых сквозных отверстий на базовую подложку накладывается на геометрический центр ортогональной проекции соответствующего третьего сквозного отверстия на базовую подложку.

7. Матричная подложка по п. 3, в которой выравнивающий слой имеет толщину 1-4 мкм.

8. Матричная подложка по п. 1, в которой ортогональная проекция третьего сквозного отверстия на базовую подложку окружает ортогональную проекцию второго сквозного отверстия на базовую подложку.

9. Матричная подложка по п. 8, в которой ортогональная проекция третьего сквозного отверстия на базовую подложку имеет форму круга.

10. Матричная подложка по п. 8, в которой геометрический центр ортогональной проекции третьего сквозного отверстия на базовую подложку накладывается на геометрический центр ортогональной проекции второго сквозного отверстия на базовую подложку.

11. Матричная подложка по п. 8, в которой ортогональная проекция третьего сквозного отверстия на базовую подложку частично накладывается на ортогональную проекцию второго сквозного отверстия на базовую подложку.

12. Матричная подложка по п. 1, дополнительно содержащая:

ограничивающий пиксель слой, расположенный на множестве электродов пикселей и снабженный множеством отверстий, каждое из множества отверстий проходит через ограничивающий пиксель слой, чтобы открыть область соответствующего одного из множества электродов пикселей;

множество органических светоизлучающих слоев, каждый из которых расположен в соответствующем одном из отверстий и покрывает открытую область соответствующего электрода пикселя; и

дополняющий электрод пикселя, покрывающий множество органических светоизлучающих слоев и ограничивающий пиксель слой.

13. Матричная подложка по п. 12, в которой ограничивающий пиксель слой имеет толщину 1-3 мкм.

14. Матричная подложка по п. 1, в которой второе сквозное отверстие сужается по направлению к базовой подложке.

15. Матричная подложка по п. 14, в которой второе сквозное отверстие имеет минимальную апертуру, которая больше, чем утроенная глубина второго сквозного отверстия.

16. Матричная подложка по п. 1, дополнительно содержащая изолирующий слой затвора, расположенный между электродами затвора и активными слоями.

17. Матричная подложка по п. 16, в которой в каждом из множества тонкопленочных транзисторов электрод затвора расположен дальше от базовой подложки, чем активный слой.

18. Матричная подложка по п. 16, в которой в каждом из множества тонкопленочных транзисторов электрод затвора расположен ближе к базовой подложке, чем активный слой.

19. Панель отображения, содержащая матричную подложку по любому из пп. 1-18.

20. Устройство отображения, содержащее панель отображения по п. 19.

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| US 9252268 B2, 02.02.2016 | |||

| ПОДЛОЖКА АКТИВНОЙ МАТРИЦЫ, ЖИДКОКРИСТАЛЛИЧЕСКАЯ ПАНЕЛЬ, ЖИДКОКРИСТАЛЛИЧЕСКИЙ ДИСПЛЕЙНЫЙ БЛОК, ЖИДКОКРИСТАЛЛИЧЕСКОЕ ДИСПЛЕЙНОЕ УСТРОЙСТВО И ТЕЛЕВИЗИОННЫЙ ПРИЕМНИК | 2009 |

|

RU2490724C2 |

| CN 202796957 U, 13.03.2013. | |||

Авторы

Даты

2021-04-02—Публикация

2018-08-02—Подача