Изобретение относится к области электротехники, а именно к источникам опорного напряжения с калибровкой выходного напряжения и может быть использовано в составе различных электронных устройств в качестве источника опорного напряжения (далее ИОН).

Основное требование к схеме ИОН - стабильное выходное напряжение Vout, то есть минимальный уход Vout при изменении температуры во всем рабочем диапазоне температур (от -40 до 100 С), а также минимальный уход Vout при заданной температуре в зависимости от образцов и партии изготовления ИОН (пластины).

В схемах ИОН, представленных в патентах RU172597, RU2673243, CN103389772 A и CN205942498 U температурная стабильность выходного напряжения Vout достигается определенным отношением номиналов резисторов в схеме ИОН при фиксированных значениях технологических и конструктивных параметров активных элементов (Ni, XTI, IS и M для диодов и W, L, TOX и VTH для МОП транзисторов) которые в свою очередь отклоняются от модельных значений в ходе процесса изготовления пластины ИОН.

Нарушение температурной компенсации ИОН и смещение выходного напряжения при фиксированной температуре происходит в силу ряда дестабилизирующих факторов:

- смещение ИТУН (источника тока управляемого напряжением) в составе ИОН и температурный дрейф смещения (из-за разброса топологии, толщины, подзатворного окисла и порога транзисторов);

- разброс параметров диодов (Ni, XTI, IS) образованных p-n переходом эмиттер-база PNP биполярного транзистора;

- разброс топологии (ширина/длина) резисторов;

- разброс топологии, толщины подзатворного окисла и порога P-канальных транзисторов, образующих источники тока, управляемые выходным потенциалом ИТУН.

В перечисленных выше патентах аналогах отсутствуют схемотехнические решения для уменьшения чувствительности рабочей точки ИОН к разбросу вышеописанных параметров. Чтобы свезти к минимуму действия дестабилизирующих факторов используют либо калибровку выходного напряжения (как в заявленном изобретении) по точкам из рассматриваемого диапазона температур (-40, 100) с использованием эталонного опорного напряжения, либо ручную подстройку (тримминг) с визуальной оценкой выходного напряжения. В зависимости от алгоритма калибровки или подстройки схемы ИОН возможен полный либо частичный учет дестабилизирующих факторов, что в свою очередь влияет на диапазон разброса выходного напряжения.

Наиболее близкими к заявленному изобретению являются источники опорного напряжения (ИОН), описанные в двух статьях:

- A 2-V 23-uA 5.3-ppm/ C Curvature-Compensated CMOS Bandgap Voltage Reference (IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 38, NO. 3, 10 MARCH 2003, Page(s): 561-564);

- A Process Variation Insensitive Bandgap Reference with Self-Calibration Technique (2013 IEEE 10th International Conference on ASIC, Data of Conference: 28-31 Oct 2013, Date Added to IEEE Xplore: 08 May 2014).

В первой статье представлен ИОН с триммингом, во второй ИОН с калибровкой. Данные ИОН выбраны в качестве прототипов заявленного изобретения. Оба варианта существенно усложняют схему ИОН, увеличивают площадь кристалла, но разброс выходного напряжения в рабочем диапазоне температур после калибровки или тримминга будет заведомо меньше чем у представленных выше схем ИОН в патентах RU172597, RU2673243, CN103389772 A и CN205942498 U при изготовлении пластин ИОН по одной технологии.

В схеме ИОН первого прототипа с триммингом происходит подстройка 2-х резисторов с разными температурными коэффициентами так, чтобы изменение выходного напряжения в рассматриваемом диапазоне температур было минимальным. При правильном подборе номиналов резисторов и режимного тока прямо пропорционального абсолютной температуре получают второй порядок температурной компенсации (график зависимости выходного напряжения в рабочем диапазоне температур в виде синусоиды с двумя экстремумами). При этом изменение выходного напряжения получают порядка 100 мкВ в рабочем диапазоне температур.

Недостаток ИОН первого прототипа заключается в отсутствии автоматизации процесса подстройки, необходимости визуальной оценки (снятие осциллограммы) измеренного при фиксированных значениях температуры выходного напряжения для правильного выбора комбинации управляющих сигналов схемы подстройки (Табл. 1).

В схеме ИОН второго прототипа с калибровкой происходит автоматическая подстройка резистора для подавления действия ряда дестабилизирующих факторов, происходит полная компенсация напряжения смещения ИТУН (источника тока управляемого напряжением), входящего в состав ИОН, и частичная компенсация разброса топологии резисторов ИОН. Преимущество ИОН второго прототипа заключается в наличии автоматического процесса калибровки при данной температуре (используется одна точка), запускающегося в момент подачи питания на ИОН.

Недостаток ИОН второго прототипа заключается в том, что он является чувствительным к разбросу параметров диодов и токозадающего резистора, поэтому существенно уступает по критерию стабильности выходного напряжения ИОН первого прототипа с тримменгом (Табл. 1).

Техническим результатом изобретения является создание источника опорного напряжения с калибровкой выходного напряжения с улучшенными эксплуатационными характеристиками, а именно со стабильным выходным напряжением Vout после калибровки и автоматическим процессом подстройки регулируемых элементов, за счет наличия схемы смещения базы биполярных транзисторов BJT1 и BJT2, состоящей из блока управления температурным коэффициентом (СTK - Control block temperature coefficient), осуществляющим преобразование цифрового входного кода в температурный коэффициент выходного тока, и нагрузочныого резистора Rt, подключенного между эмиттером и коллектором биполярных транзисторов BJT1 и BJT2, а также за счет наличия источника тока управляемого напряжением (OTA_TR - Operational Transconductance Amplifier) с подстройкой смещения, выполняемой блоком управления напряжением смещения CVOS (Control block offset voltage), входящим в состав источника тока управляемого напряжением.

Поставленный технический результат достигнут путем создания источника опорного напряжения с калибровкой выходного напряжения, включающего цифровой и аналоговый блоки, причем аналоговый блок содержит соединенные между собой источник опорного напряжения (ИОН) типа bandgap, компаратор с перекрестными ключами на входе и генератор тактовых импульсов, а цифровой блок содержит регистр последовательного приближения, память и схему управления, включающую в себя цифровую схему упрощенного арифметико-логического устройства, при этом выходы компаратора и генератора тактовых импульсов соединены с входами цифрового блока, выходы которого соединены с входами управления перекрестных ключей на входе компаратора и с входом ИОН типа bandgap, о т л и ч а ю щ е г о с я тем, что ИОН типа bandgap содержит источник тока управляемый напряжением (OTA_TR), выполненный с возможностью подстройки смещения с помощью входящего в его состав блока управления напряжением смещения (CVOS), и схему смещения базы биполярных транзисторов BJT1 и BJT2, состоящую из блока управления температурным коэффициентом (СTK) напряжения базы биполярных транзисторов BJT1 и BJT2 с токовым выходом и нагрузочного резистора Rt, подключенного между эмиттером и коллектором биполярных транзисторов BJT1 и BJT2, входящих в состав ИОН типа bandgap, причем

- блок управления напряжением смещения (CVOS) источника тока управляемого напряжением (OTA_TR) выполнен с возможнстью изменения, с пмощью цифрового входного кода, смещения источника тока управляемый напряжением (OTA_TR) и, следовательно, изменения выходного напряжения Vout ИОН типа bandgap в требуемом диапазоне; причем регистр последовательного приближения выполнен с возможностью формирования цифрового кода на входе блока управления напряжением смещения (CVOS) на соответствующей стадии калибровки, при этом уменьшения с каждым шагом разницы между выходным напряжением Vout ИОН типа bandgap и внешним опорным напряжением Vref в средней точке рабочего диапазона температур, при этом любое изменение смещения источника тока управляемого напряжением (OTA_TR) не влияет на кривизну температурной зависимости выходного напряжения Vout ИОН типа bandgap;

- блок управления температурным коэффициентом (СTK) потенциала базы биполярных транзисторов BJT1 и BJT2 выполнен с возможностью преобразования цифрового входного кода в температурный коэффициент выходного тока, и, следовательно, температурного коэффициента выходного напряжения Vout ИОН типа bandgap в требуемом диапазоне; регистр последовательного приближения выполнен с возможностью формирования цифрового кода на входе блок управления температурным коэффициентом (СTK) на соответствующей стадии калибровки, при этом с каждым шагом уменьшения разницы между внешним опорным напряжением Vref и выходным напряжением Vout ИОН типа bandgap в крайних точках рабочего диапазона температур, при этом выравнивания температурной зависимости выходного напряжения Vout ИОН типа bandgap, при постоянном и приблизительно равном Vref выходном напряжении Vout в средней точке рабочего диапазона температур;

- блок управления напряжением смещения (CVOS) и блок управления температурным коэффициентом (СTK) выполнены с возможностью определения алгоритма калибровки, содержащего от двух до трех стадий калибровки в зависимости от требований к температурной стабильности.

В предпочтительном варианте осуществления источника опорного напряжения источник тока управляемого напряжением (OTA_TR) содержит блок управления напряжением смещения (CVOS), который выполнен с возможностью преобразования цифрового кода на входе в смещение источника тока управляемого напряжением (OTA_TR), при этом величина смещения задается разностью токов транзисторов входной дифференциальной пары блока управления напряжением смещения (CVOS) при постоянном суммарном токе потребления источника тока управляемого напряжением (OTA_TR), а разбаланс токов входной дифференциальной пары устанавливается цифро-аналоговым преобразователем ЦАП на базе двоично-взвешенных источников тока с токовым выходом (DAC_OTA), входящих в состав в состав блока CVOS.

В предпочтительном варианте осуществления источника опорного напряжения ИОН типа bandgap содержит блок управления температурным коэффициентом (СTK) с токовым выходом, подключенным к узлу базы биполярных транзисторов BJT1 и BJT2, и нагрузочный резистор Rt, подключенный между базой и эмиттером биполярных транзисторов BJT1 и BJT2, при этом блок управления температурным коэффициентом (СTK) выполнен с возможностью преобразования цифрового кода на входе в температурный коэффициент выходного тока и содержит:

- блок I_PTAT, выполненный с возможностью формирования опорного тока, пропорционального абсолютной температуре;

- блок I_CTAT, выполненный с возможностью формирования опорного тока, обратно пропорционального абсолютной температуре;

- блок SAD, выполненный с возможностью формирования двух токов одинаковой величины с равными по модулю и противоположными по знаку температурными коэффициентами;

- блок DAC_TK, выполненный с возможностью формирования выходного тока постоянной величины с температурным коэффициентом, задаваемым входным цифровым кодом.

В предпочтительном варианте осуществления источника опорного напряжения ИОН типа bandgap содержит два биполярных транзистора BJT1 и BJT2; блок управления температурным коэффициентом (CTK) с токовым выходом, подключенным к узлу базы биполярных транзисторов BJT1 и BJT2; нагрузочный низкоомный резистор Rt, подключенный между базой и эмиттером биполярных транзисторов BJT1 и BJT2; P-канальные транзисторы P1 и P2; источник тока управляемый напряжением (OTA_TR) с подстройкой смещения, причем сток транзистора P2 подключен к прямому входу источника тока управляемого напряжением (OTA_TR), сток транзистора P1 через резистор Rp подключен к инверсному входу источника тока управляемого напряжением (OTA_TR), выходное напряжение источника тока управляемого напряжением (OTA_TR) устанавливает потенциал затворов P-канальных транзисторов P1 и P2; токозадающий резистор R0 подключен между эмиттером биполярного транзистора BJT2 и стоком P-канального транзистора P2; резистор температурной компенсации Rp выполнен в виде сборки из последовательно соединенных резисторов R1, R2, R3, R4, R5, R6 и подключен между эмиттером биполярного транзистора BJT1 и стоком P-канального транзистора P1.

Для лучшего понимания заявленной полезной модели далее приводится ее подробное описание с соответствующими графическими материалами.

Табл. 1. Сравнительная характеристика прототипов и источника опорного напряжения с калибровкой выходного напряжения, выполненного согласно изобретению.

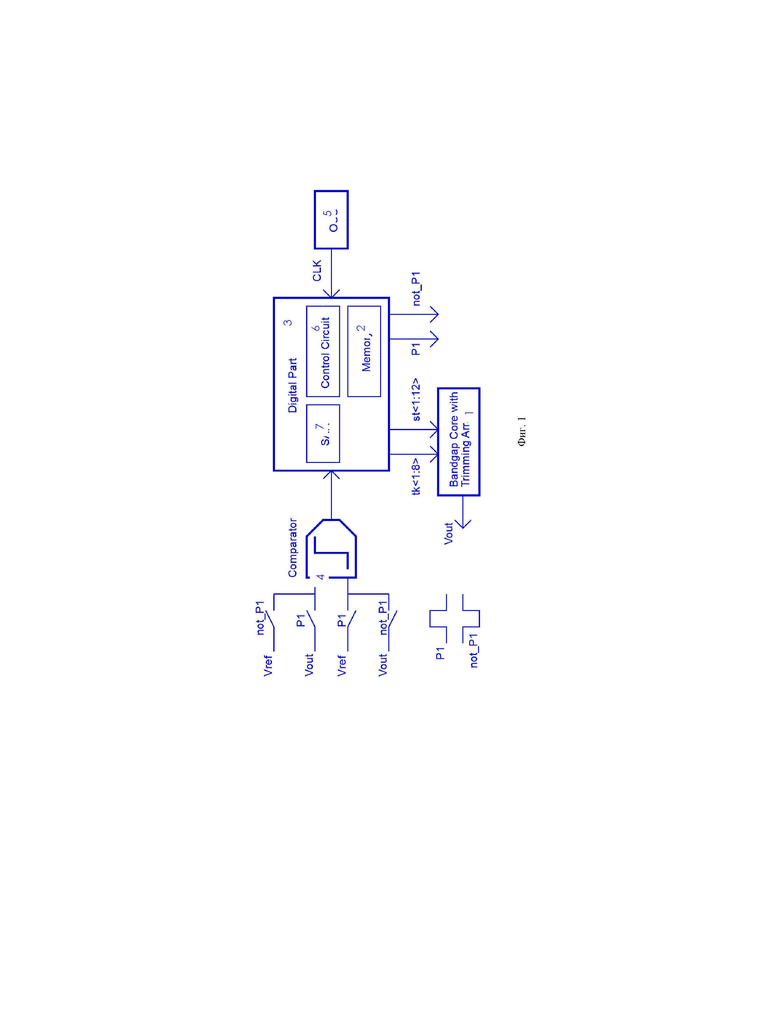

Фиг. 1. Блок-схема источника опорного напряжения с калибровкой выходного напряжения, выполненная согласно изобретению.

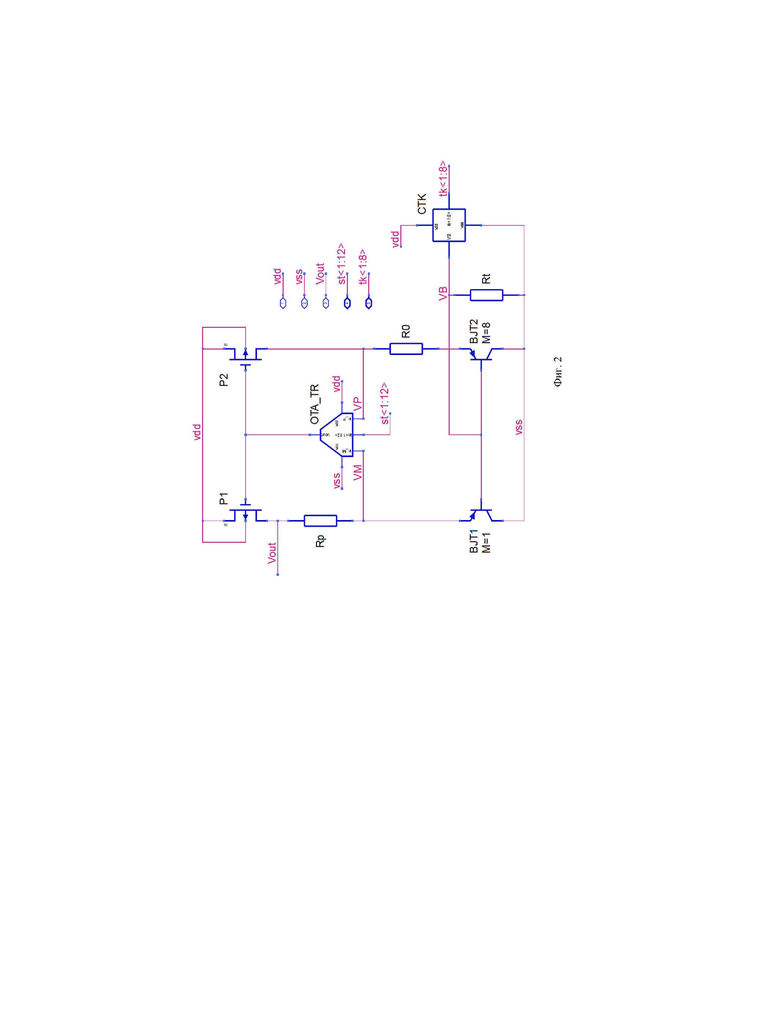

Фиг. 2. Схема источника опорного напряжения с калибровкой выходного напряжения, выполненная согласно изобретению.

Фиг. 3. Схема на транзисторном уровне источника опорного напряжения с калибровкой выходного напряжения, выполненная согласно изобретению.

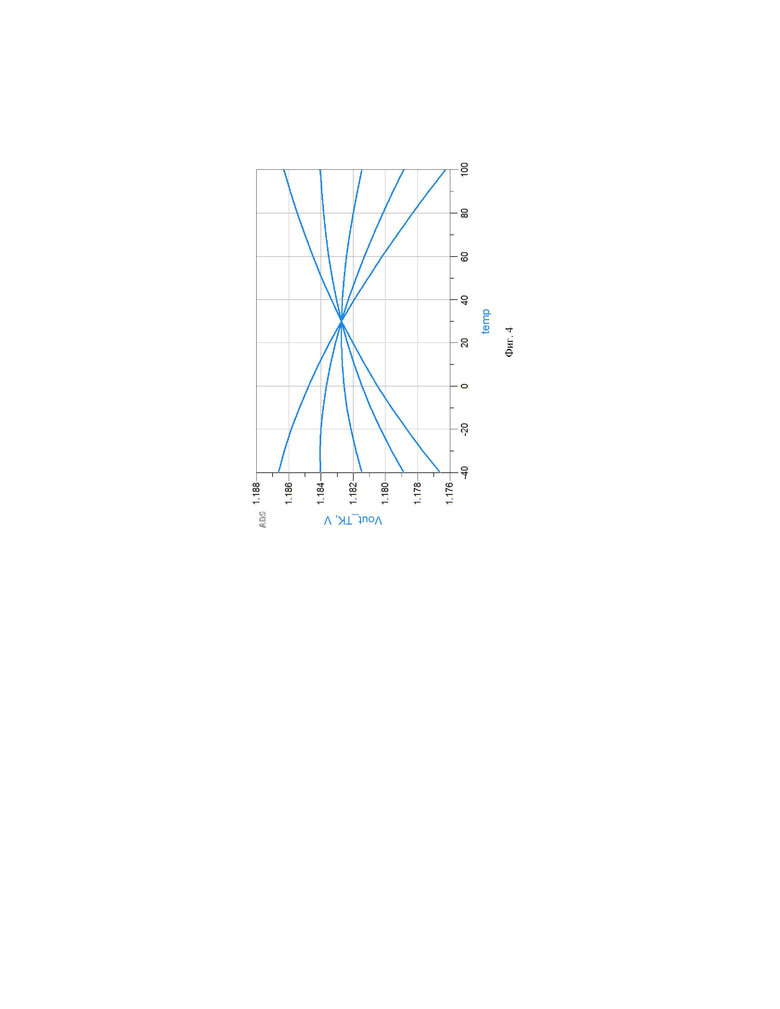

Фиг. 4. График функции зависимости выходного напряжения от температуры Vout(T) при изменении температурного коэффициента напряжения базы в источнике опорного напряжения с калибровкой выходного напряжения, выполненный согласно изобретению.

Фиг. 5. Схема блоков I_PTAT и I_CTAT, входящих в состав блока управления температурным коэффициентом (CTK), выполненная согласно изобретению.

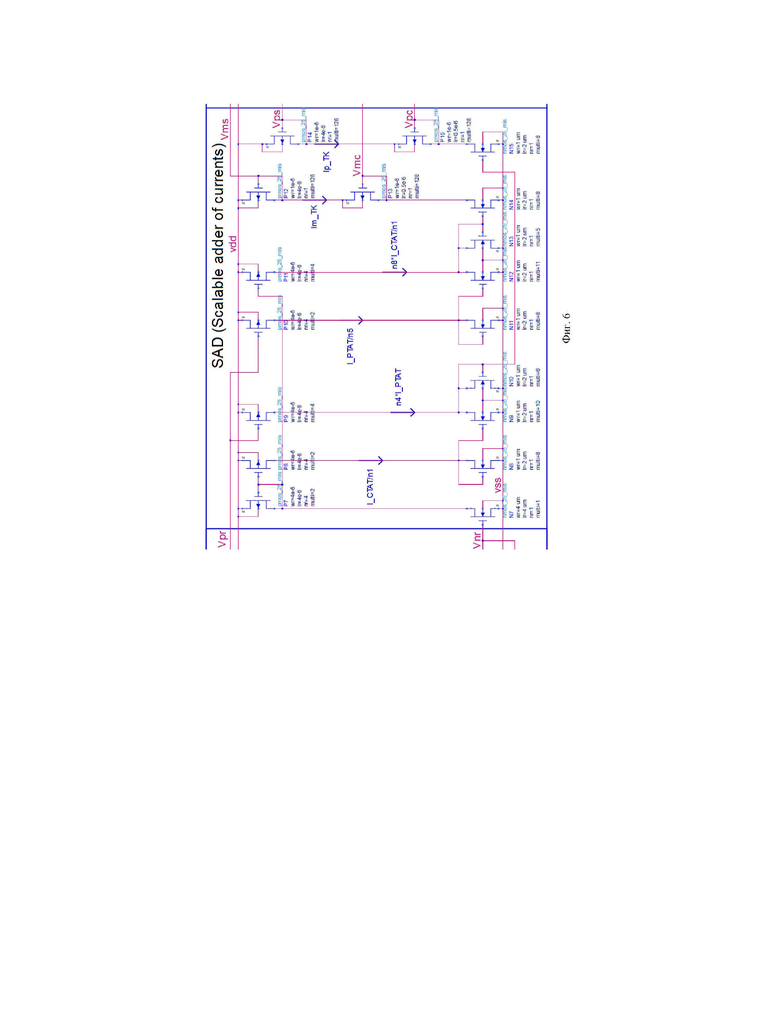

Фиг. 6. Схема блоков SAD, входящих в состав блока управления температурным коэффициентом (CTK), выполненная согласно изобретению.

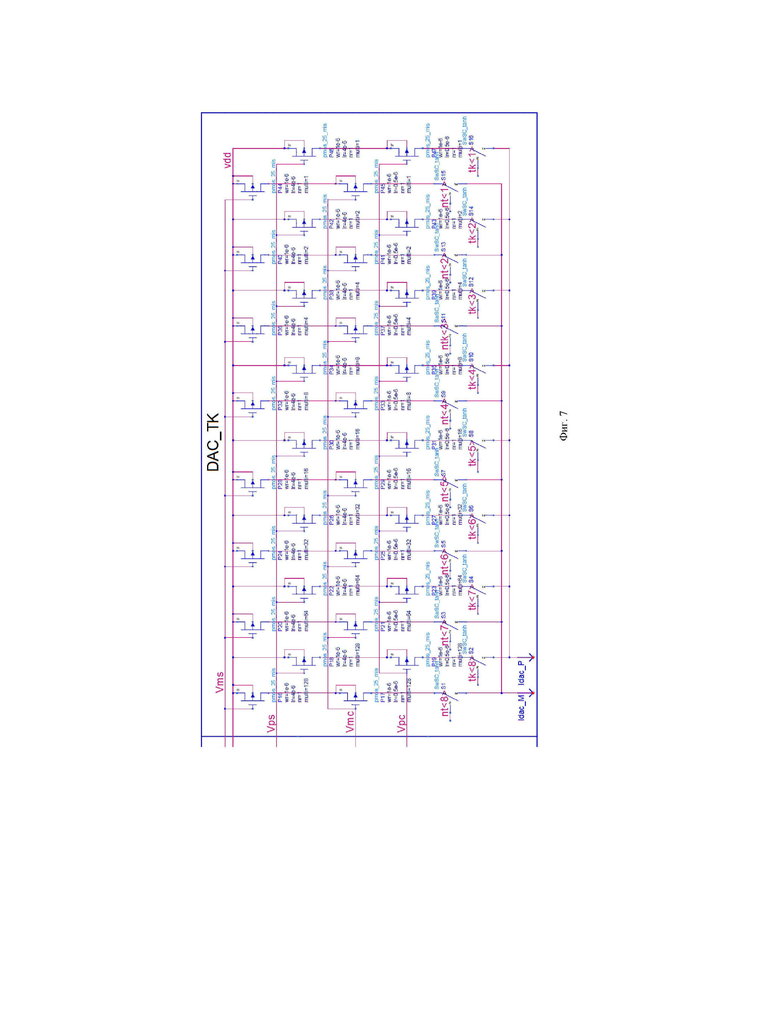

Фиг. 7. Схема блока DAC_TK, входящего в состав блока управления температурным коэффициентом (CTK), выполненная согласно изобретению.

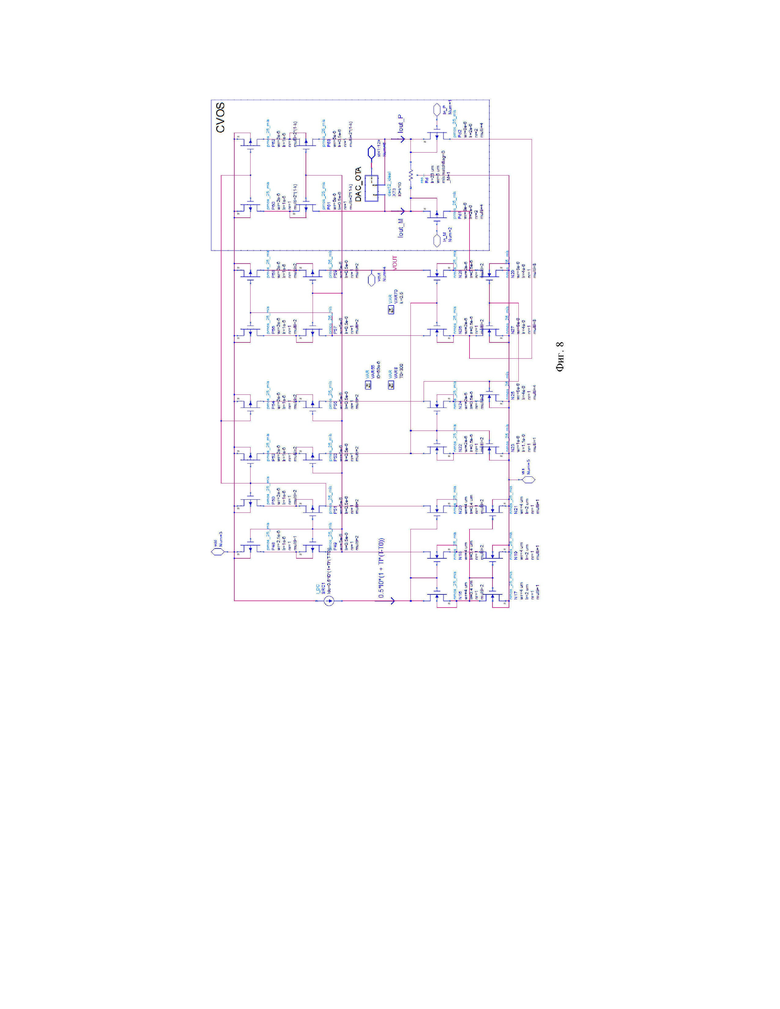

Фиг. 8. Схема источника тока управляемого напряжением (OTA_TR), входящего в состав ИОН типа bandgap, выполненная согласно изобретению.

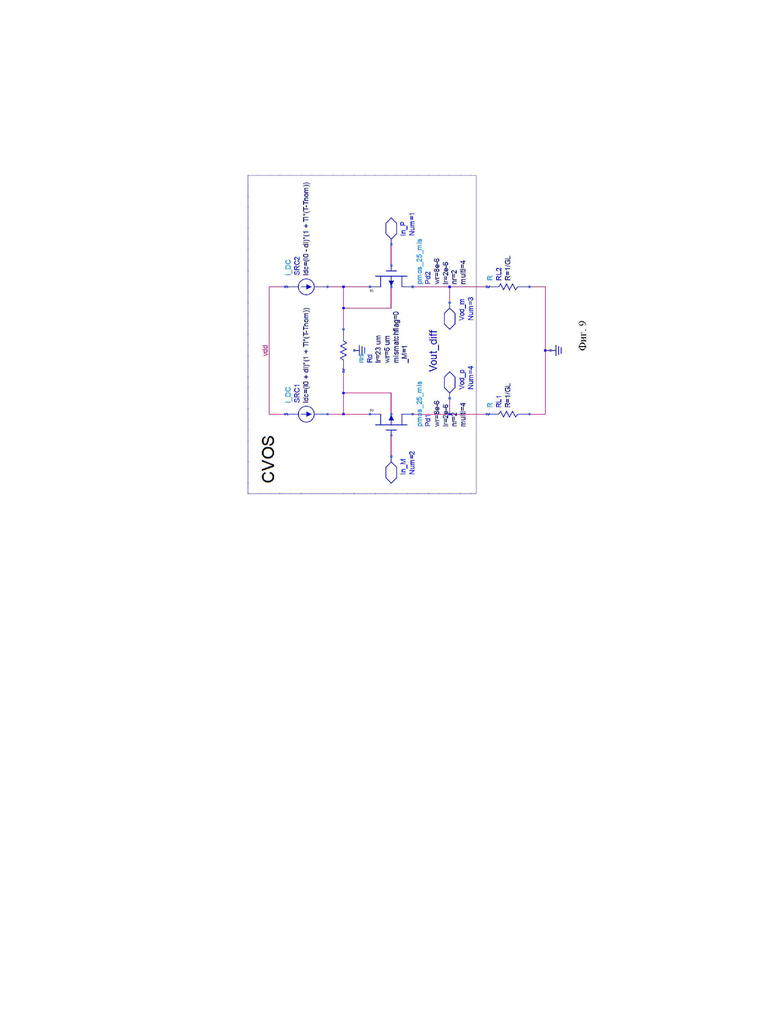

Фиг. 9. Схема блока управления напряжением смещения (CVOS), входящего в состав источника тока управляемого напряжением (OTA_TR), выполненная согласно изобретению.

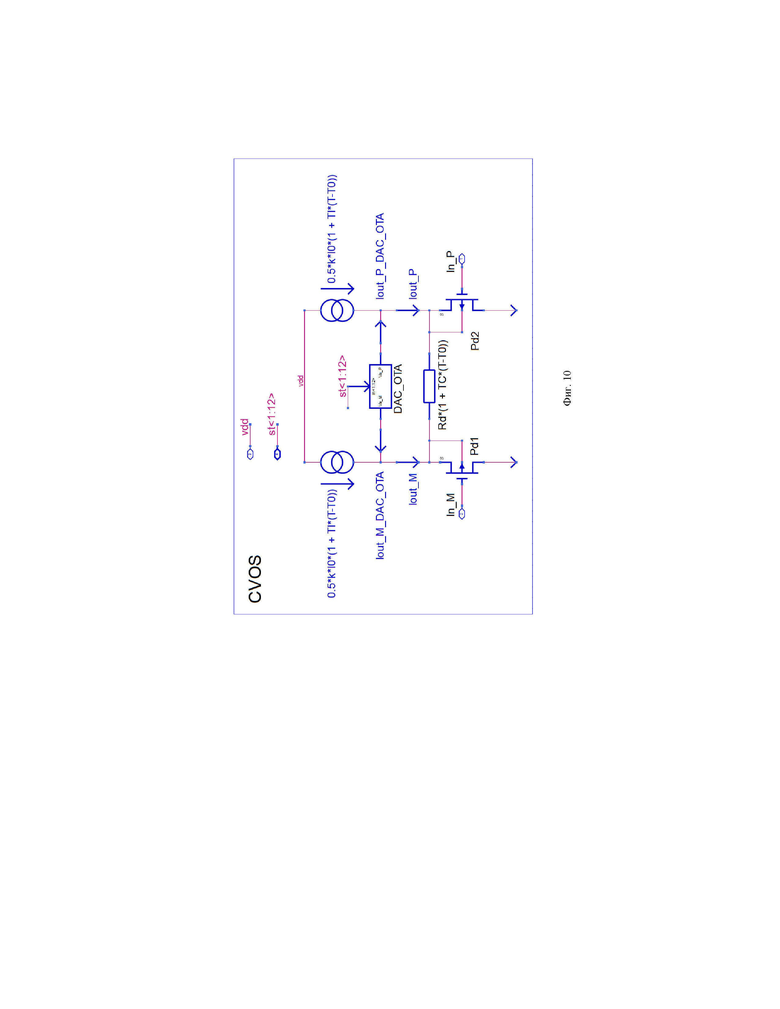

Фиг. 10. Эквивалентная схема подстроечной дифференциальной пары, входящего в состав блока управления напряжением смещения (CVOS) с недифференциальной нагрузкой 1/GL, выполненная согласно изобретению.

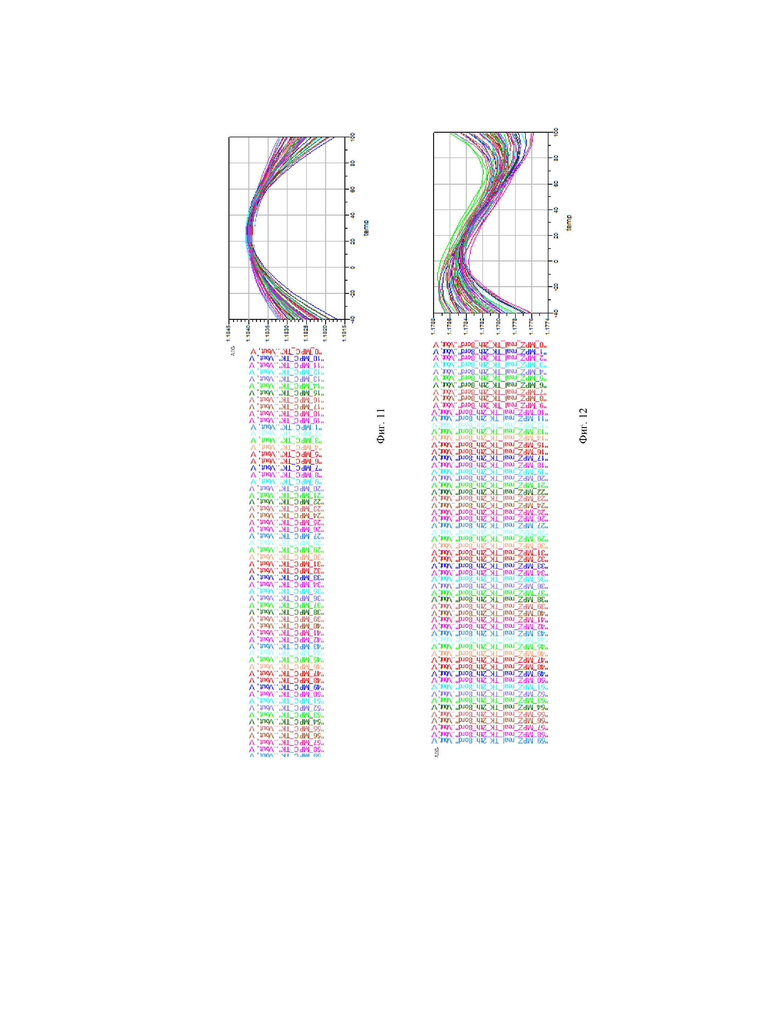

Фиг. 11. Семейство графиков выходного напряжения Vout(T) после калибровки источника опорного напряжения с калибровкой выходного напряжения, полученное в ходе статистического анализа MonteCarlo Process + Mismatch 60 Trials, выполненное согласно изобретению.

Фиг. 12. Семейство графиков выходного напряжения Vout(T) после калибровки источника опорного напряжения с калибровкой выходного напряжения (схема источника опорного напряжения с увеличенным порядком температурной компенсации), полученное в ходе статистического анализа MonteCarlo Process + Mismatch 60 Trials, выполненное согласно изобретению.

Рассмотрим более подробно функционирование заявленного источника опорного напряжения с калибровкой выходного напряжения (Фиг. 1 – 12).

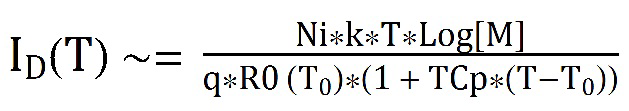

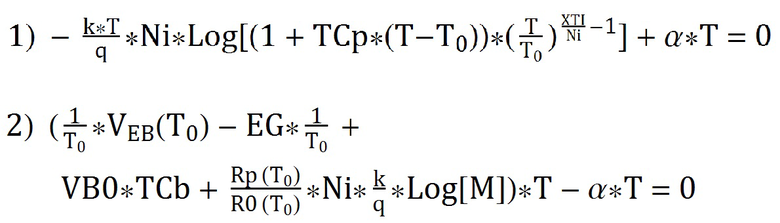

Рассмотрим алгоритм калибровки выходного напряжения. В заявленном источнике опорного напряжения используют калибровку выходного напряжения по трем точкам (-40, 26.85, 100) в рассматриваемом диапазоне температур (-40, 100). Число точек определяет число стадий калибровки (в заявленном изобретении - три точки). На первой стадии кристалл нагревают или охлаждают в зависимости от начальной температуры до средней температуры T0 = 26.85 (первая точка), осуществляют подстройку выходного напряжения Vout к внешнему опорному напряжению Vref путем изменения смещения источника тока управляемого напряжением (ИТУН) (OTA_TR), входящего в сотав источника 1 опорного напряжения (ИОН) типа bandgap, и сохранение в памяти 2 кода ключей подстроечного двеннадцатибитного цифро-аналогового преобразователя (ЦАП) (блок DAC_OTA в составе блока OTA_TR) на базе двоично-взвешенных источников тока с токовым выходом.

Смещение ИТУН (OTA_TR) подстраивают относительным изменением токов транзисторов входной дифференциальной пары, при этом суммарный ток потребления ИТУН остается постоянным (Фиг. 8 - 9). Ток дифференциальной пары равен сумме выходного тока цифро-аналогового преобразователя (DAC_OTA) (1-k)*I0*(1+TI*(T-T0)) и постоянной составляющей k*I0*(1+TI*(T-T0)), которые формируют с помощью токового зеркала от одного опорного ИТУН (OTA_TR) (0.5*I0*(1 + TI*(T-T0))). В зависимости от максимальной величины смещения ИТУН (OTA_TR), полученной в ходе статистического анализа (Monte Carlo Process + Mismatch), устанавливают вклад выходного тока ЦАП (DAC_OTA) в общий ток дифференциальной пары с помощью коэффициента k (в данной схеме k = 0.5). Температурные коэффициенты источника опорного тока и резистора Rd между истоками транзисторов входной дифференциальной пары должны быть равны по модулю и противоположны по знаку (резистор Rd с положительным температурным коэффициентом, источник тока для ИТУН (OTA_TR) и ЦАП (DAC_OTA) с отрицательным температурным коэффициентом). В такой схеме любое изменение смещения ИТУН (OTA_TR) в ходе подстройки не влияет на кривизну температурной зависимости выходного напряжения ИОН 1 типа bandgap, то есть точки экстремума функции Vout(T) не смещаются по температурной оси в диапазоне от -40 до 100 С, что в свою очередь обеспечивает меньший диапазон подстройки Vout на следующей стадии калибровки (это первый ключевой момент схемы калибровки).

Для сравнения, подстройка номинала одного из резисторов Rp и/или R0 в схеме заявленного источника опорного напряжения приводит к изменению величины выходного напряжения при заданной температуре и к смещению экстремумов функции Vout(T) по оси температур в рассматриваемом диапазоне. В такой схеме для установки температурной компенсации (выравнивания кривой Vout(T) по оси напряжения) потребуется больший диапазон, а, следовательно, и число разрядов, подстроечного ЦАП на следующей стадии калибровки.

В конце первой стадии калибровки в памяти сохраняют состояние ключей подстроечного ЦАП (DAC_OTA) st<1:12> и вычисленную разность st_d<1:12> = st<1:12> - D_const<1:12>. Постоянная D_const<1:12> равна оцифрованному значению разности Vref - Vout(T1) (максимальное отклонение Vout с температурой), T1 - крайняя точка в рассматриваемом диапазоне (или -40 или 100 С), в которой выходное напряжение принимает минимальное значение. Например, в данной схеме производят вычет из 12-ти разрядного двоичного числа st<1:12> постоянной D_const<1:12> = b’000000111000, что соответствует изменению Vout примерно на 1.5 мВ. Этот шаг нужен для следующих стадий калибровки, на которых происходит подстройка выходного напряжения в крайних точках (Vout(-40)\Vout(100)) к опорному Vref. Так же в памяти сохраняют состояние регистра управления (биты отвечающие за стадию калибровки). Для схемы ИОН с увеличенным порядком температурной компенсации (график зависимости выходного напряжения от температуры имеет форму синусоиды) за счет определенного выбора площадей диодов (образованных эмиттерными переходами PNP транзисторами BJT1 и BJT2) и номиналов резисторов R0 и Rp, не требуется отнимать от st<1:12> постоянную величину D_const<1:12>, поскольку выходное напряжение в крайних точках и в середине после калибровки совпадают Vout(T1) = Vout(T0).

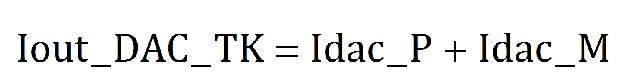

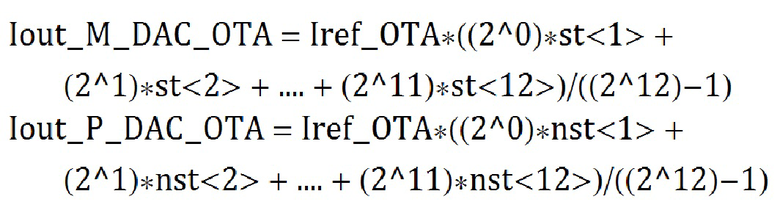

При изменении температурного коэффициента фиксированного напряжения базы происходит смещение точки максимума графика температурной зависимости выходного напряжения от центральной точки, при этом значение Vout в точке T0 не изменяется (что является вторым ключевым моментом в схеме калибровки, Фиг. 4). Схема смещения базы включает нагрузочный низкоомный резистор Rt и блок CTK (Фиг. 2 - 3), выполняющий функцию цифро-аналогового преобразования входного кода в температурный коэффициент выходного тока Iout_DAC_TK с помощью сдвоенного 8-битного ЦАП (DAC_TK) на базе двоично-взвешенных выходных токов блока SAD (Scalable adder of currents) Ip_TK и Im_TK в составе блока CTK (Фиг. 5 - 7). Блок SAD содержит масштабируемые сумматоры токов с противоположными по знаку температурными коэффициентами (от источников I_PTAT и I_CTAT) для увеличения и точной подстройки температурного коэффициента и значений выходных токов. Выходные токи блока SAD Ip_TK и Im_TK в первом приближении устанавливают одинаковыми по величине и с равными по модулю и противоположными по знаку температурного коэффициента, отражаясь в токовом зеркале с двоично-взвешенными коэффициентами ЦАП (DAC_TK) суммируются на выходе. Входной цифровой код tk<1:8> ЦАП (DAC_TK) устанавливает комбинации открытых и закрытых ключей двоично-взвешенных источников тока, определяя вклады Ip_TK и Im_TK в выходной суммарный ток Iout_DAC_TK и, следовательно, его температурный коэффициент, изменяющийся от отрицательного (все нули на входе ЦАП (DAC_TK)) к положительному (все единицы на входе ЦАП (DAC_TK)). Суммарный ток Iout_DAC_TK = Idac_P + Idac_M при температуре T0 остается постоянным во всем диапазоне входного цифрового кода. Передаточная характеристика блока CTK, определяемая как функция температурного коэффициента выходного тока Iout_DAC_TK от входного цифрового кода tk<1:8>, из-за не нулевого температурного коэффициента резистора Rt должна иметь постоянное смещение, чтобы графики зависимости выходного напряжения Vout(T) ИОН от температуры при всех нулях и при всех единицах кода tk<1:8> были полностью симметричны относительно оси ординат (Фиг. 4), при этом температурный коэффициент выходного тока Iout_DAC_TK не равен нулю в середине шкалы кода tk<1:8>.

На второй стадии калибровки кристалл охлаждают до минимальной температуры (вторая точка, -40 С), происходит подстройка выходного напряжения Vout(-40) изменением температурного коэффициента выходного тока ЦАП (DAC_TK) к внешнему опорному Vref и сохранение в памяти кода ключей подстроечного ЦАП (DAC_TK) и состояния регистра управления. При этом состояние ключей подстроечного ЦАП (DAC_OTA) установлено st_d<1:12>, а для схемы ИОН с увеличенным порядком температурной компенсации st<1:12>. На третьей стадии калибровки кристалл нагревают до максимальной температуры (третья точка, 100 С), происходит перекрестное переключение входов компаратора (изменение состояния управляющих ключами инверсных сигналов P1 (1->0) и not_P1 (0->1), рис. 1) и затем подстройка выходного напряжения Vout(100) к внешнему опорному Vref изменением температурного коэффициента выходного тока ЦАП (DAC_TK). Рассчитывают среднее значение (в цифровой части схемы) из кодов, полученных на второй и третьей стадиях, усредненный код ключей подстроечного ЦАП (DAC_TK) сохраняют вместе с состоянием регистра управления в памяти. После второй и третьей стадий калибровки состояние ключей подстроечного ЦАП (DAC_OTA) можно установить st<1:12> вместо st_d<1:12>, в случае если требуется равенство выходного потенциала Vout в точке T0 и опорного напряжения Vref (иначе опорное напряжение в крайней точке Vout(T1) = Vref, а Vout(T0) > Vout(T1) приблизительно на 1.5 мВ). Калибровка на этом заканчивается.

Можно использовать только одну крайнюю точку, без усреднения (калибровка по двум точкам), упрощается алгоритм и схема калибровки, но разброс выходного напряжения больше.

На Фиг. 11 представлены семейства графиков выходного напряжения Vout(T) в рассматриваемом диапазоне температур [-40, 100] схемы заявленного источника опорного напряжения (под PDK TSMC90nm) после калибровки, полученные в ходе статистического анализа MonteCarlo Process + Mismatch 60 Trials (учитывают все вышеописанные дестабилизирующие факторы при моделировании схемы на транзисторном уровне).

Для схемы заявленного источника опорного напряжения (под PDK TSMC 90 nm) с увеличенным порядком температурной компенсации за счет определенного выбора площадей диодов (образованных эмиттерными переходами PNP транзисторами BJT1 и BJT2) и номиналов резисторов R0 и Rp на Фиг. 12 представлены семейства графиков выходного напряжения Vout(T) в рассматриваемом диапазоне температур [-40, 100] после калибровки, полученные в ходе статистического анализа MonteCarlo Process + Mismatch 60 Trials (учитывают все вышеописанные дестабилизирующие факторы при моделировании схемы на транзисторном уровне).

Заявленный источник опорного напряжения с калибровкой выходного напряжения (Фиг. 1) содержит цифровой блок 3 (Digital Part) и аналоговый блок. Аналоговый блок содержит ИОН 1 типа bandgap (Bandgap Core with Trimming Array), компаратор 4 (Comparator) и генератор 5 тактовых импульсов (OSC). Цифровой блок 3 содержит схему управления 6 (Control Circuit), регистр 7 последовательного приближения (SAR), память 2 (Memory) и цифровую схему упрощенного арифметико-логического устройства (которая входит в состав схемы управления 6). Все блоки стандартные, за исключением ключевого аналогового блока ИОН 1 типа bandgap (Фиг. 2 - 3). Основная новизна заявленного изобретения заключается в конструкции блока ИОН 1 типа bandgap и в алгоритме калибровки выходного напряжения.

Рассмотрим более подробно функционирование блоков заявленного источника опорного напряжения с калибровкой выходного напряжения (Фиг. 2 – 10.)

Рассмотрим функционирование блока ИОН 1 типа bandgap (Фиг. 2 - 3). ИОН 1 типа bandgap содержит два биполярных транзистора BJT1 и BJT2 с соотношением площадей p-n перехода эмиттер-база 1 : M (где M = 8) соответственно; схему смещения базы биполярных транзисторов, состоящую из блока СTK с токовым выходом, подключенным к узлу базы транзисторов (узел VB) и нагрузочным низкоомным резистором Rt; емкостные нагрузки C1, C2 и C3; два источника тока на P-канальных транзисторах P1 и P2; источник тока управляемый напряжением (ИТУН) (OTA_TR) с подстройкой смещения в петле обратной связи. Сток транзистора P2 подключен к прямому входу ИТУН (узел VP). Сток транзистора P1 (опорное напряжение ИОН 1 типа bandgap - Vout) через резистор Rp подключен к инверсному входу ИТУН (узел VM). Выходное напряжение ИТУН (узел VA) управляет затворами транзисторов P1 и P2. Токозадающий резистор R0 подключен между эмиттером биполярного транзистора BJT2 и стоком P-канального транзистора P2 (узел VP, прямой вход ИТУН). Резистор Rp (выполненный в виде сборки из последовательно соединенных резисторов – R1, R2, R3, R4, R5, R6) подключен между эмиттером биполярного транзистора BJT1 и стоком P-канального транзистора P1 (узел VM, инверсный вход ИТУН) для установки термостабильного выходного напряжения схемы ИОН 1 типа bandgap. Конденсаторы C3 и C1 подключены между землей и выходными узлами ИОН 1 типа bandgap и ИТУН (Vout и VA) соответственно. В схеме ИОН 1 типа bandgap резисторы R0 – R6 одного типа, резистор Rt может быть другого типа, но в рассматриваемом варианте изобретения резистор Rt на основе поликремния, как и резисторы R0 – R6.

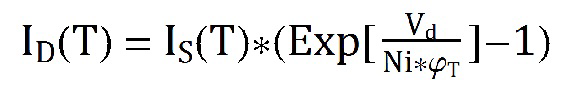

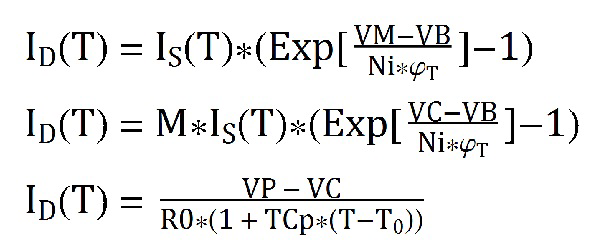

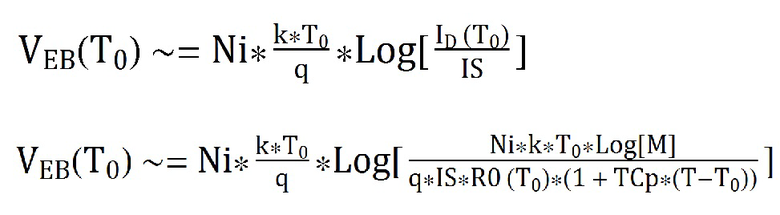

Переход эмиттер-база PNP биполярных транзисторов имеет достаточно большую площадь, и сопротивлением RS квазинейтральной области базы, эмиттера и коллектора можно пренебречь. Поэтому ток через переход эмиттер-база можно представить как прямой ток идеального диода:

где ток насыщения:

Ni - emmision coefficient (junction diode parameters), коэффициент не идеальности,

XTI - (saturation current temperature exponent) коэффициент, учитывающий температурную зависимость тока насыщения,

EG - ширина запрещенной зоны (в данных расчетах не зависит от температуры),

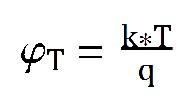

тепловой потенциал:

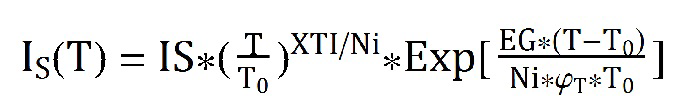

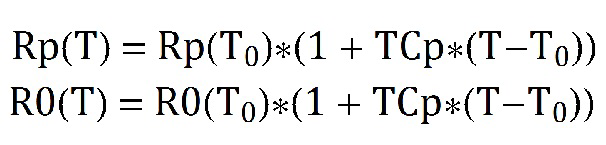

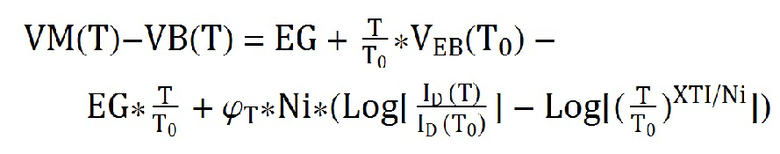

Поскольку резисторы Rp и R0 одного типа, они имеют одинаковый температурный коэффициент TCp:

В петле обратной связи в составе ИОН 1 типа bandgap разность входных напряжений ИТУН OTA_TR (VP и VM) стремится к нулю и устанавливается с точностью приведенного ко входу смещения ИТУН. В случае одинаковых транзисторов P1 и P2 (без учета разброса топологии, порога и подзатворного окисла) получаем равные токи в биполярных транзисторах:

с учетом VP ~= VM

Ток в схеме ИОН 1 типа bandgap прямо пропорционален абсолютной температуре и не зависит от напряжения базы VB.

Напряжение на переходе эмиттер-база BJT1:

с учетом выражения

где TCb - подстроечный температурный коэффициент базы,

VB0 - постоянная величина (не изменяется в ходе подстройки),

и напряжение на переходе эмиттер-база BJT при температуре T = T0:

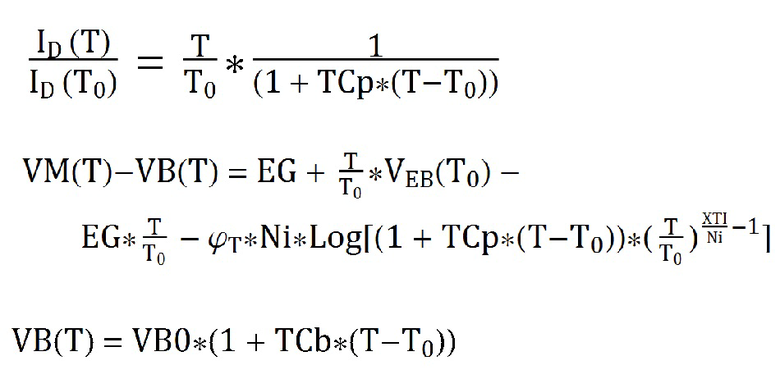

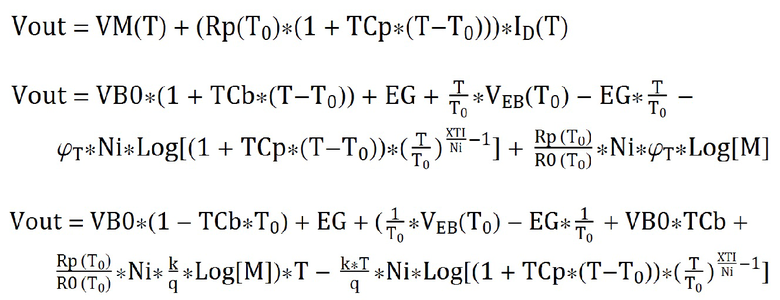

Выходное напряжение ИОН типа bandgap:

Условие для температурной компенсации в виде системы уравнений:

Где б - некоторая константа (определяется параметрами модели транзистора, температурным коэффициентом резистора и константами: Ni, XTI, TCp, k, q).

Из второго уравнения получаем:

Параметры Ni, XTI, IS, соотношение площадей p-n перехода M, а, следовательно, и константа б и VEB(T0), подвержены отклонению в ходе изготовления пластины от средних значений. Так же изменяются номиналы резисторов Rp и R0 в следствии разброса топологических параметров (ширины и длины W, L). Поэтому для температурной компенсации необходимо подстройка.

Из выведенных уравнений для определенного набора параметров Ni, XTI, IS и M можно получить необходимое для температурной стабильности Vout соотношение резисторов Rp и R0 подстройкой величины VB0*TCb.

Выходное напряжение ИОН 1 типа bandgap при температуре T0 не изменяется с подстройкой TCb:

но зависит от величины VB0 (на Фиг. 4 представлены графики функции Vout(T) при различных значениях TCb).

Из полученной системы уравнений следует, что при использовании данной схемы при правильном подборе номиналов (в данном случае после калибровки) резисторов можно получить первый порядок температурной компенсации, график зависимости выходного напряжения от температуры будет иметь форму параболы.

Если в схеме ИОН 1 типа bandgap уменьшить площади диодов (образованных эмиттерными переходами PNP транзисторами BJT1 и BJT2) до величины порядка 1мкм, то сопротивление квазинейтральной области базы RS с температурным коэффициентом TS станет соизмеримо с токозадающим сопротивлением R0. При этом если температурные коэффициенты резисторов R0 и RS (TCp и TS соответственно) отличаются хотя бы в 1.5 раза или на знак, что определяется технологией изготовления кристалла (имеет место в моделях PDK TSMC 90 nm), то при правильном подборе номиналов резисторов R0 и Rp можно увеличить порядок температурной компенсации, график зависимости выходного напряжения от температуры в данном случае будет иметь форму синусоиды.

Рассмотрим функционирование блока преобразования кода в температурный коэффициент выходного тока (блок управления температурным коэффициентом - CTK) (Фиг. 5 - 7). Блок CTK с помощью входного кода входным кодом подстраивает температурный коэффициент (в широком диапазоне [-0.013117, +0.012477] в данной схеме) выходного фиксированного при температуре T0 тока. Блок CTK содержит следующие блоки: I_PTAT (опорный источник тока, пропорционального абсолютной температуре, Фиг. 5), I_CTAT (опорный источник тока, обратно пропорционального абсолютной температуре, Фиг. 5), SAD (масштабируемые сумматоры токов, Фиг. 6) с инверсией для увеличения и точной подстройки температурного коэффициента выходного тока и DAC_TK (сдвоенный восьмиразрядный ЦАП с токовым выходом, Фиг. 7), образующий с сумматорами токов токовое зеркало.

Рассмотрим функционирование опорных источников тока (I_PTAT и I_CTAT), входящих в состав блока CTK (Фиг. 5).

Опорный источник тока, пропорционального абсолютной температуре (I_PTAT) (Фиг. 5), содержит два биполярных транзистора (BJT4 и BJT3) с соотношением площадей p-n перехода эмиттер-база 1 : M (где M = 8) соответственно, токозадающий резистор R9, подключенный к эмиттеру транзистора BJT3, токовое зеркало на P-канальных транзисторах P3 (в диодном включении) и P4. Для уравнивания напряжения эмиттера BJT4 и напряжения второго узла токозадающего резистора R9 (первый узел - эмиттер BJT3) вместо ИТУН используют пару N-канальных транзисторов N1 и N2 (последний в диодном включении с дополнительной емкостью C4 на затворе), чтобы упростить схему, поскольку в данном случае использование ИТУН избыточно (требования к схеме I_PTAT в сравнении с общей схемой ИОН существенно ниже). Ток в схеме опорного источника тока, пропорционального абсолютной температуре (I_PTAT):

Опорный источник тока, в первом приближении обратно пропорционального абсолютной температуре (зависимость нелинейная) (блок I_PTAT и I_CTAT) (Фиг. 5) содержит p-канальный транзистор P5, образующий токовое зеркало 1 : 1 с транзистором в диодном включении P3 блока I_PTAT; n-канальные транзисторы N3 (в диодном включении с дополнительной емкостью C5 на затворе) и N5, образующие токовое зеркало 1 : 1, затвор N3 соединен со стоком P5, ток N5 равен I_PTAT; биполярный транзистор BJT5 в петле отрицательной обратной связи (ООС), коллектор подключен к стоку N5, режимный ток устанавливается равным I_PTAT, поэтому напряжения коллектора и базы в первом приближении зависят от температуры обратно пропорционально; петля ООС для формирования тока I_CTAT, включающая p-канальный токозадающий транзистор P6 (создает ток I_CTAT), затвор которого подключен к коллектору BJT5; n-канальные транзисторы N6 и N4 (в диодном включении, сток подключен к стоку P6), образующие токовое зеркало 1 : 1, отражая ток I_CTAT в резистивную нагрузку (сборка из последовательно включенных резисторов R10 и R11) между стоком N6 (подключенным к базе BJT5, замыкая петлю ООС) и питанием.

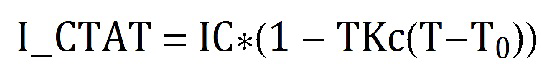

Ток в схеме опорного источника тока, обратно пропорционального абсолютной температуре (блок I_PTAT и I_CTAT):

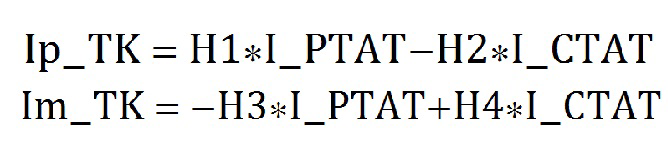

Рассмотрим функционирование блока SAD, входящего в состав блока управления температурным коэффициентом (CTK). Блок SAD (Фиг. 6) состоит из двух токовых усилителей, выполненных на транзисторах <N8-N10,N15,P8,P9,P14,P15> и <N11-N14,P10-P13>, усиливающих разность входных токов от источников I_PTAT и I_CTAT, при этом формирующих выходные токи:

соответственно (H1-H4 - коэффициенты, задаются топологией транзисторов в составе блока).

<N8-N10,N15,P8,P9,P14,P15> :

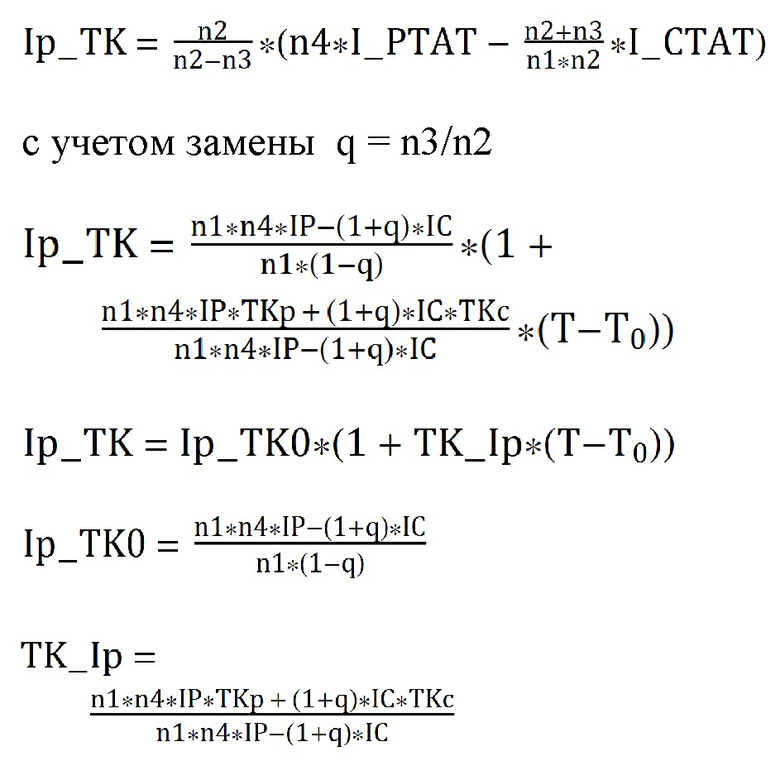

Выходной ток источника I_CTAT отражается в токовом зеркале n1 : 1 (n1 = 3) на n-канальных транзисторах N4 и N7, где N4 в диодном включении (затвор соединен со стоком), истоки транзисторов на земле. Ток N7 и p-канального транзистора P7 равен I_CTAT/n1. Транзистор P7 в диодном включении (затвор соединен со стоком) с P8 образуют токовое зеркало 1 : 1 (истоки транзисторов на питании), поэтому ток транзистора P8 и нагрузочного n-канального N8 равен I_CTAT/n1. Транзистор N8 в диодном включении (затвор соединен со стоком) и транзистор N9 образуют токовое зеркало (истоки на земле) n2 : (n2+n3) (где n2 = 8, n3 = 2, n3 < n2), ток N9 равен (n2+n3)*I_CTAT/(n1*n2). Тр-р P3 в диодном включении (затвор соединен со стоком) в составе блока I_PTAT и тр-р P9 образуют токовое зеркало 1 : n4 (где n4 = 2), ток транзистора P9 устанавливается n4*I_PTAT и равен сумме токов транзисторов N9 и N10 в диодном включении (стоки N9, N10, P9 и затвор N10 - один узел схемы). Транзистор N10 в диодном включении (затвор соединен со стоком) и тр-р N15 образуют токовое зеркало (истоки на земле) (n2-n3):n2, выходной ток N15:

Знаменатель TK_Ip равный числителю амплитуды тока n1*n4*IP-(1+q)*IC устанавливаем коэффициентом q (q < 1) и n1*n4 (остальные параметры в выражении TK_Ip постоянные) для достижения требуемой величины TK_Ip. Для установки амплитуды тока изменяем n1 при фиксированном значении n4*n1 и q, при этом TK_Ip остается постоянным.

<N11-N14,P10-P13> :

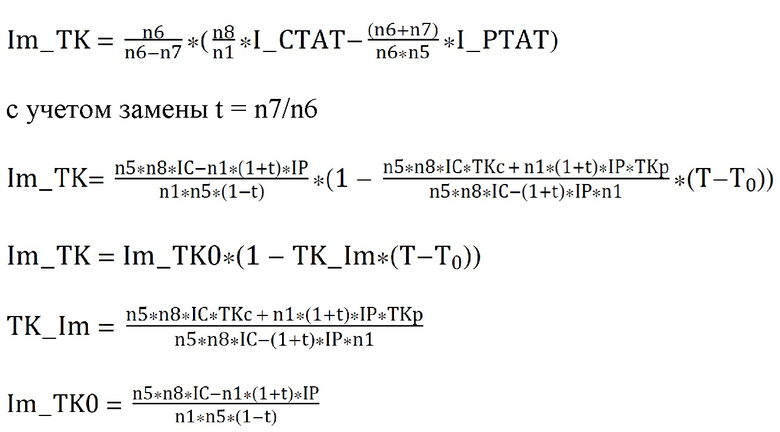

Транзистор P3 в диодном включении (затвор соединен со стоком) в составе блока I_PTAT и транзистор P10 образуют токовое зеркало n5:1 (n5 = 1), ток транзистора P10 устанавливается I_PTAT/n5 и равен току транзистора N11. Транзистор N11 в диодном включении (затвор соединен со стоком) и транзистор N12 образуют токовое зеркало (истоки на земле) n6 : (n6+n7) (где n6 = 8, n7 = 3, n7 < n6), ток N12 равен (n6+n7)/(n6*n5)*I_PTAT. Транзистор P7 в диодном включении (затвор соединен со стоком) с P11 образуют токовое зеркало 1 : n8 (где n8 = 2) (истоки транзисторов на питании), поэтому ток тр-ра P11 устанавливается n8*I_CTAT/n1 и равен сумме токов тр-ра N12 и N13 в диодном включении (стоки N12, N13, P11 и затвор N10 - один узел схемы). Транзистор N13 в диодном включении (затвор соединен со стоком) и транзистор N14 образуют токовое зеркало (истоки на земле) (n6-n7) : n6, выходной ток N14:

Знаменатель TK_Im равный числителю амплитуды тока n5*n8*IC-(1+t)*IP устанавливаем коэффициентом t (t < 1) и n5*n8 (остальные параметры в выражении TK_Im постоянные) для достижения требуемой величины TK_Im. Для установки амплитуды тока изменяем n5 при фиксированном значении n8*n5 и t, при этом TK_Im остается постоянным.

В частном случае (в представленной схеме):

I_PTAT(T0) = IP = 13.81e-6

I_CTAT(T0) = IС = 41.3e-6

TKp = 0.0038

TKc = 0.00145

TK_Ip = 0.012477

Ip_TK0 = 13.88e-6

TK_Im = 0.013117

Im_TK0 = 13.67e-6

У выходного тока Ip_TK в сравнении с I_PTAT сохраняется амплитуда при T0, а температурный коэффициент увеличивается в 3.28 раз.

У выходного тока Im_TK в сравнении с I_CTAT уменьшается амплитуда при T0 (выравнивается с амплитудой тока I_PTAT), а температурный коэффициент увеличивается в 9.04 раз.

Рассмотрим функционирование блока DAC_TK, входящего в состав управления температурным коэффициентом (СTK). Блок DAC_TK состоит из двух ЦАП (восемь разрядов в данном варианте изобретения, Фиг. 7) с токовыми выходами (Idac_P и Idac_M), выходной ток DAC_TK (и всего блока CTK):

Токи Idac_P и Idac_M равны сумме двоично-взвешенных источников тока, формируемыми токозадающими и каскодными транзисторами <P18/P19,P22/P23,P26/P27,P30/P31,P34/P35,P38/P39,P42/P43,P46/P47> и <P16/P17,P20/P21,P24/P25,P28/P29,P32/P33,P36/P37,P40/P41,P44/P45> соответственно, которые образуют токовое зеркало с транзисторами в диодном включении из блока SAD <P14/P15> и <P12/P13> соответственно. Ключи <S1/S2,S3/S4,S5/S6,S7/S8,S9/S10,S11/S12,S13/S14,S15/S16> управляются противофазными сигналами tk<8>/ntk<8>,tk<7>/ntk<7>,...,tk<2>/ntk<2>,tk<1>/ntk<1> соответственно (tk<i> = NOT(ntk<i>), i = (1,8), tk<i> = 1\0 - ключ открыт\закрыт; токи противофазных ключей (S1/S2,S3/S4,...,S15/S16) в блоке DAC_TK равны при комнатной температуре T0 и с одинаковым по модулю, но разным по знаку температурным коэффициентом.

Цифровой код tk<1:8> устанавливает отношение токов Idac_P и Idac_M, при этом величина выходного тока Iout_DAC _TK при комнатной температуре остается постоянной при любой комбинации tk<1:8>, изменяется только температурный коэффициент выходного тока (в широком диапазоне ~[-0.012, 0.012]).

Температурные коэффициенты TK_Ip\TK_Im и амплитуды токов Ip_TK\Im_TK соответственно в блоке SAD подбирают таким образом, чтобы графики температурной зависимости выходного напряжения Vout(T) схемы ИОН 1 типа bandgap при всех единицах и при всех нулях управляющих сигналах tk<1:8> были симметричными (Фиг. 4).

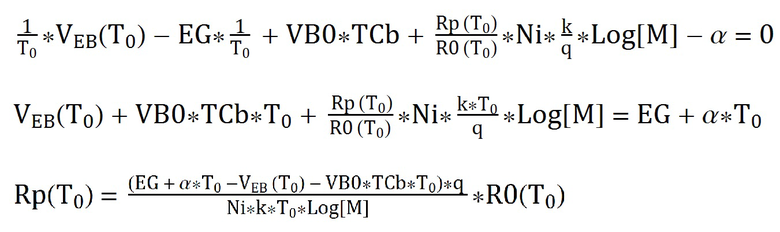

Рассмотрим функционирование ИТУН (OTA_TR) и схемы подстройки смещения. Схема ИТУН (Фиг. 8) стандартная - изогнутый каскод (из-за требования низкого входного синфазного напряжения) без P-канальных каскодных транзисторов. В таком исполнении схема ИОН 1 типа bandgap менее чувствительна к рассогласованию параметров симметричных транзисторов ИТУН.

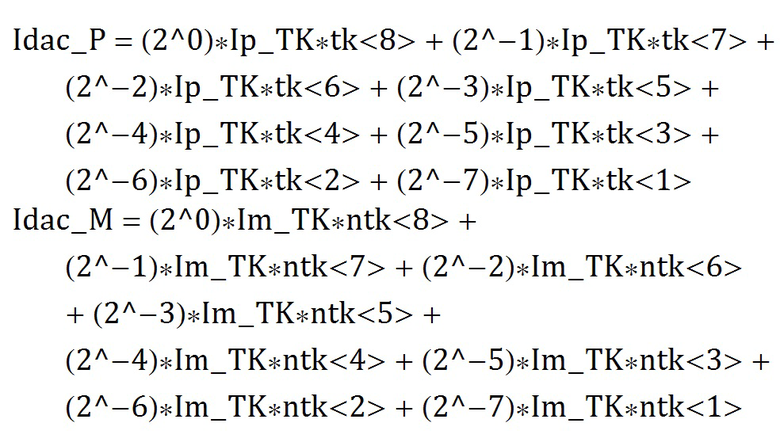

Схема подстройки смещения ИТУН (CVOS, Фиг. 9) включает дифференциальную пару с P-канальными транзисторами Pd1 и Pd2 (подложка каждого тр-ра соединена с истоком), истоки которых разделены резистором Rd с температурным коэффициентом TC и два подстраиваемых источника тока (Iout_M и Iout_P) с температурным коэффициентом TI, подключенных к истокам транзисторов диф.пары.

Выходные токи подстраиваемых источников тока (Iout_M и Iout_P) равны сумме выходных токов подстроечного ЦАП DAC_OTA (Iout_M_DAC_OTA и Iout_P_DAC_OTA) на базе двоично-взвешенных источников тока (схема DAC_OTA стандартная) и двух одинаковых источников тока (0.5*k*I0*(1 + TI*(T-T0))) с температурным коэффициентом TI, формируемыми токозадающими или каскодными транзисторами <P60\P61> и <P62\P63> соответственно в составе токового зеркала с транзисторами <N16-N21, P48-P51> источника опорного тока блока ИТУН (0.5*I0*(1 + TI*(T-T0))).

Стоки каскодных транзисторов P61 и P63 подключены к истокам входных транзисторов диф. пары Pd1 и Pd2 и к выходным узлам подстроечного ЦАП. Стоки токозадающих транзисторов P60 и P62 соединены с истоками каскодных P61 и P63 соответственно.

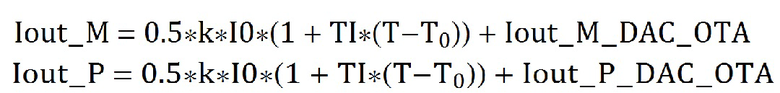

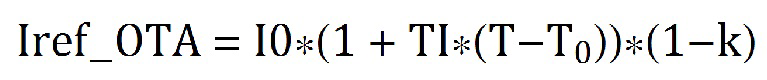

Выходные токи ЦАП (DAC_OTA, разрядность 12 бит в данной схеме):

формируют токозадающими и каскодными транзисторами в составе токового зеркала источника опорного тока блока ИТУН (0.5*I0*(1 + TI*(T-T0))), где

Cигналы в противофазе st<12>/nst<12>,st<11>/nst<11>,....,st<1>/nst<1> управляют парами параллельно включенных ключей на каждом двоично-взвешенном источнике тока в составе ЦАП (nst<i> = NOT[st<i>]), i = (1,12), st<i> = 1\0 - ключ открыт\закрыт. Максимальное значение Iout_M_DAC_OTA при всех открытых ключах (st<1> = st<2> = ... = st<12> = 1) составляет I0*(1 + TI*(T-T0))*(1-k), при этом Iout_P_DAC_OTA = 0 (nst<1> = nst<2> = ... = nst<12> = 0). И наоборот, максимальное значение Iout_P_DAC_OTA при всех открытых ключах (nst<1> = nst<2> = ... = nst<12> = 1) составляет I0*(1 + TI*(T-T0))*(1-k), при этом Iout_M_DAC_OTA = 0 (st<1> = st<2> = ... = st<12> = 0).

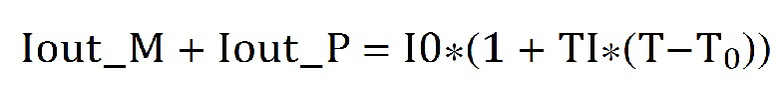

Суммарный ток при заданной температуре - постоянная величина:

при любом значении коэффициента k в диапазоне (0:1). Коэффициент k задает разбаланс ДI токов Iout_M и Iout_P, определяя диапазон подстройки смещения ИТУН. В данной схеме k = 0.5, при этом диапазон изменения выходного напряжения заявленного источника опорного напряжения с калибровкой выходного напряжения составляет около 100 мВ.

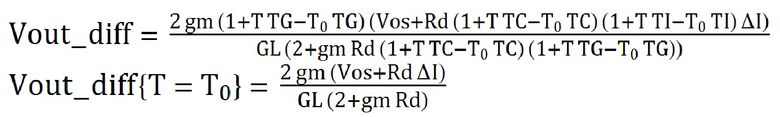

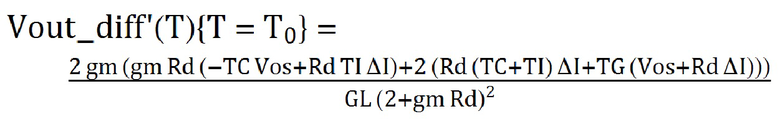

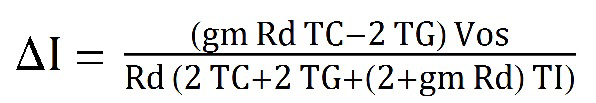

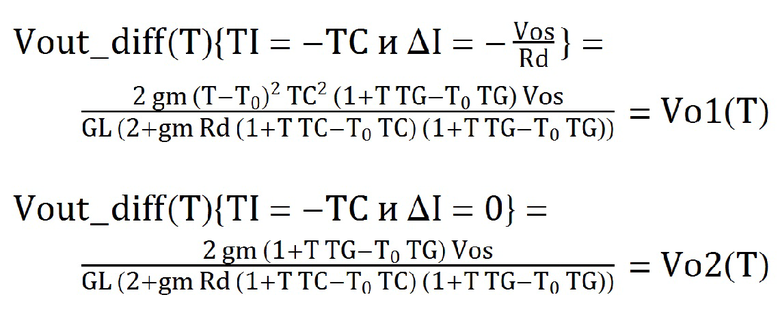

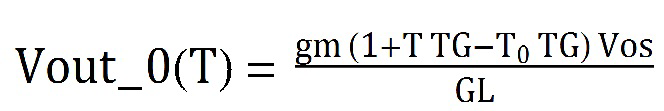

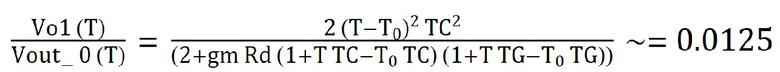

Если рассмотреть отдельно от ИТУН подстроечную дифференциальную пару (Фиг. 10) с недифференциальной нагрузкой 1/GL (2 резистора RL1 и RL2, подключенные к стокам входных транзисторов диф. пары и к земле), при этом TI\TG\TC - температурные коэффициенты источника тока и подстроечного ЦАП, входных транзисторов диф. пары, резистора между истоками транзисторов диф. пары соответственно.

ДI - разбаланс источников токов, вводимый подстроечным ЦАП для компенсации напряжения смещения Vos, приведенного к одному из входов диф. пары.

Тогда

Для компенсации при комнатной температуре: ДI = - (Vos/Rd) ==> Vout{T = T0} = 0

Производная от функции Vout_diff(T) в точке T = T0:

При Vout_diff '(T){T = T0} = 0 получаем

ДI = - (Vos/Rd) ==> TI = -TC

То есть температурные коэффициенты источника тока и резистора должны быть равны по модулю и противоположны по знаку.

Напряжение на выходе при 2-х значениях ДI:

Для сравнения

- без схемы подстройки (обычная дифференциальная пара).

Из полученных формул видно, что напряжение смещения на выходе в схеме с подстройкой подавляется приблизительно в 80 раз в наихудшем случае при крайней температуре T = 374 K с учетом TC = 1.53e-3, Rd = 400 Ом, gm = 0.11e-3 См и TG = 1e-6:

и коэффициент передачи схемы с подстройкой уменьшается (если сравнивать с обычной диф. парой) за счет резистора Rd на небольшую величину в процентах:

Данную схему можно использовать как для компенсации смещения ИТУН, так и для ввода дополнительного смещения ИТУН при подстройке выходного напряжения заявленного источника опорного напряжения с калибровкой выходного напряжения к внешнему опорному напряжению (используется в заявленном изобретении). При этом диапазон подстройки определяется максимальным значением разбаланса ДI, либо при всех единицах, либо при всех нулях на входе подстроечного ЦАП (DAC_OTA).

В заявленном изобретении калибровка выходного напряжения направлена на выравнивание кривой зависимости выходного напряжения от температуры, как в схеме ИОН с тримменгом, но сам процесс при этом автоматический, как в схеме ИОН с калибровкой. Преимущество заявленного изобретения по сравнению с первым прототипом - автоматический процесс подстройки, по сравнению со вторым прототипом - стабильность выходного напряжения (которая соизмерима со стабильностью первого прототипа).

Заявленное изобретение отличается от прототипов, во-первых, наличием в составе ИОН 1 типа bandgap блока СTK с нагрузочным резистором Rt (Фиг. 2-3) и, во-вторых, схемой источника тока управляемого напряжением (ИТУН) (OTA_TR) с подстройкой смещения, выполняемой блоком CVOS, входящим в состав блока OTA_TR (см. фиг. 8-9). Блоки СTK и CVOS выполняют функции на стадиях калибровки. Цифровой код на входе блока CVOS изменяет смещение блока OTA_TR при рабочей температуре, за счет чего происходит подстройка выходного напряжения ИОН к внешнему опорному напряжению Vref. Блок CTK подстраивает температурный коэффициент базы биполярных транзисторов в диодном включении BJT1 и BJT2 при рабочей температуре в схеме ИОН для выравнивания графика температурной зависимости выходного напряжения. Блоки CVOS и CTK задают алгоритм калибровки, который включает две или три стадии в зависимости от требований к температурной стабильности.

Отличительные особенности заявленного изобретения - это стабильное выходное напряжение Vout после калибровки (минимальный уход Vout от температуры, минимальный уход Vout при заданной температуре в зависимости от образцов и партии изготовления ИОН) и автоматический процесс подстройки регулируемых элементов в схеме ИОН. Диапазон изменения выходного напряжения заявленного ИОН составляет порядка 2 мВ (Фиг. 11) и порядка 1 мВ (Фиг. 12) в схеме ИОН с увеличенным порядком температурной компенсации за счет определенного выбора площадей диодов (образованных эмиттерными переходами PNP транзисторами BJT1 и BJT2) и номиналов резисторов R0 и Rp. Схема заявленного ИОН спроектирована под технологический процесс TSMC 90nm.

Хотя описанный выше вариант выполнения изобретения был изложен с целью иллюстрации заявленного изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла заявленного изобретения, раскрытого в прилагаемой формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Малошумящий источник опорного напряжения | 2023 |

|

RU2813175C1 |

| НИЗКОВОЛЬТНЫЙ ТЕМПЕРАТУРНО СТАБИЛЬНЫЙ РАДИАЦИОННО СТОЙКИЙ ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2013 |

|

RU2517683C1 |

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2013 |

|

RU2568323C2 |

| Источник опорного напряжения | 1983 |

|

SU1108415A1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2012 |

|

RU2473951C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2012 |

|

RU2523956C2 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ НА ОСНОВЕ МАТРИЦЫ БОЛОМЕТРИЧЕСКИХ ДЕТЕКТОРОВ СО СХЕМОЙ КОМПЕНСАЦИИ НЕОДНОРОДНОСТИ, УЧИТЫВАЮЩЕЙ ЭФФЕКТ САМОРАЗОГРЕВА | 2020 |

|

RU2745484C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2012 |

|

RU2475807C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2013 |

|

RU2525745C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2447477C1 |

Изобретение относится к области электротехники, в частности к источникам опорного напряжения. Технический результат заключается в создании источника опорного напряжения с калибровкой выходного напряжения с улучшенными эксплуатационными характеристиками, а именно со стабильным выходным напряжением после калибровки и автоматическим процессом подстройки регулируемых элементов. Достигается за счет наличия схемы смещения базы биполярных транзисторов, состоящей из блока управления температурным коэффициентом, осуществляющим преобразование цифрового кода в температурный коэффициент выходного тока, и нагрузочного резистора, подключенного между эмиттером и коллектором биполярных транзисторов, а также за счет наличия источника тока, управляемого напряжением, с подстройкой смещения, выполняемой блоком управления напряжением смещения, входящим в состав источника тока, управляемого напряжением. 3 з.п. ф-лы, 12 ил.

1. Источник опорного напряжения с калибровкой выходного напряжения, включающий цифровой и аналоговый блоки, причем аналоговый блок содержит соединенные между собой источник опорного напряжения (ИОН) типа bandgap, компаратор с перекрестными ключами на входе и генератор тактовых импульсов, а цифровой блок содержит регистр последовательного приближения, память и схему управления, включающую в себя цифровую схему упрощенного арифметико-логического устройства, при этом выходы компаратора и генератора тактовых импульсов соединены с входами цифрового блока, выходы которого соединены с входами управления перекрестных ключей на входе компаратора и с входом ИОН типа bandgap, отличающийся тем, что ИОН типа bandgap содержит источник тока, управляемый напряжением (OTA_TR), выполненный с возможностью подстройки смещения с помощью входящего в его состав блока управления напряжением смещения (CVOS), и схему смещения базы биполярных транзисторов BJT1 и BJT2, состоящую из блока управления температурным коэффициентом (СTK) напряжения базы биполярных транзисторов BJT1 и BJT2 с токовым выходом и нагрузочного резистора Rt, подключенного между эмиттером и коллектором биполярных транзисторов BJT1 и BJT2, входящих в состав ИОН типа bandgap, причем

- блок управления напряжением смещения (CVOS) источника тока, управляемого напряжением (OTA_TR), выполнен с возможностью изменения с помощью цифрового входного кода, смещения источника тока, управляемого напряжением (OTA_TR), и, следовательно, изменения выходного напряжения Vout ИОН типа bandgap в требуемом диапазоне, причем регистр последовательного приближения выполнен с возможностью формирования цифрового кода на входе блока управления напряжением смещения (CVOS) на соответствующей стадии калибровки, при этом уменьшения с каждым шагом разницы между выходным напряжением Vout ИОН типа bandgap и внешним опорным напряжением Vref в средней точке рабочего диапазона температур, при этом любое изменение смещения источника тока управляемого напряжением (OTA_TR) не влияет на кривизну температурной зависимости выходного напряжения Vout ИОН типа bandgap;

- блок управления температурным коэффициентом (СTK) потенциала базы биполярных транзисторов BJT1 и BJT2 выполнен с возможностью преобразования цифрового входного кода в температурный коэффициент выходного тока, и, следовательно, температурного коэффициента выходного напряжения Vout ИОН типа bandgap в требуемом диапазоне; регистр последовательного приближения выполнен с возможностью формирования цифрового кода на входе блока управления температурным коэффициентом (СTK) на соответствующей стадии калибровки, при этом с каждым шагом уменьшения разницы между внешним опорным напряжением Vref и выходным напряжением Vout ИОН типа bandgap в крайних точках рабочего диапазона температур, при этом выравнивания температурной зависимости выходного напряжения Vout ИОН типа bandgap, при постоянном и приблизительно равном Vref выходном напряжении Vout в средней точке рабочего диапазона температур;

- блок управления напряжением смещения (CVOS) и блок управления температурным коэффициентом (СTK) выполнены с возможностью определения алгоритма калибровки, содержащего от двух до трех стадий калибровки в зависимости от требований к температурной стабильности.

2. Источник опорного напряжения по п. 1, отличающийся тем, что источник тока, управляемого напряжением (OTA_TR), содержит блок управления напряжением смещения (CVOS), который выполнен с возможностью преобразования цифрового кода на входе в смещение источника тока, управляемого напряжением (OTA_TR), при этом величина смещения задается разностью токов транзисторов входной дифференциальной пары блока управления напряжением смещения (CVOS) при постоянном суммарном токе потребления источника тока, управляемого напряжением (OTA_TR), а разбаланс токов входной дифференциальной пары устанавливается цифроаналоговым преобразователем ЦАП на базе двоично-взвешенных источников тока с токовым выходом (DAC_OTA), входящих в состав блока CVOS.

3. Источник опорного напряжения по п. 1, отличающийся тем, что ИОН типа bandgap содержит блок управления температурным коэффициентом (СTK) с токовым выходом, подключенным к узлу базы биполярных транзисторов BJT1 и BJT2, и нагрузочный резистор Rt, подключенный между базой и эмиттером биполярных транзисторов BJT1 и BJT2, при этом блок управления температурным коэффициентом (СTK) выполнен с возможностью преобразования цифрового кода на входе в температурный коэффициент выходного тока и содержит:

- блок I_PTAT, выполненный с возможностью формирования опорного тока, пропорционального абсолютной температуре;

- блок I_CTAT, выполненный с возможностью формирования опорного тока, обратно пропорционального абсолютной температуре;

- блок SAD, выполненный с возможностью формирования двух токов одинаковой величины с равными по модулю и противоположными по знаку температурными коэффициентами;

- блок DAC_TK, выполненный с возможностью формирования выходного тока постоянной величины с температурным коэффициентом, задаваемым входным цифровым кодом.

4. Источник опорного напряжения по п. 1, отличающийся тем, что ИОН типа bandgap содержит два биполярных транзистора BJT1 и BJT2, блок управления температурным коэффициентом (CTK) с токовым выходом, подключенным к узлу базы биполярных транзисторов BJT1 и BJT2, нагрузочный низкоомный резистор Rt, подключенный между базой и эмиттером биполярных транзисторов BJT1 и BJT2, P-канальные транзисторы P1 и P2, источник тока, управляемый напряжением (OTA_TR), с подстройкой смещения, причем сток транзистора P2 подключен к прямому входу источника тока, управляемого напряжением (OTA_TR), сток транзистора P1 через резистор Rp подключен к инверсному входу источника тока, управляемого напряжением (OTA_TR), выходное напряжение источника тока, управляемого напряжением (OTA_TR), устанавливает потенциал затворов P-канальных транзисторов P1 и P2, токозадающий резистор R0 подключен между эмиттером биполярного транзистора BJT2 и стоком P-канального транзистора P2, резистор температурной компенсации Rp выполнен в виде сборки из последовательно соединенных резисторов R1, R2, R3, R4, R5, R6 и подключен между эмиттером биполярного транзистора BJT1 и стоком P-канального транзистора P1.

| ЭЛЕКТРОННАЯ ЧАСТЬ ПОЛЕВОГО УСТРОЙСТВА, ЗАПИТЫВАЕМАЯ ВНЕШНИМ ИСТОЧНИКОМ ЭЛЕКТРОЭНЕРГИИ | 2007 |

|

RU2414739C2 |

| Источник опорного напряжения | 1983 |

|

SU1108415A1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2013 |

|

RU2523121C1 |

| Шпаговый манипулятор | 1963 |

|

SU172597A1 |

| US 4703249 A1, 27.10.1987. | |||

Авторы

Даты

2020-02-26—Публикация

2019-10-21—Подача