Изобретение относится к области электроники и может быть применено в составе микросхем аналогово-цифровых и цифро-аналоговых преобразователей, аппаратуры радиосвязи и радиолокации, высокоточной измерительной аппаратуры, работающей в широком температурном диапазоне, требующей наличия прецизионных источников опорного напряжения с низким уровнем низкочастотных фликкер-шумов.

Известно, что типовым блоком для построения большинства цифровых и аналоговых систем по-прежнему остаются источники опорного напряжения (ИОН). В некоторых приложениях, таких как аналогово-цифровые и цифро-аналоговые преобразователи (АЦП и ЦАП), точность и шумовые характеристики ИОН зачастую оказываются решающими для производительности всей системы. Следует также отметить, что низкочастотные фликкер-шумы достаточно плохо поддаются фильтрации и значительно понизить их уровень получается только с использованием схемотехнических решений на биполярных транзисторах [1]. Получение низкого уровня низкочастотных фликкер-шумов и приемлемого технологического разброса для комплементарных металл-оксид-полупроводниковых (КМОП) устройств представляет весьма сложную задачу, которая зачастую приводит разработчиков к необходимости значительного увеличения площадей транзисторов.

Повсеместная цифровизация всех областей человеческой деятельности достаточно быстро привела к доминированию на рынке современных технологических процессов, ориентированных на производство КМОП. Ключевую роль здесь сыграли энергоэффективность цифровых схем на КМОП в сравнении с их биполярными аналогами, а также масштабируемость КМОП-процессов, что позволило значительно увеличить плотность упаковки цифровых элементов в схемах.

Необходимость использования всех типов транзисторов достаточно быстро привела к возникновению БиКМОП-технологий изготовления интегральных микросхем с использованием биполярных и КМОП-транзисторов на одном кристалле. Однако, получение приемлемых характеристик биполярных транзисторов с одновременным уменьшением технологической нормы по-прежнему остается нетривиальной задачей. Зачастую в данных технологиях лучшие характеристики имеют полевые транзисторы, что заставляет разработчиков использовать именно их для построения аналоговых схем.

Уменьшение фликкер-шумов КМОП-приборов путем увеличения их топологических размеров частично улучшает ситуацию [1], однако, размеры устройств становятся непригодными для их интеграции в сверхбольшие интегральные схемы (СБИС), и выигрыш от такого подхода в области низкочастотных шумов оказывается несущественным.

Достаточно интересным и популярным подходом к разработке малошумящих ИОН с использованием КМОП-приборов являются так называемые чопперные (chopper, прерыватель) решения [5,6,7]. Зарекомендовавшая себя технология устранения смещения нуля операционных усилителей [8] постепенно стала использоваться для уменьшения шумов ИОН [6,7]. Основная идея данной технологии заключается в стабилизации прерыванием. Входной сигнал коммутируется с определенной частотой, а на выходе происходит его обратное восстановление. Данный подход позволяет устранять эффекты несоответствия (mismatch-эффекты) внутренних приборов усилителя, а также уменьшать низкочастотные шумы схемы. Недостатком данной техники необходимо отметить высокие предъявляемые требования к топологии схемы. Наличие коммутируемых приборов, ключей, паразитных емкостей между сигнальными линиями, необходимость строгого соблюдения фазовых соотношений в применяемых режекторных фильтрах, превращают проектирование устройств с применением данной техники прерываний в достаточно трудоемкий процесс.

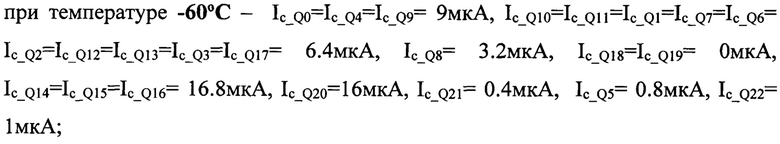

В настоящий момент классическим подходом к разработке ИОН является использование биполярных транзисторов в его ядре с последующей схемой компенсации температурной зависимости, выполненной на операционных усилителях и токовых зеркалах с использованием исключительно КМОП-приборов [1-4]. Типовая схема приведена на фиг.1. Данный подход приводит к достаточно высоким уровням низкочастотных шумов, поскольку введение КМОП-приборов увеличивает общий уровень низкочастотного шума схемы. Тем не менее, большая часть эталонных источников напряжения в интегральном исполнении разрабатывается именно по схеме на фиг.1, поскольку позволяет легко получать приемлемые характеристики в приложениях, нетребовательных к низкочастотным шумам. Фильтрация высокочастотных шумов обычно осуществляется при помощи, подключаемой к микросхеме, внешней емкости.

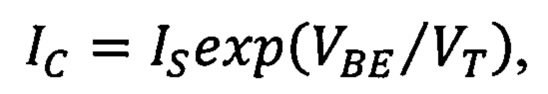

Формирование опорного напряжения в классическом варианте исполнения источника опорного напряжения происходит согласно описанной ниже схеме. Напряжение база-эмиттер VBE биполярных транзисторов или, в более общем случае, прямое напряжение диода с pn - переходом имеет отрицательный температурный коэффициент. Ток коллектора биполярного устройства равен

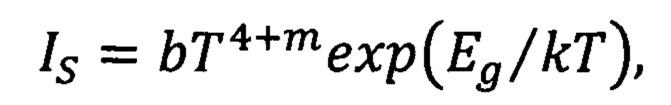

где VT=kT/q - тепловое напряжение, k=1.38⋅10-23 Дж/К - постоянная Больцмана, Т - температура в Кельвинах, q=-1.6⋅10-19 Кл - заряд электрона [1]. Ток насыщения равен

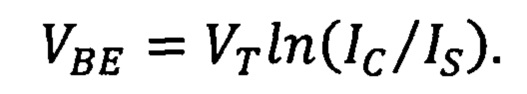

где Eg ≈ 1.12 эВ - ширина запрещенной зоны кремния m ≈ - 3/2 -степень зависимости от температуры, зависящая от технологии производства, b - некоторый коэффициент пропорциональности, зависящий от технологии производства. Напряжение база-эмиттер VBE имеет вид:

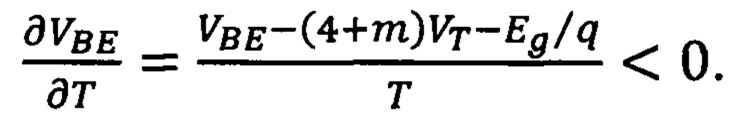

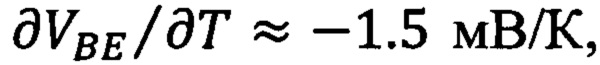

Первая частная производная по температуре от напряжения база-эмиттер VBE явно показывает отрицательный температурный коэффициент:

При  имеем

имеем  В старых биполярных технологиях

В старых биполярных технологиях

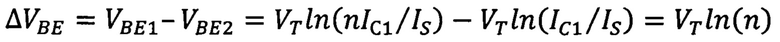

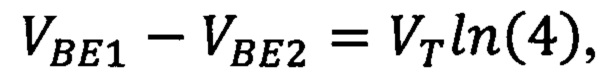

С другой стороны, [10] разница напряжений база-эмиттер двух биполярных транзисторов может иметь положительный температурный коэффициент. Пусть имеются два биполярных транзистора, которые работают при неравных плотностях тока. Плотность тока определяется как отношение тока коллектора IC и тока насыщения IS. Пусть два топологически идентичных транзистора имеют разные токи коллекторов IC1 и IC2=nIC1, где n некоторый коэффициент пропорциональности. Учитывая, что токи насыщения данных транзисторов идентичны IS1=IS2=IS. Тогда разница между их напряжениями база-эмиттер прямо пропорциональна абсолютной температуре

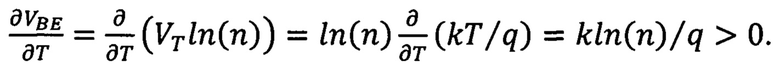

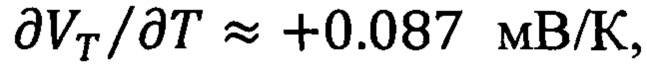

Первая частная производная показывает положительный температурный коэффициент

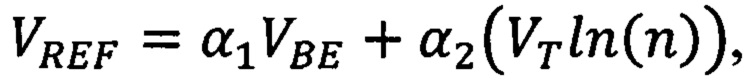

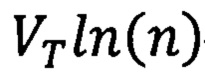

С полученными выше отрицательными и положительными температурными коэффициентами становится возможным разработать ИОН с номинально нулевым температурным коэффициентом. Обозначим эталонное напряжение с близким к нулю температурным коэффициентом на выходе ИОН как VREF. Для получения близкого к нулю температурного коэффициента достаточно сформировать эталонное напряжение

где  - разность между напряжениями база-эмиттер двух биполярных транзисторов, работающих при разных плотностях тока, а α1 и α2 некоторые коэффициенты масштабирования, которые необходимо сформировать, для выполнения предыдущего равенства.

- разность между напряжениями база-эмиттер двух биполярных транзисторов, работающих при разных плотностях тока, а α1 и α2 некоторые коэффициенты масштабирования, которые необходимо сформировать, для выполнения предыдущего равенства.

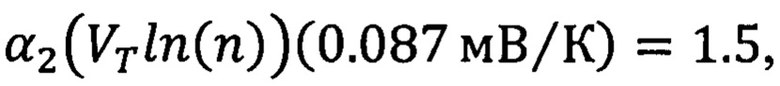

Поскольку при комнатной температуре  тогда как

тогда как  полагая α1=1 и выбирая

полагая α1=1 и выбирая  так, чтобы

так, чтобы  то есть

то есть  становится возможным получить нулевой температурный коэффициент, при котором эталонное напряжение VREF равно:

становится возможным получить нулевой температурный коэффициент, при котором эталонное напряжение VREF равно:

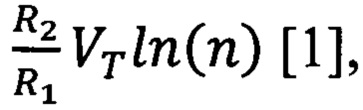

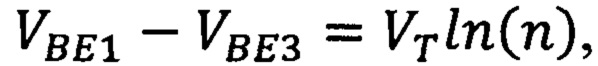

Классической схемой для реализации данного принципа является схема представленная на фиг.1 [1], где M1, M2, M3 - одинаковые полевые транзисторы, Q1, Q2 - одинаковые биполярные транзисторы с площадями эмиттеров А, а транзистор Q3 имеет в n раз большую площадь эмиттера nA, чем Q1, Q2, VDD - напряжение питания. Формируемое опорное напряжение равно:

где VBE3 - напряжение база-эмиттер биполярного транзистора Q3, R2 и R1 - резисторы 1 и 2 с температурным коэффициентом наиболее близким к нулю. Здесь и далее в зависимости от контекста будем подразумевать под Ri как наименование i-того резистора на схеме, так и номинал этого резистора в случае употребления данного обозначения в формульных выражениях.

где VBE3 - напряжение база-эмиттер биполярного транзистора Q3, R2 и R1 - резисторы 1 и 2 с температурным коэффициентом наиболее близким к нулю. Здесь и далее в зависимости от контекста будем подразумевать под Ri как наименование i-того резистора на схеме, так и номинал этого резистора в случае употребления данного обозначения в формульных выражениях.

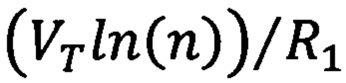

В данной схеме операционный усилитель (ОУ) из-за большого коэффициента усиления приравнивает напряжения в узлах X и Y, устанавливая необходимое напряжение на затворах транзисторов М1 и М2. Разница напряжений  где VBE1 - напряжение база-эмиттер транзистора Q1, a VBE3 - напряжение база-эмиттер транзистора Q3 приводит к протеканию через резистор R1 тока

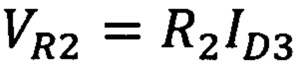

где VBE1 - напряжение база-эмиттер транзистора Q1, a VBE3 - напряжение база-эмиттер транзистора Q3 приводит к протеканию через резистор R1 тока  с положительным температурным коэффициентом. Транзисторы M1, M2, M3 представляют собой классическое токовое зеркало, с коэффициентом передачи, равным единице в следствие идентичности транзисторов M1, M2, M3. Таким образом, токи стоков транзисторов М1,М2,М3 оказываются равными, ID1=ID2=ID3. Как следствие этого ток стока транзистора М3 также имеет положительный температурный коэффициент. Проходя через резистор R2, ток стока ID3 транзистора М3 формирует напряжение

с положительным температурным коэффициентом. Транзисторы M1, M2, M3 представляют собой классическое токовое зеркало, с коэффициентом передачи, равным единице в следствие идентичности транзисторов M1, M2, M3. Таким образом, токи стоков транзисторов М1,М2,М3 оказываются равными, ID1=ID2=ID3. Как следствие этого ток стока транзистора М3 также имеет положительный температурный коэффициент. Проходя через резистор R2, ток стока ID3 транзистора М3 формирует напряжение  на резисторе R2, которое увеличивается с ростом температуры. Поскольку напряжение база-эмиттер VBE2 транзистора Q2 имеет отрицательную температурную зависимость, путем подбора номинала резистора R2.становится возможным сформировать эталонное напряжение VREF, которое имеет нулевой температурный коэффициент.

на резисторе R2, которое увеличивается с ростом температуры. Поскольку напряжение база-эмиттер VBE2 транзистора Q2 имеет отрицательную температурную зависимость, путем подбора номинала резистора R2.становится возможным сформировать эталонное напряжение VREF, которое имеет нулевой температурный коэффициент.

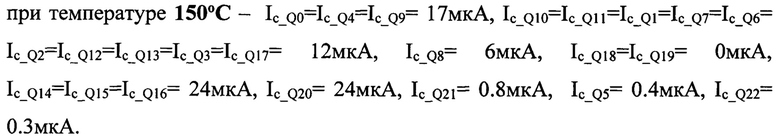

Наиболее близким по совокупности признаков является устройство, выполненное полностью на биполярных транзисторах [9], того же назначения, что и предлагаемое. Схема устройства прототипа приведена на фиг.2. В качестве основного усилителя в схеме используется инвертирующий каскад с общим эмиттером (ОЭ), выполненный на биполярном npn транзисторе Q3. Между базой и коллектором данного каскада добавлена стабилизирующая емкость Cm1, повышающая запас по фазе всей схемы и предотвращающая нежелательные колебания во внутренних ее цепях. Все pnp транзисторы Q4 - Q8 в верхней части схемы представляют собой классическое токовое зеркало, которое повторяет ток коллектора транзистора Q3. Резисторы R2 - R6, добавленные со стороны эмиттеров pnp транзисторов Q4 - Q8, позволяют повысить линейность токового зеркала. За счет обратной связи в цепи: коллектор транзистора Q3 - токовое зеркало Q5 - Q7 - цепь коллектора транзистора Q2 - база транзистора Q1, напряжение коллектор-эмиттер транзистора Q1, совпадающее с напряжением база-эмиттер транзистора Q3, устанавливается таким, что токи коллекторов транзисторов Q1 и Q2 становятся практически одинаковыми. Напряжение питания схемы обозначено как VCC. Поскольку базы транзисторов Q1 и Q2 электрически соединены, то выполняется равенство

где VBE1 - напряжение база-эмиттер транзистора Q1, VBE2 - напряжение база-эмиттер транзистора Q2, IC2 - ток коллектора транзистора Q2, R1IC2 - напряжение на резисторе R1. Учитывая, что в устройстве прототипе площадь эмиттера Q2 в четыре раза больше, чем у транзистора Q1, напряжение на резисторе R1 равно

тогда ток через резистор R1 и как следствие ток коллектора IC2 равны

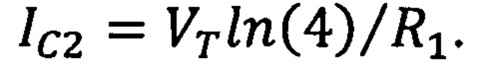

Из последнего выражения видно, что сформированный схемой прототипом ток имеет положительный температурный коэффициент, поскольку частная производная тока коллектора IC2 по температуре Т оказывается положительной

Ток, сформированный схемой прототипом, оказывается пропорциональным абсолютной температуре (proportional to absolute temperature, PTAT) и обозначен на фиг. 2 как IPTAT. Данный ток оказывается достаточным для формирования выходного эталонного напряжения VREF с нулевым температурным коэффициентом. Достаточно пропустить его через биполярный транзистор с последовательно включенным резистором, аналогично выходному каскаду, состоящему из R2 и Q2 на фиг.1.

Наличие трудно воспроизводимого при изготовлении выходного каскада, не отвечающего современным требованиям согласования элементов, при производстве препятствует применению данного решения в современных технологических процессах.

Задача, на решение которой направлено данное изобретение, заключается в создании воспроизводимого на современных технологических КМОП-процессах малошумящего эталонного источника опорного напряжения.

Технический результат заключается в возможности значительной компенсации нелинейности температурного коэффициента в расширенном температурном диапазоне, расширении диапазона питающих напряжений, в стабильности запуска схемы, достижении низкого уровня низкочастотных фликкер-шумов.

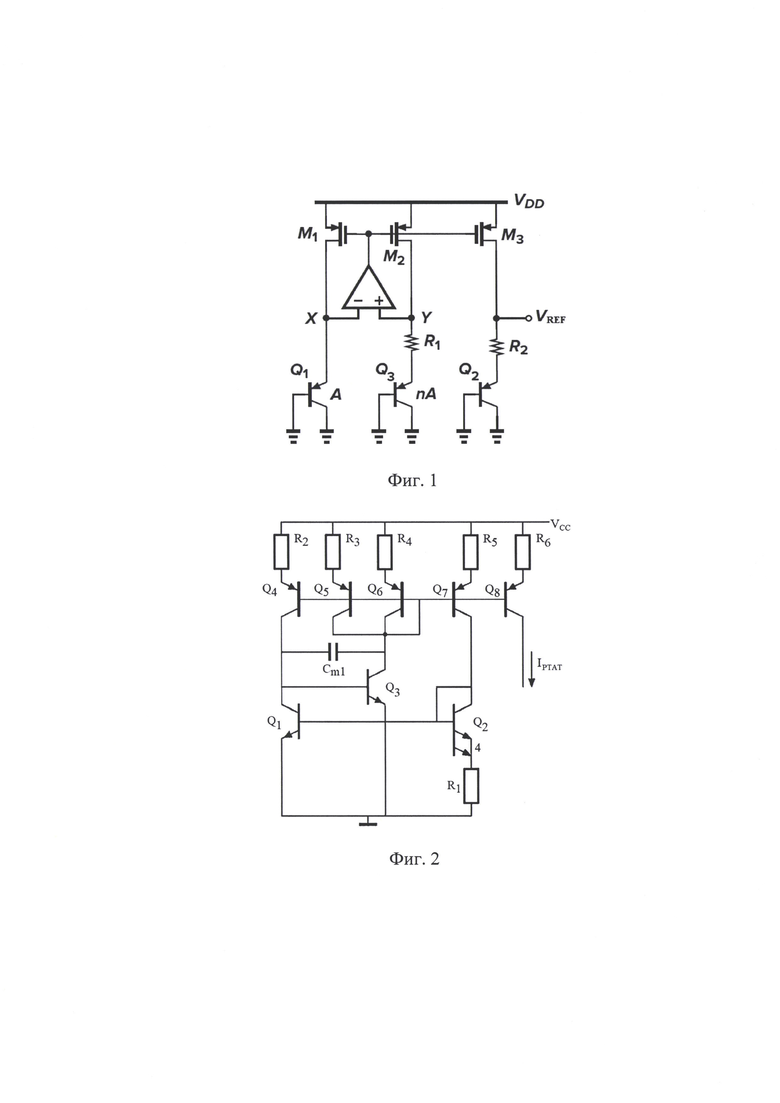

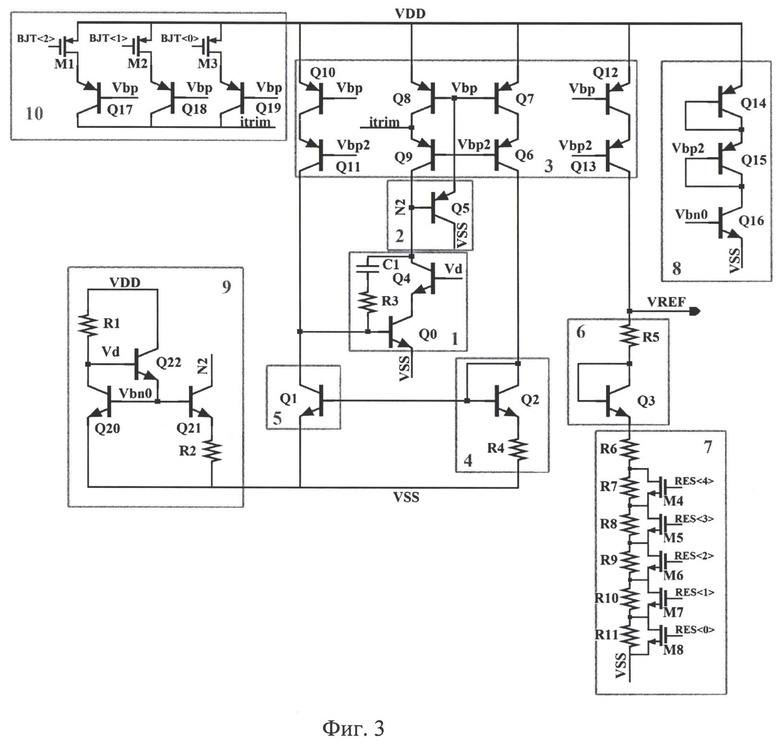

Технический результат достигается тем, что малошумящий источник опорного напряжения, содержащий основной усилительный каскад с общим эмиттером 1, выполненный на npn транзисторе Q0, подключенный к основному токовому зеркалу 3, выполненному на биполярных pnp транзисторах Q7, Q8, Q10, Q12 с объединенными базами, токи которых, установленные за счет основного усилительного каскада 1, формирующего напряжение Vbp на их базах, поступают на коллекторы двух npn биполярных транзисторов Q1 и Q2 в левой и правой ветвях токового зеркала 5 и 4, соответственно, базы которых объединены, в правой ветви токового зеркала 4 выполнен в диодном включении и соединен со стороны эмиттера с первым контактом не зависящего от температуры резистора R4, а транзистор Q1 в левой ветви токового зеркала 5 включен по схеме каскада с общим эмиттером и своим коллектором подключен к базе основного усилительного каскада с общим эмиттером 1 транзистора Q0, между базой и коллектором которого расположена стабилизирующая емкость C1, формируя, убывающие с ростом температуры, напряжения база-эмиттер транзисторов Q1 и Q2, за счет разных плотностей токов, обусловленных несовпадающими площадями эмиттеров транзисторов Q1 и Q2, разница напряжений база-эмиттер которых растет с ростом температуры, формируя на резисторе R4 ток, пропорциональный абсолютной температуре, который проходя через основное токовое зеркало 3 через транзисторы Q8, Q7, повторяется на транзисторе Q12 и формирует пропорциональный абсолютной температуре ток IPTAT на коллекторе транзистора Q12, при этом эмиттером транзистор Q1 соединяют с сетью VSS, а резистор R4 вторым контактом соединяют с сетью VSS, основной усилительный каскад с общим эмиттером 1, подключают эмиттером транзистора Q0 к потенциалу земли VSS, согласно изобретению, база транзистора Q0 содержит резистор R3, последовательно подключенный с емкостью С1, а напряжение на коллекторе транзистора Q0 фиксируют, подключенным к коллектору транзистора Q0, эмиттером биполярного npn транзистора Q4, с напряжением смещения базы Vd, включенным по типу эмиттерного повторителя, базой Q4 соединен с блоком запуска 9, а коллектором соединяют с емкостью С1, основное токовое зеркало 3 выполнено в каскадном исполнении с добавлением pnp биполярных транзисторов Q6, Q9, Q11, Q13 с объединенными базами и равными площадями эмиттеров, а также напряжением смещения на их базах Vbp2, при этом коллекторы транзисторов Q10, Q8, Q7 и Q12 соединяют с эмиттерами транзисторов Q11, Q9, Q6 и Q13, соответственно, эмиттеры транзисторов Q10, Q8, Q7 и Q12 подключены к сети VDD, базой транзисторы Q8, Q7, Q12, Q10 соединены с эмиттером транзистора Q5, а коллекторы транзисторов Q11 и Q1, а также Q6 и Q2 объединяют попарно, и добавлением в блоке диода 2 pnp транзистора Q5 с коллектором на потенциале земли VSS, базу транзистора Q5 соединяют через сеть N2 с коллектором транзистора Q4, а также с коллектором транзистора Q9, для компенсации токов баз транзисторов Q7, Q8, Q10, Q12, калибруемого путем добавления тока через сеть itrim при помощи блока тримминга токового зеркала 10, калибруемая часть которого набрана из двоично-взвешенных по площадям эмиттеров набора pnp биполярных транзисторов Q17, Q18, Q19, коллекторы которых соединяют с сетью itrim, базы которых смещают напряжением Vbp с КМОП-ключами МОП-транзисторов М1 М2, М3, подключенными к эмиттерам транзисторов Q17, Q18, Q19, соответственно, и управляемые напряжениями на затворах BJT<2>, BJT<1>, BJT<0>, соответственно, подключенными к сети VDD, площади эмиттеров транзисторов Q17, Q18, Q19 двоично взвешены и равны 16⋅Apnp, 8⋅Apnp и 4⋅Apnp, соответственно, причем площадь эмиттера транзистора Q8 равна 8⋅Apnp, а площади эмиттеров транзисторов Q7, Q10, Q12 и Q17 равны 16⋅Apnp основного токового зеркала 3, где Apnp - минимальная используемая для согласования ряда транзисторов Q17, Q18, Q19, Q7, Q8, Q10, Q12 площадь эмиттера, устройство дополнительно содержит выходной каскад 6, состоящий из npn транзистора Q3 по габаритам идентичного транзистору Q1, но выполненному в диодном включении, и топологически согласованного с транзисторами Q1,Q2, где транзистор Q2, в восемь раза больший по площади эмиттера, чем транзистор Q1, по типу согласования массивов с перекрестными связями cross-couplet, соединенного коллектором с одним контактом резистора R5, а другим контактом резистор соединяют с коллектором транзистора Q13, калибруемого при помощи блока тримминга резистора 7, выходной каскад 6, формирующий выходное эталонное напряжение VREF, посредством тока РТАТ, сформированного на коллекторах транзисторов Q12 и Q13 основного токового зеркала 3, где блок триммингуемых резисторов 7 в эмиттере транзистора Q3, содержит двоично-взвешенный набор резисторов R7, R8, R9, R10, R11 последовательно включенных с резистором R6, подключенных через контакт резистора R11 к потенциалу земли VSS для уменьшения влияния сопротивлений шунтирующих ключей МОП транзисторов М4, М5, М6, М7, М8, топологически согласованных между собой и с резисторами R4 и R5, с шунтирующими их КМОП-ключами МОП транзисторов М4, М5, М6, М7, М8, управляемыми напряжениями на затворах RES<4>, RES<3>, RES<2>, RES<1>, RES<0>, соответственно, устройство дополнительно содержит блок запуска 9, состоящий из ток задающего резистора R1 соединенного с базой транзистора Q22, и с напряжением питанием VDD и определяющего стартовый ток при подаче питания VDD, токового зеркала на npn биполярных транзисторах Q20 Q21, Q22, формирующего опорные напряжения Vd и Vbn0, диодную часть которого, состоящую из транзисторов Q20 и Q22, выполняют по схеме компенсации тока базы, где коллектор транзистора Q22 соединен с напряжением питанием VDD, транзистор Q20 выполнен в диодном включении, база транзистора Q22 соединена коллектором транзистора Q20, эмиттер соединен с объединенными базами транзисторов Q20 и Q21, отраженный ток которого с коллектора транзистора Q21, с расположенным в эмиттере резисторе R2, протекает через сеть N2 в блоке запуска 9 и понижает напряжение в электрически соединенном с блоком запуска 9 сети N2 диода 2 токового зеркала 3, тем самым выводя всю схему из устойчивого выключенного состояния, при этом другим контактом резистор R2, а также эмиттером транзистор Q20 подключают к потенциалу земли VSS, а также устройство содержит блок формирования напряжения смещения 8, формирующий напряжение Vbv2 на базах транзисторов Q11, Q9, Q6 Q13 основного токового зеркала 3, формирующегося из отраженного тока блока запуска 9 при помощи напряжения смещения Vbn0, приложенного к базе npn транзистора Q16, на эмиттере которого задан потенциал земли VSS, формирующего напряжение Vbp2 путем пропускания заданного тока через два последовательно включенных биполярных pnp транзистора Q14 и Q15 в диодном включении к коллектору транзистора Q16, где коллектор транзистора Q14 подключают к эмиттеру транзистора Q15, коллектор транзистора Q15 подключают к коллектору транзистора Q16, а эмиттер транзистора Q14 соединяют с напряжением питания VDD.

В изобретении, включающем биполярные транзисторы, как основное устройство для построения схемы источника опорного напряжения используется оригинальная калибровка, которая позволяет значительно снизить величину температурной зависимости схемы. Выходной каскад выполнен по классической архитектуре, см. фиг. 1, однако, со схемотехническим решением, выполненным полностью на биполярных транзисторах, которые в БиКМОП технологиях позволяют получить низкие уровни фликкер-шумов схемы в сравнении с классической реализацией на КМОП устройствах.

Для получения эталонного напряжения в изобретении на фиг. 3 вместо операционного усилителя, в сравнении с фиг. 1, по аналогии с прототипом [9] на фиг. 2, в центральной части схемы используется каскад с общим эмиттером на Q0 с цепью компенсации из С1 и R3, которая обеспечивает лучшую устойчивость системы по обратной связи. В отличие от классической реализации базы основных биполярных транзисторов Q1 Q2 объединены, что не меняет принципа функционирования ИОНа, но значительно упрощает реализацию схемы с использованием однокаскадного усилителя с ОЭ.

Устройство реализуется следующим образом.

Пример 1. Спроектированное под PDK XFAB 180 нм изобретение на фиг. 3 было реализовано схемотехнически и топологически с последующим производством и измерением основных шумовых и температурных параметров.

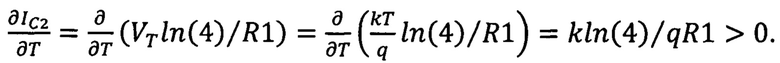

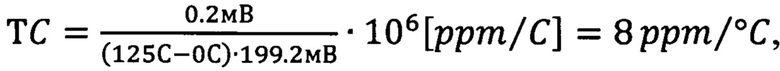

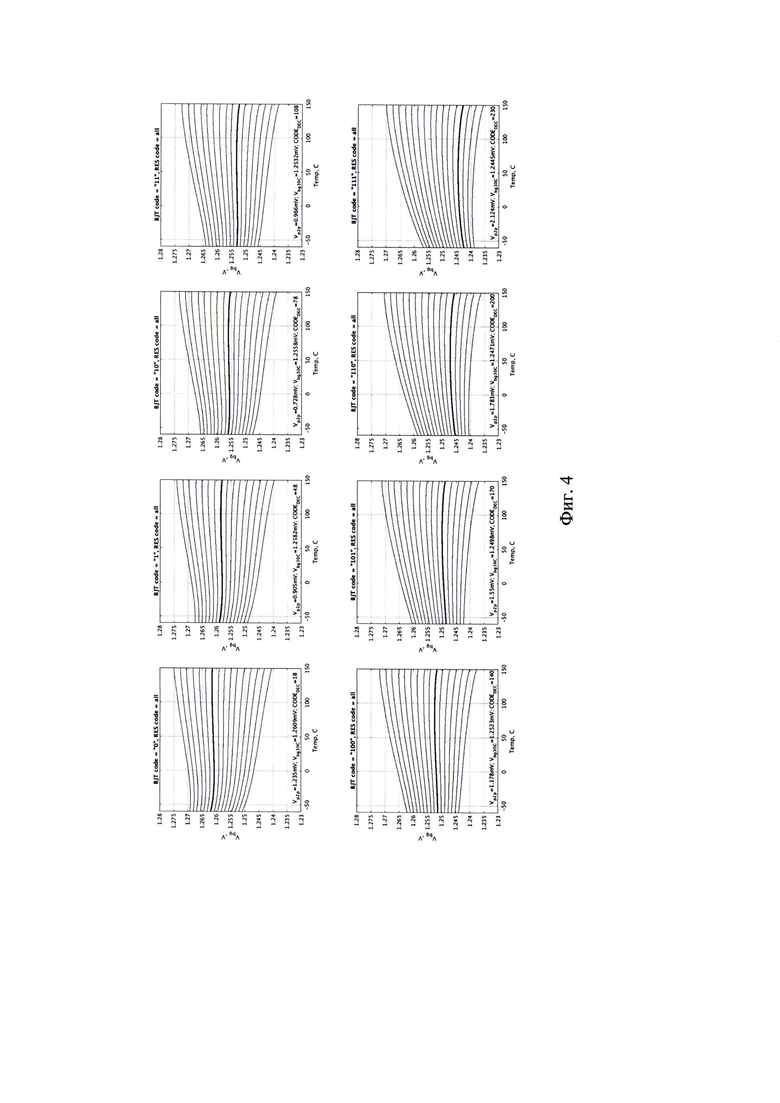

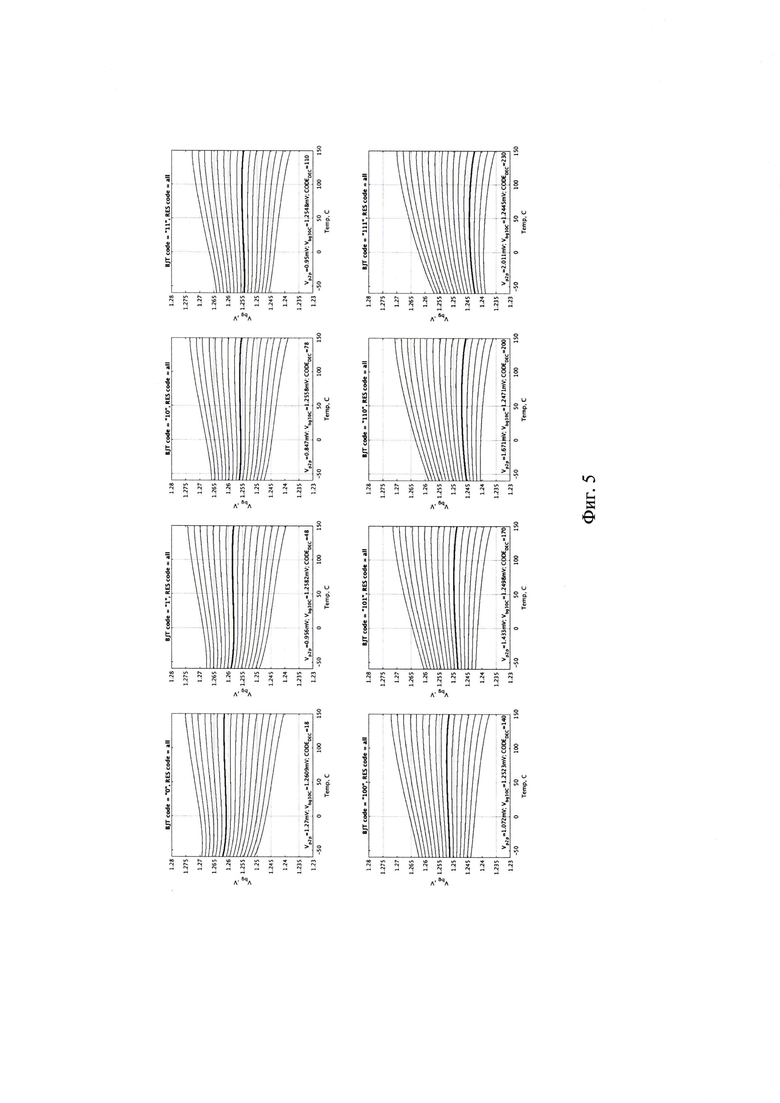

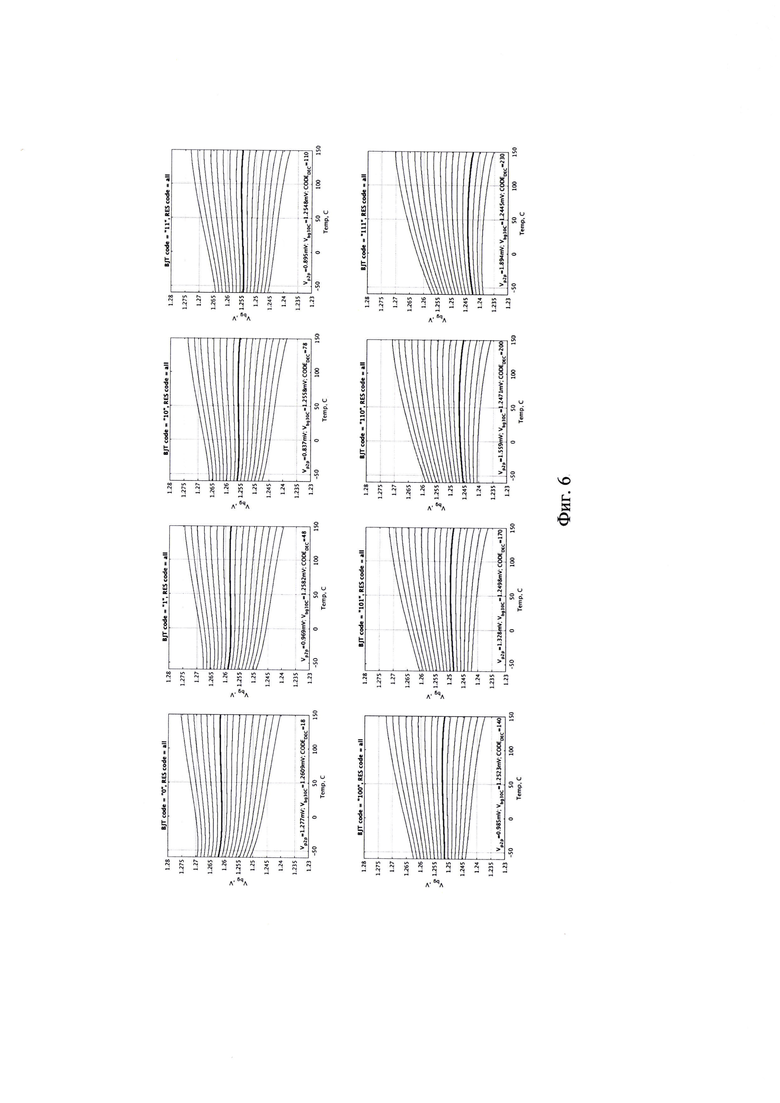

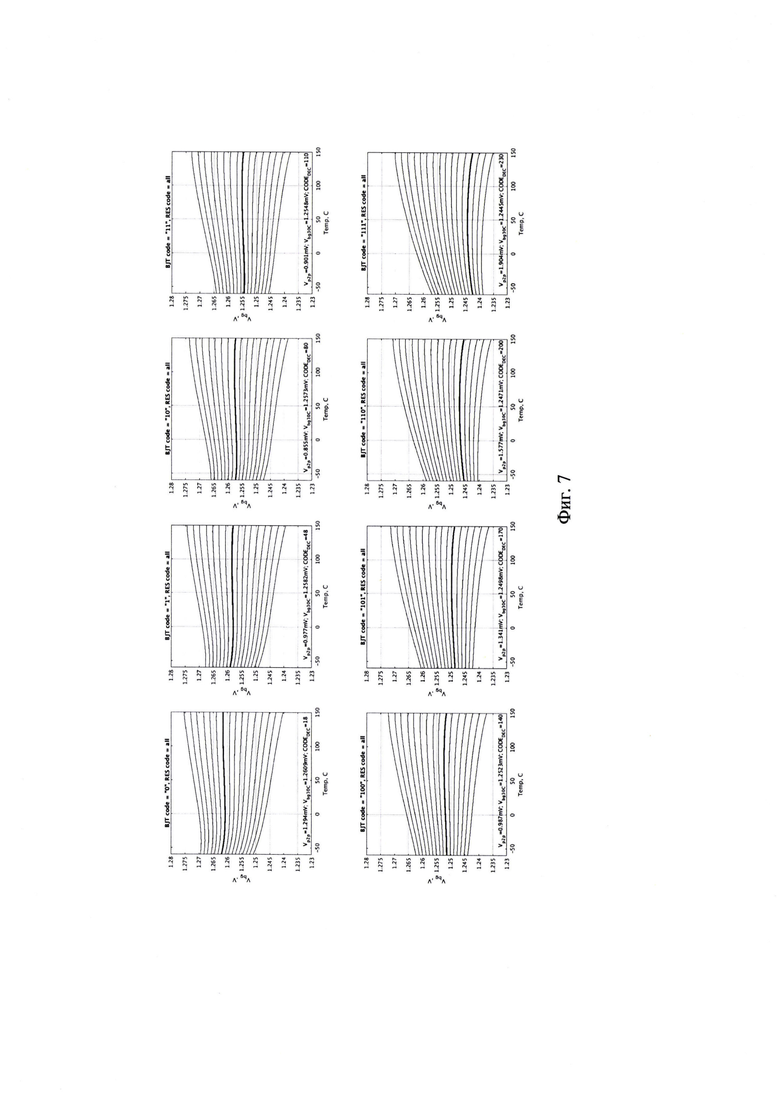

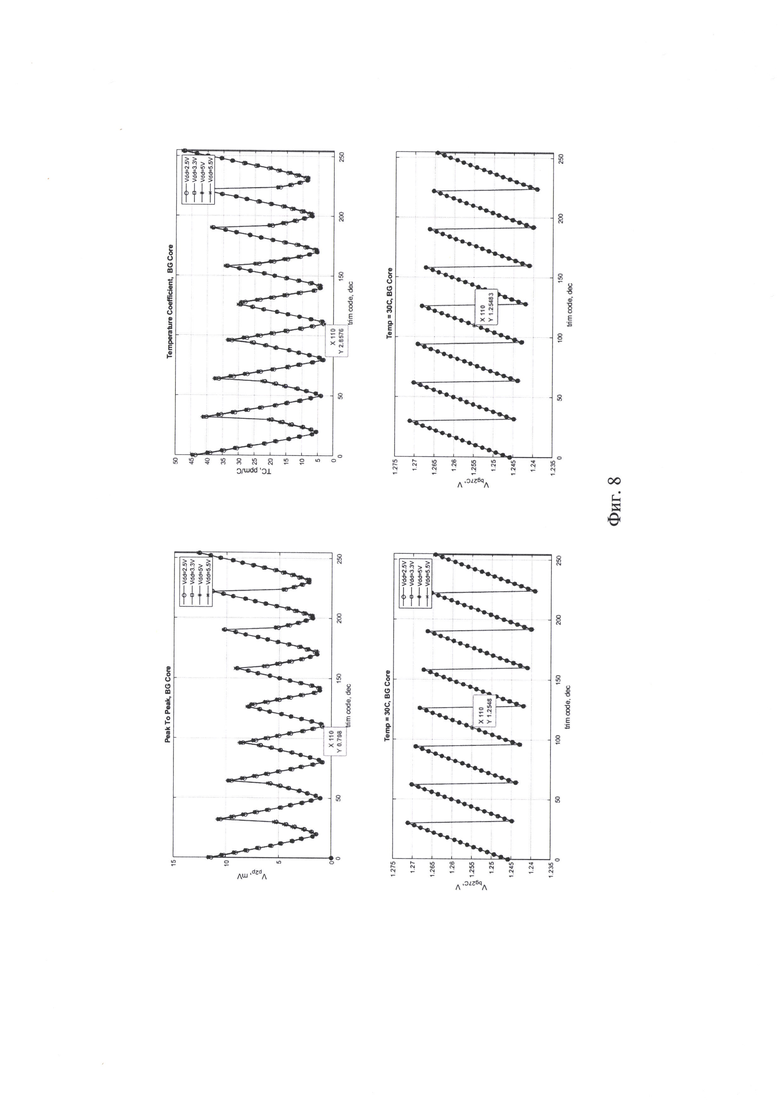

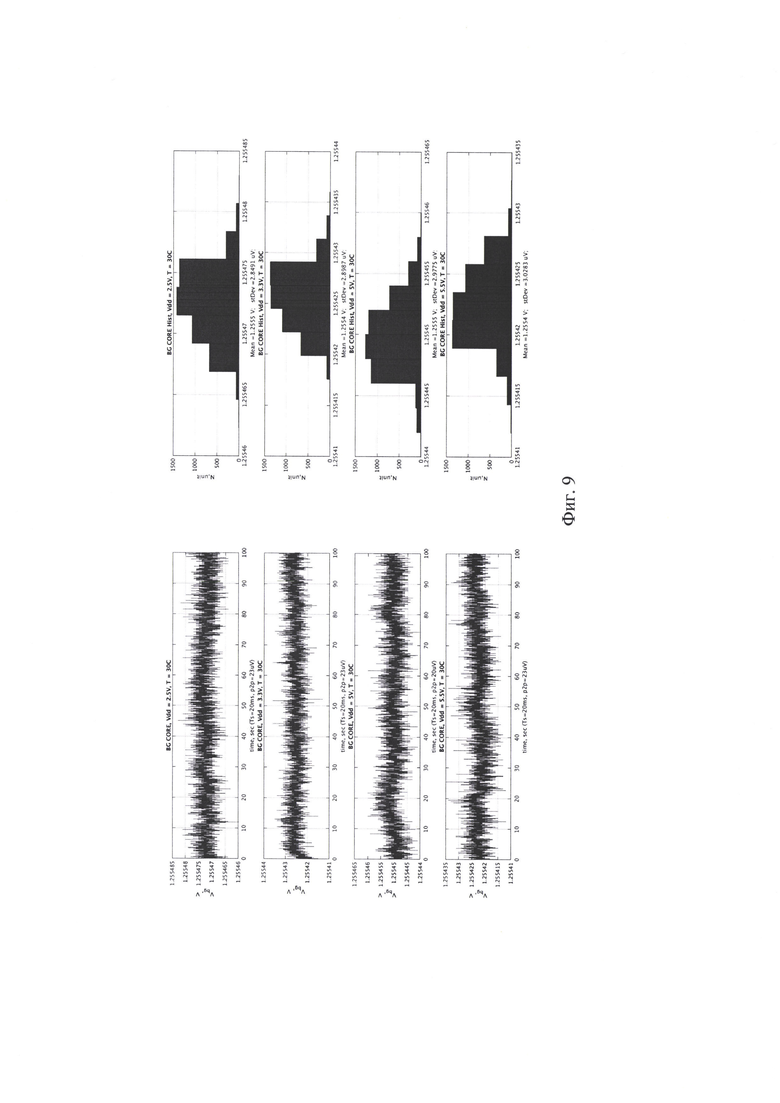

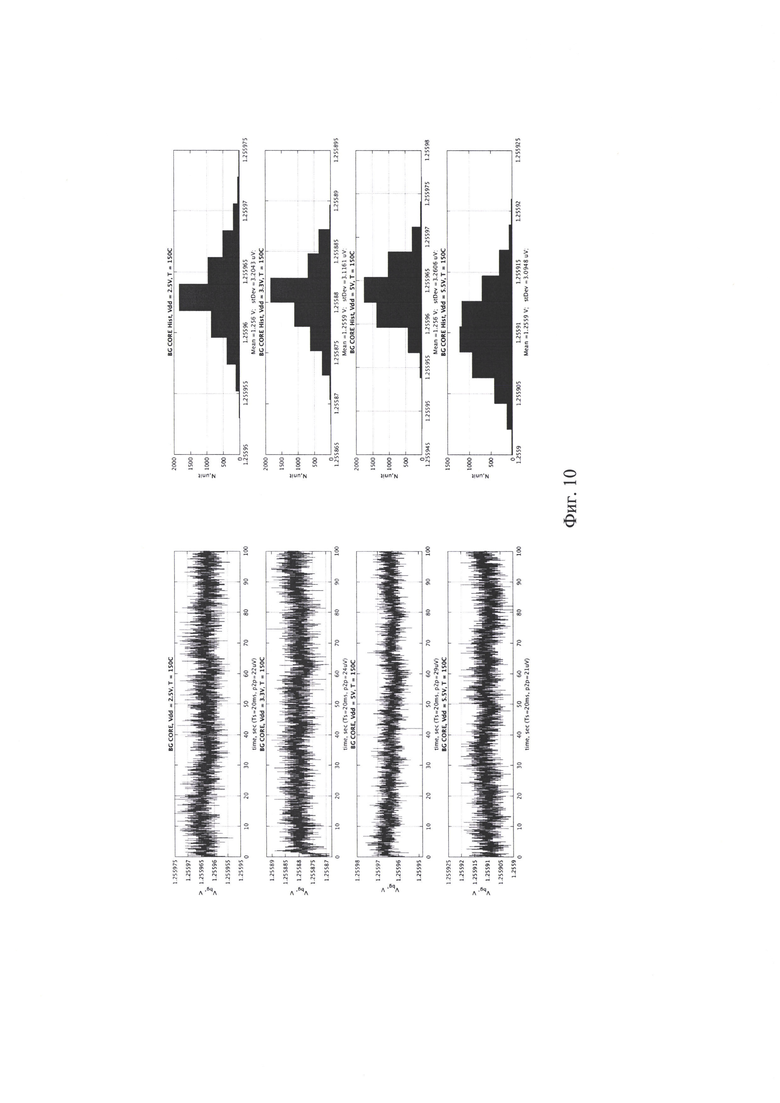

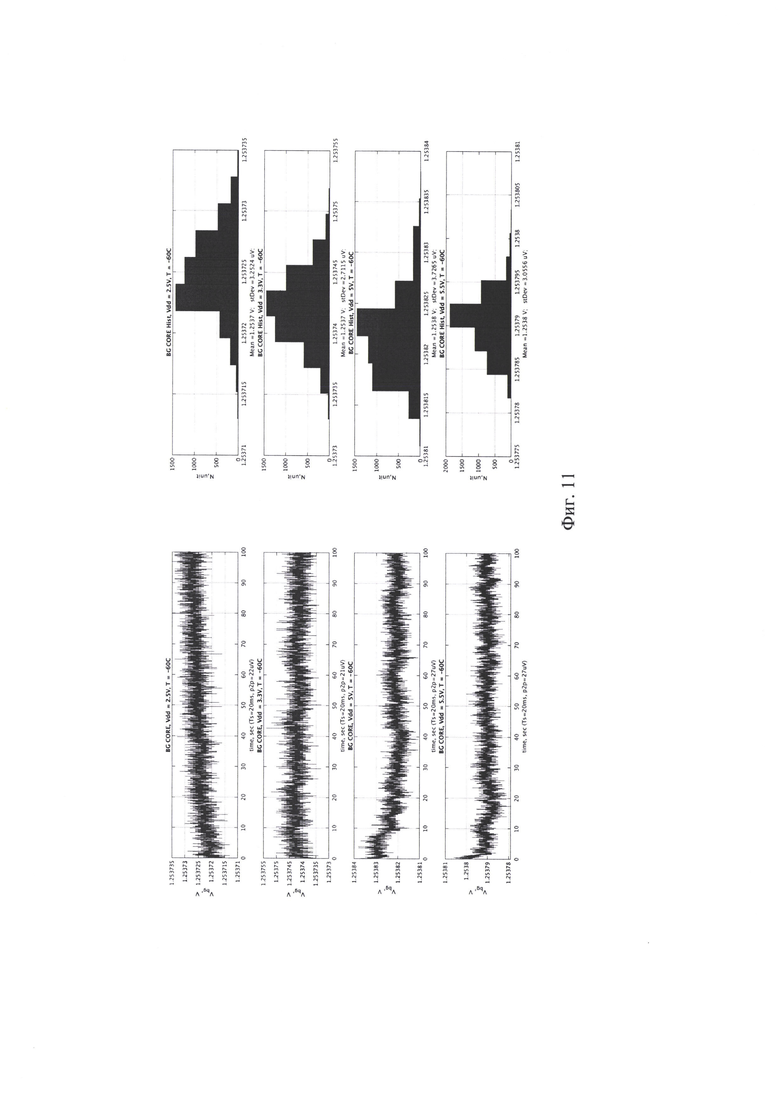

На фиг. 1 изображена классическая для КМОП процессов схема устройства источника опорного напряжения; на фиг.2 приведена схема прототипа, на фиг. 3 приведена схема изобретения малошумящего источника опорного напряжения, на фиг. 4 приведены зависимости выходного опорного напряжения от температуры для всех возможных значений кодов калибровки BJT<2:0> и RES<4:0> для напряжения питания VDD=2.5B, на фиг. 5 приведены зависимости выходного опорного напряжения от температуры для всех возможных значений кодов калибровки BJT<2:0> и RES<4:0> для напряжения питания VDD=3.3B, на фиг. 6 приведены зависимости выходного опорного напряжения от температуры для всех возможных значений кодов калибровки BJT<2:0> и RES<4:0> для напряжения питания VDD=5B, на фиг.7 приведены зависимости выходного опорного напряжения от температуры для всех возможных значений кодов калибровки BJT<2:0> и RES<4:0> для напряжения питания VDD=5.5B, на фиг.8 приведены на левом верхнем графике зависимости величины Vp2p - максимального отклонения опорного напряжения VREF (Vp2p - разница максимального и минимального напряжений величины VREF в указанном температурном диапазоне, так называемое напряжение «от пика до пика», англ. аббр. «peak to peak», типовое условное сокращение «р2р»), измеренного в диапазоне температур -60°С … 150°С от полного восьмибитового кода BJT<2:0>, RES<4:0>, правом верхнем графике - зависимости температурного коэффициента ТС, измеренного в диапазоне температур -60°С…150°С от полного восьмибитового кода BJT<2:0>, RES<4:0>, рассчитанного по формуле

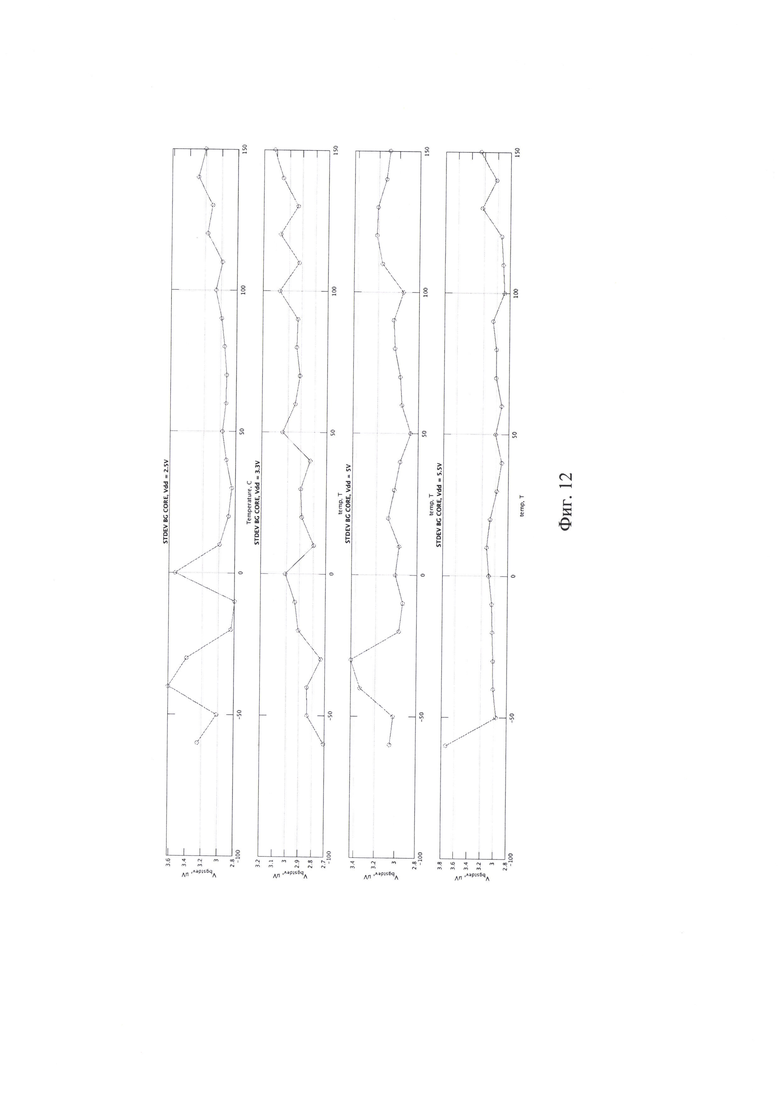

где Tmax, Tmin - максимальная и минимальная температура из диапазона температур -60°С…150°С, V30°C - напряжение при температуре 30°С, на нижних графиках дано усредненное по температуре значение опорного напряжения VREF в зависимости от полного восьмибитового кода BJT<2:0>, RES<4:0>, представленного в десятичном формате, на фиг.9 приведены зависимости опорного напряжения от времени для различных напряжений-питания VDD=2.5B, 3.3 В, 5 В, 5.5 В и соответствующие им гистограммы при температуре 30°С, на фиг.10 приведены зависимости опорного напряжения от времени для различных напряжений питания VDD=2.5B, 3.3 В, 5 В, 5.5 В и соответствующие им гистограммы при температуре 150°С, на фиг.11 приведены зависимости опорного напряжения от времени для различных напряжений питания VDD=2.5B, 3.3 В, 5 В, 5.5 В и соответствующие им гистограммы при температуре -60°С, на фиг.12 приведены зависимости среднеквадратического отклонения опорного напряжения от температуры для различных напряжений питания VDD=2.5B, 3.3 В, 5 В, 5.5 В, на фиг.13 представлены габаритные размеры элементов схемы, приведенной на фиг.3, применительно к реализации под PDK XFAB 180 нм.

В приведенном примере реализации на фиг.4-8 показана возможность значительной компенсации нелинейной зависимости температурного коэффициента в расширенном температурном диапазоне -60С … 150°С, большем, чем в прототипе [9], где заявлен температурный диапазон 0°С … 125°С (см. [9], фиг. 5). В прототипе температурный коэффициент согласно фиг.5, [9] и формуле расчета ТС, приведенной выше, составляет 8 ppm/°С

в приведенном примере реализации по технологической норме 180 нм согласно фиг.8 (правый верхний график, при построении которого использовалась формула для расчета температурного коэффициента приведенная выше) для большей части оптимальных кодов калибровки значение температурного коэффициента составило менее 5 ppm/°С, а в лучшем случае 2.8 ppm/°С, для расширенного диапазона температур -60С … 150°С.

Согласно прототипу, диапазон в котором может изменяться напряжение питания схемы составляет 1 В [9], в то время как для приведенного примера реализации диапазон изменения напряжения питания схемы составляет 3В, т.е. является расширенным в сравнении со схемой прототипа.

На фиг. 12 приведены зависимости среднеквадратического отклонения опорного напряжения от температуры для различных напряжений питания VDD=2.5B, 3.3 В, 5 В, 5.5 В. При измерении каждого значения для соответствующей температуры и напряжения питания осуществлялось включение и выключение схемы, что показало стабильность запуска схемы при любых внешних воздействиях.

Резюмируя для приведенного примера реализации, среднеквадратичное отклонение низкочастотного шума в полосе от 0,1 Гц до 10 Гц составило менее 5 мкВ; в диапазоне напряжений питания от 2,5 В до 5,5 В и температур -60 … 150°С значение температурного коэффициента составило менее 5 ppm/°С.

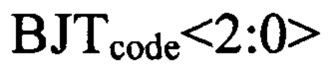

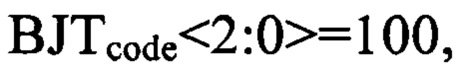

В предлагаемой схеме на фиг. 3 изображены биполярные каскодные токовые зеркала для уменьшения влияния напряжения питания. Реализована возможность тримминга коэффициента передачи тока в токовом зеркале 3 трехбитовым кодом BJT<2:0>, путем подключения и отключения дополнительных двоично взвешенных секций биполярных транзисторов в блоке 10. Реализован блок тримминга резисторов 7, который непосредственно формирует независящее от температуры эталонное опорное напряжение VREF, для чего используется набор двоично-взвешенных секций резисторов с минимальной температурной зависимостью, которые подключаются и отключаются с помощью пятибитового кода RES<4:0>.

Необходимо отметить, что основной идеей алгоритма калибровки является именно одновременный тримминг тока токового зеркала и номинала выходного резистора, т.е. совместный подбор кодов BJT<2:0> и RES<4:0>, что и позволяет добиваться низких значений температурного коэффициента в достаточно широких температурных диапазонах, а также корректировать уровень опорного эталонного напряжения VREF в некотором диапазоне, который преимущественно зависит от диапазона тримминга тока токового зеркала 10, задающегося кодом BJT<2:0>. Таким образом, подбор кода RES<4:0> уменьшает температурную зависимость эталонного напряжения VREF, а подбор кода BJT<2:0> задает его абсолютный уровень. Правильная оценка технологического разброса позволяет получать для каждого кода BJT<2:0> минимально доступное значение температурного коэффициента при подборе соответствующего кода RES<4:0>.

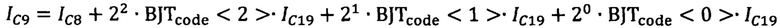

Формула для расчета тока токового зеркала с учетом кода калибровки BJTcode<2:0> может быть записана в следующем виде

где IC9 - ток коллектора транзистора Q9, IC8 - ток коллектора транзистора Q8, IC19 - ток коллектора транзистора Q19 переменные  в последнем уравнении могут принимать значения 1 или 0, в зависимости от калибровочного кода. По умолчанию код калибровки равен

в последнем уравнении могут принимать значения 1 или 0, в зависимости от калибровочного кода. По умолчанию код калибровки равен  (что тоже самое

(что тоже самое  что соответствует

что соответствует  При таком варианте задания становится возможным как увеличить ток IC9 до IC8 + 7IC19 при коде BJTcode<2:0>=111, так и уменьшить его до IC8 при коде BJTcode<2:0>=000. Отметим, что поскольку р-канальными ключами М1-М3 управляют напряжения BJT<2:0>, см. фиг.3, то необходимо отметить, что коду BJTcode<2:0>=100 будут соответствовать напряжения BJT<2:0>=<VSS VDD VDD>. Нужно иметь ввиду, что BJTcode коду «1» будет соответствовать BJT напряжение VSS, a BJTcode коду «0» будет соответствовать BJT напряжение VDD. В зависимости от технологического разброса, который необходимо определить еще на стадии моделирования схемы в системе автоматизированного проектирования (САПР) возможно увеличение разрядности кода

При таком варианте задания становится возможным как увеличить ток IC9 до IC8 + 7IC19 при коде BJTcode<2:0>=111, так и уменьшить его до IC8 при коде BJTcode<2:0>=000. Отметим, что поскольку р-канальными ключами М1-М3 управляют напряжения BJT<2:0>, см. фиг.3, то необходимо отметить, что коду BJTcode<2:0>=100 будут соответствовать напряжения BJT<2:0>=<VSS VDD VDD>. Нужно иметь ввиду, что BJTcode коду «1» будет соответствовать BJT напряжение VSS, a BJTcode коду «0» будет соответствовать BJT напряжение VDD. В зависимости от технологического разброса, который необходимо определить еще на стадии моделирования схемы в системе автоматизированного проектирования (САПР) возможно увеличение разрядности кода  Необходимо методом Монте-Карло с достаточным количеством итераций для требуемой достоверности результатов моделирования [16], провести моделирование с учетом разброса по технологическому процессу и несоответствию элементов. По результатам моделирования определить диапазон изменения температурной кривой. От этого диапазона, а также от необходимого шага корректировки температурной зависимости нужно и выбрать разрядность кода BJTcode. Чем шире диапазон и чем меньше шаг корректировки, тем больше необходимо выбирать разрядность кода BJTcode.

Необходимо методом Монте-Карло с достаточным количеством итераций для требуемой достоверности результатов моделирования [16], провести моделирование с учетом разброса по технологическому процессу и несоответствию элементов. По результатам моделирования определить диапазон изменения температурной кривой. От этого диапазона, а также от необходимого шага корректировки температурной зависимости нужно и выбрать разрядность кода BJTcode. Чем шире диапазон и чем меньше шаг корректировки, тем больше необходимо выбирать разрядность кода BJTcode.

Формула для расчета сопротивления триммингованного резистора 7 с учетом кода калибровки  может быть записана в следующем виде

может быть записана в следующем виде

где RSUM - общее сопротивление цепи резисторов, R11 - наименьшее сопротивление в цепи резисторов, переменные  в последнем уравнении могут принимать значения 1 или 0, в зависимости от калибровочного кода. По умолчанию код калибровки равен

в последнем уравнении могут принимать значения 1 или 0, в зависимости от калибровочного кода. По умолчанию код калибровки равен  (что тоже самое

(что тоже самое  ), что соответствует RSUM = R6 + 16R11. При таком варианте задания становится возможным как увеличить сопротивление RSUM R6 + 31 ⋅ R11 при коде REScode<4:0>=11111, так и уменьшить его до R6 при коде

), что соответствует RSUM = R6 + 16R11. При таком варианте задания становится возможным как увеличить сопротивление RSUM R6 + 31 ⋅ R11 при коде REScode<4:0>=11111, так и уменьшить его до R6 при коде  Отметим, что поскольку n-канальными ключами М4-М8 управляют напряжения RES<4:0>, см. фиг.3, то необходимо отметить, что коду REScode<4:0>=10000 будут соответствовать напряжения RES<4:0>=<VSS VDD VDD VDD VDD>. Нужно иметь ввиду, что REScode коду «1» будет соответствовать RES напряжение VSS, a REScode коду «0» будет соответствовать RES напряжение VDD. В зависимости от технологического разброса, который необходимо определить еще на стадии моделирования схемы в САПР возможно увеличение разрядности кода REScode. Необходимо методом Монте-Карло с достаточным количеством итераций для требуемой достоверности результатов моделирования [16], провести моделирование с учетом разброса по технологическому процессу и несоответствию элементов. По результатам моделирования определить диапазон изменения температурной кривой. От этого диапазона, а также от необходимого шага корректировки температурной зависимости нужно и выбрать разрядность кода REScode. Чем шире диапазон и чем меньше шаг корректировки, тем больше необходимо выбирать разрядность кода REScode.

Отметим, что поскольку n-канальными ключами М4-М8 управляют напряжения RES<4:0>, см. фиг.3, то необходимо отметить, что коду REScode<4:0>=10000 будут соответствовать напряжения RES<4:0>=<VSS VDD VDD VDD VDD>. Нужно иметь ввиду, что REScode коду «1» будет соответствовать RES напряжение VSS, a REScode коду «0» будет соответствовать RES напряжение VDD. В зависимости от технологического разброса, который необходимо определить еще на стадии моделирования схемы в САПР возможно увеличение разрядности кода REScode. Необходимо методом Монте-Карло с достаточным количеством итераций для требуемой достоверности результатов моделирования [16], провести моделирование с учетом разброса по технологическому процессу и несоответствию элементов. По результатам моделирования определить диапазон изменения температурной кривой. От этого диапазона, а также от необходимого шага корректировки температурной зависимости нужно и выбрать разрядность кода REScode. Чем шире диапазон и чем меньше шаг корректировки, тем больше необходимо выбирать разрядность кода REScode.

При разработке ИОН в САПР необходимо проектировать типовой случай для кодов калибровки  Разрядности NR и NB необходимо выбирать исходя из приведенных выше рекомендаций, т.е. по результатам моделирования технологических разбросов и несоответствий элементов. Для совместного определения разрядностей NR и NB на этапе проектирования ИОНа необходимо использовать следующий алгоритм: моделирование в САПР настраивается таким образом, чтобы для каждой итерации Монте-Карло с учетом разброса по технологическому процессу и несоответствию элементов автоматически осуществлялся перебор всех возможных значений кодов калибровок

Разрядности NR и NB необходимо выбирать исходя из приведенных выше рекомендаций, т.е. по результатам моделирования технологических разбросов и несоответствий элементов. Для совместного определения разрядностей NR и NB на этапе проектирования ИОНа необходимо использовать следующий алгоритм: моделирование в САПР настраивается таким образом, чтобы для каждой итерации Монте-Карло с учетом разброса по технологическому процессу и несоответствию элементов автоматически осуществлялся перебор всех возможных значений кодов калибровок  Для каждой итерации Монте-Карло необходимо убедиться, что существует такие коды

Для каждой итерации Монте-Карло необходимо убедиться, что существует такие коды  при которых полностью удовлетворяются требования к величине температурного коэффициента ИОНа и шагу подстройки напряжения. Если это условие не выполняется для необходимого количества итераций [16], то следует увеличить разрядности NR и NB и повторить описанный выше алгоритм до тех пор, пока не будет достигнут требуемый результат. При реализации описанного выше подхода можно гарантировать существование необходимого кода калибровки для любого технологического разброса при производстве ИОНа, при условии, что фабричные модели транзисторов адекватно описывают реальные производимые фабрикой устройства. Конкретно для технологического процесса по проектной норме 180 нм в котором была реализована данная схема разрядности NR=5 и NB=3 позволили добиться возможности подстройки опорного напряжения с шагом 2-3 мВ в диапазоне 1.24…1.26 В.

при которых полностью удовлетворяются требования к величине температурного коэффициента ИОНа и шагу подстройки напряжения. Если это условие не выполняется для необходимого количества итераций [16], то следует увеличить разрядности NR и NB и повторить описанный выше алгоритм до тех пор, пока не будет достигнут требуемый результат. При реализации описанного выше подхода можно гарантировать существование необходимого кода калибровки для любого технологического разброса при производстве ИОНа, при условии, что фабричные модели транзисторов адекватно описывают реальные производимые фабрикой устройства. Конкретно для технологического процесса по проектной норме 180 нм в котором была реализована данная схема разрядности NR=5 и NB=3 позволили добиться возможности подстройки опорного напряжения с шагом 2-3 мВ в диапазоне 1.24…1.26 В.

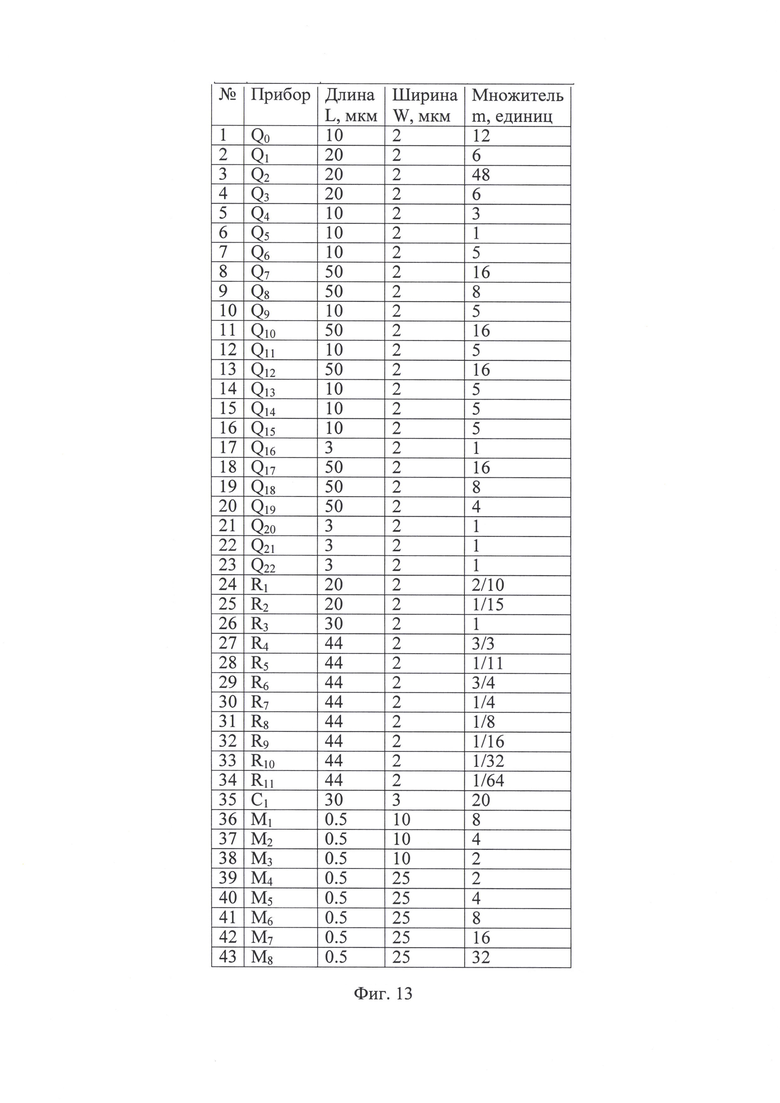

На фиг. 13 приведены габаритные размеры элементов схемы, приведенной на фиг. 3, применительно к реализации под PDK XFAB 180 нм, где для резисторов множитель m приводится в виде дроби, где числитель дроби обозначает количество последовательно соединенных секций из параллельно соединенных резисторов, а знаменатель обозначает количество параллельно соединенных элементарных резисторов длиной L и шириной W в каждой секции. Для транзисторов множитель m показывает во сколько раз увеличена ширина транзистора W или, что тоже самое, сколько таких же транзисторов включено параллельно.

Типовые значения обозначенных на схеме напряжений для приведенного примера при напряжении питания 2.5 В:

при температуре 27°С - Vd=1.2 В, Vbn0=0.7 В, N2=1.3 В, Vbp=1.9 В, Vbp2=1.3 В, itrim=1.9B, VREF=1.254 В;

при температуре -60°С - Vd=1.613 В, Vbn0=0.832 В, N2=0.998 В, Vbp=1.765 В, Vbp2=0.961 В, itrim=1.754 В, VREF=1.254B;

при температуре 150°С - Vd=0.729 В, Vbn0=0.447 В, N2=1.963 В, Vbp=1.82 В, Vbp2=2.247 В, itrim=2.19 В, VREF=1.253 В;

Типовые значения обозначенных на схеме напряжений для приведенного примера при напряжении питания 5.5 В:

при температуре 27°С - Vd=1.317 В, Vbn0=0.708 В, N2=4.384 В, Vbp=4.982 В, Vbp2=4.237 В, itrim=4.857B, VREF=1.254B;

при температуре -60°С - Vd=1.669 В, Vbn0=0.861 В, N2=3.969 В, Vbp=4.765 В, Vbp2=3.895 В, itrim=4.687 В, VREF=1.254 В;

при температуре 150°С - Vd=0.803 В, Vbn0=0.485 В, N2=4.964 В, Vbp=5.247 В, Vbp2=4.736 В, itrim=5.109 В, VREF=1.252B;

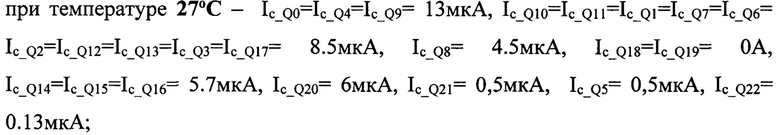

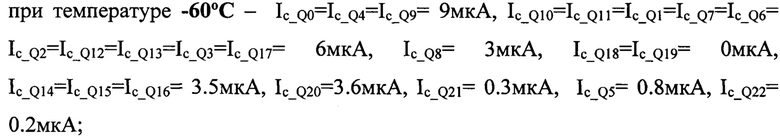

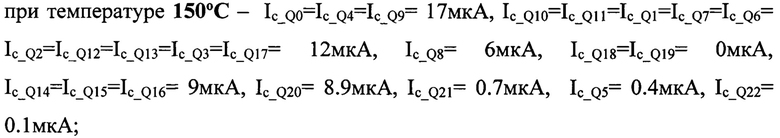

Типовые значения токов коллекторов транзисторов при напряжении питания 2.5 В:

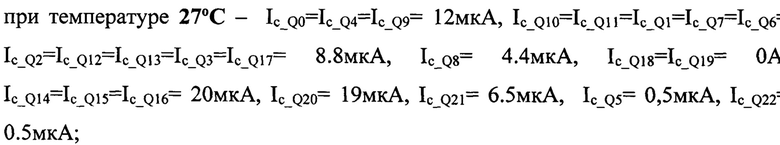

Типовые значения токов коллекторов транзисторов при напряжении питания 5.5 В:

Непосредственно калибровку произведенных ИОНов необходимо проводить с использованием термокамеры, где для каждой установленной температуры необходимо перебрать все доступные значения калибровочных кодов REScode<NR:0> и BJT<NB:0>. Затем путем построения полученных температурных зависимостей опорного напряжения VREF для всех кодов калибровки выбрать необходимые коды REScode<NR:0> и BJT<NB:0> при которых полученные температурные коэффициенты минимальны. Увеличение размеров приборов на фиг.3 приводит к уменьшению влияния эффектов рассогласования элементов. При этом полученные средние коды калибровки по нескольким образцам, согласно предыдущему алгоритму, становится возможным применить для всех устройств на изготовленной пластине.

В блоке 9 реализована схема запуска, задающая начальный ток в токовое зеркало при подаче питания на схему, обеспечивающая стабильность включения источника опорного напряжения при любых внешних условиях. На фиг.3 и фиг.1 напряжения питания обозначены как VDD, на фиг.2. как VCC. На фиг.3 напряжение земли обозначено как VSS.

Устройство состоит из десяти блоков

1. основной усилительный каскад с общим эмиттером;

2. диод;

3. основное токовое зеркало;

4. правая ветвь токового зеркала;

5. левая ветвь токового зеркала;

6. выходной каскад;

7. тримминга резистора;

8. формирования напряжения смещения;

9. запуска;

10. тримминга токового зеркала. Устройство работает следующим образом:

При подаче напряжения питания VDD и задании потенциала земли VSS в блоке запуска 9 через ток ограничивающий резистор R1 начинает протекать стартовый ток. Ток протекает через составной биполярный транзистор Q20 в диодном включении, между базой и коллектором которого расположен транзистор Q22 по схеме компенсации тока базы и формирует напряжения Vd и Vbn0. Стартовый ток повторяется на коллекторе транзистора Q21 с токоограничивающим резистором R2, в сети N2 и также в коллекторе согласованного транзистора Q16 блока напряжения смещения 8. Рост напряжения питания VDD начинает понижать напряжение в сети N2 блока запуска 9 и повышать значения напряжений Vd и Vbn0. Понижение напряжения в сети N2 блоком запуска 9 приводит к протеканию тока в блоке диода 2 и токовом зеркале 3, что приводит к открытию составного диода Q8, Q9,Q5. Повышение напряжения Vbn0 происходит до определенного уровня после чего наступает его стабилизация. Данное напряжение позволяет сформировать опорный ток для блока смещения 8 в котором происходит формирование напряжения смещения Vbp2, путем пропускания этого тока через последовательно включенные pnp транзисторы Q14 и Q15 в диодном включении.

После выхода на режим основного усилительного каскада с общим эмиттером 1, за счет обратной связи в цепи:

каскад с общим эмиттером, выполненный на транзисторе Q0 с стабилизирующим транзистором Q4, смещенным напряжением Vd, и последовательно соединенными резистором R3 и емкостью С1 в обратной связи;

токовое зеркало 3, состоящее из транзисторов Q6-Q13, а так же транзисторов Q17-Q19, соединенных с токовым зеркалом через сеть itrim, смещение которых задано напряжением Vbp, в зависимости от кода калибровки BJT<2:0>, который открывает или закрывает соответствующие транзисторы КМОП-ключами МОП транзисторов М1-М3 в блоке тримминга токового зеркала 10;

транзистор Q2 правой ветви токового зеркала 4;

транзистор Q1 левой ветви токового зеркала 5;

база транзистора Q0

происходит задание и стабилизация тока, протекающего через транзисторы Q1 и Q2.

Отметим, что выбор габаритов транзистора Q0 осуществляется из условия достаточности коэффициента усиления схемы основного усилительного каскада с общим эмиттером - 1, построенной на основе этого транзистора Q0 и ее способности обеспечивать равенство токов, протекающих через транзисторы Q1 и Q2. Выбор габаритов транзистора Q4, который работает по схеме эмиттерного повторителя, осуществляется из условия стабилизации напряжения на его эмиттере и уменьшения влияния эффекта Эрли транзистора Q0.

Поскольку базы транзисторов Q1 и Q2 соединены электрически, напряжение база-эмиттер транзистора Q1 равно напряжению база-эмиттер транзистора Q2, выполненного в диодном включении, плюс напряжение, падающее на резисторе R4 со стороны эмиттера транзистора Q2. Данное обстоятельство позволяет получить РТАТ ток с положительным температурным коэффициентом, по аналогии с классической схемой на фиг.1., подробный формульный вывод которой был рассмотрен ранее, т.е. величина тока увеличивается с ростом температуры. Учитывая, что транзисторы Q10, Q7, Q12 топологически одинаковы, сформированный основным токовым зеркалом 3 ток через транзисторы Q1 и Q2, точно повторяется как на коллекторах транзисторов Q10 и Q7 так и на коллекторе транзистора Q12, поскольку на всех базах транзисторов Q10, Q7 Q12 задано одинаковое напряжение Vbp. Данный ток с коллектора транзистора Q12 поступает на выходной каскад 6, состоящий из транзистора Q3 в диодном включении, резистора R5 и блок тримминга резисторов 7. Транзистор Q3 по габаритам идентичный транзистору Q1, но выполнен в диодном включении, топологически согласован с транзисторами Q1 Q2. Согласование транзисторов Q1,Q2,Q3 выполнено в виде двумерного массива с общим центром, обеспечивающим высокую степень симметрии, по типу перекрестных связей (cross-coupled).

Ток с положительной температурной зависимостью, проходя через резисторы R5 и R6-R11, в зависимости от кода калибровки RES<4:0>, который открывает или закрывает соответствующие транзисторы КМОП-ключами МОП транзисторов М4-М8, создает падение напряжения с положительным температурным коэффициентом, поскольку резисторы имеют минимальный температурную зависимость, а ток коллекторов транзисторов Q12 и Q13 - положительную температурную зависимость. Ширины транзисторов М1-М3 выбираются таким образом, чтобы сопротивление их каналов в открытом состоянии обеспечивало двоичную взвешенность токов транзисторов Q17-Q19. Ширины транзисторов М4-М8 выбираются таким образом, чтобы собственные сопротивления их каналов в открытом состоянии были достаточно малы для шунтирования параллельно включенных им резисторов R7-R11 и обеспечения двоичной взвешенности этих резисторов. Подробные рекомендации по подбору резисторов R4-R11 приведены в [1]. Резистор R3 и емкость С1 выбираются из условия обеспечения достаточного запаса по фазе цепи обратной связи, что приводит к стабильной работе схемы и отсутствия колебательных процессов в ее внутренних цепях. Резисторы R1-R2 выбираются из условия ограничения тока схемы запуска - 9. В то же время напряжение на транзисторе Q3 в диодном включении в выходном каскаде 6 имеет температурную зависимость с отрицательным температурным коэффициентом. Подбирая соотношение резисторов R4 в блоках правой ветви токового зеркала 4, R5 - выходном каскаде 6 и R6-R11 - тримминге резисторов 7, а также добавляя или убавляя ток в токовом зеркале 3 посредством блока тримминга токового зеркала 10, возможно сформировать выходное напряжение VREF с температурным коэффициентом близким к нулю, в первом приближении не зависящим от температуры.

При подборе транзисторов Q5 Q14, Q15, Q16, Q20, Q21, Q22 руководствуются принципом, изложенным в [1]. Отметим, что выбор габаритов транзисторов Q20, Q21, Q22 осуществляется из условия достаточности стартового тока в сети N2 для запуска схемы в заданном температурном диапазоне и в заданном диапазоне напряжений питания. Выбор габаритов транзисторов Q14, Q15, Q16 осуществляется исходя из допустимого диапазона изменений напряжения Vbp2, при котором транзисторы Q10, Q8, Q7, Q12, остаются в активном режиме. Выбор габаритов транзистора Q5 осуществляется, исходя из достаточности компенсации токов баз транзисторов QB, Q7, Q10, Q12.

Из приведенного описания работы устройства видно, что каждый из десяти обозначенных блоков имеет свое уникальное функционально назначение. Совокупность этих функциональных назначений позволяет устройству в целом решать задачу формирования эталонного напряжения VREF с минимальной температурной зависимостью. Конструктивно все блоки соединены между собой электрически через соответствующие электрические сети, обозначенные на схеме соответствующими линиями. Над некоторыми сетями присутствуют метки - буквенно-цифровые обозначения, к примеру: N2, Vbn0, Vd, …, см. фиг. 3. Если одна или несколько сетей имеют одинаковые метки, то это означает, что эти сети соединены электрически, даже если на схеме отсутствует сеть, которая обозначает это соединение. Названия меток начинающихся с символа «V» одновременно обозначает и название напряжения в этой электрической сети, к примеру: Vbp, Vbp2, …, см. фиг.3. Данный подход к обозначению меток является общепринятым и используется для одновременного обозначения напряжения сети и определения этого напряжения, а также электрических соединений на схеме.

Блок основного усилительного каскада с общим эмиттером 1 соединен базой транзистора Q0 с коллектором транзистора Q1 блока левой ветви токового зеркала 5 и блоком токового зеркала 3 путем соединения с коллектором транзистора Q11, эмиттером с сетью земли VSS, а коллектором с эмиттером транзистора Q4, транзистор Q4 коллектором соединен через сеть N2 с базой транзистора Q5 блока диода 2, базой с блоком запуска 9, база транзистора Q0 подключена к последовательному соединению сопротивления R3 емкости С1 которые соединены с коллектором транзистора Q4 посредством электрических сетей, обозначенных на фиг.3 соответствующими линиями.

Блок диода 2 соединен базой транзистора Q5 через сеть N2 с коллектором транзистора Q4 блока основного усилительного каскада 1 и коллектором транзистора Q9 блока токового зеркала 3, коллектором транзистор Q5 соединен с сетью земли VSS, а эмиттером с токовым зеркалом 3 посредством электрических сетей, обозначенных на фиг.3 соответствующими линиями.

Блок основного токового зеркала 3 соединен базами транзисторов Q8, Q7, Q12, Q10 с эмиттером транзистора Q5 блока диода 2, блоком правой ветви токового зеркала 4, блоком левой ветви токового зеркала 5, блоком выходного каскада 6, блоком тримминга токового зеркала 10 через сеть itrim, при этом коллектор транзистора Q11 соединен с базой транзистора Q0, коллектор транзистора Q6 соединен с коллектором транзистора Q2, коллектор транзистора Q13 соединен с резистором R5, транзистор Q9 соединен с базой транзистора Q5 через сеть N2, при этом коллекторы транзисторов Q10, Q8, Q7 и Q12 соединяют с эмиттерами транзисторов Q11, Q9, Q6 и Q13, соответственно, эмиттеры транзисторов Q10, Q8, Q7 и Q12 подключены к напряжению питания VDD, а коллекторы транзисторов Q11 и Q1, а также Q6 и Q2 объединяют попарно, базы транзисторов Q10, Q8, Q7, Q12 соединены через сеть Vbp, базы транзисторов Q11, Q9 Q6 Q13 соединены через сеть Vbp2, а так же посредством электрических сетей, обозначенных на фиг.3 соответствующими линиями.

Блок правой ветви токового зеркала 4 соединен с блоком основного токового зеркала 3, блоком левой ветви токового зеркала 5, при этом базы транзисторов Q1 и Q2 соединены, база и коллектор транзистора Q2 соединены, эмиттер транзистора Q2 соединен с резистором R4, вторым контактом резистор R4, соединен с землей VSS посредством электрических сетей, обозначенных на фиг.3 соответствующими линиями.

Блок левой ветви токового зеркала 5 соединен с блоком основного токового зеркала 3, блоком правой ветви токового зеркала 4, эмиттер транзистора Q1 соединен с землей VSS по средствам электрических сетей, обозначенных на фиг. 3 соответствующими линиями.

Блок выходного каскада 6 соединен с блоком тримминга резистора 7, блоком основного токового зеркала 3, где база и коллектор транзистора Q3 соединены, коллектор транзистора Q3 соединен с резистором R5, а эмитером с резистором Re посредством электрических сетей, обозначенных на фиг. 3 соответствующими линиями.

Блок тримминга резистора 7 соединен с блоком выходного каскада 6, резисторы R6 - R11 соединены последовательно, резистор R11 соединен с землей VSS. МОП транзисторы М4 - М8, управляемые напряжениями на затворах RES<4>, RES<3>, RES<2>, RES<1>, RES<0>, шунтируют резисторы R6 - R11 посредством электрических сетей, обозначенных на фиг.3 соответствующими линиями.

Блок напряжения смещения 8 соединен с блоком основного токового зеркала 3 через сеть Vbp2, блоком запуска 9 через сеть Vbn0, коллектор и база транзистора Q14 объединены, коллектор и база транзистора Q15 объединены, эмиттер транзистора Q16 подключен к сети VSS, а эмиттер транзистора Q14 к напряжению питания VDD, коллектор транзистора Q14 соединен с эмиттером транзистора Q15, а коллектор транзистора Q15 с коллектором транзистора Q15 транзисторы Q14 - Q16 соединены последовательно, по средствам электрических сетей, обозначенных на фиг. 3 соответствующими линиями.

Блок запуска 9, соединен с блоком диода 2 через сеть N2, с блоком напряжения смещения 8 через сеть Vbn0, с блоком основного усилительного каскада с общим эмиттером 1 через сеть Vd, резистор R1 соединен с питанием VDD и базой транзистора Q22 и коллектором транзистора Q20, базы транзисторов Q20 и Q21 объединены и соединены с эмиттером транзистора Q22, коллектор транзистора Q22 подключен к напряжению питания VDD, эмиттер транзистора Q21 соединен с резистором R2, вторым контактом резистор соединен с эмиттером транзистора Q20, сетью земли VSS и посредством электрических сетей, обозначенных на фиг. 3 соответствующими линиями.

Блок тримминга токового зеркала 10 соединен с блоком токового зеркала 3 через сети itrim и Vbp, базы транзисторов Q17, Q1Q, Q19 соединены через сеть Vbp, коллекторы транзисторов Q17, Q18 Q19 подключены к сети itrim, стоки МОП транзисторов М1,М2,М3 управляемые напряжениями на затворах BJT<2>, BJT<1>, BJT<0>, соответственно, соединены с эмиттерами соответствующих транзисторов Q17, Q1Q, Q19 по средствам электрических сетей, обозначенных на фиг. 3 соответствующими линиями.

Список использованных источников

1. Behzad Razavi, Design of Analog CMOS Integrated Circuits, 2nd ed. (Boston: McGraw-Hill, 2017)

2. Sen-Wen Hsiao, Yen-Chih Huang and David Liang, "A 1.5-V 1 O-ppm/°C 2nd-Order Curvature-Compensated CMOS Bandgap Reference with Trimming",IEEE International Symposium on Circuits and Systems (ISCAS), pp.565-568, june 2006

3. Kin Keung Lau, "A 7μA 1.6ppm/°C bandgap design realizable in CMOS process", 2017 IEEE International Symposium on Circuits and Systems (ISCAS), May 2017

4. Quanwang Liu, Bo Zhang, Shaowei Zhen, Weidong Xue and Ming Qiao, "A 2.6 ppm/°C 2.5 V Piece-Wise Compensated Bandgap Reference with Low Beta Bipolar", Electronics, May 2019

5. Kapil Jainwal, Mukul Sarkar and Kushal Shahz, "Analysis and validation of low-frequency noise reduction in MOSFET circuits using variable duty cycle switched biasing", IEEE Journal of the Electron Devices Society, pp.420-431, February 2018

6. Guang Ge, Cheng Zhang, Gian Hoogzaad, and Kofi A. A. Makinwa, "A Single-Trim CMOS Bandgap Reference With a Inaccuracy of 0.15% From 40 С to 125 C", IEEE International Solid-State Circuits Conference - (ISSCC), March 2010

7. Steven Herbst, "A Low-Noise Bandgap Voltage Reference Employing Dynamic Element Matching", Massachusetts Institute Of Technology, September 2011

8. Johan F. WitteKofi A. A. MakinwaJohan H. Huijsing "Dynamic Offset Compensated CMOS Amplifiers", 2009

9. M. Gunawan; G.C.M. Meijer; J. Fonderie; J.H. Huijsing, "A Curvature-Corrected Low-Voltage Bandgap Reference", IEEE Journal of Solid-State Circuits,pp.667-670, June 1993

10. D. Hilbiber, "A New Semiconductor Voltage Standard," ISSCC Dig. of Tech. Papers, pp.32-33, February 1964.

11. Foundation of rf CMOS and SiGe BiCMOS technologies - J.S. Dunn, IBM J. Res. & Dev., Vol.47, No. 2/3, March/May 2003, p.101-138.

12. SiGe HBT Technology: A New Contender for Si-Based RF and Microwave Circuit Applications - John D. Cressler, IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, May 1998, p.572~589.

13. Transistor Noise in SiGe HBT RF Technology - Niu, Gressler, e.a., Journal of Solid-State Circuits, Sept. 2001, p.1424 ~ 1427.

14. Sub-Micron Silicon RF 1С Technologies - D.K. Lovelace, e.a, 1998 IEEE MTT-S Digest, p.1859-1862.

15. Using SiGe in a CMOS World, Jakob Jongsma / Manager RF Design, Bipolar Arbeitskreis Unterpremstatten, 23 Oct 2003

16. Accelerating Monte Carlo Analysis at Advanced Nodes San Jose CA USA Jan. 2016 [online] Available: https://www.cadence.com/content/dam/cadence-www/global/en_US/documents/tools/custom-ic-analog-rf-design/monte-carlo-analysis-at-advanced-nodes-wp.pdf.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНТУР ДИСКРЕТНОГО СЧИТЫВАНИЯ (ВАРИАНТЫ) | 2005 |

|

RU2297052C1 |

| ИНВЕРТОР НАПРЯЖЕНИЯ И СПОСОБ УПРАВЛЕНИЯ ТАКИМ ИНВЕРТОРОМ | 2011 |

|

RU2567738C2 |

| КОМБИНАЦИЯ ДЕТЕКТОРА И ЧАСТОТНО-ИЗБИРАТЕЛЬНОГО ФИЛЬТРА | 1993 |

|

RU2124276C1 |

| РЕГУЛЯТОР МОЩНОСТИ С УЛУЧШЕННОЙ УСТОЙЧИВОСТЬЮ К ПУЛЬСАЦИЯМ | 2003 |

|

RU2319194C2 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ С КАЛИБРОВКОЙ ВЫХОДНОГО НАПРЯЖЕНИЯ | 2019 |

|

RU2715215C1 |

| ПАРАЛЛЕЛЬНЫЕ АПЕРИОДИЧЕСКИЕ УПЧ | 1993 |

|

RU2118063C1 |

| РЕГУЛЯТОР МОЩНОСТИ С УЛУЧШЕННОЙ ЗАЩИТОЙ ОТ ДИСБАЛАНСА ИНДУКТИВНОЙ НАГРУЗКИ | 2003 |

|

RU2310295C2 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2021 |

|

RU2767980C1 |

| УСОВЕРШЕНСТВОВАННЫЙ РЕГУЛЯТОР МОЩНОСТИ | 2003 |

|

RU2308821C2 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ТОКОВОЙ ОБРАТНОЙ СВЯЗЬЮ | 2018 |

|

RU2683502C1 |

Изобретение относится к области электроники и может быть применено в составе микросхем аналогово-цифровых и цифро-аналоговых преобразователей, аппаратуры радиосвязи и радиолокации, высокоточной измерительной аппаратуры, работающей в широком температурном диапазоне, требующей наличия прецизионных источников опорного напряжения с низким уровнем низкочастотных фликкер-шумов. Технический результат: обеспечение значительной компенсации нелинейности температурного коэффициента в расширенном температурном диапазоне, расширение диапазона питающих напряжений, обеспечение стабильности запуска схемы, достижение низкого уровня низкочастотных фликкер-шумов. Сущность: схемотехническое решение выполнено на биполярных транзисторах. В схеме реализованы алгоритмов калибровок, позволяющих значительно уменьшить нелинейности температурного коэффициента в широком температурном диапазоне. 13 ил., 1 пр.

Малошумящий источник опорного напряжения, содержащий основной усилительный каскад с общим эмиттером 1, выполненный на npn транзисторе Q0, подключенный к основному токовому зеркалу 3, выполненному на биполярных pnp транзисторах Q7, Q8, Q10, Q12 с объединенными базами, токи которых, установленные за счет основного усилительного каскада 1, формирующего напряжение Vbp на их базах, поступают на коллекторы двух npn биполярных транзисторов Q1 и Q2 в левой и правой ветвях токового зеркала 5 и 4, соответственно, базы которых объединены, в правой ветви токового зеркала 4 выполнен в диодном включении и соединен со стороны эмиттера с первым контактом не зависящего от температуры резистора R4, а транзистор Q1 в левой ветви токового зеркала 5 включен по схеме каскада с общим эмиттером и своим коллектором подключен к базе основного усилительного каскада с общим эмиттером 1 транзистора Q0, между базой и коллектором которого расположена стабилизирующая емкость С1, формируя, убывающие с ростом температуры, напряжения база-эмиттер транзисторов Q1 и Q2, за счет разных плотностей токов, обусловленных несовпадающими площадями эмиттеров транзисторов Q1 и Q2, разница напряжений база-эмиттер которых растет с ростом температуры, формируя на резисторе R4 ток, пропорциональный абсолютной температуре, который проходя через основное токовое зеркало 3 через транзисторы Q8, Q7, повторяется на транзисторе Q12 и формирует пропорциональный абсолютной температуре ток IPTAT на коллекторе транзистора Q12, при этом эмиттером транзистор Q1 соединяют с сетью VSS, а резистор R4 вторым контактом соединяют с сетью VSS, основной усилительный каскад с общим эмиттером 1, подключен эмиттером транзистора Q0 к потенциалу земли VSS, отличающийся тем, что база транзистора Q0 содержит резистор R3, последовательно подключенный с емкостью С1, а напряжение на коллекторе транзистора Q0 фиксируют, подключенным к коллектору транзистора Q0, эмиттером биполярного npn транзистора Q4, с напряжением смещения базы Vd, включенным по типу эмиттерного повторителя, базой Q4 соединен с блоком запуска 9, а коллектором соединяют с емкостью С1, основное токовое зеркало 3 выполнено в каско дном исполнении с добавлением pnp биполярных транзисторов Q6,Q9, Q11, Q13 с объединенными базами и равными площадями эмиттеров, а также напряжением смещения на их базах Vbp2, при этом коллекторы транзисторов Q10, Q8, Q7 и Q12 соединяют с эмиттерами транзисторов Q11, Q9, Q6 и Q13, соответственно, эмиттеры транзисторов Q10, Q8, Q7 и Q12 подключены к сети VDD, базой транзисторы Q8, Q7, Q12, Q10 соединены с эмиттером транзистора Q5, а коллекторы транзисторов Q11 и Q1, а также Q6 и Q2 объединяют попарно, и добавлением в блоке диода 2 pnp транзистора Q5 с коллектором на потенциале земли VSS, базу транзистора Q5 соединяют через сеть N2 с коллектором транзистора Q4, а также с коллектором транзистора Q9, для компенсации токов баз транзисторов Q7, Q8, Q10, Q12, калибруемого путем добавления тока через сеть itrim при помощи блока тримминга токового зеркала 10, калибруемая часть которого набрана из двоично-взвешенных по площадям эмиттеров набора pnp биполярных транзисторов Q17, Q18, Q19, коллекторы которых соединяют с сетью itrim, базы которых смещают напряжением Vbp с КМОП-ключами МОП-транзисторов М1 М2, М3, подключенными к эмиттерам транзисторов Q17, Q18, Q19, соответственно, и управляемые напряжениями на затворах BJT<2>, BJT<1>, BJT<0>, соответственно, подключенными к сети VDD, площади эмиттеров транзисторов Q17, Q18, Q19 двоично взвешены и равны 16⋅Apnp, 8⋅Apnp и 4⋅Apnp, соответственно, причем площадь эмиттера транзистора Q8 равна 8⋅Apnp, а площади эмиттеров транзисторов Q7, Q10, Q12 и Q17 равны 16⋅Apnp основного токового зеркала 3, где Apnp - минимальная используемая для согласования ряда транзисторов Q17, Q18, Q19, Q7, Q8, Q10, Q12 площадь эмиттера, устройство дополнительно содержит выходной каскад 6, состоящий из npn транзистора Q3 по габаритам идентичного транзистору Q1, но выполненному в диодном включении, и топологически согласованного с транзисторами Q1, Q2, где транзистор Q2, в восемь раза больший по площади эмиттера, чем транзистор Q1, по типу согласования массивов с перекрестными связями cross-couplet, соединенного коллектором с одним контактом резистора R5, а другим контактом резистор соединяют с коллектором транзистора Q13, калибруемого при помощи блока тримминга резистора 7, выходной каскад 6, формирующий выходное эталонное напряжение VREF, посредством тока РТАТ, сформированного на коллекторах транзисторов Q12 и Q13 основного токового зеркала 3, где блок триммингуемых резисторов 7 в эмиттере транзистора Q3, содержит двоично-взвешенный набор резисторов R7, R8, R9, R10, R11 последовательно включенных с резистором R6, подключенных через контакт резистора R11 к потенциалу земли VSS для уменьшения влияния сопротивлений шунтирующих ключей МОП транзисторов М4, М5, М6, М7, М8, топологически согласованных между собой и с резисторами R4 и R5, с шунтирующими их КМОП-ключами МОП транзисторов М4, М5, М6, М7, М8, управляемыми напряжениями на затворах RES<4>, RES<3>, RES<2>, RES<1>, RES<0>, соответственно, устройство дополнительно содержит блок запуска 9, состоящий из ток задающего резистора R1, соединенного с базой транзистора Q22, и с напряжением питанием VDD и определяющего стартовый ток при подаче питания VDD, токового зеркала на npn биполярных транзисторах Q20 Q21, Q22, формирующего опорные напряжения Vd и Vbn0, диодную часть которого, состоящую из транзисторов Q20 и Q22, выполняют по схеме компенсации тока базы, где коллектор транзистора Q22 соединен с напряжением питанием VDD, транзистор Q20 выполнен в диодном включении, база транзистора Q22 соединена коллектором транзистора Q20, эмиттер соединен с объединенными базами транзисторов Q20 и Q21, отраженный ток которого с коллектора транзистора Q21, с расположенным в эмиттере резисторе R2, протекает через сеть N2 в блоке запуска 9 и понижает напряжение в электрически соединенном с блоком запуска 9 сети N2 диода 2 токового зеркала 3, тем самым выводя всю схему из устойчивого выключенного состояния, при этом другим контактом резистор R2, а также эмиттером транзистор Q20 подключают к потенциалу земли VSS, а также устройство содержит блок формирования напряжения смещения 8, формирующий напряжение Vbp2 на базах транзисторов Q11, Q9, Q6, Q13 основного токового зеркала 3, формирующегося из отраженного тока блока запуска 9 при помощи напряжения смещения Vbn0, приложенного к базе npn транзистора Q16, на эмиттере которого задан потенциал земли VSS, формирующего напряжение Vbp2 путем пропускания заданного тока через два последовательно включенных биполярных pnp транзистора Q14 и Q15 в диодном включении к коллектору транзистора Q16, где коллектор транзистора Q14 подключают к эмиттеру транзистора Q15, коллектор транзистора Q15 подключают к коллектору транзистора Q16, а эмиттер транзистора Q14 соединяют с напряжением питания VDD.

| АВИАЦИОННЫЙ ТРЕНАЖЕР | 0 |

|

SU195898A1 |

| Источник опорного напряжения | 1990 |

|

SU1838814A3 |

| US 11320851 B1, 03.05.2022 | |||

| WO 2009021043 A1, 12.02.2009 | |||

| US 5399960 A1, 21.03.1995 | |||

| CN 103729009 A, 16.04.2014. | |||

Авторы

Даты

2024-02-07—Публикация

2023-06-08—Подача