Изобретение относится к электронике интегральных микросхем (ИМС) и может быть использовано в составе радиоэлектронной аппаратуры наземного, морского и аэрокосмического базирования для защиты от воздействия тяжелых заряженных частиц (ТЗЧ), высокоэнергетичных протонов (ВЭП), импульсного ионизирующего излучения, пучкового оружия.

Техническим результатом является повышение надежности работы аппаратуры при воздействии ТЗЧ, в частности существенное повышение детектирования возникновения тиристорного эффекта (ТЭ) в защищаемой аппаратуре.

Известно устройство защиты ИМС от ТЭ, представленное в патенте № RU 2661282 «Устройство защиты полупроводниковых микросборок от тиристорного эффекта».

Устройство содержит токозадающий резистор, датчик тока, времязадающий одновибратор, инвертирующий операционный усилитель и транзисторный ключ.

Способ работы устройства заключается в измерении тока питания ИМС (Iизм), сравнивании измеренного тока (Iизм) ИМС с максимальным током (Iмах) для указанной ИМС, и отключении тока питания ИМС на задаваемое время отключения (Тоткл) при превышении измеренного тока максимально допустимого тока ИМС.

К недостаткам способа и устройства следует отнести низкую надежность защиты программируемых интегральных микросхем, например микроконтроллеров (МК), от возникающих ТЭ вследствие влияния ТЗЧ из-за выбора неоптимального критерия определения возникновения ТЭ в ИМС.

В указанном способе и устройстве критерием возникновения ТЭ считается превышение измеренного тока над максимальным током ИМС, в то время, как фактический ток ИМС даже при отсутствии ТЭ существенно изменяется в зависимости от условий и режима работы ИМС. В частности, от температуры, нагрузок ИМС, а также от изменения режима работы, определяемом алгоритмом программного обеспечения (например, включение АЦП или ШИМ преобразований повышают потребляемый ток на 10-20%).

Кроме того, импульсный ток при включении ИМС превышает ток штатной работы ИМС не менее, чем в 1,5-2,5 раз, что требует существенного увеличения, задаваемого при настройке максимального тока, а, следовательно, существенно снижая защитные свойства устройства.

При этом, добавка тока, вызванная возникновением в ИМС тиристорного эффекта (ΔIтэ) может быть сравнительно небольшой, (5-15 мА), когда площадь ИМС, на которой возник тиристорный эффект невелика и занимает незначительную часть общей площади ИМС, а диапазон изменения штатного тока ИМС существенно превышает значение ΔIтэ, что не позволяет выявить возникновение ТЭ.

Дополнительно следует отметить, что увеличение тока ИМС может быть:

а) длительным с плавным изменением при изменении температуры ИМС;

б) периодически изменяющимся при неизменном среднем уровне при выполнении микроконтроллером действий согласно алгоритму программного обеспечения (ПО) (например, с периодичностью 5-30 мс при преобразованиях АЦП);

в) кратковременным (не более 1-15 мс) при возникновении внешних помех, либо работы МК по алгоритму ПО, либо при подаче питания на МК;

г) длительным с резким нарастанием при возникновении ТЭ, вплоть до принудительного отключения тока ИМС устройством защиты;

Как видно из проведенного анализа, увеличение тока в вариантах, а), б) и в) вызваны не ТЭ и не требуют отключения питания ИМС, и только в варианте г) рост тока вызван возникновением ТЭ и требует отключения питания ИМС на время Тоткл. Тоткл, определяется временем рассасывания заряда на участках ИМС, на которых возник ТЭ, и определяется экспериментально по результатам испытаний.

Описанный в патенте №2661282 способ не реагирует на различную природу возникновения скачков тока, а, следовательно, допускает отключение питания ИМС при отсутствии ТЭ (варианты, а), б) и в) или, наоборот, не отключает питания при возникновении ТЭ (вариант г).

В качестве прототипа выбрано устройство защиты от тиристорного эффекта фирмы «НПК Технологический центр», реализованное в виде микросхемы 1469ТК025 и способ его работы.

Данный способ защиты интегральных микросхем (ИМС) от тиристорного эффекта (ТЭ), заключается в измерении тока питания ИМС (Iизм), сравнении Iизм с максимально допустимым током (Iмах) для указанной ИМС, ограничении тока питания ИМС на уровне Iмах при превышении током Iизм тока Iмах на время ограничения Тогр, отключении ограничения тока, если на момент Тогр ток питания снизился ниже уровня Iмах, или полном отключении тока питания, если на момент Тогр измеренный ток Iизм превышает Iмах. При этом, детектирование факта возникновения ТЭ определяется по превышению измеренного над максимально допустимым током ИМС, что не соответствует действительности.

Устройство для реализации способа содержит токоизмерительный резистор, компаратор превышения тока с гистерезисом, времязадающий таймер ограничения тока, времязадающий таймер полного отключения тока питания ИМС, транзисторный ключ и схему управления логикой работы последнего.

Очевидно, что преимуществом данного способа по сравнению с аналогом является несколько более высокая надежность детектирования возникновения ТЭ, обусловленная учетом части отличий поведения устройства защиты (УЗ) в варианте в) от остальных вариантов, когда УЗ не отключает питание ИМС, а только ограничивает его ток при запуске МК и различных кратковременных помехах.

Кроме того, устройство реализующее способ, выполнено в виде малогабаритной микросхемы, занимающей вчетверо меньшую площадь, чем у аналога при лучшем качестве детектирования наличия ТЭ.

К недостатку прототипа, как и аналога, следует отнести недостаточную чувствительность детектирования возникновения ТЭ, а, следовательно, недостаточную надежность защиты ИМС от воздействия ТЗЧ, в частности, микроконтроллеров МК из-за отсутствия учета условий работы ИМС.

Как и у аналога, отключение тока питания производится при превышении максимально допустимого тока ИМС, а не при незначительных по величине набросов тока из-за возникновения ТЭ. Иначе говоря, УЗ работает с учетом воздействий в соответствии с условиями варианта в), но, как и аналог, не учитывает условия работы ИМС в соответствии с вариантами, а), б) и г).

Описанные в прототипе способ и устройство не оптимальны по критерию детектирования возникновения ТЭ в ИМС и не реагируют на различную природу увеличения тока от изменения температуры в аппаратуре, работы МК по алгоритму ПО, от возникновения ТЭ на небольшой части кристалла, а не всей его площади, а, следовательно, допускает отключение питания ИМС при отсутствии ТЭ в вариантах, а), б), или не отключает питание при возникновении ТЭ в варианте г).

Так, согласно результатам испытаний в СПЭЛС микроконтроллера 1986ВЕ92 совместно с устройством защиты, приведенном в прототипе, (ПРОТОКОЛ СПЭЛС ЖКНЮ.ИЦ.01.0001-ПРЧ, Москва, 2018 г), ток питания МК при тактовой частоте 80 МГц и средней загрузке согласно ПО (Iизм=100-150) мА и периодически увеличивается на (10-15) мА при работающим АЦП), в то время, как добавка тока при возникновении ТЭ может быть всего 5-15 мА, что делает защиту ИМС неэффективной и, как следствие, может привести и реально приводит к выходу из строя МК при воздействии ТЗЧ.

Задачей, на решение которой направлено создание настоящего изобретения, является повышение чувствительности детектирования факта возникновения ТЭ в ИМС для способа и устройства защиты программируемых ИМС в зависимости от причин изменения тока, а, следовательно, надежности радиоэлектронной аппаратуры, содержащей программируемые микросхемы (МК, память, …) при воздействии ТЗЧ.

Для решения поставленной задачи, способ защиты программируемых интегральных микросхем, например микроконтроллеров, от тиристорного эффекта, заключающийся в измерении тока питания ИМС (Iизм), детектировании факта возникновения тиристорного эффекта, ограничении тока ИМС на уровне максимально допустимого тока для указанной ИМС (Iмах) на время ограничения (Тогр), определяемое продолжительностью безотказной работы ИМС при возникновении ТЭ, отключении ограничения тока, если на момент Тогр ток питания снизился ниже уровня Iмах, или полном отключении тока питания на время рассасывания заряда от возникшего ТЭ (Тоткл), если на момент Тогр тиристорный эффект не устранился, дополнен операциями интегрирования тока Iизм за 3-5 циклов работы ИМС в соответствии с алгоритмом программного обеспечения (ПО) (Тпо) с получением значения эффективного значения тока (Iэф) за период интегрирования Тэф, интегрирования тока Iизм за несколько (3-5) циклов Тэф, с получением значения тока Iпред за предыдущий отрезок времени на участке времени Тпред, предшествующим возникновению тиристорного эффекта, детектирования факта возникновения тиристорного эффекта по превышении разности токов (Iэф - Iпред) значению добавки тока питания от возникновения тиристорного эффекта (ΔIтэ мин), при этом значение ΔIтэ мин определено по результатам испытаний ИМС на воздействие ТЗЧ, ограничении и отключении тока питания ИМС при детектировании факта возникновения ТЭ.

Очевидно, что ограничение и отключение питания в предлагаемом способе при превышении максимально допустимого тока, как в прототипе (порядка 100-150 мА), используется, как правило, в качестве подстраховки при крайних условиях работы (максимальная загрузка МК, высокая температура, расширенная площадь кристалла, занятая тиристорным эффектом.

Основной вариант защиты заключается в отключении тока питания ИМС при детектировании факта возникновения ТЭ по превышении разности текущего и предшествовавшего значения тока (Iэф - Iпред) > ΔIтэ мин = (5-15) мА, при этом сравниваемые величины токов для предлагаемого способа и прототипа отличаются на порядок (100-150 и 5-15 мА), а, следовательно, чувствительность определения факта возникновения ТЭ и надежность защиты повышается на порядок.

Операция ограничения тока позволяет исключить ошибочные отключения тока питания при воздействии кратковременных импульсных помех, не являющихся признаком возникновения ТЭ.

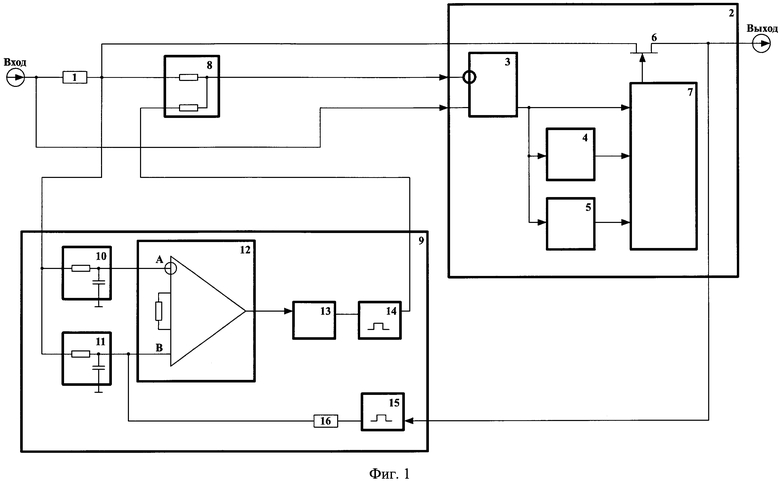

Для устройства защиты программируемых интегральных микросхем (ИМС), например микроконтроллеров, от тиристорного эффекта (ТЭ), реализующего предложенный способ, поставленная задача решается тем, что устройство защиты, содержащее токоизмерительный резистор и устройство защиты от превышения максимального тока (УЗМТ), включающее компаратор превышения тока, таймер ограничения тока, таймер отключения тока, транзистор и устройство управления транзистором, первый вывод токоизмерительного резистора является входом УЗ ИМС и подключен к положительному входу компаратора превышения тока, второй вывод токоизмерительного резистора подключен к стоку транзистора, выход компаратора превышения тока подключен ко входу устройства управления транзистором, входу таймера ограничения тока и входу таймера отключения тока, выходы которых связаны с входами устройства управления транзистором, а выход устройства управления транзистором подключен к затвору транзистора, исток которого является выходом УЗ ИМС, дополнено резистивным сумматором напряжений и устройством выделения тока тиристорного эффекта (УВТЭ), включающим в себя первый и второй интеграторы значений тока, усилитель разности токов (УРТ), компаратор тиристорного эффекта (КТЭ), таймер удержания факта ТЭ (ТУФ), при этом входы первого и второго интеграторов значений тока подключены к второму выводу токоизмерительного резистора, выходы указанных интеграторов значений тока подключены к положительному и отрицательному, соответственно, входам УРТ, выход УРТ подключен к входу КТЭ, выход которого подключен к входу ТУФ, выход ТУФ и второй вывод токоизмерительного резистора подключены к входам резистивного сумматора напряжений, выход которого подключен к отрицательному входу компаратора превышения тока.

Предусмотрено, что устройство дополнительно содержит таймер блокировки (ТБ) УВТЭ. Вход таймера блокировки ТБ УВТЭ подключен к выходу УЗ, а выход через масштабирующий резистор подключен к положительному входу УРТ.

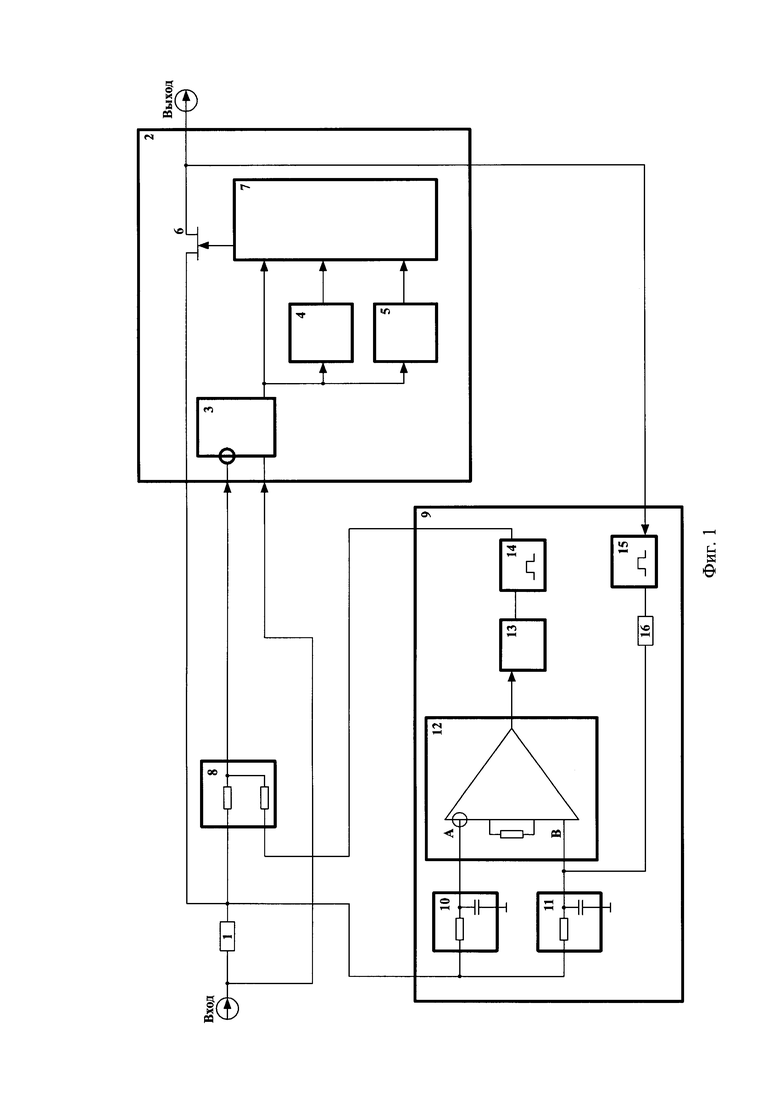

Структурная схема устройства защиты приведена на фигуре 1 и содержит следующие элементы:

1 - токоизмерительный резистор;

2 - устройство защиты максимального тока (УЗМТ);

3 - компаратор превышения тока;

4 - таймер ограничения тока;

5 - таймер отключения тока;

6 - полевой транзистор;

7 - устройство управления транзистором;

8 - резистивный сумматор напряжений;

9 - устройство выделения тока тиристорного эффекта (УВТЭ);

10 - первый интегратор значений тока;

11 - второй интегратор значений тока;

12 - усилитель разности токов (УРТ);

13 - компаратор тиристорного эффекта (КТЭ)

14 - таймер удержания факта ТЭ (ТУФ);

15 - таймер блокировки УВТЭ (ТБ);

16 - масштабирующий резистор.

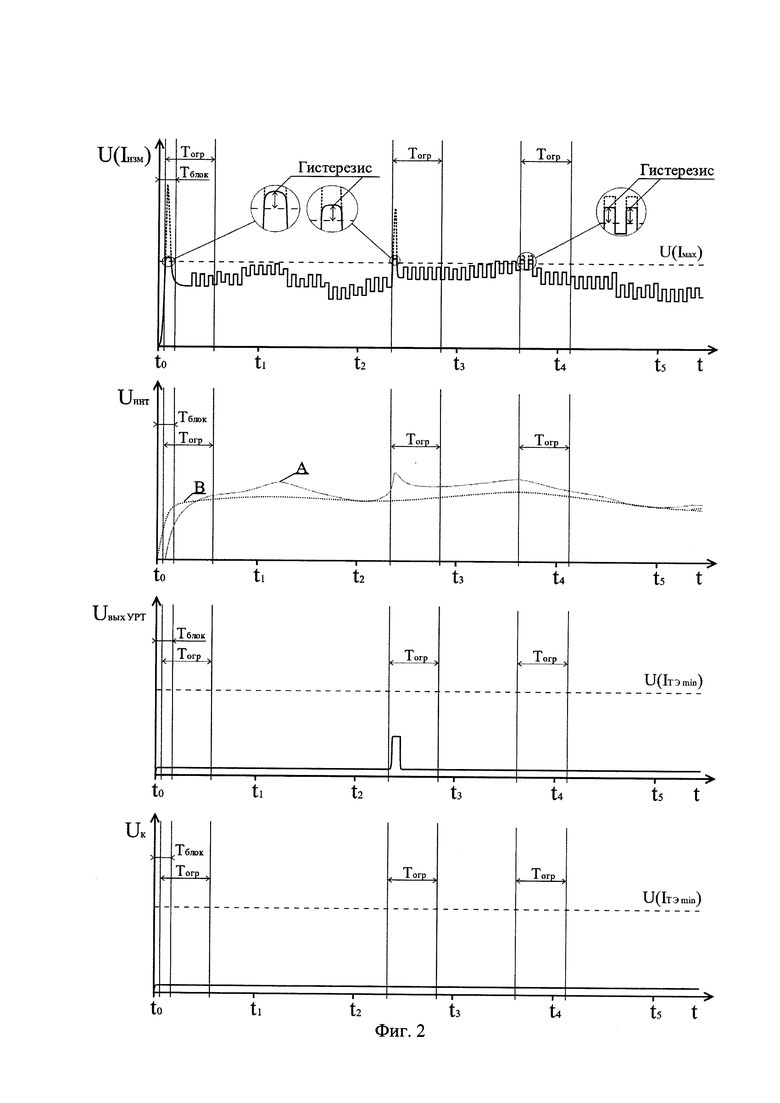

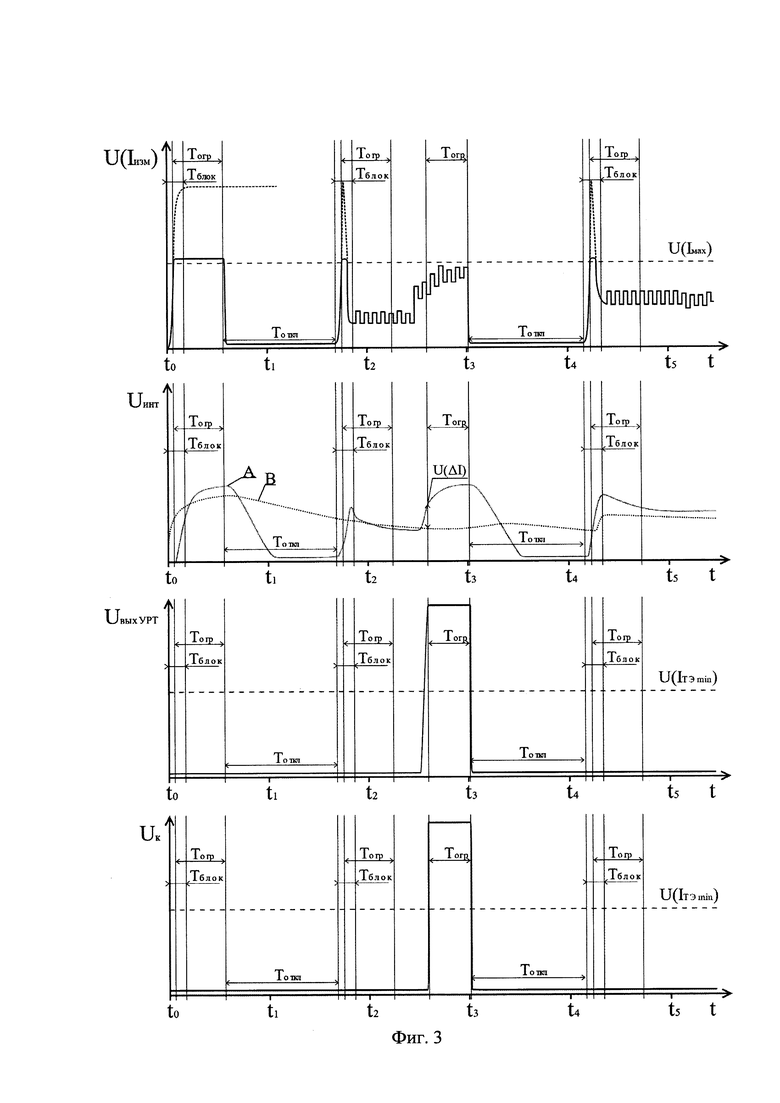

На фигуре 2 приведена временная диаграмма работы УЗ при отсутствии ТЭ, а на фигуре 3 диаграмма работы УЗ при возникновении в ИМС ТЭ, либо превышении максимального тока.

Предлагаемый СПОСОБ при отсутствии ТЭ функционирует следующим образом:

- на токоизмерительном резисторе 1 (см. Фиг. 1) выделяется напряжение, пропорциональное фактическому току питания ИМС - Iизм;

- при превышении током Iизм значения максимально допустимого для ИМС тока, по любой причине, в том числе и при возникновении факта ТЭ,

вначале предусмотрено ограничение тока на максимальном уровне на время Тогр,

а затем, если к моменту окончания времени Тогр не снизится до величины меньшей, чем максимально допустимый ток, полностью отключается на период Тоткл, обесточивая ИМС и обеспечивая защиту ИМС от максимального тока.

Защита ИМС при возникновения ТЭ осуществляется следующим образом:

- измеренный ток I изм, после подачи питания на ИМС, интегрируется за несколько (3-5) циклов работы программного обеспечения (ПО) для оценки эффективного (усредненного) тока ИМС (Iэф) за последний период Тэфф, работы (в котором возможно наличие части тока, обусловленной наличием тиристорного эффекта, но отсутствуют изменения тока, вызванные периодическими изменениями последнего в соответствии с отработкой алгоритма ПО и импульсными помехами;

- измеренный ток I изм интегрируется за несколько (3-5) циклов Тэфф для получения значения тока Iтэ в предшествующий период работы ИМС, в котором отсутствует вклад в суммарный ток частей, обусловленных возникшим тиристорным эффектом и работой ИМС по алгоритму ПО;

- определяется разница токов ΔIтэ = Iэфф-Iпред, обусловленная возможным возникновением тиристорного эффекта;

- детектируется возникновение тиристорного эффекта по удовлетворению неравенства при разнице ΔIтэ > ΔIтэ мин, после чего ток питания ИМС ограничивается, а затем полностью отключается на время рассасывания заряда в ИМС.

Расчетные методы определения указанных предельных параметров на настоящее время не обеспечивают удовлетворительных результатов.

Предельные параметры УЗ определяются по результатам испытаний ИМС на воздействие ТЗЧ:

- Тогр должен быть не более времени безопасной работы ИМС при возникновении ТЭ;

- Тоткл должен быть не менее времени рассасывании заряда в ИМС после возникновения ТЭ;

- ΔIтэ мин должно быть не более минимального значения наброса тока от ТЭ при воздействии ТЗЧ на ИМС.

Предлагаемое УСТРОЙСТВО при отсутствии ТЭ работает следующим образом:

- после запуска ИМС напряжение, пропорциональное току питания, через один из резисторов резистивного сумматора напряжений 8 подается на отрицательный вход компаратора превышения тока 3;

- одновременно, через второй вход резистивного сумматора напряжений 8 на отрицательный вход компаратора превышения тока 3 подается сигнал с выхода УВТЭ 9 о возможном возникновении тиристорного эффекта;

- при отсутствии тиристорного эффекта или тока, превышающего максимально допустимый ток для ИМС, УЗМТ 2 выдает на затвор транзистора 6 отпирающее напряжение, транзистор 6 открыт, выдает ток питания на ИМС и обеспечивает штатную работ ИМС;

- при токе ИМС, превышающем Iмах, в УЗМТ 2 срабатывает компаратор превышения тока 3, запуская таймеры ограничения 4 и отключения тока 5, по сигналам которых устройство управления выдает соответствующие сигналы, на транзистор 6, который вначале ограничивает, а затем полностью отключает ток питания от УЗ к ИМС на время рассасывания заряда от ТЭ в ИМС (Тоткл);

- по истечении времени Тоткл устройство управления 7 отпирает транзистор 6, переводя УЗ и ИМС в исходное состояние.

Работа УЗ при возникновении факта ТЭ осуществляется следующим образом:

напряжение с выхода токоизмерительного резистора 1, пропорциональное измеренному току Iизм, интегрируется первым интегратором значений тока 10 с постоянной времени Тогр, обеспечивая на выходе интегратора 10 сигнал Iэф, пропорциональный эффективному (среднему) току, очищенному от импульсных помех и переменной составляющей, полученной в результате работы ИМС по алгоритму ПО. Сигналы с выходов первого и второго интеграторов значений тока, содержащие составляющие токов до начала возникновения и после возникновения тиристорного эффекта, подаются на вход УРТ 12, который осуществляет их вычитание и нормирование, устанавливая на выходе УРТ 12 уровень сигнал, пропорциональный набросу тока от возможного ТЭ (ΔIтэ);

- при возникновении в ИМС тиристорного эффекта, который детектируется компаратором тиристорного эффекта 13 по выполнению неравенства ΔIтэ>ΔIтэ мин, сигнал компаратора тиристорного эффекта 13 о возникновении ТЭ запускает таймер удержания ТЭ 14, поскольку ограничение тока ИМС существенно уменьшает незначительную разницу напряжений до и после возникновения ТЭ;

- сигнал с выхода таймера удержания ТЭ 14 через резистивный сумматор напряжения 8 подается на вход компаратора превышения тока 3, который и осуществляет ограничение, отключение и последующее повторное включение тока питания ИМС по описанной выше методике.

Особо следует остановиться на динамических характеристиках УЗ, включая процесс запуска, ИМС, поясняемых фигурами 2 и 3.

На фиг. 2 показаны временные зоны, характеризующие участок блокировки УВТЭ на время запуска Тблок, в диапазоне времени Т0-Т1, Тогр в том же диапазоне и других участках.

На данной фиг. 2 показаны зависимости от времени напряжений УЗ, пропорциональных измеренному току (U(Iизм)), напряжений на выходе интеграторов (Uинт) эффективного (А) и предшествующего (В) значений токов, напряжения на выходе УРТ (Uвых урт), напряжения на выходе компаратора тиристорного эффекта (Uк).

Пунктирной линией на фиг. 2 в зонах Т0 Т1 и Т2-Т3 показаны значения токов ИМС, если бы ИМС работала без УЗ, т.е. без ограничения тока.

В связи с существенным повышением точности детектирования, от значения (100-150) до (5-15) мА, и соответственно значительной разницы между граничными значениями максимального тока и тока ТЭ, каждый запуск ИМС УВТЭ 9 воспринимает как возникновение ТЭ, что требует блокировки УВТЭ 9 на время запуска.

Указанную блокировку УВТЭ 9 н время запуска осуществляет таймер блокировки 16, который при появлении питания на выходе УЗ блокирует работу УВТЭ 9 на время запуска путем удержания напряжения на выходе интегрирующей цепи на уровне, характерном для отсутствии ТЭ.

Резистор 16 обеспечивает масштабирование напряжения второго интегратора значений тока 11 с минимизацией времени таймера блокировки УВТЭ 15.

На фиг. 3 пунктирной линией в зонах Т0-2, Т1-Т2 и Т4-Т5 показано значение тока в ИМС при отсутствии УЗ. В этих зонах таймер блокировки блокирует работу УВТЭ 9, с последующим переходом в режим ограничения тока из-за превышения максимального тока, а в зоне Т2-Т3 показана работа УЗ при возникновении факта тиристорного эффекта (ΔIтэ>ΔIтэ мин).

Таким образом, предлагаемое решение позволяет, практически, на порядок улучшить чувствительность определения факта возникновения в ИМС тиристорного эффекта, а, следовательно, повысить надежность аппаратуры, содержащей указанные ИМС.

Работоспособность предлагаемого технического решения подтверждена результатами испытаний в СПЭЛС (ПРОТОКОЛЫ СПЭЛС № ЖКНЮ.ИЦ.02.0001-ПРЧ, Москва 2018 г для 1986ВЕ92 и, № ЖКНЮ.ИЦ.03.0001-ПРЧ, Москва, 2019 г для 1986ВЕ1)

На предприятии ЗАО «Орбита» принято решение об использовании предлагаемого технического решения в аппаратуре космической станции «Научно-энергетический модуль НЭМ») Это позволит вместо более стойких, но дорогих микроконтроллеров (МК), требующих дополнительно применения внешних однократно программируемых ПЗУ и ОЗУ, применить сравнительно недорогие нестойкие МК с внутренними флэш-памятью и ОЗУ, а следовательно существенно снизить стоимость космической аппаратуры, уменьшить время разработки схемотехнических и программных решений, снизить его массу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство защиты программируемых микроконтроллеров от тиристорного эффекта | 2020 |

|

RU2749017C1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ОТ ТИРИСТОРНОГО ЭФФЕКТА | 2012 |

|

RU2510893C2 |

| Устройство защиты полупроводниковых микросборок от тиристорного эффекта | 2017 |

|

RU2661282C1 |

| УСТРОЙСТВО ЗАЩИТЫ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ ПРИ ВОЗДЕЙСТВИИ НА НЕЁ ИМПУЛЬСНОГО ИОНИЗИРУЮЩЕГО ИЗЛУЧЕНИЯ | 2015 |

|

RU2589350C1 |

| СПОСОБ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ПРИ ПОПАДАНИИ В НИХ ТЯЖЕЛЫХ ЗАРЯЖЕННЫХ ЧАСТИЦ | 2011 |

|

RU2480898C2 |

| СПОСОБ УПРАВЛЕНИЯ СИСТЕМОЙ ЭЛЕКТРОПИТАНИЯ КОСМИЧЕСКОГО АППАРАТА ПОВЫШЕННОЙ ЖИВУЧЕСТИ | 2016 |

|

RU2636384C1 |

| УСТРОЙСТВО ЗАЩИТЫ ИСТОЧНИКА ПИТАНИЯ ПОСТОЯННОГО ТОКА | 2015 |

|

RU2595270C1 |

| Датчик определения заданного порога тока потребления | 2018 |

|

RU2678718C1 |

| УСТРОЙСТВО ЗАЩИТЫ И КОНТРОЛЯ СОПРОТИВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕКТРИЧЕСКИХ АППАРАТОВ | 2000 |

|

RU2183375C2 |

| УСТРОЙСТВО ОГРАНИЧЕНИЯ МОЩНОСТИ, ПОТРЕБЛЯЕМОЙ НАГРУЗКОЙ ИЗ ПИТАЮЩЕЙ СЕТИ | 1999 |

|

RU2157037C1 |

Изобретение относится к электронике интегральных микросхем (ИМС) и может быть использовано в составе радиоэлектронной аппаратуры для защиты микросхем от воздействия тяжелых заряженных частиц (ТЗЧ), высокоэнергетичных протонов (ВЭП), импульсного ионизирующего излучения, пучкового оружия. Технический результат - повышение в 10-15 раз точности детектирования факта ТЭ и надежности аппаратуры, содержащей программируемые ИМС при воздействии ТЗЧ. Для этого предложен способ, который заключается в измерении тока питания ИМС, ограничении и отключении тока питания ИМС при детектировании факта возникновения ТЭ, а возникновение ТЭ определяется по набросу тока при его возникновении. Устройство защиты (УЗ) ИМС от ТЭ содержит датчик тока, устройство защиты по максимальному току, а также усилитель разности текущего и предшествующего значений токов на двух интеграторах токов, устройство выделения тока ТЭ и таймеры, обеспечивающие требуемый алгоритм работы устройства. 2 н. и 1 з.п. ф-лы, 3 ил.

1. Способ защиты программируемых интегральных микросхем (ИМС) от тиристорного эффекта (ТЭ), заключающийся в измерении тока питания ИМС (Iизм), детектировании факта возникновения тиристорного эффекта, ограничении тока ИМС на уровне максимально допустимого тока для указанной ИМС (Iмах) на время ограничения (Тогр), определяемое продолжительностью безотказной работы ИМС при возникновении ТЭ, отключении ограничения тока, если на момент Тогр ток питания снизился ниже уровня Iмах, или полном отключении тока питания на время рассасывания заряда от возникшего ТЭ (Тоткл), если на момент Тогр тиристорный эффект не устранился, отличающийся тем, что он дополнен операциями интегрирования тока Iизм за 3-5 циклов работы ИМС в соответствии с алгоритмом программного обеспечения (ПО) (Тпо) с получением значения эффективного значения тока (Iэф) за период интегрирования Тэф, интегрирования тока Iизм за несколько (3-5) циклов Тэф с получением значения тока Iпред за предыдущий отрезок времени на участке времени Тпред, предшествующем возникновению тиристорного эффекта, детектирования факта возникновения тиристорного эффекта по превышении разности токов (Iэф - Iпред) значению добавки тока питания от возникновения тиристорного эффекта (ΔIтэ мин), при этом значение ΔIтэ мин определено по результатам испытаний ИМС на воздействие ТЗЧ, ограничение и отключение тока ИМС при детектировании факта возникновения ТЭ.

2. Устройство защиты (УЗ), реализующее способ защиты программируемых интегральных микросхем (ИМС) от тиристорного эффекта (ТЭ), содержащее токоизмерительный резистор и устройство защиты от превышения максимального тока (УЗМТ), включающее компаратор превышения тока, таймер ограничения тока, таймер отключения тока, транзистор и устройство управления транзистором, при этом первый вывод токоизмерительного резистора является входом УЗ ИМС и подключен к положительному входу компаратора превышения тока, второй вывод токоизмерительного резистора подключен к стоку транзистора, выход компаратора превышения тока подключен к входу устройства управления транзистором, входу таймера ограничения тока и входу таймера отключения тока, выходы которых связаны с входами устройства управления транзистором, а выход устройства управления транзистором подключен к затвору транзистора, исток которого является выходом УЗ ИМС, отличающееся тем, что оно дополнено резистивным сумматором напряжений и устройством выделения тока тиристорного эффекта (УВТЭ), включающим в себя первый и второй интеграторы значений тока, усилитель разности токов (УРТ), компаратор тиристорного эффекта (КТЭ), таймер удержания факта ТЭ (ТУФ), при этом входы первого и второго интеграторов значений тока подключены к второму выводу токоизмерительного резистора, выходы указанных интеграторов значений тока подключены к положительному и отрицательному, соответственно, входам УРТ, его выход подключен к входу КТЭ, выход которого подключен к входу ТУФ, а выход ТУФ и второй вывод токоизмерительного резистора подключены к входам резистивного сумматора напряжений, выход которого подключен к отрицательному входу компаратора превышения тока.

3. Устройство защиты по п. 2, отличающееся тем, что оно дополнено таймером блокировки устройства выделения тиристорного эффекта (УВТЭ), вход которого подключен к выходу УЗ, а выход через масштабирующий резистор подключен к положительному входу УРТ.

| Приспособление для отрывания гондолы от аэростата в несчастных случаях и спуска ее на парашюте | 1924 |

|

SU1469A1 |

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ОТ ТИРИСТОРНОГО ЭФФЕКТА | 2012 |

|

RU2510893C2 |

| Устройство для очистки чистительных валиков ровничных и прядильных машин | 1962 |

|

SU151952A1 |

| US 7663853 B2, 16.02.2010. | |||

Авторы

Даты

2020-03-05—Публикация

2019-05-07—Подача