Изобретение относится к электронике интегральных микросхем (ИМС) и может быть использовано в составе радиоэлектронной аппаратуры наземного, морского и аэрокосмического базирования для защиты от воздействия тяжелых заряженных частиц (ТЗЧ), высокоэнергетических протонов (ВЭП), импульсного ионизирующего излучения, пучкового оружия.

Известно устройство для защиты (УЗ) интегральных микросхем (ИМС) от тиристорного эффекта (ТЭ) по патенту № RU 2510893.

Устройство содержит датчик тока, резистивный ключ, компаратор напряжения, генератор сброса сигналов и ключ, отключающий ток питания защищаемой ИМС (микроконтроллера (МК)) при возникновении тиристорного эффекта (ТЭ).

Работа устройства заключается в измерении тока питания ИМС и отключении тока питания МК при превышении допустимого тока ИМС транзисторным ключом на время, достаточное для снижение тока тиристорного эффекта до нуля с последующим восстановлением тока питания ИМС.

Данное устройство обладает рядом недостатков:

а) защищает ИМС только от отказов, но не от сбоев. Следует отметить, что при воздействии на аппаратуру ТЭ, например в условиях космоса, как правило, алгоритм работы МК записывается в однократно программируемую (прошиваемую) память (ПЗУ), а изменяемые параметры изделия (текущие параметры аккумуляторной и солнечной батарей, реконфигурации устройств космического аппарата, и прочие характеристики изменяющиеся в процессе его работы в течение 15-20 лет) хранятся в оперативном запоминающем устройстве (ОЗУ), обнуляемом при сбросе питания МК, что приводит к сбоям при защите МК от ТЗЧ (ТЭ).

б) защищает ИМС от отказов только при статическом повышении тока независимо от причины его возникновения, а поскольку изменения тока при штатной работе МК (например, включение АЦП) превышает уровень превышения тока от ТЗЧ, то резко снижается эффективность его работы. Отсутствие анализа динамического изменения тока приводит к множеству ненужных отключений питания МК и множеству случаев, когда ТЭ есть, а УЗ не сработало, т.е. к отказу МК (его окончательному выходу из строя).

в) УЗ не позволяет восстановить (сохранить) память ОЗУ после окончания воздействия тиристорного эффекта, приводящего к переводу отказа в сбой, а тем более при двух одновременных сбоях;

г) не позволяет сохранить память ОЗУ при нештатном отключении питания защищаемого устройства, например, при потере ориентации направления фотоэлектрических батарей космического аппарата на солнце и отсутствии питания на бортовой шине КА.

Известно устройство защиты ИМС от ТЗЧ, описанное в способе по патенту № RU 2480898. Устройство основано на применении специализированной цифровой вычислительной машины (СЦВМ) с модернизацией ее программного обеспечения и организацией рестарта с отключением питания при обнаружении ТЗЧ.

Естественно, данное устройство обладает всеми недостатками предыдущего, но еще и обладает завышенными массогабаритными характеристиками, не позволяющими его применить в каждом из многочисленных приборов космического аппарата.

Известно трехканальное устройство защиты для подключения к трем контроллерам и описанное в патенте № RU 2653243 и предназначенное для восстановления данных ОЗУ при сбоях в ИМС за счет использования мажоритарного принципа использования информации, хранящейся в регистрах памяти.

К недостатку данного устройства следует отнести:

- отсутствие устройств защиты от отказов при ТЗЧ;

- невозможность восстановления данных ОЗУ при одновременном сбое двух из трех МК в связи с мажоритарным принципом работы два из трех;

- невозможность восстановления данных ОЗУ при снижении напряжения на шине питания КА до нуля, например, при потере ориентации направления фотоэлектрических батарей на солнце или любом, даже кратковременном пропадании питания на бортовой шине КА, т.к. регистр памяти хранит информацию только при наличии питания.

В качестве прототипа выбрано устройство защиты программируемых ИМС от тиристорного эффекта согласно патенту RU №2716030.

Данное УЗ программируемых ИМС содержит токоизмерительный резистор, устройство защиты максимального тока (УЗМТ) и устройство выделения тока тиристорного эффекта (УВТЭ) благодаря которым оно с высокой надежностью исключает отказы программируемых МК при возникновении ТЗЧ с учетом как статических, так и динамических изменений тока. В дальнейшем, совместное применение УЗМТ и УВТЭ будем называть устройством защиты ИМС по току или УЗТ. Работа данного УЗ, как и других аналогов, заключается в переводе возможных отказов МК в сбои с потерей информации ОЗУ.

К недостаткам устройства следует отнести:

- отсутствие возможности восстановления информации в ОЗУ МК при штатной работе в условиях ТЗЧ, а также после снижения напряжения питания в МК до нуля и последующего восстановлением нормального напряжения питания.

Задачей, на решение которой направлено создание настоящего изобретения, является защита МК от сбоев путем восстановления данных ОЗУ, а также обеспечение работоспособности УЗ при одновременном сбое двух МК, что существенно повышает надежность приборов космической аппаратуры, содержащей программируемые микросхемы (микроконтроллеры) при воздействии ТЗЧ.

Поставленная задача решается тем, что устройство защиты (УЗ1) программируемых микроконтроллеров (МК) от тиристорного эффекта (ТЭ), включающее токозадающий резистор (TP), первым и вторым выводом связанный с устройством защиты микроконтроллера (МК) от отказов по току (УЗТ), выход которого предназначен для подключения ко входу питания защищаемого МК, а первый вывод токозадающего резистора также является входом устройства защиты и предназначен для подключения к цепи питания, дополнительно содержит модуль восстановления памяти (МВП), входом подключенный к первому выводу токозадающего резистора и первому выводу устройства защиты микроконтроллера от отказов по току (УЗТ), включающий последовательно подключенные по питанию ключ, вход по питанию которого связан со входом модуля восстановления памяти, а его управляющий вход предназначен для подключения к управляющему порту МК, ограничитель тока и микросхему флеш-памяти, интерфейсные выводы которой предназначены для подключения к выводам интерфейсной шины связи с МК.

Предусмотрено, что с целью обеспечения возможности восстановления данных ОЗУ при двух сбоях устройства защиты оно дополнительно содержит два аналогичных устройства защиты, каждое из которых предназначено для подключения к своему микроконтроллеру, а все их интерфейсные шины объединены, при этом в качестве восстановленного сигнала модуля восстановления памяти принят мажоритированный сигнал, полученный из пяти принятых сигналов ОЗУ микроконтроллеров и модуля восстановления памяти за исключением ОЗУ восстанавливаемого микроконтроллера.

Предусмотрено также, что для повышения надежности флеш-памяти при ТЗЧ частота интерфейсной шины выбрана такой, при которой ток чтения/записи флэш-памяти соответствует установленному току ограничителя тока, а произведение тока чтения/записи на время открытия ключа не превышает предельного значения, характерного для отсутствия отказов при воздействии тиристорного эффекта.

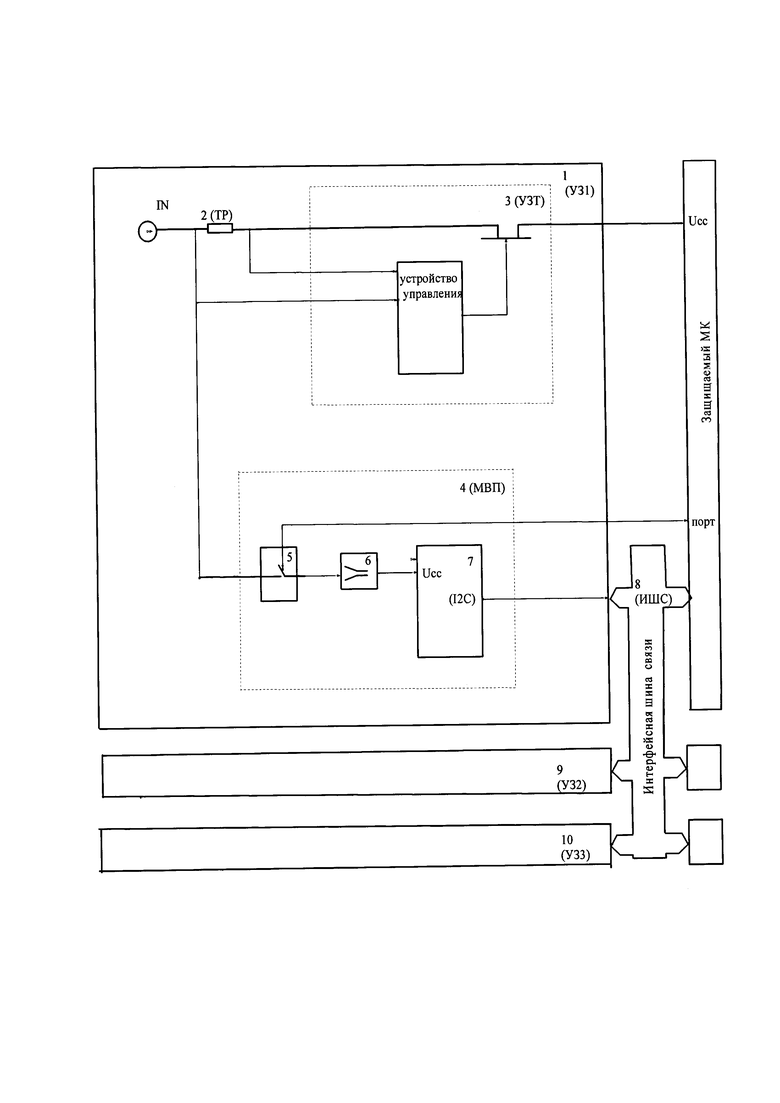

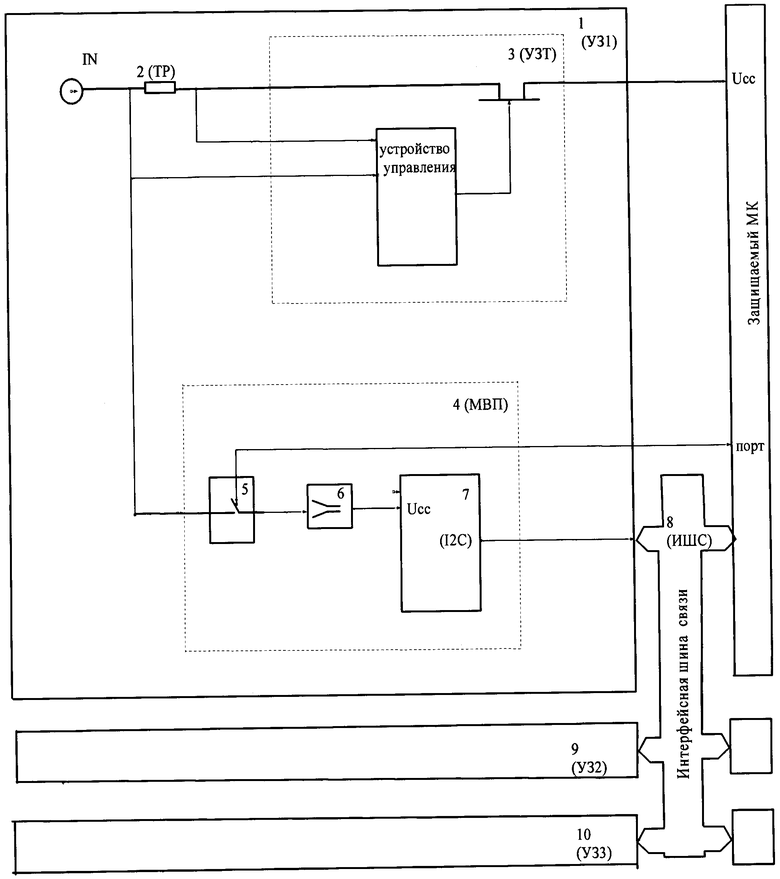

Структурная схема устройства защиты приведена на фигуре и содержит следующие элементы:

1 - устройство защиты одноканальное (УЗ1);

2 - токоизмерительный резистор (TP);

3 - устройство защиты от отказов по току (УЗТ);

4 - модуль восстановления памяти (МВП);

5 - ключ по питанию ИМС флэш-памяти;

6 - ограничитель тока;

7 - ИМС флэш-памяти;

8 - интерфейсная шина обмена информацией;

9, 10 - дополнительные одноканальные устройства защиты (УЗ2), (УЗ3).

Работа УЗ при возникновении факта ТЭ осуществляется следующим образом:

В процессе работы основного изделия микроконтроллеры записывают изменяемые данные реконфигурации системы в микросхему флэш-памяти 7.

При факте статического или динамического увеличения тока вследствие возникновения ТЗЧ устройство защиты 3 от отказов по току УЗТ устройств УЗ1, УЗ2, УЗ3 отключают защищаемые микроконтроллеры от источников питания, чем возможные отказы МК из-за ТЗЧ переводятся в сбои. Одновременно, при снятии питания с МК автоматически обнуляется память ОЗУ, данных МК.

После рассасывания тока ТЗЧ в МК УЗТ3 вновь подают питание на защищаемые МК, каждый из которых по интерфейсной шине 8 опрашивает состояние всех ИМС флэш-памяти 7 и ОЗУ, работающих МК, мажоритирует значения всех результатов по методике три из пяти, после чего восстанавливает значение своего ОЗУ в состояние бывшее до ТЗЧ.

Поскольку мажоритация производится методом 3 из 5, то система работоспособна даже при одновременном отказе трех ОЗУ.

Для обеспечения работы экспериментально, на стенде СПЭЛС, определяют ток, при котором происходит сбой ИМС и соответствующая ему частота шины (частота шины примерно пропорциональна току), после чего программно задается частота f равной 0,7-08 от замеренной и аппаратно задается ток ограничителя 6 тока 0,7-0,8 от замеренного тока.

Безотказная работа ИМС флэш-памяти 7 при этом обеспечивается следующими мерами:

А) Применением в качестве указанной ИМС испытанной на уровень энергии одиночного сбоя (ОИН), например, микросхемы МС 1636РР4 в СПЭЛС и имеющий следующие параметры стойкости:

- по поглощению радиации (параметры 7К1/7К4) - не хуже 1*1К/0,05*1К;

- по катастрофическим отказам от ТЭ (параметры 7К11/7К12) - не хуже 18 МэВ*см2/мг;

- по одиночным сбоям от ТЭ (7К11/7К12) - не менее 42 МэВ*см2/мг; е

Б) Снижением тактовой частоты записи и чтения программным путем на уровне порядка 1 МГц, позволяющем использовать аппаратное ограничение тока величиной (3-5) мА с использованием МС 1158ЕН3.3, что не позволяет развиваться процессу защелкивания ключей;

В) Ограничением количества требуемых циклов перезаписи ориентировочно до 1000 при допустимом количестве -100000 циклов, что определяет сверхнизкую загрузку флэш-памяти по данному параметру.

Г) Ограничением общего времени включенного состояния ИМС за счет ее принудительного включения ключом, управляемым МК только на время записи и чтения. Учитывая, что время одного обращения к памяти имеет порядок 1 сек, а количество циклов чтения порядка 100 на 1 цикл записи, общее время включенного состояния равно 900*100*1 сек. = 90000 сек. Или 0,03 года при сроке работы по ТУ - 25 лет;

Таким образом, предлагаемое решение позволяет, обеспечить работоспособность защищаемых микроконтроллеров как по катастрофическим отказам, так и по сбоям при одновременном сбое всех трех МК, а следовательно, существенно повысить надежность аппаратуры, содержащей указанные ИМС, практически без увеличения ее массы и габаритов.

На предприятии ЗАО «Орбита» принято решение об использовании предлагаемого технического решения в аппаратуре космической станции «Научно-энергетический модуль НЭМ», что позволит выполнять раннее невыполнимые задачи.

Предлагаемое устройство относится к электронике интегральных микросхем и может быть использовано в составе радиоэлектронной аппаратуры наземного, морского и аэрокосмического базирования для защиты вычислительных средств от сбоев при воздействии на программируемые МК тяжелых заряженных частиц (ТЗЧ). Техническим результатом является восстановление информации в оперативной памяти защищаемых МК при воздействии тиристорного эффекта и потере питания в аппаратуре при любых нештатных ситуациях. Он достигается тем, что устройство защиты от отказов дополнено модулем восстановления памяти, включающим управляемый ограничитель тока и микросхему флэш-памяти. При этом устройство выполнено в резервированном варианте, рассчитанном на два одновременных сбоя в системе с использованием мажоритарного принципа (три из пяти) для восстановления информации. 2 з.п. ф-лы, 1 ил.

1. Устройство защиты программируемых микроконтроллеров от тиристорного эффекта, включающее токозадающий резистор (TP), первым и вторым выводом связанный с устройством защиты микроконтроллера (МК) от отказов по току (УЗТ), выход которого предназначен для подключения к входу питания защищаемого МК, а первый вывод токозадающего резистора также является входом устройства защиты и предназначен для подключения к цепи питания, отличающееся тем, что оно дополнительно содержит модуль восстановления памяти (МВП), входом подключенный к первому выводу токозадающего резистора и первому выводу устройства защиты микроконтроллера от отказов по току (УЗТ), включающий последовательно подключенные по питанию ключ, вход по питанию которого связан со входом модуля восстановления памяти, а его управляющий вход предназначен для подключения к управляющему порту МК, ограничитель тока и микросхему флеш-памяти, интерфейсные выводы которой предназначены для подключения к выводам интерфейсной шины связи с МК.

2. Устройство защиты по п. 1, отличающееся тем, что оно дополнительно содержит два аналогичных устройства защиты, каждое из которых предназначено для подключения к своему микроконтроллеру, а все их интерфейсные шины объединены, при этом в качестве восстановленного сигнала модуля восстановления памяти принят мажоритированный сигнал, полученный из пяти принятых сигналов ОЗУ микроконтроллеров и модуля восстановления памяти, за исключением ОЗУ восстанавливаемого микроконтроллера.

3. Устройство защиты по п. 1, отличающееся тем, что частота интерфейсной шины микросхемы флеш-памяти выбрана такой, при которой ток чтения/записи флэш-памяти соответствует установленному току ограничителя тока, а произведение тока чтения/записи на время открытия ключа не превышает предельного значения, характерного для отсутствия отказов при воздействии тиристорного эффекта.

| Способ и устройство защиты программируемых интегральных микросхем, например микроконтроллеров, от тиристорного эффекта | 2019 |

|

RU2716030C1 |

| Фазосдвигающее устройство | 1958 |

|

SU120255A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ОТ ТИРИСТОРНОГО ЭФФЕКТА | 2012 |

|

RU2510893C2 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

Авторы

Даты

2021-06-03—Публикация

2020-08-14—Подача