Изобретение относится к области микро- и наноэлектроники и может быть использовано для изготовления как полевых нанотранзисторов со структурой металл-диэлектрик-полупроводник, так и интегральных схем.

Продвижение в область меньших размеров элементов полевых транзисторов требует не только изменения их конструкции и принципа работы, но и применения новых материалов. Так, для высокого быстродействия необходимо использовать высокопроводящие материалы затворов, например, металлы или силициды металлов [1] и диэлектрики с высоким значением диэлектрической проницаемости k более 10. Использование подложки "кремний на изоляторе" позволяет избавиться от "короткоканальных" эффектов.

Дальнейшее уменьшение размеров элементов транзисторов требует отказа от легирования полупроводника в контактных областях. Реализация такой возможности обеспечивается только с использованием полевого нанотранзистора с контактами Шотки на истоке и стоке (Schottky Barrier FET) вместо омических контактов, которые создаются путем сильного легирования. Такие транзисторы были реализованы различными авторами [2]. Преимущества подобных транзисторов обусловлены, прежде всего, отсутствием высокотемпературных технологических операций, связанных с легированием контактов.

В настоящее время тактовая частота цифровых схем ограничена сильным разогревом в процессе их работы. Снижения разогрева можно добиться путем уменьшения рабочего напряжения транзисторов в цифровой логической схеме. Для уменьшения рабочего напряжения требуется увеличение наклона подпороговой характеристики транзистора. Однако во всех полевых транзисторах, основанных на термоэмиссионном механизме протекания тока, в том числе и в транзисторах с контактами Шоттки, наклон подпороговой характеристики ограничен величиной 60 мВ напряжения на затворе на декаду тока при комнатной температуре, как и в объемном легированном транзисторе.

Известны туннельные транзисторы [3], которые, в принципе, позволяют достичь большой крутизны подпороговой характеристики. Работа таких транзисторов основана на смыкании и размыкании зоны проводимости и валентной зоны полупроводника под управлением напряжения на затворе.

Еще в большей степени повышения подпороговой крутизны транзистора можно добиться за счет увеличения числа затворов и отсутствия физического легирования. С помощью дополнительных затворов осуществляется так называемое "электрическое легирование" подзатворных областей [4]. В процессе работы транзистора на дополнительные затворы подается постоянное напряжение. Выбор величины и знака этого напряжения позволяет получать структуры p+-i-n+ и n+-i-p+, т.е. с разным типом проводимости, что необходимо для создания КМОП пары, применяемой в цифровых схемах.

В работе [4] в процессе изготовления многозатворного транзистора формирование центрального управляющего электрода затвора на кремниевой подложке осуществляется с помощью электронной литографии с критическим размером 25-50 нм, при этом в качестве материала используется поликремний с сильным р+ легированием. Далее на боковые стенки наносится изолирующий материал и создаются вспомогательные затворы из сильнолегированного поликремния (n+) по технологии формирования спейсеров в полевых транзисторах. После этого производится ионная имплантация для создания сильнолегированных областей контактов истока и стока, с последующим высокотемпературным отжигом.

При работе такого транзистора средний затвор является управляющим, а два боковых затвора создают электрическое легирование, обеспечивающее продленные контакты истока и стока. Использование электрического легирования вместо физического увеличивает крутизну транзистора и снижает пороговое напряжение.

Недостатки такой технологии изготовления многозатворного полевого транзистора заключаются в следующем:

1) длина управляющего затвора ограничена литографическими размерами;

2) использование поликремния в качестве материала затворов приводит к меньшему быстродействию транзисторов по сравнению с транзисторами с металлическими затворами;

3) наличие высокотемпературных операций по легированию контактов истока и стока приводит к взаимной диффузии материалов структуры транзистора и ухудшению его характеристик;

4) не решается задача работы транзистора в режиме туннельного транзистора с высокой подпороговой крутизной, что позволяет снизить рабочее напряжение, уменьшить разогрев и увеличить тактовую частоту работы цифровой схемы.

Чтобы избавиться от этих недостатков, предлагается изготавливать многозатворные полевые транзисторы по более простой, но устойчивой технологии.

По способу изготовления предлагаемого многозатворного полевого транзистора наиболее близким является способ изготовления полевого транзистора [4].

Предлагаемый способ изготовления многозатворного полевого транзистора нацелен на расширение функциональных возможностей цифровых схем на основе подобных транзисторов, отсутствие технологических операций, связанных с легированием, увеличение крутизны подпороговой характеристики, обеспечение работы транзистора в режиме туннельного транзистора, обеспечение возможности изготовления элементов транзисторов - истока, стока и затворов по самосовмещенной технологии, расширение возможностей литографии, методов самоформирования, плазмохимического травления, ионно-лучевого травления в формировании структур нанометровых размеров.

Для этого на полупроводниковую подложку наносится контактный слой истока/стока (первый металл), а затем наносится вспомогательный слой (ВС) диэлектрик-металл (первый диэлектрик-второй металл), в котором с помощью плазмохимического травления, литографии и самоформирования формируется нанометровая щель через зазор между двумя маскирующими металлическими слоями (второй металл), далее формируются три управляющих электрода затворов, причем, первый и третий управляющие электроды (третий металл), их спейсеры и подзатворный диэлектрик формируются на стенках и дне в нанометровой щели вспомогательного слоя последовательным осаждением в щель и плазмохимическим травлением диэлектрика спейсеров (второй диэлектрик) и металла (третий металл), что обеспечивает формирование нанометровых затворов (несколько нм), затем второй управляющий электрод формируется осаждением в зауженную на величину длин первого и третьего управляющих электродов и их спейсеров щель слоя диэлектрика (третий диэлектрик), выполняющего роль спейсеров и подзатворного диэлектрика второго управляющего электрода, металла (четвертый металл) и их ПХТ; одновременно с управляющими электродами в третьем и четвертом металлах с использованием фоторезистивной маски, дополнительного слоя металла (пятый металл) в качестве защитной маски и метода сухого травления формируются контактные площадки трех управляющих электродов, а контактные площадки истока/стока формируются после завершения технологических операций формирования управляющих электродов.

Возможен вариант, когда для упрощения технологии изготовления туннельного нанотранзистора с контактами Шоттки не производится формирование центрального (второго) управляющего электрода (затвора), а щель между первым и третьими управляющими электродами заполняется диэлектриком с низкой диэлектрической проницаемостью k. Однако изготовленный таким образом нанотранзистор с двумя затворами обладает большей величиной управляющего напряжения и, соответственно, большим энергопотреблением при работе в цифровых логических схемах, нежели нанотранзистор с тремя затворами. Возможен вариант, когда первый и третий управляющие электроды находятся в электрическом контакте с помощью общей контактной площадки, что обеспечивает работу транзистора в обычном режиме, не туннельном, как и в конструкции [4]. Тем не менее, и в этих упрощенных конструкциях нанотранзисторов осуществляется «электрическое легирование» подзатворных областей.

В качестве первого металла можно использовать металлы Ta, Ni, Co, Cr, V и другие устойчивые к плазмохимическому травлению при формировании щели в ВС. В этом случае после формирования щели в ВС проводится химическое травление первого металла на дне нанометровой щели.

Целесообразно в качестве вспомогательного слоя использовать слои: полиимид, SiO2, Si3N4, AI2O3 - W, Ta, Al, Ti, Cr, Ni, FeNi, V.

В качестве материалов для формирования "спейсеров" и подзатворного диэлектрика используются одни и те же слои диэлектрика с высоким значением диэлектрической проницаемости k более 10 - ZrO2, HfO2, Ta2O5, Al2O3, InO2, LaO2.

В качестве полупроводниковой подложки может использоваться подложка КНИ, объемный кремний, гетероструктуры кремний-германий, подложки из материалов группы AIIIBV.

Возможен вариант, когда формирование нанометровых щелей во вспомогательном слое (ВС) обеспечивается с помощью фотолитографии и самоформирования. Для этого после плазмохимического травления диэлектрика вспомогательного слоя (ВС) щель зауживается по технологии формирования спейсеров: наносится дополнительный диэлектрик на стенки щели.

В качестве материала первого и третьего управляющих электродов используются проводящие материалы, такие как TiN, TaN, NbN и другие нитриды металлов или металлы, например W, Pt, Ru и др., а в качестве материала второго управляющего электрода используется металлы Со, Ti, Ni, Pt, Ta, Ir, Pd, W, силициды этих металлов, проводящие материалы TiN, TaN.

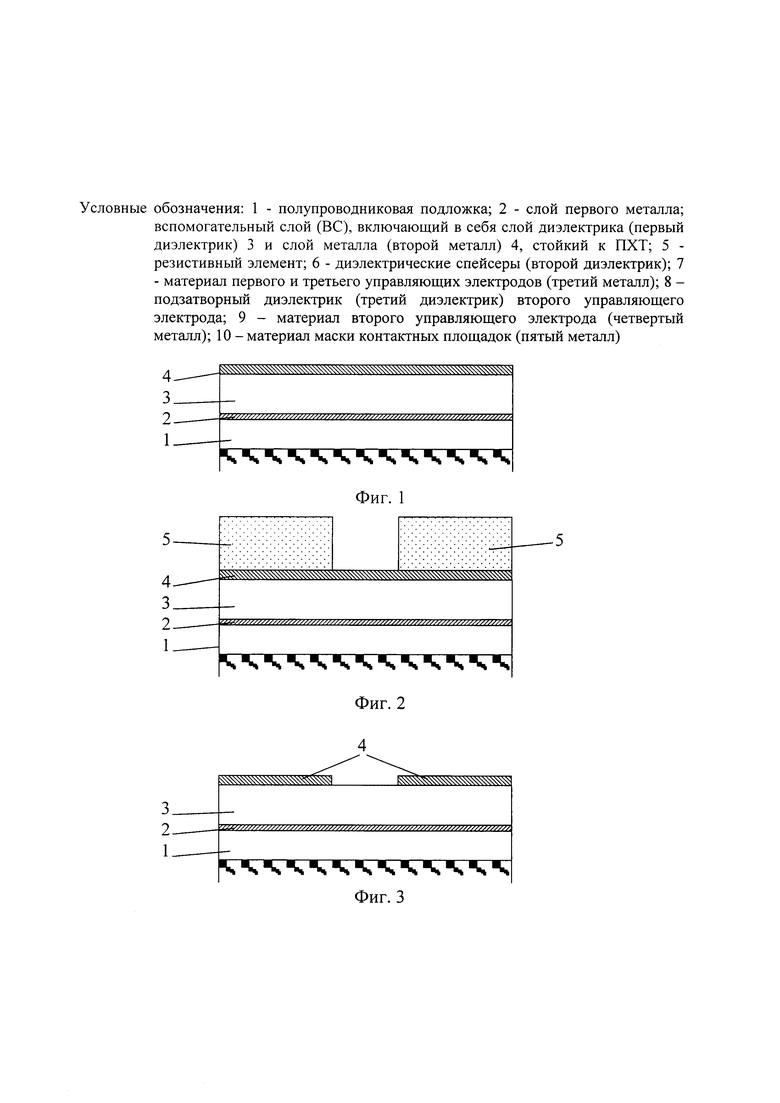

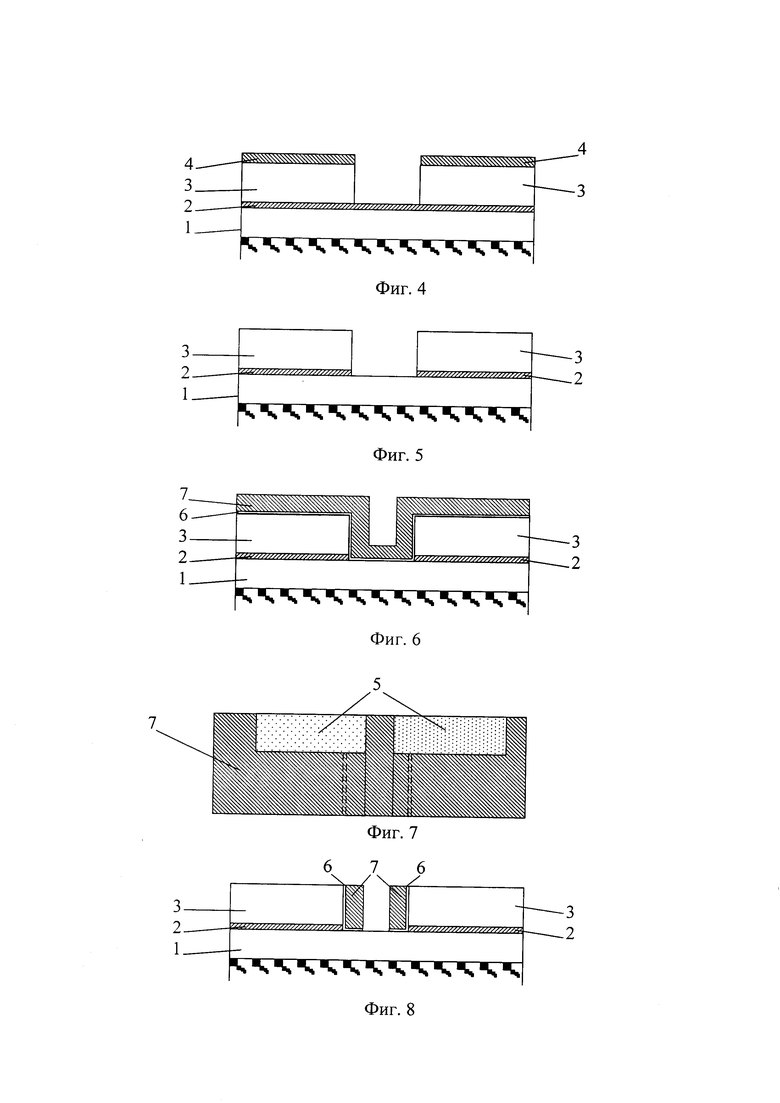

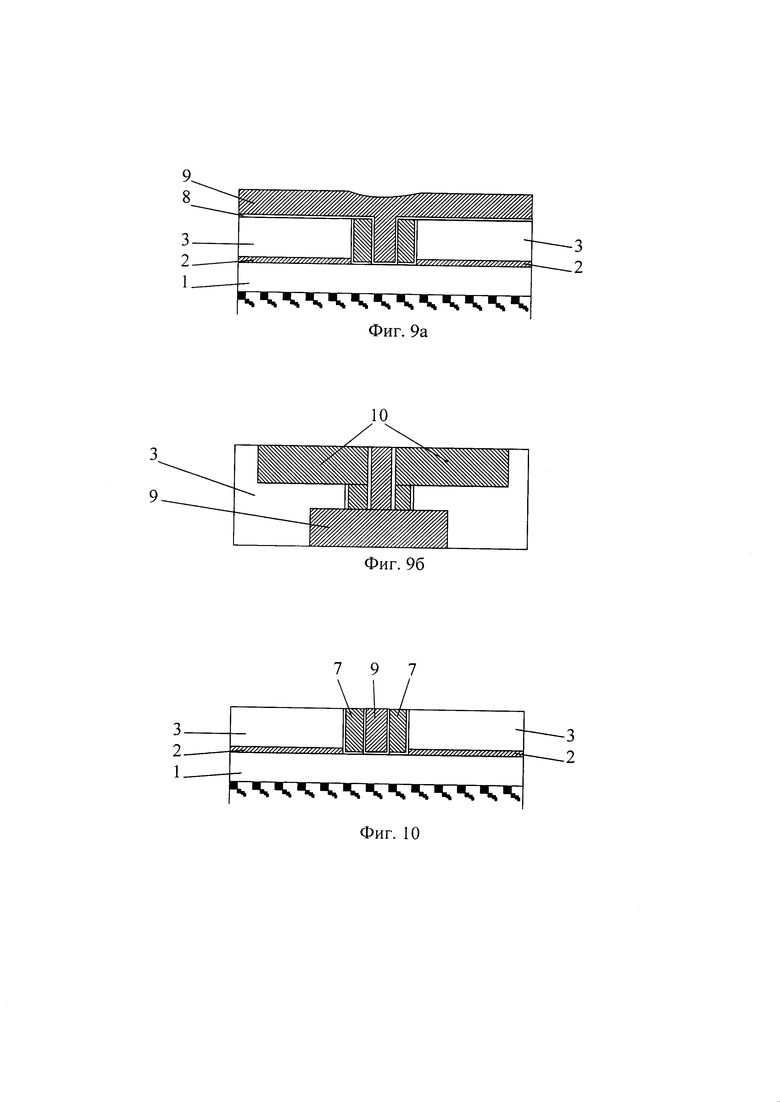

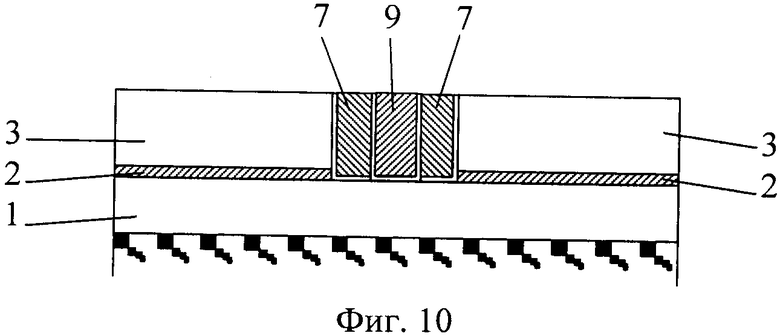

На фиг. 1-10 представлена технологическая последовательность изготовления туннельного полевого нанотранзистора с тремя управляющими электродами нанометровой длины на полупроводниковой подложке.

На чертежах показаны: полупроводниковая подложка 1; слой первого металла 2; вспомогательный слой (ВС), состоящий из слоя диэлектрика (первый диэлектрик) 3 и слоя металла (второй металл) 4, стойкий к ПХТ; резистивные элементы 5; диэлектрические спейсеры (второй диэлектрик) 6; материал первого и третьего управляющих электродов (третий металл) 7; подзатворный диэлектрик (третий диэлектрик) 8 второго управляющего электрода; и материал второго управляющего электрода (четвертый металл) 9, материал (пятый металл) дополнительного слоя контактных площадок 10.

В качестве рабочей подложки взята полупроводниковая кремниевая подложка 1 (фиг. 1) на которую вначале наносился первый металл контактного слоя истока/стока, например Ni 2. Затем формировался вспомогательный слой, состоящий из первого диэлектрика, например, SiO2 3 и слоя второго металла, например W 4.

После этого на вспомогательном слое электронной литографией формировались резистивные элементы 5 (фиг. 2) в виде двух прямоугольников с минимальным расстоянием между ними, определяемым требуемой шириной управляющих электродов, и с помощью плазмохимического травления формировалась щель во втором металле (рис. 3). После этого через эту металлическую маску с зазором ПХТ формировалась нанометровая щель в диэлектрике ВС (фиг. 4). Затем проводилось химическое травление первого металла на дне щели и удаление металлической маски ВС (фиг. 5). Далее на полупроводниковую подложку наносился слой диэлектрика для формирования спейсеров и подзатворного слоя (второй диэлектрик) 6, например HfO2; и слоя металла (третий металл) 7 первого и третьего управляющих электродов, например нитрид тантала (фиг. 6), который плазмохимическим травлением удалялся с поверхности вспомогательного слоя и со дна нанометровой щели (фиг. 8) после формирования защитной металлической маски контактных площадок этих электродов (фиг. 7) с помощью фотолитографии, напыления металла, стойкого к ПХТ, и «взрыва» фоторезиста.

Аналогичным образом на боковых стенках сформированных первого и третьего управляющих электродов и дне нанометровой щели осаждался диэлектрик для формирования спейсеров и подзатворного слоя второго управляющего электрода (третий диэлектрик) 8, например, HfO2 (фиг. 9а), с последующим осаждением металла 9 второго управляющего электрода (четвертый металл), например W (фиг.9а), и создавалась защитная металлическая маска контактной площадки второго управляющего электрода (фиг. 9б). Затем ПХТ слоев 8 и 9 на открытых участках защитной маски формировался второй управляющий электрод (фиг. 10). После этого проводилось формирование контактного слоя истока/стока.

Использование предлагаемого способа изготовления полупроводниковых полевых нанотранзисторов с тремя управляющими электродами нанометровой длины и интегральных схем на их основе обеспечивает следующие преимущества:

- совмещение в одном транзисторе преимуществ транзисторов с барьерами Шоттки, т.е. отсутствие легирования, с преимуществами туннельных транзисторов, т.е. высокой крутизной подпороговой характеристики);

- электрическое легирование, используемое вместо физического легирования, устраняет потребность в высокотемпературной операции отжига для активации примесей и повышает крутизну характеристики туннельного транзистора;

- выбор величины и знака напряжения на вспомогательных легирующих затворах позволяет получать транзисторы с разным типом проводимости канала, а именно n- и p-типа, что необходимо для создания КМОП-пары, применяемой в цифровых интегральных схемах.

- появляется возможность формирования нескольких нанометровых управляющих электродов с помощью обычной фотолитографии и существующего технологического оборудования;

- появляется возможность устойчивого формирования по самосовмещенной технологии областей стока-затворов-истока и спейсеров;

- формирование проводящих контактов истока, затворов и стока производится по самосовмещенной технологии с применением обычной литографии.

Эти преимущества обеспечивают нанометровую длину канала полевого нанотранзистора, решая задачи достижения высокой степени интеграции, увеличения рабочей частоты, повышения крутизны подпороговой характеристики и увеличения тока открытого состояния при работе в режиме туннельного транзистора, уменьшения рабочего напряжения, снижения энергопотребления, повышения быстродействия и воспроизводимости параметров приборов, одновременно упрощая и удешевляя их изготовление.

Источники информации

1. Патент США US 6602781 B1, 2003, (Metal silicide gate transistors, Qi Xiang et al.)

2.

D. J. Pearman, G. Pailloncy, J.-P. Raskin, J. M. Larson, J. P. Snyder, E. H. C. Parker, and T. E. Whall. Static and High-Frequency Behavior and Performance of Schottky-Barrier p-MOSFET Devices, IEEE Tr. El. Dev., vol. 54, pp, 2796- 2802, 2007.

Li Ding-Yu, Sun Lei, Zhang Sheng-Dong, Wang Yi, Liu Xiao-Yan, and Han Ru-Qi. Schottky barrier MOSFET structure with silicide source/drain on buried metal. Chinese Physics, vol. 16. pp. 240-244, 2007.

C. Ahn and M. Shin. Ballistic Quantum Transport in Nanoscale Schottky-Barrier Tunnel Transistors. IEEE Tr. Nanotech., vol. 5, pp. 278-283, 2006.

J. Park, A. M. Ozbek, L. Maa, M. T. Veety, M. P. Morgensen, D. W. Barlage,

V. D. Wheeler, M. A.L. Johnson. An analytical model of source injection for N-type enhancement mode GaN-based Schottky Source/Drain MOSFET’s with experimental demonstration. Solid-State Electronics 54 (2010) 1680-1685.

3. C. Aydin, A. Zaslavsky, S. Luryi, S. Cristoloveanu, D. Mariolle, D. Fraboulet, and S. Deleonibus. Lateral interband tunneling transistor in silicon-on-insulator. Applied Physics Letters 84, 1780 (2004).

4. Sungil Chang, Sangyeon Han, Hyungcheol Shin, Jongho Lee. A 25-nm MOSFET with an Electrically Induced Source/Drain Journal of the Korean Physical Society, Vol. 37, No. 6, December 2000, pp. 902-906.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВОГО НАНОТРАНЗИСТОРА С КОНТАКТАМИ ШОТТКИ С УКОРОЧЕННЫМ УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ НАНОМЕТРОВОЙ ДЛИНЫ | 2012 |

|

RU2504861C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА С УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ НАНОМЕТРОВОЙ ДЛИНЫ | 2003 |

|

RU2237947C1 |

| ТУННЕЛЬНЫЙ НЕЛЕГИРОВАННЫЙ МНОГОЗАТВОРНЫЙ ПОЛЕВОЙ НАНОТРАНЗИСТОР С КОНТАКТАМИ ШОТТКИ | 2016 |

|

RU2626392C1 |

| ПОЛЕВОЙ НАНОТРАНЗИСТОР | 2003 |

|

RU2250535C1 |

| БиКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2003 |

|

RU2282268C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS-ТРАНЗИСТОРНЫХ КРИСТАЛЛОВ С МНОГОСЛОЙНОЙ ДРЕЙФОВОЙ ОБЛАСТЬЮ СТОКА | 2024 |

|

RU2819581C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОМАСШТАБИРУЕМОГО ПОЛЕВОГО ТРАНЗИСТОРА СО СТРУКТУРОЙ СУПЕРСАМОСОВМЕЩЕННОГО БИПОЛЯРНОГО ТРАНЗИСТОРА | 2001 |

|

RU2230392C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОП-ТРАНЗИСТОРА | 1991 |

|

RU2024107C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ АВТОМАСШТАБИРУЕМОЙ БИКМОП СТРУКТУРЫ | 2003 |

|

RU2234165C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИКМОП ПРИБОРА | 1998 |

|

RU2141148C1 |

Использование: в полупроводниковой технологии для изготовления нанотранзисторов и СБИС. Технический результат: электрическое легирование с помощью дополнительных затворов, позволяющее создавать более резкие p-n переходы, чем в туннельных транзисторах с физическим легированием; увеличение крутизны характеристик туннельных транзисторов и снижение их порогового напряжения; возможность изменения типа проводимости канала для применения предлагаемых транзисторов в КМОП технологии цифровых интегральных схем, упрощение технологии изготовления нанотранзисторов с нанометровыми затворами, отсутствие технологических операций, связанных с легированием, расширение функциональных возможностей нанотранзисторов, увеличение крутизны подпороговой характеристики за счет увеличения количества управляющих электродов и обеспечение работы в режиме туннельного транзистора. Сущность изобретения: предлагается способ изготовления туннельного полевого нанотранзистора с контактами Шоттки и несколькими управляющими электродами затворов на полупроводниковой подложке с использованием вспомогательного слоя (ВС) диэлектрик-металл, осажденного на предварительно нанесенный на полупроводниковую подложку контактный слой истока/стока, в котором формируется нанометровая щель, с последующим формированием на ее стенках и дне первого и третьего управляющих электродов, их спейсеров и подзатворного диэлектрика путем последовательного осаждения в щель и плазмохимического травления диэлектрика спейсеров и металла, а второй управляющий электрод формируется осаждением в зауженную на суммарную ширину первого и третьего управляющих электродов и их спейсеров щель слоя металла и его ПХТ, при этом вначале формируются диэлектрический спейсер и подзатворный диэлектрик второго управляющего электрода путем осаждения диэлектрика на боковые стенки первого и третьего управляющих электродов и дно щели в ВС. Одновременно с управляющими электродами формируются с использованием фоторезистивной маски, дополнительного слоя металла и метода сухого травления контактные площадки трех управляющих электродов, а контактные площадки истока/стока создаются после завершения технологических операций формирования управляющих электродов. 13 з.п. ф-лы, 10 ил.

1. Способ изготовления полевого многозатворного нанотранзистора, заключающийся в том, что для формирования центрального поликремниевого управляющего электрода затвора на полупроводниковой подложке используется электронная литография, далее на боковые стенки управляющего электрода затвора наносится изолирующий материал и создаются вспомогательные затворы из сильнолегированного поликремния n+ по технологии формирования спейсеров в полевых транзисторах, после этого производится ионная имплантация для создания сильнолегированных областей контактов истока и стока, с последующим высокотемпературным отжигом, отличающийся тем, что на полупроводниковую подложку предварительно наносится контактный слой истока/стока (первый металл) с последующим нанесением вспомогательного слоя (ВС) диэлектрик-металл (первый диэлектрик-второй металл), в котором с помощью литографии, плазмохимического травления и самоформирования создается нанометровая щель через зазор между двумя маскирующими металлическими слоями (второй металл), далее на боковых стенках щели формируются управляющие электроды затворов, причем первый и третий управляющие электроды затворов (третий металл), их спейсеры и подзатворный диэлектрик формируются на стенках и дне нанометровой щели во вспомогательном слое последовательным осаждением в щель и плазмохимическим травлением диэлектрика спейсеров (второй диэлектрик) и металла (третий металл), а второй управляющий электрод затвора формируется осаждением в зауженную на величину длин первого и третьего управляющих электродов затворов и их спейсеров щель слоя диэлектрика (третий диэлектрик), выполняющего роль спейсеров и подзатворного диэлектрика второго управляющего электрода затвора, металла (четвертый металл) и их ПХТ; одновременно с управляющими электродами затворов в третьем и четвертом металлах с использованием фоторезистивной маски, дополнительного слоя металла (пятый металл) в качестве защитной маски и метода сухого травления формируются контактные площадки трех управляющих электродов затворов, а контактные площадки истока/стока формируются после завершения технологических операций формирования управляющих электродов затворов.

2. Способ по п. 1, отличающийся тем, что в качестве материала первого и третьего управляющих электродов затворов используются проводящие материалы, такие как TiN, TaN, NbN и другие нитриды металлов или металлы, например W, Pt, Ru и др.

3. Способ по п. 1, отличающийся тем, что в качестве материала второго управляющего электрода затвора используется металлы Со, Ti, Ni, Pt, Ta, Ir, Pd, W, силициды этих металлов, проводящие материалы TiN, ТаN.

4. Способ по п. 1, отличающийся тем, что в качестве второго металла используются устойчивые к плазмохимическому травлению металлы, например Ni, Cr, FeNi, V, W.

5. Способ по п. 1, отличающийся тем, что в качестве вспомогательного слоя первый диэлектрик-второй металл используются такие сочетания материалов, как, например, полиимид, SiO2, Si3N4, Аl2O3-W, Ta, Ti, Cr, Ni, FeNi, V.

6. Способ по п. 1, отличающийся тем, что в качестве материалов для формирования диэлектрических "спейсеров" и подзатворного диэлектрика (второй диэлектрик и третий диэлектрик) используется один и тот же диэлектрик с высоким значением диэлектрической проницаемости k (более 10), например HfO2, ZrO2, Аl2O3, InO2, LaO2, Ta2O5, ZrSiO4, HfSiO4.

7. Способ по п. 1, отличающийся тем, что в качестве полупроводниковой подложки может использоваться подложка «кремний на изоляторе» (КНИ), объемная подложка кремния, структуры с напряженным кремнием, гетероструктуры кремний-германий или материалы группы AIIIBV.

8. Способ по п. 1, отличающийся тем, что в качестве первого металла используются переходные металлы Ni, Co, Ta, Ti, Pt и другие, устойчивые к ПХТ при формировании щели в ВС и способные образовывать силициды на поверхности полупроводниковой подложки для формирования контактных слоев истока/стока.

9. Способ по п. 2, отличающийся тем, что для обеспечения процесса силицидизации металла контактного слоя истока/стока перед нанесением контактного слоя (первый металл) на полупроводниковую подложку наносится тонкий слой (несколько нанометров) химически активного по отношению к кислороду металла (Ti, Zr, Hf, Ta, Mo) очищающего поверхность полупроводника от кислорода и других примесей и обеспечивающего получение качественных силицидов.

10. Способ по п. 1, отличающийся тем, что формирование контактных площадок управляющих электродов затворов производится с помощью литографии, дополнительного слоя металла, стойкого к ПХТ, служащего маской при ПХТ слоев материалов, формирующих управляющие электроды затворов.

11. Способ по п. 1, отличающийся тем, что контактные площадки управляющих электродов затворов состоят из двух слоев, т.е. материала управляющих электродов затворов и металла защитной маски, используемой при ПХТ этих материалов в процессе формирования управляющих электродов затворов.

12. Способ по п. 1, отличающийся тем, что формирование нанометровой щели во вспомогательном слое проводится с использованием фотолитографии и самоформирования, обеспечивающих создание металлической маски нанометрового размера во втором металле.

13. Способ по п. 1, отличающийся тем, что в качестве первого металла используется стойкий к ПХТ металл и его удаление со дна нанометровой щели проводится химическим травлением после формирования щели в ВС.

14. Способ по п. 1, отличающийся тем, что для создания управляющих электродов затворов с разными пороговыми напряжениями используются проводящие материалы и металлы, такие как W, TaN, HfN, TiN, WSi, TiSi и др.

| RU 2016112743 A, 06.10.2017 | |||

| ТУННЕЛЬНЫЙ НЕЛЕГИРОВАННЫЙ МНОГОЗАТВОРНЫЙ ПОЛЕВОЙ НАНОТРАНЗИСТОР С КОНТАКТАМИ ШОТТКИ | 2016 |

|

RU2626392C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВОГО НАНОТРАНЗИСТОРА С КОНТАКТАМИ ШОТТКИ С УКОРОЧЕННЫМ УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ НАНОМЕТРОВОЙ ДЛИНЫ | 2012 |

|

RU2504861C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА С УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ НАНОМЕТРОВОЙ ДЛИНЫ | 2003 |

|

RU2237947C1 |

| ПОЛЕВОЙ НАНОТРАНЗИСТОР | 2003 |

|

RU2250535C1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

Авторы

Даты

2020-03-18—Публикация

2018-06-07—Подача