Изобретение относится к области микро- и наноэлектроники и может быть использовано для изготовления как полевых нанотранзисторов, так и интегральных схем на их основе.

При создании транзисторов малых размеров на объемной полупроводниковой подложке сталкиваются с принципиальными ограничениями, вызванными так называемыми короткоканальными эффектами. Используя материалы с высоким, более 10, значением диэлектрической проницаемости k, уменьшая глубину переходов и толщину подзатворного диэлектрика, используя полупроводниковые подложки "кремний на изоляторе", добиваются возможности избавиться от "короткоканальных" эффектов, чтобы тем самым уменьшить размеры транзисторов и, главное, длину канала нанотранзисторов. Это позволяет повысить быстродействие интегральных схем. Кроме того, для высокого быстродействия также необходимо использовать высокопроводящие материалы затворов, например металлы или силициды металлов [1].

Продвижение в область еще меньших размеров элементов транзисторов требует отказа от легирования полупроводника в контактных областях. Реализация такой возможности обеспечивается только с использованием полевого транзистора с контактами Шоттки (SB FET) на истоке и стоке вместо омических контактов, которые обычно создаются путем сильного легирования полупроводника. Такие транзисторы были реализованы различными авторами [2]. Преимущества подобных транзисторов обусловлены отсутствием технологических операций, связанных с легированием контактов. Легирование включает процессы ионной имплантации и быстрого отжига при высокой, около 1000°С, температуре. Высокая температура вызывает нежелательную диффузию примеси и атомов металлов в структуре транзисторов.

Хотя предложенные конструкции транзисторов и решали поставленную задачу повышения степени интеграции и быстродействия, развитие технологии требует дальнейшего улучшения характеристик транзисторов, а также снижения энергопотребления и уменьшения разогрева. Этого можно добиться путем уменьшения рабочего напряжения транзисторов в цифровой логической схеме. Для уменьшения рабочего напряжения требуется увеличение наклона подпороговой вольт-амперной характеристики транзистора. Однако в транзисторах с контактами Шоттки наклон подпороговой характеристики ограничен величиной 60 мВ напряжения на затворе на декаду тока канала при комнатной температуре, как и в обычном полевом транзисторе [3].

Известны туннельные транзисторы [4], в которых в принципе может быть достигнута большая крутизна подпороговой характеристики. Работа таких транзисторов основана на смыкании и размыкании зоны проводимости и валентной зоны полупроводника, которые управляются напряжением на затворе. У этой конструкции имеется механический аналог в виде электромеханических переключателей, в которых напряжение на затворе смыкает и размыкает электрические контакты. В туннельных транзисторах обычно используется латеральная структура с областями разного типа легирования: p+-i-n+, причем затвор расположен над нелегированной i-областью. Недостатки подобных транзисторов обусловлены наличием технологических операций, связанных с легированием контактов. В частности, не удается создать резкие переходы в структурах p+-i-n+, в результате ток открытого состояния транзистора падает, что сказывается на его быстродействии. Кроме того, в процессе отжига примеси из контактов заходят в канал транзистора, уменьшая его проводимость. Другим нежелательным обстоятельством является то, что флуктуации концентрации легирующей примеси делают невозможным резкое смыкание и размыкание зоны проводимости и валентной зоны, что ограничивает достижимую крутизну вольт-амперной характеристики транзистора [5]. В связи с этим мы предлагаем добиваться повышения подпороговой крутизны транзистора за счет увеличения числа затворов и отсутствия легирования. С помощью дополнительных затворов осуществляется так называемое "электрическое легирование" подзатворных областей, при этом в процессе работы транзистора на дополнительные затворы подается постоянное напряжение. Выбор величины и знака этого напряжения позволяет получать структуры p+-i-n+ и n+-i-p+, т.е. с разным типом проводимости, что необходимо для создания КМОП (CMOS) пары, применяемой в цифровых логических схемах.

Для предлагаемой конструкции туннельного нелегированного многозатворного полевого нанотранзистора с контактами Шоттки с несколькими управляющими электродами затворов наиболее близким по конструкции является полевой транзистор с контактами Шоттки на истоке и стоке и одним управляющим электродом затвора [6]. Как отмечалось ранее, у такого транзистора наклон подпороговой вольт-амперной характеристики ограничен величиной 60 мВ напряжения на управляющем электроде затвора на декаду тока канала при комнатной температуре, как и в обычном полевом транзисторе.

Решение задачи повышения наклона подпороговой характеристики достигается тем, что предлагается конструкция туннельного нелегированного многозатворного полевого нанотранзистора с контактами Шоттки, включающая в себя полупроводниковую подложку, электроды стока и истока с контактами Шоттки, сформированные на слое полупроводника, канал полевого транзистора в слое полупроводника, расположенный между электродами стока и истока с контактами Шоттки и покрытый сверху слоем подзатворного диэлектрика, на котором расположен управляющий электрод затвора, сформированный на участке между электродами стока и истока над каналом нанотранзистора, при этом боковые поверхности управляющего электрода затвора закрыты изолирующими слоями диэлектрика спейсеров, отличается тем, что на поверхности слоя подзатворного диэлектрика на участке над каналом нанотранзистора между электродами стока и истока располагаются последовательно два или больше управляющих электродов затворов, при этом боковые поверхности управляющих электродов (затворов) закрыты слоями диэлектрика спейсеров, легирование слоя полупроводника не производится ни под электродами стока и истока, ни в канале нанотранзистора на участке между электродами стока и истока, а необходимые режимы работы нанотранзистора обеспечиваются использованием эффекта туннелирования и соответствующим выбором материалов электродов стока, истока и управляющих электродов затворов, а также прилагаемыми к управляющим электродам затворов напряжениями.

На прилагаемых чертежах показаны: изолирующая подложка 1; кремний 2; электрод истока 3; электрод стока 4; диэлектрик спейсера 5; управляющий электрод затвора 6 и подзатворный диэлектрик 7.

На фиг. 1-2 представлены конструкция выбранного в качестве прототипа туннельного полевого транзистора и конструкция предлагаемого туннельного нелегированного многозатворного полевого нанотранзистора с контактами Шоттки в варианте использования в качестве полупроводниковой подложки типа "кремний на изоляторе". Во втором случае показаны три управляющих электрода затворов, однако следует отметить, что - это только пример конструкции, а в общем случае может быть несколько, т.е. два или больше управляющих электродов затворов, как это сказано в формуле изобретения.

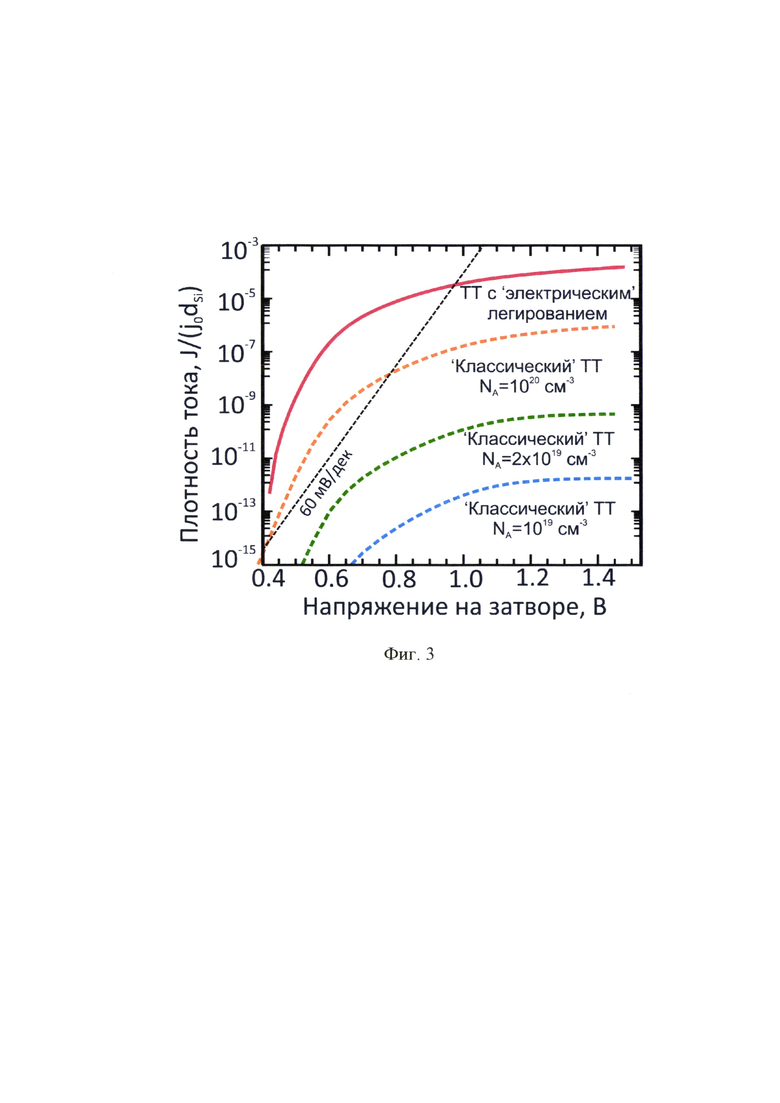

На фиг. 3 представлен результат расчета вольт-амперных характеристик, т.е. зависимости тока транзистора от напряжения на затворе для «классического» кремниевого транзистора с физическим легированием и одним затвором и для предлагаемого транзистора с электрическим легированием и несколькими управляющими электродами затворов.

Мы провели расчет вольт-амперных характеристик «классического» кремниевого транзистора с физическим легированием и одним затвором и предлагаемого транзистора с электрическим легированием и несколькими управляющими электродами затворов. При расчете характеристики транзистора с одним затвором мы использовали идеализированную модель резкой границы легирования на p-i-переходе. Это приближение дает завышенные значения подпороговой крутизны, т.к. не принимает во внимание флуктуацию плотности легирующей примеси. По-видимому, именно в результате этих флуктуаций экспериментально достигнутые значения подпороговой крутизны в легированных туннельных транзисторах гораздо ниже, а именно (53 мВ/дек)-1 для кремниевых транзисторов [7] и (47 мВ/дек)-1 для транзисторов на основе материалов А3В5 [8].

Следует отметить, что использование германия приводит к улучшению характеристик (крутизны и тока открытого состояния) по сравнению с кремниевыми туннельными транзисторами. Полупроводники группы А3В5, в принципе, также позволяют улучшить характеристики предлагаемых транзисторов, однако до сих пор не решена проблема подзатворных диэлектриков, т.к. существующие в настоящее время диэлектрики обладают большим количеством дефектов на границе раздела с полупроводником.

Предлагаемая конструкция туннельного нелегированного многозатворного полевого нанотранзистора с контактами Шоттки и интегральные схемы на их основе обеспечивают следующие преимущества:

- совмещение в одном транзисторе преимуществ транзисторов с контактами Шоттки (отсутствие легирования) с преимуществами туннельных транзисторов (высокая крутизна подпороговой характеристики);

- электрическое легирование, используемое вместо физического легирования, устраняет потребность в высокотемпературной операции отжига для активации примесей и повышает крутизну характеристики туннельного транзистора;

- выбор величины и знака напряжения на вспомогательных легирующих управляющих электродах затворов позволяет получать транзисторы с разным типом проводимости канала, т.е. n- и p-типа, что необходимо для создания КМОП-пары, применяемой в цифровых интегральных схемах.

Эти преимущества обеспечивают нанометровую, вплоть до нескольких нанометров, длину канала полевого нанотранзистора, решая проблемы достижения высокой степени интеграции, увеличения рабочей частоты, повышения крутизны подпороговой характеристики и увеличения тока открытого состояния при работе в режиме туннельного транзистора, уменьшения рабочего напряжения, снижения энергопотребления, а также повышения быстродействия и воспроизводимости параметров приборов. В целом наличие необходимого, произвольно выбираемого, количества управляющих электродов затворов значительно расширяет функциональные возможности нанотранзистора и повышает эффективность управления его характеристиками.

Источники информации

1. Патент США US 6602781 В1, 2003 (Metal silicide gate transistors, Qi Xiang et al.).

2. A) D.J. Pearman, G. Pailloncy, J.-P. Raskin, J.M. Larson, J.P. Snyder, E.H.C. Parker and Т.E. Whall. Static and High-Frequency Behavior and Performance of Schottky-Barrier p-MOSFET Devices, IEEE Tr. El. Dev., vol. 54, pp, 2796-2802, 2007.

B) Li Ding-Yu, Sun Lei, Zhang Sheng-Dong, Wang Yi, Liu Xiao-Yan and Han Ru-Qi. Schottky barrier MOSFET structure with silicide source/drain on buried metal. Chinese Physics, vol. 16. pp. 240-244, 2007.

C) C. Ahn and M. Shin. Ballistic Quantum Transport in Nanoscale Schottky-Barrier Tunnel Transistors. IEEE Tr. Nanotech., vol. 5, pp. 278-283, 2006.

3. D. Svintsov, V. Vyurkov, A. Burenkov, R. Oechsner, V. Lukichev and A. Orlikovsky. Tunnel FET with nanotube and graphene channels, Semiconductors, 47, 2, p. 279-284, 2013.

4. C. Aydin, A. Zaslavsky, S. Luryi, S. Cristoloveanu, D. Mariolle, D. Fraboulet and S. Deleonibus. Lateral interband tunneling transistor in silicon-on-insulator. Applied Physics Letters 84, 1780 (2004).

5. A) S. Mookerjea, D. Mohata, T. Mayer, V. Narayanan, S. Datta Temperature-Dependent I-V Characteristics of a Vertical In0,53Ga0,47As Tunnel FET // IEEE Electron Device Letters, Vol. 31, 2010, p. 564.

B) C.D. Bessire, M.T.  , H. Schmid, A. Schenk, K.B. Reuter, H. Riel Trap-Assisted Tunneling in Si-InAs Nanowire Heteroj unction Tunnel Diodes // Nano Letters, Vol. 11, 2011, p. 4195.

, H. Schmid, A. Schenk, K.B. Reuter, H. Riel Trap-Assisted Tunneling in Si-InAs Nanowire Heteroj unction Tunnel Diodes // Nano Letters, Vol. 11, 2011, p. 4195.

6. Патент США US 2007/0187758 A1 (SB-MOSFET (Schottky Barrier Metal-Oxide-Semiconductor Field Effect Transistor), with low barrier height and fabricating method thereof, Myung Sim Jun et al.).

7. Gandhi, R. et al. Vertical Si-nanowire n-type tunneling FETs with low subthreshold swing (≤50 mV/decade) at room temperature. IEEE Electron Device Lett. 32, 437-439 (2011).

8. Tomioka, K., Yoshimura, M. & Fukui, T. Steep-slope tunnel field-effect transistors using III-V nanowire / Si heterojunction. In Symposium on VLSI Technology, 47-48 (IEEE, 2012).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ТУНЕЛЬНОГО МНОГОЗАТВОРНОГО ПОЛЕВОГО НАНОТРАНЗИСТОРА С КОНТАКТАМИ ШОТТКИ | 2018 |

|

RU2717157C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВОГО НАНОТРАНЗИСТОРА С КОНТАКТАМИ ШОТТКИ С УКОРОЧЕННЫМ УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ НАНОМЕТРОВОЙ ДЛИНЫ | 2012 |

|

RU2504861C1 |

| ПОЛЕВОЙ НАНОТРАНЗИСТОР | 2003 |

|

RU2250535C1 |

| ПОЛЕВОЙ ТРАНЗИСТОР ТИПА МЕТАЛЛ - ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 1994 |

|

RU2130668C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА С УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ НАНОМЕТРОВОЙ ДЛИНЫ | 2003 |

|

RU2237947C1 |

| Способ изготовления латерального ДМОП - транзистора с увеличенным значением напряжения пробоя | 2023 |

|

RU2803252C1 |

| ПОЛЕВОЙ ТРАНЗИСТОР ШОТТКИ | 1991 |

|

RU2025831C1 |

| ТУННЕЛЬНЫЙ ПОЛЕВОЙ НАНОТРАНЗИСТОР С ИЗОЛИРОВАННЫМ ЗАТВОРОМ | 2007 |

|

RU2354002C1 |

| МОДУЛИРОВАННО-ЛЕГИРОВАННЫЙ ПОЛЕВОЙ ТРАНЗИСТОР | 2013 |

|

RU2539754C1 |

| ПЛАНАРНЫЙ СИЛОВОЙ МОП ТРАНЗИСТОР С БЛОКИРУЮЩИМ ЕМКОСТЬ СТОКА БАРЬЕРОМ ШОТТКИ | 2002 |

|

RU2229758C1 |

Использование: в полупроводниковой технологии для изготовления нанотранзисторов и СБИС. Технический результат: электрическое легирование с помощью дополнительных управляющих электродов затворов, позволяющее создавать более резкие p-n-переходы, чем в туннельных транзисторах с физическим легированием; увеличение крутизны вольт-амперных характеристик туннельных транзисторов и снижение их порогового напряжения; возможность изменения типа проводимости канала для применения предлагаемых транзисторов в КМОП технологии цифровых интегральных схем, отсутствие технологических операций, связанных с легированием, расширение функциональных возможностей, увеличение крутизны подпороговой вольтамперной характеристики за счет увеличения количества управляющих электродов затворов и обеспечение работы в режиме туннельного транзистора. Сущность изобретения: предлагается конструкция туннельного нелегированного многозатворного полевого нанотранзистора с контактами Шоттки, характеризующаяся тем, что на поверхности слоя подзатворного диэлектрика располагаются последовательно два или больше управляющих электродов затворов на участке над каналом нанотранзистора между электродами стока и истока, при этом боковые поверхности управляющих электродов затворов закрыты слоями диэлектрика спейсеров, легирование слоя полупроводника не производится ни под электродами стока и истока, ни в канале нанотранзистора на участке между электродами стока и истока, а необходимые режимы работы нанотранзистора обеспечиваются использованием эффекта туннелирования и соответствующим выбором материалов электродов стока, истока и управляющих электродов затворов, а также прилагаемыми к управляющим электродам затворов напряжениями. 3 з.п. ф-лы, 3 ил.

1. Туннельный нелегированный многозатворный полевой нанотранзистор с контактами Шоттки, включающий в себя полупроводниковую подложку, электроды стока и истока с контактами Шоттки, сформированные на поверхности полупроводниковой подложки, канал полевого транзистора в полупроводниковой подложке, расположенный между электродами стока и истока с контактами Шоттки и покрытый сверху слоем подзатворного диэлектрика, на котором расположен управляющий электрод затвора, сформированный на участке между электродами стока и истока над каналом нанотранзистора, при этом боковые поверхности управляющего электрода затвора закрыты изолирующими слоями диэлектрика спейсеров, отличающийся тем, что на поверхности слоя подзатворного диэлектрика на участке над каналом нанотранзистора между электродами стока и истока располагаются последовательно два или больше управляющих электродов затворов, при этом боковые поверхности управляющих электродов затворов закрыты слоями диэлектрика спейсеров, легирование полупроводниковой подложки не производится ни под электродами стока и истока, ни в канале нанотранзистора на участке между электродами стока и истока, а необходимые режимы работы нанотранзистора обеспечиваются использованием эффекта туннелирования и соответствующим выбором материалов электродов стока, истока и управляющих электродов затворов, а также прилагаемыми к управляющим электродам затворов напряжениями.

2. Туннельный нелегированный многозатворный полевой нанотранзистор с контактами Шоттки по п. 1, отличающийся тем, что в качестве полупроводниковой подложки используется полупроводниковая подложка типа "полупроводник на изоляторе", например "кремний на изоляторе".

3. Туннельный нелегированный многозатворный полевой нанотранзистор с контактами Шоттки по п. 1, отличающийся тем, что в качестве полупроводниковой подложки используется полупроводниковая подложка в виде объемного полупроводника.

4. Туннельный нелегированный многозатворный полевой нанотранзистор с контактами Шоттки по п. 1, отличающийся тем, что в качестве подзатворного диэлектрика и диэлектрика спейсеров используется один и тот же диэлектрический материал с высоким, более 10, значением диэлектрической проницаемости k, например HfO2, ZrO2, Al2O3, InO2, LaO2, Ta2O5, ZrSiO4, HfSiO4.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Токарный резец | 1924 |

|

SU2016A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ПЛАНАРНОГО ДВУХЗАТВОРНОГО МОП-ТРАНЗИСТОРА НА КНИ ПОДЛОЖКЕ | 2003 |

|

RU2312422C2 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Устройство для магнитно-импульсной сварки деталей | 1973 |

|

SU522020A1 |

Авторы

Даты

2017-07-26—Публикация

2016-06-17—Подача