Область техники, к которой относится изобретение

[0001] Варианты осуществления настоящего раскрытия сущности относятся к подложке отображения и к способу ее изготовления, а также к устройству отображения.

Уровень техники

[0002] В области техники отображения, пиксельная матрица панели отображения, такой как жидкокристаллическая панель отображения или панель отображения на органических светодиодах (OLED), в общем, содержит множество линий затвора и множество линий передачи данных, перемежаемых с линиями затвора. Возбуждение линий затвора может достигаться посредством связанной интегрированной возбуждающей схемы. В последние годы, в силу непрерывного совершенствования процесса подготовки тонкопленочных транзисторов на основе аморфного кремния или оксидных тонкопленочных транзисторов, возбуждающая схема затвора также может непосредственно интегрироваться на матричной подложке из тонкопленочных транзисторов, чтобы формировать GOA (формирователь сигналов управления затвором на матрице) с возможностью возбуждать линии затвора. Например, GOA, включающий в себя множество единиц каскадных сдвиговых регистров, может использоваться для того, чтобы предоставлять сигналы напряжения для состояния включения/выключения (сигналы сканирования) во множество строк линий затвора пиксельной матрицы, за счет этого, например, управляя множеством строк линий затвора таким образом, что они последовательно включаются, и одновременно, линии передачи данных предоставляют сигналы данных в пиксельные единицы в соответствующей строке в пиксельной матрице, с тем чтобы формировать напряжения полутонов, требуемые для соответствующих шкал полутонов отображаемого изображения в соответствующих пиксельных единицах, за счет этого отображая одно кадровое изображение.

Сущность изобретения

[0003] По меньшей мере один вариант осуществления настоящего раскрытия сущности предоставляет подложку отображения, содержащую: базовую подложку, содержащую область пиксельной матрицы и периферийную область; и первую возбуждающую схему сканирования, множество линий питания, первую группу сигнальных линий и вторую группу сигнальных линий, которые находятся в периферийной области и расположены на первой стороне базовой подложки. Первая возбуждающая схема сканирования содержит множество каскадных первых сдвиговых регистров; множество линий питания выполнены с возможностью предоставлять множество напряжений питания во множество каскадных первых сдвиговых регистров в первой возбуждающей схеме сканирования; первая группа сигнальных линий содержит по меньшей мере одну линию синхронизирующего сигнала, выполненную с возможностью предоставлять по меньшей мере один синхронизирующий сигнал во множество каскадных первых сдвиговых регистров в первой возбуждающей схеме сканирования; вторая группа сигнальных линий содержит первую линию инициирующего сигнала, выполненную с возможностью соединения с первым сдвиговым регистром первого каскада из множества каскадных первых сдвиговых регистров в первой возбуждающей схеме сканирования и предоставлять первый инициирующий сигнал в первый сдвиговый регистр первого каскада; и первая линия инициирующего сигнала находится между множеством линий питания и областью пиксельной матрицы.

[0004] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, вторая группа сигнальных линий находится на стороне первой возбуждающей схемы сканирования, смежной с областью пиксельной матрицы, и первая группа сигнальных линий находится на стороне первой возбуждающей схемы сканирования, расположенной напротив стороны первой возбуждающей схемы сканирования, на которой расположена вторая группа сигнальных линий.

[0005] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, область пиксельной матрицы содержит первую область отображения и вторую область отображения, и первая область отображения и вторая область отображения помещаются рядом друг с другом и не перекрываются друг с другом, первая возбуждающая схема сканирования соединяется с первой областью отображения с возможностью возбуждать первую область отображения с возможностью отображать, подложка отображения дополнительно содержит вторую возбуждающую схему сканирования в периферийной области и расположена на первой стороне базовой подложки, вторая возбуждающая схема сканирования и первая возбуждающая схема сканирования последовательно размещаются вдоль направления сканирования области пиксельной матрицы, и вторая возбуждающая схема сканирования соединяется со второй областью отображения с возможностью возбуждать вторую область отображения с возможностью отображать. Вторая возбуждающая схема сканирования содержит множество каскадных вторых сдвиговых регистров, вторая группа сигнальных линий дополнительно содержит вторую линию инициирующего сигнала, выполненную с возможностью соединения со вторым сдвиговым регистром первого каскада из множества каскадных вторых сдвиговых регистров во второй возбуждающей схеме сканирования и предоставлять второй инициирующий сигнал во второй сдвиговый регистр первого каскада во второй возбуждающей схеме сканирования.

[0006] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, длина продолжения первой линии инициирующего сигнала и длина продолжения второй линии инициирующего сигнала являются идентичными длине размещения первой возбуждающей схемы сканирования и длине размещения второй возбуждающей схемы сканирования.

[0007] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, первая линия инициирующего сигнала и вторая линия инициирующего сигнала помещаются рядом.

[0008] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, множество линий питания содержат первую линию питания и вторую линию питания, и первая линия питания и вторая линия питания выполнены с возможностью предоставлять одно и то же первое напряжение питания.

[0009] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, ортографическая проекция первой линии питания на базовой подложке частично перекрывается с ортографической проекцией первой возбуждающей схемы сканирования на базовой подложке; и ортографическая проекция второй линии питания на базовой подложке находится между ортографической проекцией первой линии питания на базовой подложке и ортографической проекцией второй группы сигнальных линий на базовой подложке.

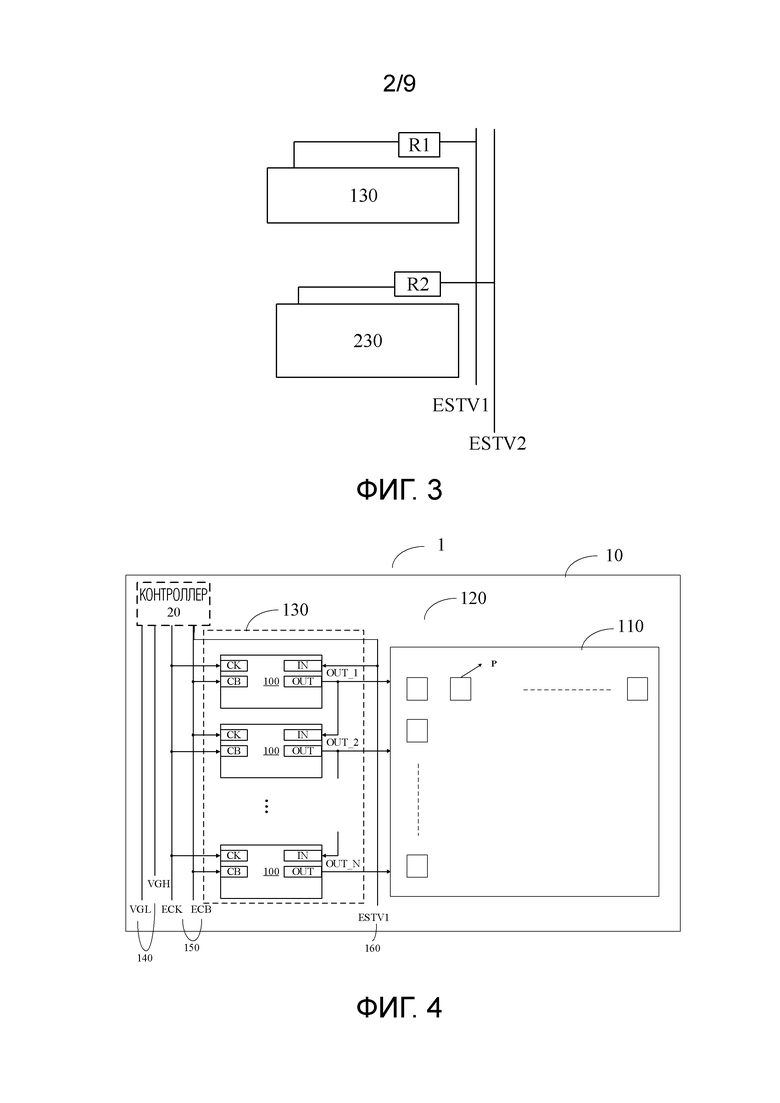

[0010] Например, подложка отображения, предоставленная посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, дополнительно содержит по меньшей мере один первый резистор, первый резистор находится на стороне, на удалении от первого сдвигового регистра первого каскада, первой возбуждающей схемы сканирования, и первая линия инициирующего сигнала соединяется с первым сдвиговым регистром первого каскада первой возбуждающей схемы сканирования через по меньшей мере один первый резистор.

[0011] Например, подложка отображения, предоставленная посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, дополнительно содержит по меньшей мере один второй резистор, второй резистор находится между первым сдвиговым регистром последнего каскада первой возбуждающей схемы сканирования и вторым сдвиговым регистром первого каскада второй возбуждающей схемы сканирования, и вторая линия инициирующего сигнала соединяется со вторым сдвиговым регистром первого каскада второй возбуждающей схемы сканирования через по меньшей мере один второй резистор.

[0012] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, значение сопротивления первого резистора отличается от значения сопротивления второго резистора.

[0013] Например, подложка отображения, предоставленная посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, дополнительно содержит линию сгиба между первой областью отображения и второй областью отображения, второй резистор расположен в направлении прохождения линии сгиба, и направление продолжения линии сгиба является перпендикулярным направлению продолжения первой группы сигнальных линий и направлению продолжения второй группы сигнальных линий.

[0014] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, ортографическая проекция по меньшей мере одного второго резистора на базовой подложке находится между ортографической проекцией первого сдвигового регистра последнего каскада первой возбуждающей схемы сканирования на базовой подложке и ортографической проекцией второго сдвигового регистра первого каскада второй возбуждающей схемы сканирования на базовой подложке.

[0015] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности по меньшей мере один первый резистор находится между базовой подложкой и второй группой сигнальных линий в направлении, перпендикулярном базовой подложке, и ортографическая проекция по меньшей мере одного первого резистора на базовой подложке находится на стороне, на удалении от области пиксельной матрицы, ортографической проекции второй группы сигнальных линий на базовой подложке.

[0016] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, материал первого резистора содержит полупроводниковый материал.

[0017] Например, подложка отображения, предоставленная посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, дополнительно содержит по меньшей мере одну первую соединительную линию и по меньшей мере одну вторую соединительную линию, первая соединительная линия соединяет один контактный вывод по меньшей мере одного первого резистора с первым сдвиговым регистром первого каскада первой возбуждающей схемы сканирования, и вторая соединительная линия соединяет другой контактный вывод по меньшей мере одного первого резистора с первой линией инициирующего сигнала.

[0018] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, первая соединительная линия и вторая соединительная линия находятся на стороне, на удалении от базовой подложки по меньшей мере одного первого резистора.

[0019] Например, подложка отображения, предоставленная посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, дополнительно содержит первую проводящую соединительную часть, вторую проводящую соединительную часть, первый изоляционный слой и второй изоляционный слой, первая проводящая соединительная часть и вторая проводящая соединительная часть находятся на стороне, на удалении от базовой подложки, первой соединительной линии и второй соединительной линии и находятся в том же слое, что и множество линий питания, первая группа сигнальных линий и вторая группы сигнальных линий; первый изоляционный слой находится между по меньшей мере одним первым резистором и первой соединительной линией или между по меньшей мере одним первым резистором и второй соединительной линией в направлении, перпендикулярном базовой подложке, второй изоляционный слой находится между первой соединительной линией и первой проводящей соединительной частью или между первой соединительной линией и второй проводящей соединительной частью, или между второй соединительной линией и первой проводящей соединительной частью, или между второй соединительной линией и второй проводящей соединительной частью в направлении, перпендикулярном базовой подложке; один контактный вывод первой проводящей соединительной части соединяется с одним контактным выводом первой соединительной линии через отверстие, проникающее через второй изоляционный слой, и другой контактный вывод первой проводящей соединительной части соединяется с одним контактным выводом по меньшей мере одного первого резистора через отверстие, проникающее через первый изоляционный слой и второй изоляционный слой; другой контактный вывод первой соединительной линии соединяется с первым сдвиговым регистром первого каскада первой возбуждающей схемы сканирования; один контактный вывод второй проводящей соединительной части соединяется с одним контактным выводом второй соединительной линии через отверстие, проникающее через второй изоляционный слой, и другой контактный вывод второй проводящей соединительной части соединяется с другим контактным выводом по меньшей мере одного первого резистора через отверстие, проникающее через первый изоляционный слой и второй изоляционный слой; и другой контактный вывод второй соединительной линии соединяется с первой линией инициирующего сигнала через отверстие, проникающее через второй изоляционный слой.

[0020] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, каждый из множества каскадных первых сдвиговых регистров первой возбуждающей схемы сканирования, содержит первый составляющий транзистор, который соединяется с первой линией питания, и содержит второй составляющий транзистор и третий составляющий транзистор, которые соединяются со второй линией питания, ортографическая проекция первого составляющего транзистора на базовой подложке находится между ортографической проекцией первой группы сигнальных линий на базовой подложке и ортографической проекцией первой линии питания на базовой подложке и находится рядом с ортографической проекцией первой линии питания на базовой подложке, ортографическая проекция второго составляющего транзистора на базовой подложке и ортографическая проекция третьего составляющего транзистора на базовой подложке находятся между ортографической проекцией первой линии питания на базовой подложке и ортографической проекцией второй линии питания на базовой подложке и находятся рядом с ортографической проекцией второй линии питания на базовой подложке.

[0021] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, множество линий питания содержат третью линию питания и четвертую линию питания, третья линия питания и четвертая линия питания выполнены с возможностью предоставлять одно и то же второе напряжение питания; ортографическая проекция четвертой линии питания на базовой подложке частично перекрывается с ортогональной частью первой возбуждающей схемы сканирования на базовой подложке; ортографическая проекция третьей линии питания на базовой подложке находится между ортографической проекцией четвертой линии питания на базовой подложке и ортографической проекцией первой группы сигнальных линий на базовой подложке.

[0022] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, каждый из множества каскадных первых сдвиговых регистров первой возбуждающей схемы сканирования дополнительно содержит четвертый составляющий транзистор, соединенный с третьей линией питания, и пятый составляющий транзистор, соединенный с четвертой линией питания, ортографическая проекция четвертого составляющего транзистора на базовой подложке находится на стороне, на удалении от ортографической проекции первой группы сигнальных линий на базовой подложке, ортографической проекции третьей линии питания на базовой подложке и находится рядом с ортографической проекцией третьей линии питания на базовой подложке, ортографическая проекция пятого составляющего транзистора на базовой подложке находится между ортографической проекцией четвертой линии питания на базовой подложке и ортографической проекцией второй группы сигнальных линий на базовой подложке и находится рядом с ортографической проекцией четвертой линии питания на базовой подложке.

[0023] По меньшей мере один вариант осуществления настоящего раскрытия сущности предоставляет подложку отображения, содержащую: базовую подложку, содержащую область пиксельной матрицы и периферийную область, и первую возбуждающую схему сканирования, множество линий питания, первую группу сигнальных линий и вторую группу сигнальных линий, которые находятся в периферийной области и расположены на первой стороне базовой подложки. Первая возбуждающая схема сканирования содержит множество каскадных первых сдвиговых регистров; множество линий питания выполнены с возможностью предоставлять множество напряжений питания во множество каскадных первых сдвиговых регистров в первой возбуждающей схеме сканирования; первая группа сигнальных линий содержит по меньшей мере одну линию синхронизирующего сигнала, выполненную с возможностью предоставлять по меньшей мере один синхронизирующий сигнал во множество каскадных первых сдвиговых регистров в первой возбуждающей схеме сканирования; вторая группа сигнальных линий содержит первую линию инициирующего сигнала, выполненную с возможностью соединения с первым сдвиговым регистром первого каскада из множества каскадных первых сдвиговых регистров в первой возбуждающей схеме сканирования и предоставлять первый инициирующий сигнал в первый сдвиговый регистр первого каскада, первая возбуждающая схема сканирования содержит первый транзистор, второй транзистор и третий транзистор, и первый транзистор, второй транзистор и третий транзистор, соответственно, соединяются с первой группой сигнальных линий, направление продолжения канала первого транзистора, направление продолжения канала второго транзистора и направление продолжения канала третьего транзистора являются параллельными направлению продолжения первой группы сигнальных линий и направлению продолжения второй группы сигнальных линий.

[0024] Например, в подложке отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, первая возбуждающая схема сканирования дополнительно содержит шестой транзистор и седьмой транзистор, и шестой транзистор и седьмой транзистор, соответственно, соединяются с первой группой сигнальных линий, направление продолжения канала шестого транзистора и направление продолжения канала седьмого транзистора являются параллельными направлению продолжения первой группы сигнальных линий и направлению продолжения второй группы сигнальных линий.

[0025] По меньшей мере один вариант осуществления настоящего раскрытия сущности предоставляет устройство отображения, содержащее подложку отображения согласно любому из вариантов осуществления настоящего раскрытия сущности.

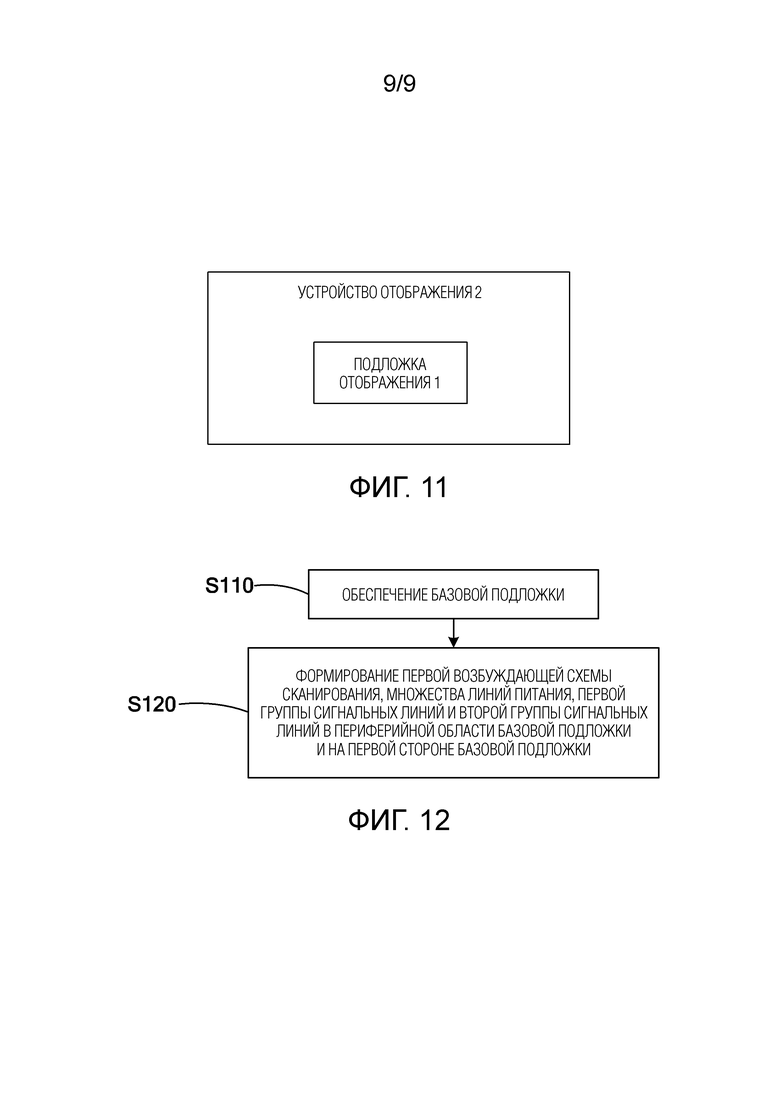

[0026] По меньшей мере один вариант осуществления настоящего раскрытия сущности предоставляет способ изготовления подложки отображения, содержащий: обеспечение базовой подложки; и последовательное формирование полупроводникового слоя, первого изоляционного слоя, первого проводящего слоя, второго изоляционного слоя, второго проводящего слоя, третьего изоляционного слоя и третьего проводящего слоя на базовой подложке в направлении, перпендикулярном базовой подложке. Множество линий питания, первая группа сигнальных линий и вторая группа сигнальных линий находятся в третьем проводящем слое; первая возбуждающая схема сканирования формируется в полупроводниковом слое, первом проводящем слое и втором проводящем слое; и первая возбуждающая схема сканирования, соответственно, соединяется с множеством линий питания, первой группой сигнальных линий и второй группой сигнальных линий через отверстия, проникающие через первый изоляционный слой, второй изоляционный слой и третий изоляционный слой.

Краткое описание чертежей

[0027] Чтобы ясно иллюстрировать технические решения вариантов осуществления раскрытия сущности, ниже кратко описываются чертежи вариантов осуществления; очевидно, что описанные чертежи относятся только к некоторым вариантам осуществления раскрытия сущности и в силу этого не ограничивают раскрытие сущности.

[0028] Фиг. 1 является принципиальной схемой светоизлучающего управляющего сдвигового регистра;

[0029] Фиг. 2 является временной диаграммой сигналов в случае, если светоизлучающий управляющий сдвиговый регистр, как показано на фиг. 1, работает;

[0030] Фиг. 3 является принципиальной схемой первого резистора и второго резистора, предоставленных посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности;

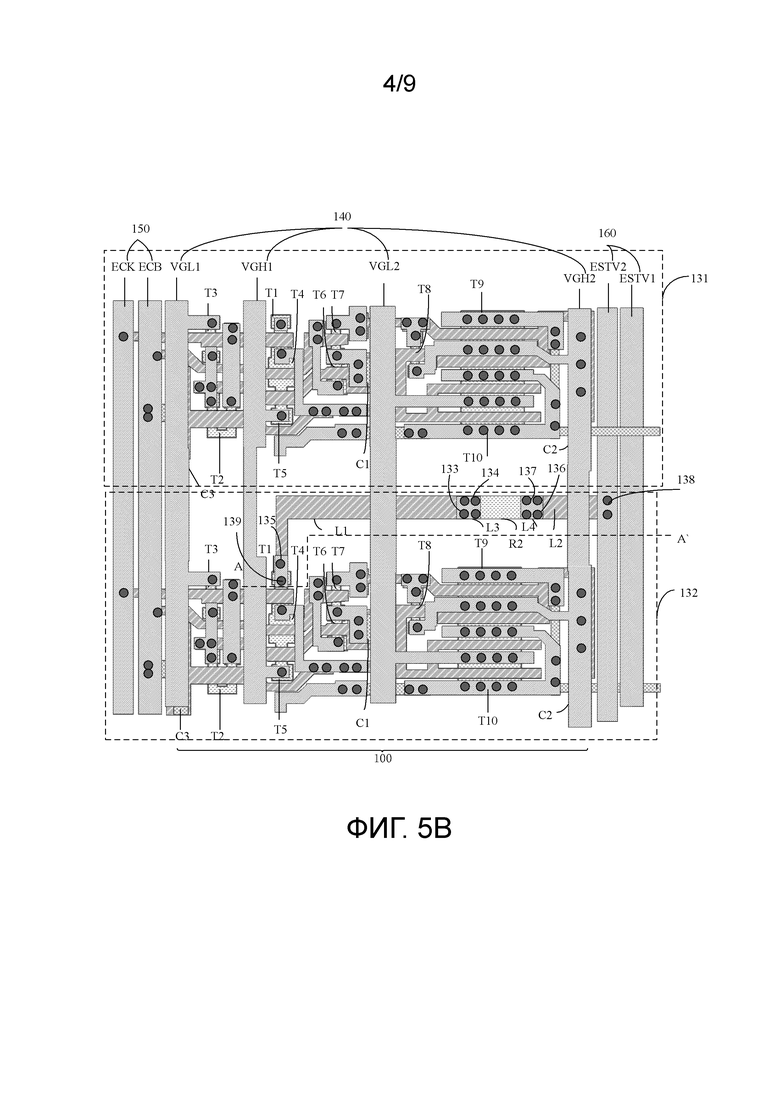

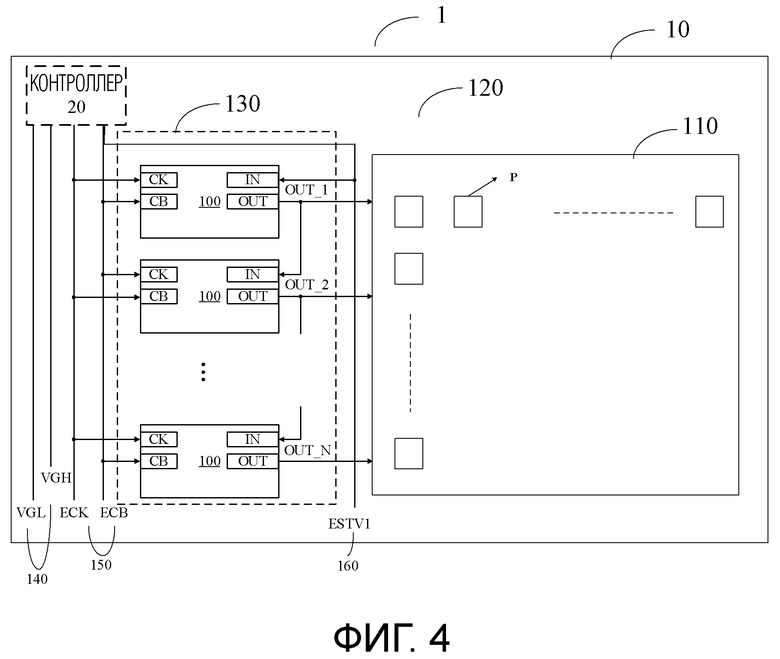

[0031] Фиг. 4 является принципиальной схемой подложки отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности;

[0032] Фиг. 5A является принципиальной схемой, показывающей компоновку подложки отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности;

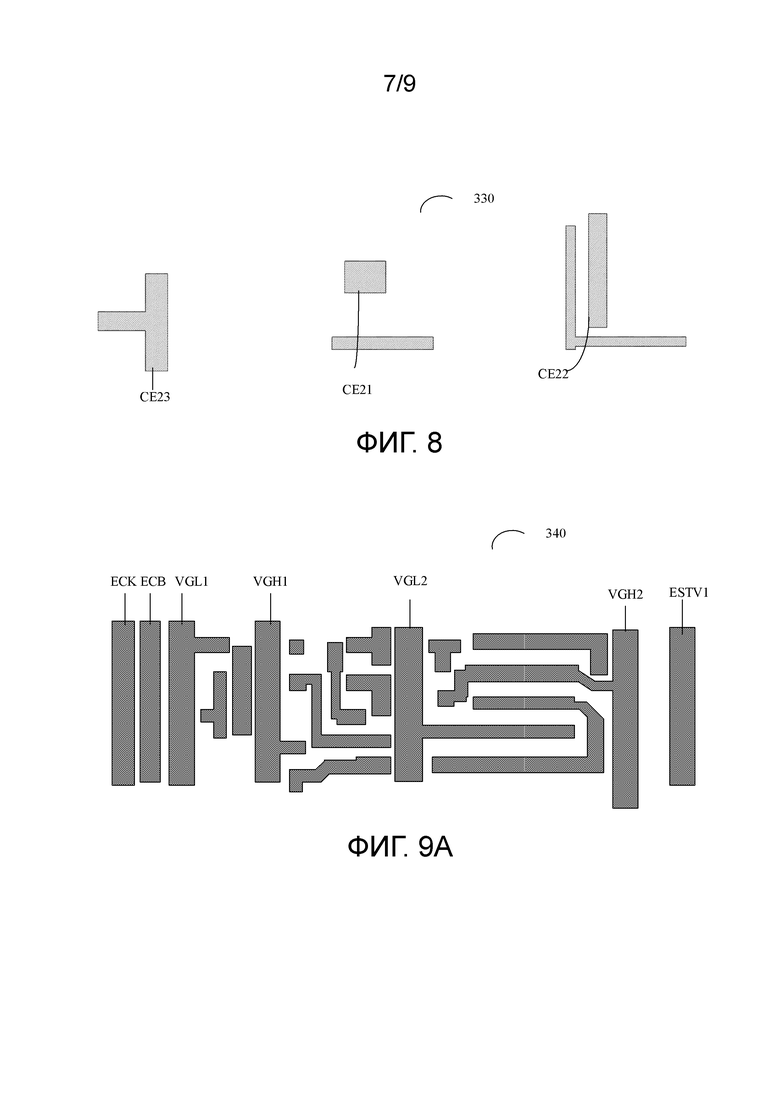

[0033] Фиг. 5B является принципиальной схемой, показывающей компоновку подложки отображения, включающей в себя сдвиговый регистр первого каскада второй возбуждающей схемы сканирования;

[0034] Фиг. 6A, 7A, 8 и 9A являются плоскими схемами, показывающими межсоединения соответствующих слоев подложки отображения, как показано на фиг. 5A, соответственно;

[0035] Фиг. 6B, 7B, 8 и 9B являются плоскими схемами, показывающими межсоединения соответствующих слоев сдвигового регистра первого каскада, включенного в подложку отображения, как показано на фиг. 5B, соответственно;

[0036] Фиг. 10 является видом в поперечном сечении подложки отображения, как показано на фиг. 5B, вдоль линии A–A';

[0037] Фиг. 11 является принципиальной схемой устройства отображения, предоставленного посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности; и

[0038] Фиг. 12 является блок–схемой последовательности операций способа изготовления подложки отображения, предоставленной посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности.

Подробное описание изобретения

[0039] Чтобы обеспечивать очевидность целей, технических подробностей и преимуществ вариантов осуществления раскрытия сущности, технические решения вариантов осуществления должны описываться четко и понятно в связи с чертежами, связанными с вариантами осуществления раскрытия сущности. Очевидно, что описанные варианты осуществления составляют только часть, а не все варианты осуществления раскрытия сущности. На основе описанных вариантов осуществления в данном документе, специалисты в данной области техники могут получать другой вариант(ы) осуществления без изобретательских усилий, что должно находиться в пределах объема раскрытия сущности.

[0040] Если не указано иное, все технические и научные термины, используемые в данном документе, имеют смысловые значения, идентичные значениям, обычно понимаемым специалистами в области техники, которой принадлежит настоящее раскрытие сущности. Термины, "первый", "второй" и т.д., которые используются в настоящем раскрытии сущности, имеют намерение не указывать любую последовательность, величину или значимость, а отличать различные компоненты. Кроме того, такие термины в единственном числе имеют намерение не ограничивать величину, а указывать наличие по меньшей мере одного. Термины "содержать", "содержащий", "включать в себя", "включающий в себя" и т.д. имеют намерение указывать то, что элементы или объекты, приведенные перед этими терминами, охватывают элементы или объекты и их эквиваленты, перечисленные после этих терминов, но не исключают другие элементы или объекты. Фразы "соединяться", "соединенный" и т.д. имеют намерение не задавать физическое соединение или механическое соединение, а могут включать в себя электрическое соединение, прямо или косвенно. "На", "под", "правый", "левый" и т.п. используются только для того, чтобы указывать относительную позиционную взаимосвязь, и когда позиция объекта, который описывается, изменяется, относительная позиционная взаимосвязь может изменяться, соответственно.

[0041] Ниже описывается настоящее раскрытие сущности со ссылкой на несколько конкретных вариантов осуществления. Чтобы обеспечивать ясность и точность нижеприведенного описания вариантов осуществления настоящего раскрытия сущности, настоящее раскрытие сущности опускает подробное описание известных функций и известных компонентов. В случае если любой компонент варианта осуществления настоящего раскрытия сущности появляется более чем на одном из чертежей, компонент обозначается посредством той же ссылочной позиции на каждом из чертежей.

[0042] Фиг. 1 является принципиальной схемой светоизлучающего управляющего сдвигового регистра. Фиг. 2 является временной диаграммой сигналов в случае, если светоизлучающий управляющий сдвиговый регистр, как показано на фиг. 1, работает. Ниже кратко описывается рабочий процесс светоизлучающего управляющего сдвигового регистра со ссылкой на фиг. 1 и фиг. 2.

[0043] Как показано на фиг. 1, светоизлучающий управляющий сдвиговый регистр 100 содержит десять транзисторов (первый транзистор T1, второй транзистор T2, ..., десятый транзистор T10) и три конденсатора (первый конденсатор C1, второй конденсатор C2 и третий конденсатор C3). Например, в случае если множество светоизлучающих управляющих сдвиговых регистров каскадируются, первый электрод первого транзистора T1 в светоизлучающем управляющем сдвиговом регистре 100 первого каскада выполнен с возможностью соединения с первой линии ESTV1 инициирующего сигнала, чтобы принимать первый инициирующий сигнал ESTV1, первый электрод первого транзистора T1 в каждом из других каскадов светоизлучающих управляющих сдвиговых регистров 100 соединяется со светоизлучающим управляющим сдвиговым регистром 100 предыдущего каскада, чтобы принимать первый выходной сигнал EM, выводимый посредством светоизлучающего управляющего сдвигового регистра 100 предыдущего каскада.

[0044] Помимо этого, на фиг. 1 и фиг. 2, CK представляет контактный вывод первого синхросигнала, ECK представляет линию первого синхросигнала и первый синхросигнал, и контактный вывод CK первого синхросигнала соединяется с линией ECK первого синхросигнала, чтобы принимать первый синхросигнал; CB представляет контактный вывод второго синхросигнала, ECB представляет линию второго синхросигнала и второй синхросигнал, и контактный вывод CB второго синхросигнала соединяется с линией ECB второго синхросигнала, чтобы принимать второй синхросигнал, например, первый синхросигнал ECK и второй синхросигнал ECB могут использовать импульсный сигнал со скважностью импульсов больше 50%; и VGH1 представляет первую линию питания и первое напряжение питания, предоставленное посредством первой линии питания. Например, первое напряжение питания представляет собой постоянное напряжение высокого уровня, и VGL1 представляет третью линию питания и второе напряжение питания, предоставленное посредством третьей линии питания, например, второе напряжение питания представляет собой постоянное напряжение низкого уровня, и первое напряжение питания превышает второе напряжение питания; и N1, N2, N3 и N4 представляют первый узел, второй узел, третий узел и четвертый узел, соответственно.

[0045] Как показано на фиг. 1, электрод затвора первого транзистора T1 соединяется с контактным выводом CK первого синхросигнала (т.е. с линией ECK первого синхросигнала), чтобы принимать первый синхросигнал, первый электрод первого транзистора T1 соединяется с входным контактным выводом IN, и второй электрод первого транзистора T1 соединяется с первым узлом N1. Например, в случае если светоизлучающий управляющий сдвиговый регистр представляет собой сдвиговый регистр первого каскада, входной контактный вывод IN соединяется с первой линией ESTV1 инициирующего сигнала, чтобы принимать первый инициирующий сигнал, в случае если светоизлучающий управляющий сдвиговый регистр представляет собой сдвиговый регистр, отличный от сдвигового регистра первого каскада, входной контактный вывод IN светоизлучающего управляющего сдвигового регистра соединяется с выходным контактным выводом OUT светоизлучающего управляющего сдвигового регистра предыдущего каскада для светоизлучающего управляющего сдвигового регистра.

[0046] Электрод затвора второго транзистора T2 соединяется с первым узлом N1, первый электрод второго транзистора T2 соединяется с линией ECK первого синхросигнала, чтобы принимать первый синхросигнал, и второй электрод второго транзистора T2 соединяется со вторым узлом N2.

[0047] Электрод затвора третьего транзистора T3 соединяется с линией ECK первого синхросигнала, чтобы принимать первый синхросигнал, первый электрод третьего транзистора T3 соединяется с третьей линией VGL1 питания, чтобы принимать второе напряжение питания, и второй электрод третьего транзистора T3 соединяется со вторым узлом N2.

[0048] Электрод затвора четвертого транзистора T4 соединяется с контактным выводом CB второго синхросигнала (т.е. с линией ECB второго синхросигнала), чтобы принимать второй синхросигнал, первый электрод четвертого транзистора T4 соединяется с первым узлом N1, и второй электрод четвертого транзистора T4 соединяется с первым электродом пятого транзистора T5.

[0049] Электрод затвора пятого транзистора T5 соединяется со вторым узлом N2, и второй электрод пятого транзистора T5 соединяется с первой линией VGH питания, чтобы принимать первое напряжение питания.

[0050] Электрод затвора шестого транзистора T6 соединяется со вторым узлом N2, первый электрод шестого транзистора T6 соединяется с линией ECB второго синхросигнала, чтобы принимать второй синхросигнал, и второй электрод шестого транзистора T6 соединяется с третьим узлом N3.

[0051] Первый контактный вывод первого конденсатора C1 соединяется со вторым узлом N2, и второй контактный вывод первого конденсатора C1 соединяется с третьим узлом N3.

[0052] Электрод затвора седьмого транзистора T7 соединяется с линией ECB второго синхросигнала, чтобы принимать второй синхросигнал, первый электрод седьмого транзистора T7 соединяется с третьим узлом N3, и второй электрод седьмого транзистора T7 соединяется с четвертым узлом N4.

[0053] Электрод затвора восьмого транзистора T8 соединяется с первым узлом N1, первый электрод восьмого транзистора T8 соединяется с первой линией VGH1 питания, чтобы принимать первое напряжение питания, и второй электрод восьмого транзистора T8 соединяется с четвертым узлом N4.

[0054] Электрод затвора девятого транзистора T9 соединяется с четвертым узлом N4, первый электрод девятого транзистора T9 соединяется с первой линией VGH1 питания, чтобы принимать первое напряжение питания, и второй электрод девятого транзистора T9 соединяется с выходным контактным выводом OUT.

[0055] Первый контактный вывод третьего конденсатора C3 соединяется с четвертым узлом N4, и второй контактный вывод третьего конденсатора C3 соединяются с первой линией VGH1 питания, чтобы принимать первое напряжение питания.

[0056] Электрод затвора десятого транзистора T10 соединяется с первым узлом N1, первый электрод десятого транзистора T10 соединяется с третьей линией VGL1 питания, чтобы принимать второе напряжение питания, и второй электрод десятого транзистора T10 соединяется с выходным контактным выводом OUT.

[0057] Первый контактный вывод второго конденсатора C2 соединяется с линией ECB второго синхросигнала, чтобы принимать второй синхросигнал, и второй контактный вывод второго конденсатора C2 соединяется с первым узлом N1.

[0058] Транзисторы в светоизлучающем управляющем сдвиговом регистре 100, как показано на фиг. 1, описываются посредством рассмотрения транзисторов с каналом p–типа в качестве примера, т.е. каждый транзистор включается в случае, если электрод затвора каждого транзистора соединяется с низким уровнем, и каждый транзистор выключается в случае, если электрод затвора каждого транзистора соединяется с высоким уровнем. В этом случае, первый электрод может представлять собой электрод истока, и второй электрод может представлять собой электрод стока.

[0059] Вариант осуществления настоящего раскрытия сущности содержит, но не только, конфигурацию, как показано на фиг. 1, например, соответствующие транзисторы в светоизлучающем управляющем сдвиговом регистре 100, как показано на фиг. 1, также могут представлять собой транзисторы с каналом n–типа или могут представлять собой транзисторы с каналом p–типа и транзисторы с каналом n–типа, при условии, что полярности порта выбранного типа транзистора, соответственно, соединяются в соответствии с полярностями порта соответствующего транзистора в вариантах осуществления настоящего раскрытия сущности.

[0060] Фиг. 2 является временной диаграммой сигналов в случае, если светоизлучающий управляющий сдвиговый регистр, как показано на фиг. 1, работает. Ниже подробно описывается рабочий процесс светоизлучающего управляющего сдвигового регистра со ссылкой на фиг. 1 и фиг. 2. Например, в дальнейшем описывается принцип работы светоизлучающего управляющего сдвигового регистра 100 первого каскада, и принцип работы других каскадов светоизлучающих управляющих сдвиговых регистров 100 является аналогичным принципу работы светоизлучающего управляющего сдвигового регистра 100 первого каскада и не описывается снова. Как показано на фиг. 2, рабочий процесс светоизлучающего управляющего сдвигового регистра 100 содержит шесть фаз, а именно, первую фазу P1, вторую фазу P2, третью фазу P3, четвертую фазу P4, пятую фазу P5 и шестую фазу P6, и фиг. 2 показывает временные формы сигнала для соответствующих сигналов в каждой фазе.

[0061] В первой фазе P1, как показано на фиг. 2, первый синхросигнал ECK имеет низкий уровень, так что первый транзистор T1 и третий транзистор T3 включаются, и включенный первый транзистор T1 передает высокоуровневый первый инициирующий сигнал ESTV1 в первый узел N1 таким образом, что уровень первого узла N1 переходит к высокому уровню, так что второй транзистор T2, восьмой транзистор T8 и десятый транзистор T10 выключаются. Помимо этого, включенный третий транзистор T3 передает второе напряжение питания низкого уровня VGL1 во второй узел N2, в силу этого приводя к тому, что уровень второго узла N2 переходит к низкому уровню, так что пятый транзистор T5 и шестой транзистор T6 включаются. Поскольку второй синхросигнал ECB имеет высокий уровень, седьмой транзистор T7 выключается. Помимо этого, вследствие функции накопления третьего конденсатора C3, уровень четвертого узла N4 может поддерживаться равным высокому уровню, в силу этого приводя к тому, что девятый транзистор T9 выключается. В первой фазе P1, поскольку девятый транзистор T9 и десятый транзистор T10 выключаются, первый выходной сигнал, выводимый из выходного контактного вывода OUT_1 светоизлучающего управляющего сдвигового регистра 100, поддерживается равным предыдущему минимальному уровню.

[0062] Во второй фазе P2, как показано на фиг. 4, второй синхросигнал ECB имеет низкий уровень, так что четвертый транзистор T4 и седьмой транзистор T7 включаются. Поскольку первый синхросигнал ECK имеет высокий уровень, первый транзистор T1 и третий транзистор T3 выключаются. Вследствие функции накопления первого конденсатора C1, второй узел N2 может продолжать оставаться на низком уровне предыдущей фазы, так что пятый транзистор T5 и шестой транзистор T6 включаются. Первое напряжение VGH1 питания высокого уровня передается в первый узел N1 через включенный пятый транзистор T5 и включенный четвертый транзистор T4 таким образом, что уровень первого узла N1 продолжает оставаться на высоком уровне предыдущей фазы, так что второй транзистор T2, восьмой транзистор T8 и десятый транзистор T10 выключаются. Помимо этого, низкоуровневый второй синхросигнал ECB передается в четвертый узел N4 через включенный шестой транзистор T6 и включенный седьмой транзистор T7 таким образом, что уровень четвертого узла N4 переходит к низкому уровню, так что девятый транзистор T9 включается, включенный девятый транзистор T9 выводит первое напряжение VGH1 питания высокого уровня таким образом, что первый выходной сигнал, выводимый из выходного контактного вывода OUT_1 светоизлучающего управляющего сдвигового регистра 100 во второй фазе P2, имеет высокий уровень.

[0063] В третьей фазе P3, как показано на фиг. 4, первый синхросигнал ECK имеет низкий уровень, так что первый транзистор T1 и третий транзистор T3 включаются. Второй синхросигнал ECB имеет высокий уровень, так что четвертый транзистор T4 и седьмой транзистор T7 выключаются. Вследствие функции накопления третьего конденсатора C3, уровень четвертого узла N4 может поддерживаться равным низкому уровню предыдущей фазы, так что девятый транзистор T9 остается включенным, включенный девятый транзистор T9 выводит первое напряжение VGH1 питания высокого уровня таким образом, что первый выходной сигнал, выводимый из выходного контактного вывода OUT_1 светоизлучающего управляющего сдвигового регистра 100 в третьей фазе P3, по–прежнему имеет высокий уровень. Одновременно, в этой фазе, выходной контактный вывод OUT_2 светоизлучающего управляющего сдвигового регистра 100 второго каскада выводит сигнал с высоким уровнем (подробное описание светоизлучающего управляющего сдвигового регистра 100 второго каскада может ссылаться на рабочий процесс светоизлучающего управляющего сдвигового регистра первого каскада во второй фазе P2, описанный выше).

[0064] В четвертой фазе P4, как показано на фиг. 4, первый синхросигнал ECK имеет высокий уровень, так что первый транзистор T1 и третий транзистор T3 выключаются. Второй синхросигнал ECB имеет низкий уровень, так что четвертый транзистор T4 и седьмой транзистор T7 включаются. Вследствие функции накопления второго конденсатора C2, уровень первого узла N1 остается имеющим высокий уровень предыдущей фазы, так что второй транзистор T2, восьмой транзистор T8 и десятый транзистор T10 выключаются. Вследствие функции накопления первого конденсатора C1, второй узел N2 продолжает оставаться на низком уровне предыдущей фазы, так что пятый транзистор T5 и шестой транзистор T6 включаются. Помимо этого, низкоуровневый второй синхросигнал ECB передается в четвертый узел N4 через включенный шестой транзистор T6 и включенный седьмой транзистор T7, в силу этого приводя к тому, что уровень четвертого узла N4 переходит к низкому уровню, и в силу этого девятый транзистор T9 включается, включенный девятый транзистор T9 выводит первое напряжение VGH1 питания высокого уровня таким образом, что первый выходной сигнал, выводимый из выходного контактного вывода OUT_1 светоизлучающего управляющего сдвигового регистра 100 в четвертой фазе P4, по–прежнему имеет высокий уровень. Одновременно, в этой фазе, выходной контактный вывод OUT_2 светоизлучающего управляющего сдвигового регистра 100 второго каскада выводит сигнал с высоким уровнем (подробное описание светоизлучающего управляющего сдвигового регистра 100 второго каскада может ссылаться на рабочий процесс светоизлучающего управляющего сдвигового регистра первого каскада в третьей фазе P3, описанный выше).

[0065] В пятой фазе P5, как показано на фиг. 4, первый синхросигнал ECK имеет низкий уровень, так что первый транзистор T1 и третий транзистор T3 включаются. Второй синхросигнал ECB имеет высокий уровень, так что четвертый транзистор T4 и седьмой транзистор T7 выключаются. Включенный первый транзистор T1 передает низкоуровневый первый инициирующий сигнал ESTV в первый узел N1 таким образом, что уровень первого узла N1 переходит к низкому уровню.

[0066] Например, в пятой фазе P5, напряжение низкого уровня первого синхросигнала ECK составляет –6 В, и напряжение низкого уровня первого инициирующего сигнала ESTV1 составляет –6 В, и пороговое напряжение Vth первого транзистора T1 составляет –1,5 В. Поскольку первый транзистор T1 представляет собой транзистор с каналом p–типа, чтобы включать первый транзистор T1, напряжение Vgs между электродом затвора и электродом истока первого транзистора T1 должно быть меньше порогового напряжения Vth первого транзистора T1, и в силу этого в случае, если первый узел N1 заряжается до (–4,5) В, первый транзистор T1 выключается, и в это время, заряд первого узла N1 прекращается, т.е. в этой фазе, напряжение низкого уровня первого узла N1 составляет –4,5 В, так что второй транзистор T2, восьмой транзистор T8 и десятый транзистор T10 включаются. Включенный второй транзистор T2 передает низкоуровневый первый синхросигнал ECK во второй узел N2 таким образом, что уровень второго узла N2 дополнительно может понижаться, и в силу этого второй узел N2 продолжает оставаться на низком уровне предыдущей фазы, в силу этого приводя к тому, что пятый транзистор T5 и шестой транзистор T6 включаются. Помимо этого, включенный восьмой транзистор T8 передает первое напряжение VGH1 питания высокого уровня в четвертый узел N4, в силу этого приводя к тому, что уровень четвертого узла N4 переходит к высокому уровню, так что девятый транзистор T9 выключается. Включенный десятый транзистор T10 выводит второе напряжение VGL питания низкого уровня (например, –6 В) в ответ на низкий уровень (например, –4,5 В) первого узла N1, аналогично, пороговое напряжение Vth десятого транзистора T10 составляет –1,5 В, чтобы включать десятый транзистор T10, напряжение Vgs между электродом затвора и электродом истока десятого транзистора T10 должно быть меньше порогового напряжения Vth десятого транзистора T10, и в силу этого в случае, если напряжение, выводимое из выходного контактного вывода OUT, составляет –3 В, десятый транзистор T10 выключается, т.е. напряжение низкого уровня, выводимое из выходного контактного вывода OUT, составляет –3 В в этой фазе, так что выходной сигнал, выводимый из выходного контактного вывода OUT_1 светоизлучающего управляющего сдвигового регистра 100 в пятой фазе P5, становится первым низким уровнем (например, –3 В). Одновременно, в этой фазе, выходной контактный вывод OUT_2 светоизлучающего управляющего сдвигового регистра 100 второго каскада выводит сигнал с высоким уровнем (подробное описание светоизлучающего управляющего сдвигового регистра 100 второго каскада может ссылаться на рабочий процесс светоизлучающего управляющего сдвигового регистра первого каскада в четвертой фазе P4, описанный выше).

[0067] В шестой фазе P6, как показано на фиг. 4, первый синхросигнал ECK имеет высокий уровень, и второй синхросигнал ECB имеет низкий уровень, так что четвертый транзистор T4 и седьмой транзистор T7 включаются. Поскольку второй синхросигнал ECB изменяется с высокого уровня в пятой фазе P5 на низкий уровень, например, величина изменения составляет Δt (например, более 6 В), согласно эффекту использования компенсационной обратной связи второго конденсатора C2, уровень первого узла N1 изменяется с низкого уровня (например, –4,5 В) в пятой фазе P5 на более низкий уровень (например, –4,5 В–Δt), так что второй транзистор T2 и десятый транзистор T10 включаются под управлением низкого уровня (например, –4,5 В–Δt) первого узла N1, согласно характеристикам проводимости десятого транзистора T10, описанного выше, второе напряжение VGL питания низкого уровня (например, –6 В) может полностью выводиться на выходной контактный вывод OUT. Например, в шестой фазе P6, напряжение, выводимое из выходного контактного вывода OUT, имеет второй низкий уровень (например, –6 В). Одновременно, в этой фазе, выходной контактный вывод OUT_2 первого сдвигового регистра 100 второго каскада выводит сигнал с низким уровнем (например, –3 В, и подробное описание может ссылаться на рабочий процесс первого сдвигового регистра первого каскада в четвертой фазе P4, описанный выше).

[0068] Например, как показано на фиг. 1, на левой стороне подложки отображения, поскольку межсоединения являются плотными, пространство, оставленное для первой линии ESTV1 инициирующего сигнала, является небольшим, что неудобно для того, чтобы вводить множество линий инициирующего сигнала. Помимо этого, как показано на фиг. 1, поскольку имеется только одна первая линия VGH1 питания, и пятый транзистор T5, восьмой транзистор T8 и девятый транзистор T9 должны обматываться с помощью провода, чтобы соединяться с первой линией VGH1 напряжения питания, за счет этого увеличивая занятое пространство подложки отображения в вертикальном направлении, что является невыгодным для компоновочной конструкции подложки отображения.

[0069] По меньшей мере один вариант осуществления настоящего раскрытия сущности предоставляет подложку отображения, и подложка отображения содержит: базовую подложку, содержащую область пиксельной матрицы и периферийную область; и первую возбуждающую схему сканирования, множество линий питания, первую группу сигнальных линий и вторую группу сигнальных линий, которые находятся в периферийной области и расположены на первой стороне базовой подложки. Первая возбуждающая схема сканирования содержит множество каскадных первых сдвиговых регистров; множество линий питания выполнены с возможностью предоставлять множество напряжений питания во множество каскадных первых сдвиговых регистров в первой возбуждающей схеме сканирования; первая группа сигнальных линий содержит по меньшей мере одну линию синхронизирующего сигнала, выполненную с возможностью предоставлять по меньшей мере один синхронизирующий сигнал во множество каскадных первых сдвиговых регистров в первой возбуждающей схеме сканирования; вторая группа сигнальных линий содержит первую линию инициирующего сигнала, выполненную с возможностью соединения с первым сдвиговым регистром первого каскада из множества каскадных первых сдвиговых регистров в первой возбуждающей схеме сканирования и предоставлять первый инициирующий сигнал в первый сдвиговый регистр первого каскада; и первая линия инициирующего сигнала находится между множеством линий питания и областью пиксельной матрицы.

[0070] По меньшей мере один вариант осуществления настоящего раскрытия сущности также предоставляет устройство отображения и способ изготовления, соответствующие вышеуказанной подложке отображения.

[0071] В подложке отображения, предоставленной посредством вышеуказанного варианта осуществления настоящего раскрытия сущности, первая линия инициирующего сигнала располагается между множеством линий питания и областью пиксельной матрицы, чтобы упрощать введение сигнальных линий, что способствует отображению на панели отображения большого размера.

[0072] Ниже подробно описываются варианты осуществления настоящего раскрытия сущности и некоторые их примеры со ссылкой на прилагаемые чертежи.

[0073] По меньшей мере один вариант осуществления настоящего раскрытия сущности предоставляет подложку отображения. Например, подложка отображения может применяться к возбуждающей схеме сканирования, которая возбуждает одну строку каждый раз, т.е. выходной сигнал, выводимый посредством однокаскадного сдвигового регистра, возбуждает только одну строку пиксельных единиц. Поскольку нагрузки, которые должны возбуждаться посредством возбуждающей схемы сканирования, которая возбуждает одну строку каждый раз, меньше половины нагрузок, которые должны 1возбуждаться посредством возбуждающей схемы сканирования, которая возбуждает двойные строки каждый раз, и в силу этого возбуждающая схема сканирования, которая возбуждает одну строку каждый раз, имеет более сильную возбуждающую способность и является более подходящей для отображения на панели отображения большого размера.

[0074] Следует отметить, что подложка отображения также может применяться к возбуждающей схеме сканирования, которая возбуждает двойные строки каждый раз, т.е. выходной сигнал, выводимый посредством однокаскадного сдвигового регистра, может возбуждать две строки пиксельных единиц, и варианты осуществления настоящего раскрытия сущности не ограничены этим.

[0075] Фиг. 4 является принципиальной схемой подложки отображения согласно по меньшей мере одному варианту осуществления настоящего раскрытия сущности. Например, как показано на фиг. 4, подложка 1 отображения содержит: базовую подложку 10, первую возбуждающую схему 130 сканирования, множество линий 140 питания, первую группу 150 сигнальных линий и вторую группу 160 сигнальных линий.

[0076] Например, базовая подложка 100 может быть изготовлена, например, из стекла, пластика, кварца или других подходящих материалов, и варианты осуществления настоящего раскрытия сущности не ограничивают материал базовой подложки 100. Например, базовая подложка 10 содержит область 110 пиксельной матрицы и периферийную область 120, первая возбуждающая схема 130 сканирования, множество линий 140 питания, первая группа 150 сигнальных линий и вторая группа 160 сигнальных линий находятся в периферийной области 120 и расположены на первой стороне базовой подложки 10, например, на левой стороне базовой подложки 10.

[0077] Например, область 110 пиксельной матрицы включает в себя множество пиксельных единиц P, размещаемых в матрице. Например, каждая из множества пиксельных единиц P включает в себя пиксельную схему и, например, дополнительно может включать в себя светоизлучающий элемент (не показан).

[0078] Например, первая возбуждающая схема 130 сканирования содержит множество каскадных первых сдвиговых регистров 100, например, содержит множество первых сдвиговых регистров 100, как показано на фиг. 1. Для понятности и краткости, первый сдвиговый регистр 100 ниже называется просто сдвиговым регистром 100. Нижеприведенные варианты осуществления являются идентичными вариантам осуществления, описанным в данном документе, и аналогичные части не описываются снова. Например, выходные контактные выводы множества сдвиговых регистров 100, соответственно, соединяются со светоизлучающими управляющими контактными выводами соответствующих строк пиксельных схем, расположенных в области пиксельной матрицы, чтобы предоставлять выходные сигналы (например, светоизлучающие управляющие сигналы) в соответствующие строки пиксельных схем, за счет этого возбуждая светоизлучающие элементы с возможностью излучать свет. Например, пиксельная схема может представлять собой пиксельную схему, включающую в себя схемную структуру, например, 2T1C, 4T2C, 8T2C и т.п., в данной области техники, и подробности не описываются в данном документе.

[0079] Например, первая возбуждающая схема 130 сканирования включает в себя по меньшей мере один транзистор, и направление продолжения канала по меньшей мере одного транзистора является параллельным направлению продолжения первой группы 150 сигнальных линий и направлению продолжения второй группы 160 сигнальных линий, так что зона первой возбуждающей схемы 130 сканирования в направлении, перпендикулярном направлению длины канала, может уменьшаться, степень совпадения процесса повышается, и лучший канальный эффект формируется.

[0080] Например, первая возбуждающая схема 130 сканирования включает в себя первый транзистор T1, второй транзистор T2 и третий транзистор T3, первый транзистор T1, второй транзистор T2 и третий транзистор T3, соответственно, соединяются с первой группой 150 сигнальных линий, например, соединяются с линией ECK первого синхросигнала в первой группе 150 сигнальных линий. Например, направление продолжения канала первого транзистора T1, направление продолжения канала второго транзистора T2 и направление продолжения канала третьего транзистора T3 являются параллельными направлению продолжения первой группы 150 сигнальных линий и направлению продолжения второй группы 160 сигнальных линий. Например, направление продолжения канала транзистора представляет собой направление продолжения из первого электрода транзистора во второй электрод транзистора, например, направление продолжения из первого электрода первого транзистора T1 во второй электрод первого транзистора T1.

[0081] Например, первая возбуждающая схема 130 сканирования дополнительно включает в себя шестой транзистор T6 и седьмой транзистор T7, и шестой транзистор T6 и седьмой транзистор T7, соответственно, соединяются с первой группой 150 сигнальных линий. Направление продолжения канала шестого транзистора T6 и направление продолжения канала седьмого транзистора T7 являются параллельными направлению продолжения первой группы 150 сигнальных линий и направлению продолжения второй группы 160 сигнальных линий.

[0082] Например, множество линий 140 питания выполнены с возможностью предоставлять множество напряжений питания во множество каскадных сдвиговых регистров 100 в первой возбуждающей схеме 130 сканирования. Например, первое напряжение питания (к примеру, имеющее высокий уровень постоянного тока), второе напряжение питания (к примеру, имеющее низкий уровень постоянного тока) и т.п. предоставляются посредством множества линий 140 питания.

[0083] Первая группа 150 сигнальных линий содержит по меньшей мере одну линию синхронизирующего сигнала, например, содержит линию ECK первого синхросигнала и линию ECB второго синхросигнала, и по меньшей мере одна линия синхронизирующего сигнала выполнена с возможностью предоставлять по меньшей мере один синхронизирующий сигнал, к примеру, первый синхросигнал ECK и второй синхросигнал ECB, описанные выше, во множество каскадных сдвиговых регистров 100 в первой возбуждающей схеме 130 сканирования.

[0084] Например, в по меньшей мере одном примере, вторая группа 160 сигнальных линий содержит первую линию ESTV1 инициирующего сигнала, выполненную с возможностью соединения со сдвиговым регистром первого каскада во множестве каскадных сдвиговых регистров 100 в первой возбуждающей схеме 150 сканирования и предоставлять первый инициирующий сигнал в сдвиговый регистр первого каскада. Например, первая линия ESTV1 инициирующего сигнала расположена между множеством линий 140 питания и областью 110 пиксельной матрицы. Например, как показано на фиг. 4, первая линия ESTV1 инициирующего сигнала может быть расположена на правой стороне первой возбуждающей схемы 130 сканирования, т.е. ортографическая проекция первой линии ESTV1 инициирующего сигнала на базовой подложке 10 расположена между ортографической проекцией первой возбуждающей схемы 130 сканирования на базовой подложке 10 и ортографической проекцией области 110 пиксельной матрицы на базовой подложке 10. Конечно, первая линия ESTV1 инициирующего сигнала также может быть расположена между транзисторами первой возбуждающей схемы 130 сканирования, т.е. ортографическая проекция первой линии ESTV1 инициирующего сигнала на базовой подложке 10 и ортографическая проекция первой возбуждающей схемы 130 сканирования на базовой подложке 10 по меньшей мере частично перекрываются друг с другом, при условии, что может удовлетворяться то, что первая линия ESTV1 инициирующего сигнала располагается в зоне, в которой межсоединения не являются плотными, с тем чтобы упрощать введение линии инициирующего сигнала, и варианты осуществления настоящего раскрытия сущности не ограничены этим.

[0085] Следует отметить, что подложка отображения дополнительно может содержать множество возбуждающих схем сканирования и множество линий инициирующего сигнала, соответственно, соединенных со сдвиговыми регистрами первого каскада множества возбуждающих схем сканирования, и варианты осуществления настоящего раскрытия сущности не ограничивают этот случай.

[0086] Например, в некоторых примерах, в случае если подложка отображения дополнительно включает в себя множество возбуждающих схем сканирования, таких как вторая возбуждающая схема сканирования, третья возбуждающая схема сканирования и т.п., подложка отображения дополнительно включает в себя множество линий инициирующего сигнала, таких как вторая линия ESTV2 инициирующего сигнала, соединенная со сдвиговым регистром первого каскада второй возбуждающей схемы сканирования, и третья линия инициирующего сигнала, соединенная со сдвиговым регистром первого каскада третьей возбуждающей схемы сканирования. Например, множество возбуждающих схем сканирования, таких как вторая возбуждающая схема сканирования и третья возбуждающая схема сканирования, имеют структуру, идентичную структуре первой возбуждающей схемы сканирования, и первая возбуждающая схема сканирования и множество возбуждающих схем сканирования, таких как вторая возбуждающая схема сканирования и третья возбуждающая схема сканирования, последовательно размещаются, чтобы объединенно возбуждать область пиксельной матрицы подложки отображения. Например, область пиксельной матрицы включает в себя множество областей отображения, которые не перекрываются друг с другом (например, помещаются рядом), и множество возбуждающих схем сканирования, таких как первая возбуждающая схема сканирования, вторая возбуждающая схема сканирования и третья возбуждающая схема сканирования, соответственно, возбуждают области отображения, соответствующие им.

[0087] Например, в случае если множество возбуждающих схем сканирования включены, вторая группа 160 сигнальных линий дополнительно включает в себя множество линий инициирующего сигнала. Например, множество линий инициирующего сигнала могут быть расположены между множеством линий 140 питания и областью 110 пиксельной матрицы, например, могут быть расположены на правой стороне соответствующих возбуждающих схем сканирования или могут по меньшей мере частично перекрываться с соответствующими возбуждающими схемами сканирования, при условии, что может удовлетворяться то, что множество линий инициирующего сигнала располагаются в зоне, в которой межсоединения не являются плотными, с тем чтобы упрощать введение линий инициирующего сигнала, и варианты осуществления настоящего раскрытия сущности не ограничены этим.

[0088] Подложка отображения, предоставленная посредством вышеуказанного варианта осуществления настоящего раскрытия сущности, посредством регулирования позиции первой линии инициирующего сигнала, исключает такие проблемы, как неспособность вводить дополнительные сигнальные линии и соединение обмоток вследствие плотных межсоединений, и является более преимущественной для реализации конструкции с узкой рамкой панели отображения, за счет этого упрощая достижение отображения на панели отображения большого размера.

[0089] Фиг. 5A является принципиальной схемой, показывающей компоновку подложки отображения согласно по меньшей мере одному варианту осуществления настоящего раскрытия сущности. Фиг. 5B является принципиальной схемой, показывающей компоновку подложки отображения, включающей в себя сдвиговый регистр первого каскада второй возбуждающей схемы сканирования. Фиг. 10 является видом в поперечном сечении подложки отображения, как показано на фиг. 5B, вдоль линии A–A'. Конечно, фиг. 10 также может использоваться для того, чтобы пояснять пакетированную структуру, как показано на фиг. 5A.

[0090] Следует отметить, что пакетированная структура сдвигового регистра первого каскада, как показано на фиг. 5B, может применяться к сдвиговому регистру первого каскада каждой возбуждающей схемы сканирования, при условии, что соединение между сдвиговым регистром первого каскада каждой возбуждающей схемы сканирования и соответствующим инициирующим сигналом может изменяться, т.е. сдвиговый регистр первого каскада первой возбуждающей схемы сканирования соединяется с первой линией ESTV1 инициирующего сигнала, сдвиговый регистр первого каскада второй возбуждающей схемы сканирования соединяется со второй линией ESTV2 инициирующего сигнала, ..., и т.д.

[0091] Фиг. 6A, 7A, 8 и 9A являются плоскими схемами, показывающими межсоединения соответствующих слоев подложки отображения, как показано на фиг. 5A, соответственно. Фиг. 6A является плоской схемой, показывающей полупроводниковый слой подложки отображения согласно по меньшей мере одному варианту осуществления настоящего раскрытия сущности, фиг. 7A является плоской схемой, показывающей первый проводящий слой подложки отображения согласно по меньшей мере одному варианту осуществления настоящего раскрытия сущности, фиг. 8A является плоской схемой, показывающей второй проводящий слой подложки отображения согласно по меньшей мере одному варианту осуществления настоящего раскрытия сущности и фиг. 9A является плоской схемой, показывающей третий проводящий слой подложки отображения согласно по меньшей мере одному варианту осуществления настоящего раскрытия сущности.

[0092] Например, межслойные изоляционные слои (например, содержащие первый изоляционный слой, второй изоляционный слой и третий изоляционный слой) могут быть расположены между слоистыми структурами, как показано на фиг. 6A–9A. Например, первый изоляционный слой 350 (как показано на фиг. 10) расположен между полупроводниковым слоем 310, как показано на фиг. 6A, и первым проводящим слоем 320, как показано на фиг. 7A, второй изоляционный слой 360 (как показано на фиг. 10) расположен между первым проводящим слоем 320, как показано на фиг. 7A, и вторым проводящим слоем 330, как показано на фиг. 8, и третий изоляционный слой 370 (показан на фиг. 10) расположен между вторым проводящим слоем 330, как показано на фиг. 8, и третьим проводящим слоем 340, как показано на фиг. 9A.

[0093] Например, как показано на фиг. 10, подложка отображения дополнительно содержит четвертый изоляционный слой 380, и четвертый изоляционный слой 380 расположен на третьем проводящем слое 340 и выполнен с возможностью защищать третий проводящий слой 340.

[0094] Например, материалы первого изоляционного слоя 350, второго изоляционного слоя 360, третьего изоляционного слоя 370 и четвертого изоляционного слоя 380 могут содержать неорганический изоляционный материал, такой как SiNx, SiOx, SiNxOy, органический изоляционный материал, такой как органическая смола, либо другой подходящий материал, и варианты осуществления настоящего раскрытия сущности не ограничены этим.

[0095] Следует отметить, что, подложка отображения, как показано на фиг. 5A, описывается посредством рассмотрения компоновочной конструкции сдвигового регистра в первой возбуждающей схеме сканирования и сигнальной линии, соединенной со сдвиговым регистром, в качестве примера, компоновочные реализации оставшихся каскадов сдвиговых регистров могут означать компоновочную реализацию, как показано на фиг. 5A, и подробности не описываются в данном документе. Конечно, оставшиеся каскады сдвиговых регистров также могут приспосабливать другие компоновочные реализации, и варианты осуществления настоящего раскрытия сущности не ограничивают компоновочные реализации оставшихся каскадов сдвиговых регистров.

[0096] Ниже подробно описывается подложка отображения, предоставленная посредством по меньшей мере одного варианта осуществления настоящего раскрытия сущности, со ссылкой на фиг. 5A–9A.

[0097] Например, первый транзистор T1 – десятый транзистор T10 сдвигового регистра 100, как показано на фиг. 5A, могут формироваться на полупроводниковом слое 310, как показано на фиг. 6A. Полупроводниковый слой 310 может формировать рисунок с использованием полупроводникового материала. Например, как показано на фиг. 6A, полупроводниковый слой 310 может иметь короткую стержневидную форму или искривленную или изогнутую форму по мере необходимости и может использоваться для того, чтобы формировать активные слои первого транзистора T1 – десятого транзистора T10, описанных выше. Каждый из активных слоев может содержать область истока, область стока и область канала между областью истока и область стока. Например, область канала может быть легирована с примесями, чтобы иметь характеристики полупроводников; область истока и область стока расположены на обеих сторонах области канала и могут быть легированы с примесями и в силу этого иметь проводимость. Например, область истока соответствует электроду истока (или первому электроду) транзистора, и область стока соответствует электроду стока (или второму электроду) транзистора. Например, как показано на фиг. 10, посредством рассмотрения первого транзистора T1 в качестве примера, активный слой первого транзистора T1 содержит область S1 истока, область D1 стока (показана посредством пунктирной линии на фиг. 10) и область P1 канала, первый транзистор T1 дополнительно содержит электрод G1 затвора, электрод G1 затвора расположен в первом проводящем слое 320, который описывается ниже, и не описывается в данном документе. Следует отметить, что область D1 стока первого транзистора не показана в виде в поперечном сечении вдоль направления A–A' по фиг. 5B. Чтобы обеспечивать ясное описание, область D1 стока первого транзистора T1 добавляется с пунктирной линией на фиг. 10.

[0098] Например, материал полупроводникового слоя 310 может содержать оксидный полупроводник, органический полупроводник или аморфный кремний, поликристаллический кремний и т.п. Например, оксидный полупроводник содержит структуру "металл–оксид–полупроводник" (например, оксид индия, галия и цинка (IGZO)), поликристаллический кремний содержит низкотемпературный поликристаллический кремний или высокотемпературный поликристаллический кремний, и варианты осуществления настоящего раскрытия сущности не ограничивают материал полупроводникового слоя 310. Следует отметить, что вышеуказанные область истока и область стока могут представлять собой области, легированные с примесями n–типа или примесями p–типа, и варианты осуществления настоящего раскрытия сущности не ограничивают этот случай.

[0099] Следует отметить, что в других примерах, первый электрод и второй электрод каждого транзистора также могут быть расположены в другом проводящем слое и соединяются с соответствующим активным слоем через отверстия, расположенные в изоляционном слое между другим проводящим слоем и полупроводниковым слоем, и варианты осуществления настоящего раскрытия сущности не ограничивают этот случай.

[00100] Фиг. 7A показывает первый проводящий слой 320 подложки отображения, первый проводящий слой 320 располагается на первом изоляционном слое таким образом, что первый проводящий слой 320 изолируется от полупроводникового слоя 310. Например, первый проводящий слой 320 может содержать первые электроды CE11, CE12, CE13 первого конденсатора C1 – третьего конденсатора C3 и электроды затвора первого транзистора T1 – десятого транзистора T10, и, соответственно, первый изоляционный слой также упоминается как изоляционный слой затвора. Как показано на фиг. 7A, электроды затвора первого транзистора T1 – десятого транзистора T10, соответственно, представляют собой перекрывающиеся части структур полупроводникового слоя соответствующих транзисторов и межсоединений в первом проводящем слое 320.

[00101] Фиг. 8 показывает второй проводящий слой 330 подложки отображения, и второй проводящий слой 330 включает в себя вторые электроды CE21, CE22 и CE23 первого конденсатора C1 – третьего конденсатора C3. Например, второй электрод CE21 по меньшей мере частично перекрывается с первым электродом CE11, чтобы формировать первый конденсатор C1, второй электрод CE22 по меньшей мере частично перекрывается с первым электродом CE12, чтобы формировать второй конденсатор C2, и второй электрод CE23 по меньшей мере частично перекрывается с первым электродом CE13, чтобы формировать третий конденсатор C3.

[00102] Фиг. 9A показывает третий проводящий слой 340 подложки отображения, и третий проводящий слой 340 содержит первую группу 150 сигнальных линий, множество линий 140 питания и вторую группу 160 сигнальных линий. Следует отметить, что третий проводящий слой дополнительно содержит проводящие соединительные части для соединения соответствующих транзисторов, конденсаторов и сигнальных линий. Как показано на фиг. 5A и 9A, первая группа 150 сигнальных линий, множество линий 140 питания и вторая группа 160 сигнальных линий соединяются с транзисторами, которые должны соединяться с первой группой 150 сигнальных линий, множеством линий 140 питания и второй группой 160 сигнальных линий, в оставшихся слоях через по меньшей мере одно отверстие, и транзисторы также соединяются через по меньшей мере одно отверстие или имеют мостовое соединение через проводящие соединительные части, и подробности не описываются повторно в данном документе.

[00103] Например, материал вышеописанного третьего проводящего слоя 340 может содержать алюминий, алюминиевый сплав, медь, медный сплав или любой другой подходящий материал, что не ограничено посредством вариантов осуществления настоящего раскрытия сущности. Например, материал первого проводящего слоя 320 и материал второго проводящего слоя 330 могут быть теми же, что и материал третьего проводящего слоя 340, и подробности не описываются повторно в данном документе.

[00104] Фиг. 5A является принципиальной схемой, показывающей пакетированную позиционную взаимосвязь полупроводникового слоя 310, как показано на фиг. 6A, первого проводящего слоя 320, как показано на фиг. 7A, второго проводящего слоя 330, как показано на фиг. 8, и третьего проводящего слоя 340, как показано на фиг. 9A.

[00105] Как показано на фиг. 5A и фиг. 9A в по меньшей мере одном примере, подложка отображения содержит первую группу 150 сигнальных линий (например, содержащую линию ECK первого синхросигнала и линию ECB второго синхросигнала), множество линий 140 питания (например, содержащих третью линию VGL1 питания, первую линию VGH1 питания и четвертую линию VGL2 питания) и вторую группу 160 сигнальных линий (например, содержащую первую линию ESTV1 инициирующего сигнала), и первая группа 150 сигнальных линий, множество линий 140 питания и вторая группа 160 сигнальных линий последовательно располагаются в направлении строк. Следует отметить, что в случае, если подложка отображения содержит вторую возбуждающую схему сканирования, например, вторая группа 160 сигнальных линий дополнительно содержит вторую линию ESTV2 инициирующего сигнала.

[00106] В некоторых вариантах осуществления, как показано на фиг. 4 или фиг. 5A, вторая группа 160 сигнальных линий расположена на стороне первой возбуждающей схемы 130 сканирования, смежной с областью 110 пиксельной матрицы, и первая группа 150 сигнальных линий расположена на другой стороне первой возбуждающей схемы 130 сканирования, расположенной напротив стороны, на которой расположена вторая группа 160 сигнальных линий. Например, как показано на фиг. 4 или фиг. 5A, вторая группа 160 сигнальных линий расположена на правой стороне сдвигового регистра 100, и первая группа 150 сигнальных линий расположена на левой стороне сдвигового регистра 100.

[00107] В варианте осуществления, посредством расположения второй группы 160 сигнальных линий, содержащей первую линию ESTV1 инициирующего сигнала и вторую линию ESTV2 инициирующего сигнала, на правой стороне сдвигового регистра, т.е. вторая группа 160 сигнальных линий располагается отдельно от первой группы сигнальных линий 150 и множества линий 140 питания таким образом, чтобы исключать плотные межсоединения, вызываемые посредством слишком большого числа сигнальных линий, расположенных на левой стороне, за счет этого исключая такую проблему, что пространство, оставленное для линий инициирующего сигнала, является слишком небольшим вследствие плотных межсоединений, что затрагивает введение других сигнальных линий.

[00108] В некоторых других примерах, как показано на фиг. 5A, множество линий 140 питания содержат первую линию VGH1 питания, вторую линию VGH2 питания, третью линию VGL1 питания и четвертую линию VGL2 питания. Например, первая линия VGH1 питания и вторая линия VGH2 питания предоставляют одно и то же первое напряжение питания, например, высокое постоянное напряжение.

[00109] Например, ортографическая проекция первой линии VGH1 питания на базовой подложке 10 частично перекрывается с ортографической проекцией первой возбуждающей схемы сканирования на базовой подложке 10; и ортографическая проекция второй линии VGH2 питания на базовой подложке 10 расположена между ортографической проекцией первой линии VGH1 питания на базовой подложке 10 и ортографической проекцией второй группы 160 сигнальных линий на базовой подложке 10.

[00110] Следует отметить, что ортографическая проекция первой возбуждающей схемы сканирования на базовой подложке 10 не представляет собой непрерывную зону, и в силу этого ортографическая проекция первой линии VGH1 питания на базовой подложке 10 должна только перекрываться с ортографической проекцией части транзисторов или конденсаторов первой возбуждающей схемы сканирования на базовой подложке 10. Варианты осуществления настоящего раскрытия сущности не ограничены этим. Например, как показано на фиг. 5A, ортографическая проекция первой линии VGH1 питания на базовой подложке 10 перекрывается с межсоединениями первого проводящего слоя 320, например, ортографическая проекция первой линии VGH1 питания на базовой подложке 10 частично перекрывается с межсоединением, соединяющим электрод затвора третьего транзистора T3 и электрод затвора первого транзистора T1, межсоединением, соединяющим электрод затвора четвертого транзистора T4, межсоединением, соединяющим электрод затвора пятого транзистора T5, и межсоединением, соединяющим электрод затвора второго транзистора T2.

[00111] Например, как показано на фиг. 5A, каждый сдвиговый регистр первой возбуждающей схемы сканирования содержит первый составляющий транзистор, который соединяется с первой линией VGH1 питания, и второй составляющий транзистор и третий составляющий транзистор, которые соединяются со второй линией VGH2 питания. Например, пятый транзистор T5 представляет собой пример первого составляющего транзистора, восьмой транзистор T8 представляет собой пример второго составляющего транзистора, и девятый транзистор T9 представляет собой пример третьего составляющего транзистора. В дальнейшем в этом документе, настоящее раскрытие сущности описывается посредством рассмотрения случая, в котором первый составляющий транзистор представляет собой пятый транзистор T5, второй составляющий транзистор представляет собой восьмой транзистор T8, и третий составляющий транзистор представляет собой девятый транзистор T9, в качестве примера, и варианты осуществления настоящего раскрытия сущности не ограничивают этот случай. Нижеприведенные варианты осуществления являются идентичными вариантам осуществления, описанным в данном документе, и не описываются снова.

[00112] Например, ортографическая проекция пятого транзистора T5 на базовой подложке 10 расположена между ортографической проекцией первой группы 150 сигнальных линий на базовой подложке 10 и ортографической проекцией первой линии VGH1 питания на базовой подложке и находится рядом с ортографической проекцией первой линии VGH1 питания на базовой подложке, ортографическая проекция восьмого транзистора T8 и ортографическая проекция девятого транзистора T9 на базовой подложке 10 расположены между ортографической проекцией первой линии VGH1 питания на базовой подложке 10 и ортографической проекцией второй линии VGH2 питания на базовой подложке 10 и находятся рядом с ортографической проекцией второй линии VGH2 питания на базовой подложке 10. Иными словами, первая линия VGH1 питания располагается в позиции рядом с пятым транзистором T5, и восьмой транзистор T8 и девятый транзистор T9 располагаются в позиции рядом с второй линией VGH2 питания таким образом, что обмотка, вызываемая посредством соединения пятого транзистора T5, восьмого транзистора T8 и девятого транзистора T9 с одной линией питания (например, с первой линией VGH1 питания), может исключаться, за счет этого исключая занятость пространства подложки отображения в вертикальном направлении вследствие обмотки.

[00113] Например, третья линия VGL1 питания и четвертая линия VGL2 питания выполнены с возможностью предоставлять одно и то же второе напряжение питания, например, низкое постоянное напряжение. Например, первое напряжение питания выше второго напряжения питания. Например, ортогональная проекция четвертой линии VGL2 питания на базовой подложке 10 частично перекрывается с ортографической проекцией первой возбуждающей схемы сканирования на базовой подложке 10, ортографическая проекция третьей линии VGL1 питания на базовой подложке 10 расположена между ортографической проекцией первой линии VGH1 питания на базовой подложке 10 и ортографической проекцией первой группы 150 сигнальных линий на базе 10 подложки.

[00114] Как описано выше, ортографическая проекция первой возбуждающей схемы сканирования на базовой подложке 10 не представляет собой непрерывную зону, и в силу этого ортографическая проекция четвертой линии VGL2 питания на базовой подложке 10 должна только частично перекрываться с ортографическими проекциями частей транзисторов или конденсаторов первой возбуждающей схемы сканирования на базовой подложке 10. Варианты осуществления настоящего раскрытия сущности не ограничены этим. Например, как показано на фиг. 5A, ортографическая проекция четвертой линии VGL2 питания на базовой подложке 10 перекрывается с межсоединениями первого проводящего слоя 320, например, ортографическая проекция четвертой линии VGL2 питания на базовой подложке 10 частично перекрывается с межсоединением, соединяющим электрод затвора восьмого транзистора T8, межсоединением, соединяющим электрод затвора десятого транзистора T10 и первый электрод CE12 второго конденсатора C2.

[00115] Например, каждый сдвиговый регистр первой возбуждающей схемы сканирования дополнительно содержит четвертый составляющий транзистор, соединенный с третьей линией VGL1 питания, и пятый составляющий транзистор, соединенный с четвертой линией VGL2 питания. Например, третий транзистор T3 представляет собой пример четвертого составляющего транзистора, и десятый транзистор T10 представляет собой пример пятого составляющего транзистора. В дальнейшем в этом документе, настоящее раскрытие сущности описывается посредством рассмотрения случая, в котором третий транзистор T3 представляет собой четвертый составляющий транзистор, и десятый транзистор T10 представляет собой пятый составляющий транзистор, в качестве примера, и варианты осуществления настоящего раскрытия сущности не ограничивают этот случай. Нижеприведенные варианты осуществления являются идентичными вариантам осуществления, описанным в данном документе, и не описываются снова.

[00116] Например, ортографическая проекция третьего транзистора T3 на базовой подложке 10 расположена на стороне, на удалении от ортографической проекции первой группы 150 сигнальных линий на базовой подложке 10, ортографической проекции третьей линии VGL1 питания на базовой подложке 10 и находится рядом с ортографической проекцией третьей линии VGL1 питания на базовой подложке 10. Например, ортографическая проекция десятого транзистора T10 на базовой подложке 10 расположена между ортографической проекцией четвертой линии VGL2 питания на базовой подложке 10 и ортографической проекцией второй группы 160 сигнальных линий на базовой подложке 10 и находится рядом с ортографической проекцией четвертой линии питания на базовой подложке 10. Иными словами, третья линия VGL1 питания располагается в позиции рядом с третьим транзистором T3, и десятый транзистор T10 располагается в позиции рядом с четвертой линией VGL2 питания таким образом, что обмотка, вызываемая посредством соединения третьего транзистора T3 и десятого транзистора T10 с одной линией питания (например, с третьей линией VGL1 питания) или, соответственно, с третьей линией VGL1 питания и четвертой линией VGL2 питания, расположенными на левой стороне подложки отображения, может исключаться, за счет этого исключая занятость пространства подложки отображения в вертикальном направлении вследствие обмотки.