Область техники, к которой относится изобретение

Настоящее раскрытие относится к области технологии отображения, в частности к подложке дисплея и устройству отображения.

Уровень техники

Дисплеи на основе органических светодиодов (OLED) широко применяются в различных областях благодаря таким преимуществам, как высокая яркость, низкое энергопотребление, высокое быстродействие, высокое разрешение, превосходная гибкость и высокая светоотдача.

Наряду с расширением применения изделий с OLED-дисплеями, имеется высокая потребность в качестве отображения OLED-дисплея, используемого в изделии. Существуют различные факторы, влияющие на качество отображения изделий с дисплеями, и, в качестве одного из важных факторов, все большее внимание уделяется перекрестным помехам, возникающим из-за пиксельной схемы в изделии с дисплеем.

Раскрытие сущности изобретения

Задача настоящего раскрытия состоит в том, чтобы выполнить подложку дисплея и устройство отображения.

В одном аспекте настоящее раскрытие предусматривает в некоторых вариантах осуществления подложку дисплея, включающую в себя базовую подложку и множество подпикселей, размещенных на базовой подложке в виде матрицы, причем подпиксель включает в себя: рисунок линии передачи данных, проходящий в первом направлении; первый экранирующий элемент, где по меньшей мере часть первого экранирующего элемента проходит в первом направлении; и возбуждающий транзистор, в котором первый транзистор соединен с электродом затвора возбуждающего транзистора, и второй экранирующий элемент соединен с первым экранирующим элементом. Первый транзистор имеет структуру с двумя затворами, причем первый транзистор включает в себя четвертый рисунок полупроводника, пятый рисунок полупроводника и шестой рисунок проводника, причем шестой рисунок проводника соединен с четвертым рисунком полупроводника и пятым рисунком полупроводника, и второй электрод возбуждающего транзистора соединен с четвертым рисунком полупроводника или пятым рисунком полупроводника; ортогональная проекция второго экранирующего элемента на базовую подложку по меньшей мере частично перекрывает ортогональную проекцию шестого рисунка проводника на базовую подложку; по меньшей мере часть первого экранирующего элемента расположена между вторым электродом возбуждающего транзистора и рисунком линии передачи данных смежного подпикселя.

При необходимости второй экранирующий элемент размещен ближе к базовой подложке, чем первый экранирующий элемент.

При необходимости площадь перекрытия между ортогональной проекцией первого экранирующего элемента на базовую подложку и ортогональной проекцией второго электрода возбуждающего транзистора на базовую подложку равна E1, участок ортогональной проекции второго электрода возбуждающего транзистора на базовую подложку не перекрывает ортогональную проекцию первого экранирующего элемента на базовую подложку, площадь участка ортогональной проекции второго электрода возбуждающего транзистора на базовую подложку, не перекрывающая ортогональную проекцию первого экранирующего элемента на базовую подложку, равна E2, и E1<E2.

При необходимости во втором направлении минимальное расстояние по прямой линии между ортогональной проекцией второго электрода возбуждающего транзистора на базовую подложку и ортогональной проекцией первого экранирующего элемента на базовую подложку равно L1, минимальное расстояние по прямой линии между ортогональной проекцией второго электрода возбуждающего транзистора на базовую подложку и ортогональной проекцией рисунка линии передачи данных смежного подпикселя на базовую подложку равно L2, и L1≤L2.

При необходимости длина канала возбуждающего транзистора равна L3, и L1≤L2≤L3.

При необходимости минимальное расстояние по прямой линии между вторым электродом возбуждающего транзистора и рисунком линии передачи данных смежного подпикселя равно L4, минимальное расстояние по прямой линии между вторым электродом возбуждающего транзистора и первым экранирующим элементом равно L5 и L5<L4.

При необходимости подпиксель дополнительно включает в себя соединительную линию, причем электрод затвора возбуждающего транзистора соединен со вторым электродом первого транзистора через соединительную линию; ортогональная проекция второго экранирующего элемента на базовую подложку расположена между ортогональной проекцией конца соединительной линии, соединенной со вторым электродом первого транзистора, на базовую подложку и ортогональной проекцией рисунка линии передачи данных смежного подпикселя на базовую подложку.

При необходимости длина первого экранирующего элемента в первом направлении больше, чем длина соединительной линии.

При необходимости длина участка второго электрода возбуждающего транзистора, не перекрывающего первый экранирующий элемент в первом направлении, равна L6, длина первого экранирующего элемента в первом направлении равна L7, и L6≤L7.

При необходимости предусмотрен зазор между ортогональной проекцией первого экранирующего элемента на базовую подложку и ортогональной проекцией второго электрода возбуждающего транзистора на базовую подложку.

При необходимости подпиксель дополнительно включает в себя четвертый транзистор, первый электрод четвертого транзистора соединен с рисунком линии передачи данных, и второй электрод четвертого транзистора соединен с первым электродом возбуждающего транзистора; ортогональная проекция второго экранирующего элемента на базовую подложку не перекрывает ортогональную проекцию четвертого транзистора смежного подпикселя на базовую подложку.

При необходимости первый экранирующий элемент и второй экранирующий элемент выполнены с возможностью приема первого сигнала с фиксированным потенциалом.

При необходимости подпиксель дополнительно включает в себя накопительный конденсатор, причем накопительный конденсатор включает в себя первую электродную пластину и вторую электродную пластину, первая электродная пластина соединена с электродом затвора возбуждающего транзистора, вторая электродная пластина выполнена с возможностью приема второго сигнала с фиксированным потенциалом; предусмотрен зазор между ортогональной проекцией второй электродной пластины на базовую подложку и ортогональной проекцией первого экранирующего элемента на базовую подложку; ортогональная проекция второго электрода возбуждающего транзистора на базовую подложку включает в себя участок внутри зазора.

При необходимости первый сигнал с фиксированным потенциалом совпадает со вторым сигналом с фиксированным потенциалом.

При необходимости второй электрод возбуждающего транзистора размещен ближе к базовой подложке, чем первый экранирующий элемент и второй экранирующий элемент.

При необходимости активный слой первого транзистора размещен в том же слое, что и активный слой возбуждающего транзистора, и сформирован как единое целое с ним.

При необходимости минимальное расстояние по прямой линии между первым экранирующим элементом и вторым электродом возбуждающего транзистора больше, чем минимальное расстояние по прямой линии между вторым экранирующим элементом и шестым рисунком проводника.

При необходимости подпиксель дополнительно включает в себя: рисунок сигнальной линии сброса и рисунок сигнальной линии инициализации, причем каждый из рисунка сигнальной линии сброса и рисунка сигнальной линии инициализации проходит во втором направлении, пересекающем первое направление; второй транзистор, причем электрод затвора второго транзистора соединен с рисунком сигнальной линии сброса, первый электрод второго транзистора соединен с рисунком сигнальной линии инициализации, и второй электрод второго транзистора соединен с электродом затвора

При необходимости ортогональная проекция контактного участка второго экранирующего элемента в контакте с первым экранирующим элементом на базовой подложке не перекрывает ортогональную проекцию активного слоя второго транзистора на базовую подложку; расстояние между контактным участком и шестым рисунком проводника меньше, чем расстояние между контактным участком и вторым электродом возбуждающего транзистора; расстояние между ортогональной проекцией контактного участка на базовую подложку и ортогональной проекцией шестого рисунка проводника на базовую подложку меньше, чем расстояние между ортогональной проекцией контактного участка на базовую подложку и ортогональной проекцией рисунка линии передачи данных на базовую подложку.

При необходимости подпиксель дополнительно включает в себя: рисунок сигнальной линии управления излучением света и рисунок сигнальной линии источника питания, причем рисунок сигнальной линии управления излучением света проходит во втором направлении, рисунок сигнальной линии источника питания включает в себя участок, проходящий в первом направлении; пятый транзистор, причем электрод затвора пятого транзистора соединен с рисунком сигнальной линии управления излучением света, первый электрод пятого транзистора соединен с рисунком сигнальной линии источника питания, и второй электрод пятого транзистора соединен с первым электродом возбуждающего транзистора.

При необходимости подпиксель дополнительно включает в себя светоизлучающий элемент и шестой транзистор, электрод затвора шестого транзистора соединен с рисунком сигнальной линии управления излучением света, первый электрод шестого транзистора соединен со вторым электродом возбуждающего транзистора, и второй электрод шестого транзистора соединен со светоизлучающим элементом.

В другом аспекте настоящее раскрытие предусматривает в некоторых вариантах осуществления подложку дисплея, включающую в себя базовую подложку и множество подпикселей, размещенных на базовой подложке в виде матрицы, причем подпиксель включает в себя: рисунок линии передачи данных, проходящий в первом направлении; первый экранирующий элемент, причем по меньшей мере часть первого экранирующего элемента проходит в первом направлении; и возбуждающий транзистор, причем первый транзистор соединен с электродом затвора возбуждающего транзистора, и второй экранирующий элемент, соединенный с первым экранирующим элементом. Первый транзистор имеет структуру с двумя затворами, причем первый транзистор включает в себя четвертый рисунок полупроводника, пятый рисунок полупроводника и шестой рисунок проводника, причем шестой рисунок проводника соединен с четвертым рисунком полупроводника и пятым рисунком полупроводника, а второй электрод возбуждающего транзистора соединен с четвертым рисунком полупроводника или пятым рисунком полупроводника; расстояние по прямой линии между контактным участком второго экранирующего элемента, контактирующим с первым экранирующим элементом, и шестым рисунком проводников меньше, чем расстояние по прямой линии между контактным участком и вторым электродом возбуждающего транзистора; и расстояние между ортогональной проекцией контактного участка второго экранирующего элемента, контактирующего с первым экранирующим элементом, на базовую подложку, и ортогональной проекцией шестого рисунка проводника на базовую подложку меньше, чем расстояние между ортогональной проекцией контактного участка на базовую подложку и ортогональной проекцией рисунка линии передачи данных на базовую подложку.

При необходимости второй экранирующий элемент размещен ближе к базовой подложке, чем первый экранирующий элемент.

При необходимости площадь перекрытия между ортогональной проекцией первого экранирующего элемента на базовую подложку и ортогональной проекцией второго электрода возбуждающего транзистора на базовую подложку равна E1, участок ортогональной проекции второго электрода возбуждающего транзистора на базовую подложку не перекрывает ортогональную проекцию первого экранирующего элемента на базовую подложку, площадь участка ортогональной проекции второго электрода возбуждающего транзистора на базовую подложку, не перекрывающая ортогональную проекцию первого экранирующего элемента на базовую подложку, равна E2, и E1<E2.

При необходимости во втором направлении минимальное расстояние по прямой линии между ортогональной проекцией второго электрода возбуждающего транзистора на базовую подложку и ортогональной проекцией первого экранирующего элемента на базовую подложку равно L1, минимальное расстояние по прямой линии между ортогональной проекцией второго электрода возбуждающего транзистора на базовую подложку и ортогональной проекцией рисунка линии передачи данных смежного подпикселя на базовую подложку равно L2, и L1≤L2.

При необходимости длина канала возбуждающего транзистора во втором направлении равна L3 и L1≤L2≤L3.

При необходимости минимальное расстояние по прямой линии между вторым электродом возбуждающего транзистора и рисунком линии передачи данных смежного подпикселя равно L4, минимальное расстояние по прямой линии между вторым электродом возбуждающего транзистора и первым экранирующим элементом равно L5, и L5<L4.

При необходимости подпиксель дополнительно включает в себя соединительную линию, причем электрод затвора возбуждающего транзистора соединен со вторым электродом первого транзистора через соединительную линию; ортогональная проекция второго экранирующего элемента на базовую подложку расположена между ортогональной проекцией конца соединительной линии, соединенной со вторым электродом первого транзистора, на базовую подложку и ортогональной проекцией рисунка линии передачи данных смежного подпикселя на базовую подложку.

При необходимости длина первого экранирующего элемента в первом направлении больше, чем длина соединительной линии.

При необходимости длина участка второго электрода возбуждающего транзистора, не перекрывающего первый экранирующий элемент в первом направлении, равна L6, длина первого экранирующего элемента в первом направлении равна L7, и L6≤L7.

При необходимости предусмотрен зазор между ортогональной проекцией первого экранирующего элемента на базовую подложку и ортогональной проекцией второго электрода возбуждающего транзистора на базовую подложку.

При необходимости подпиксель дополнительно включает в себя четвертый транзистор, причем первый электрод четвертого транзистора соединен с рисунком линии передачи данных, и второй электрод четвертого транзистора соединен с первым электродом возбуждающего транзистора; ортогональная проекция второго экранирующего элемента на базовую подложку не перекрывает ортогональную проекцию четвертого транзистора смежного подпикселя на базовую подложку.

При необходимости первый экранирующий элемент и второй экранирующий элемент выполнены с возможностью приема первого сигнала с фиксированным потенциалом.

При необходимости подпиксель дополнительно включает в себя накопительный конденсатор, причем накопительный конденсатор включает в себя первую электродную пластину и вторую электродную пластину, первая электродная пластина соединена с электродом затвора возбуждающего транзистора, вторая электродная пластина выполнена с возможностью приема второго сигнала с фиксированным потенциалом; предусмотрен зазор между ортогональной проекцией второй электродной пластины на базовую подложку и ортогональной проекцией первого экранирующего элемента на базовую подложку; ортогональная проекция второго электрода возбуждающего транзистора на базовую подложку включает в себя участок внутри зазора.

При необходимости первый сигнал с фиксированным потенциалом совпадает со вторым сигналом с фиксированным потенциалом.

При необходимости второй электрод возбуждающего транзистора размещен ближе к базовой подложке, чем первый экранирующий элемент и второй экранирующий элемент.

При необходимости активный слой первого транзистора размещен в том же слое, что и активный слой возбуждающего транзистора, и сформирован как единое целое с ним.

При необходимости минимальное расстояние по прямой линии между первым экранирующим элементом и вторым электродом возбуждающего транзистора больше, чем минимальное расстояние по прямой линии между вторым экранирующим элементом и шестым рисунком проводника.

При необходимости подпиксель дополнительно включает в себя: рисунок сигнальной линии сброса и рисунок сигнальной линии инициализации, причем каждый из рисунка сигнальной линии сброса и рисунка сигнальной линии инициализации проходит во втором направлении, пересекающем первое направление; второй транзистор, причем электрод затвора второго транзистора соединен с рисунком сигнальной линии сброса, первый электрод второго транзистора соединен с рисунком сигнальной линии инициализации, и второй электрод второго транзистора соединен с электродом затвора возбуждающего транзистора.

При необходимости ортогональная проекция контактного участка второго экранирующего элемента, контактирующего с первым экранирующим элементом, на базовую подложку не перекрывает ортогональную проекцию активного слоя второго транзистора на базовую подложку; минимальное расстояние по прямой линии между участком первого экранирующего элемента и вторым экранирующим элементом меньше минимального расстояния по прямой между рисунком линии передачи данных смежного подпикселя и вторым экранирующим элементом, и участок первого экранирующего элемента проходит в первом направлении.

При необходимости подпиксель дополнительно включает в себя: рисунок сигнальной линии управления излучением света и рисунок сигнальной линии источника питания, причем рисунок сигнальной линии управления излучением света проходит во втором направлении, при этом рисунок сигнальной линии источника питания включает в себя участок, проходящий в первом направлении; пятый транзистор, причем электрод затвора пятого транзистора соединен с рисунком сигнальной линии управления излучением света, первый электрод пятого транзистора соединен с рисунком сигнальной линии источника питания, и второй электрод пятого транзистора соединен с первым электродом возбуждающего транзистора.

При необходимости подпиксель дополнительно включает в себя светоизлучающий элемент и шестой транзистор, причем электрод затвора шестого транзистора соединен с рисунком сигнальной линии управления излучением света, первый электрод шестого транзистора соединен со вторым электродом возбуждающего транзистора, и второй электрод шестого транзистора соединен со светоизлучающим элементом.

В еще одном аспекте настоящее раскрытие предусматривает в некоторых вариантах осуществления устройство отображения, включающее в себя вышеупомянутую подложку дисплея.

Краткое описание чертежей

Следующие чертежи предоставлены для облегчения понимания настоящего раскрытия и составляют часть настоящего раскрытия. Примерные варианты осуществления и их пояснение предназначены только для иллюстративных целей и не должны рассматриваться как ограничение настоящего раскрытия. На чертежах:

фиг.1 – схематичный вид, показывающий схему возбуждения подпикселей согласно варианту осуществления настоящего раскрытия;

фиг.2 – временная диаграмма работы схемы возбуждения подпикселей согласно варианту осуществления настоящего раскрытия;

фиг.3 – схематичный вид, показывающий первую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.4 – схематичный вид, показывающий первую компоновку слоя активной пленки согласно варианту осуществления настоящего раскрытия;

фиг.5 – схематичный вид, показывающий первую компоновку первого металлического слоя затвора согласно варианту осуществления настоящего раскрытия;

фиг.6 – схематичный вид, показывающий первую компоновку второго металлического слоя затвора согласно варианту осуществления настоящего раскрытия;

фиг.7 – схематичный вид, показывающий первую компоновку металлического слоя истока/стока согласно варианту осуществления настоящего раскрытия;

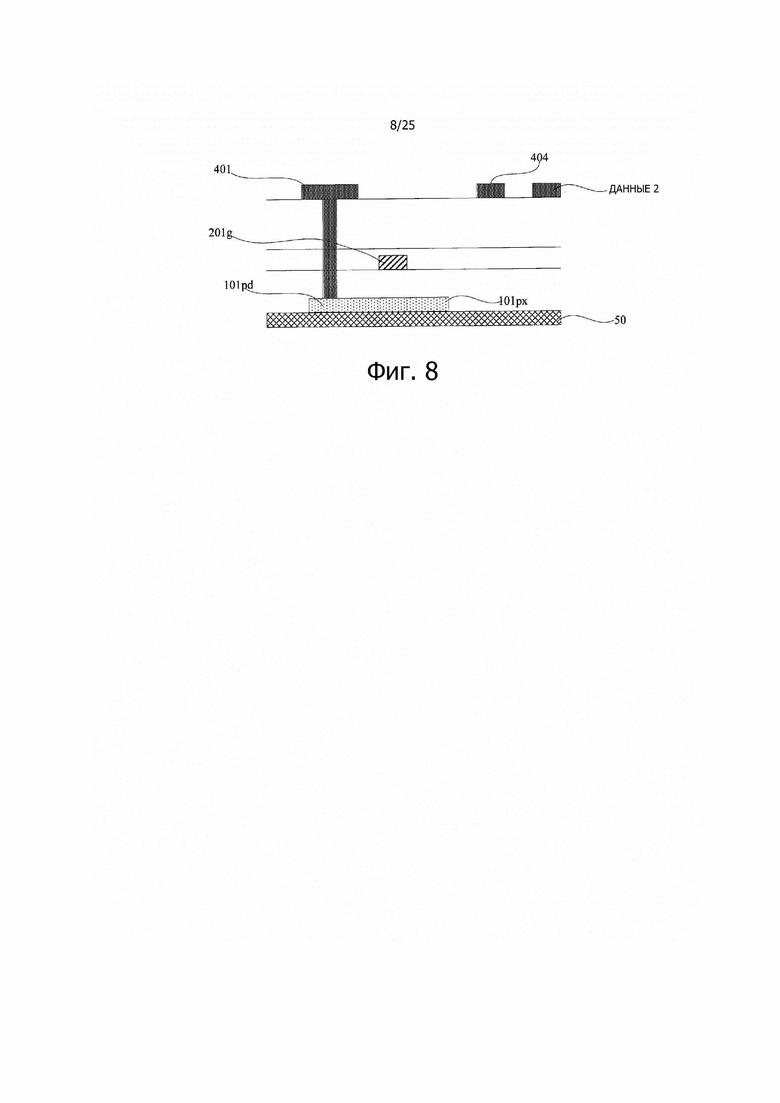

фиг.8 – вид в разрезе подложки дисплея по линии A1-A2 (фиг.3);

фиг.9 – схематичный вид, показывающий вторую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.10 – схематичный вид, показывающий третью компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.11 – схематичный вид, показывающий четвертую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.12 – схематичный вид, показывающий пятую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.13 – вид в разрезе по линии B1-B2 (фиг.11);

фиг.14 – схематичный вид, показывающий шестую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.15 – схематичный вид, показывающий первую компоновку множества подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

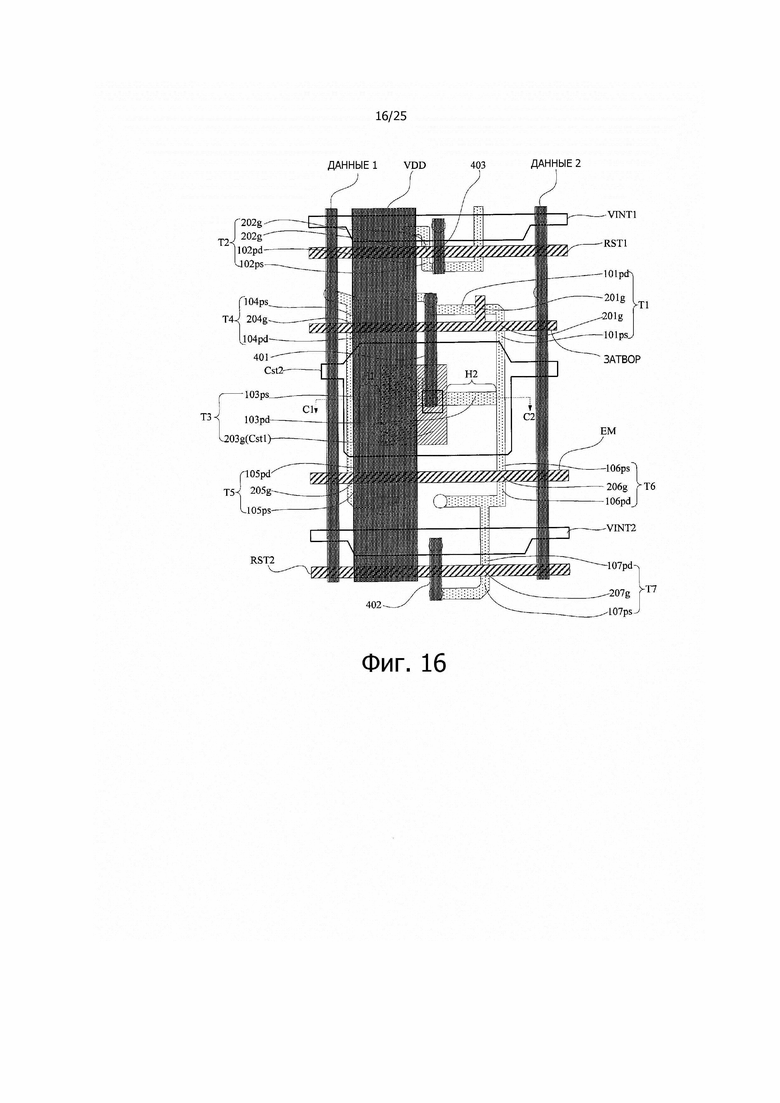

фиг.16 – схематичный вид, показывающий седьмую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.17 – вид в разрезе по линии C1-C2 (фиг.16);

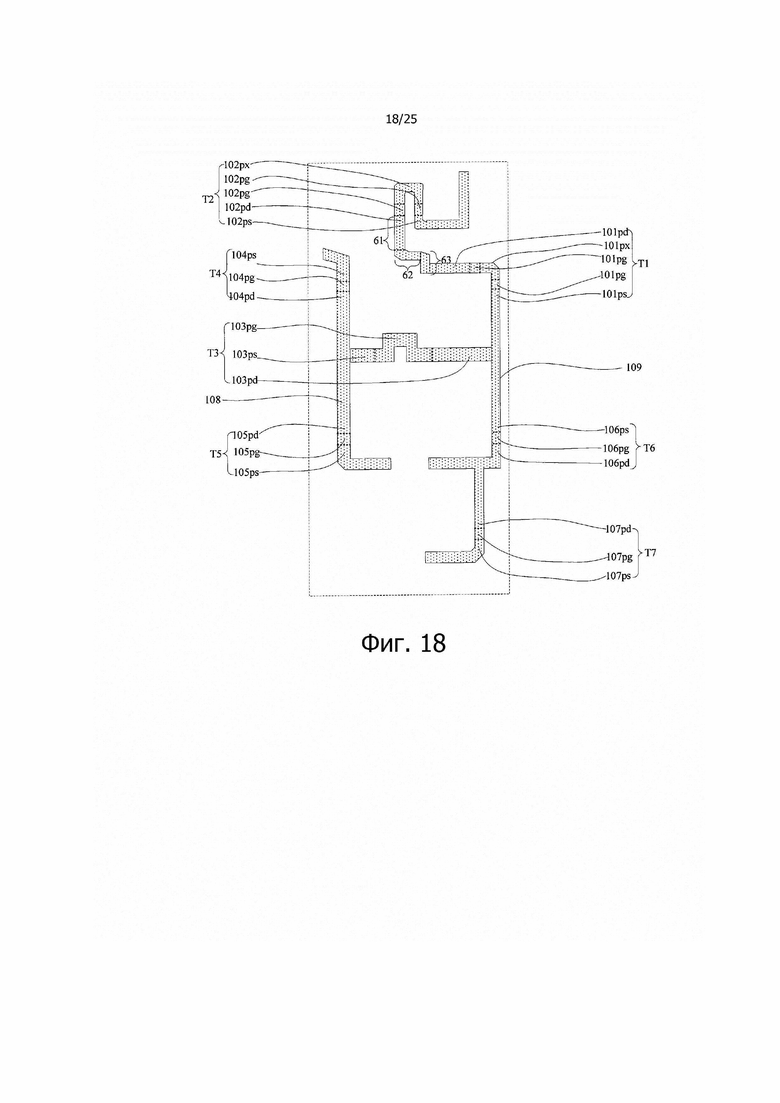

фиг.18 – схематичный вид, показывающий вторую компоновку слоя активной пленки согласно варианту осуществления настоящего раскрытия;

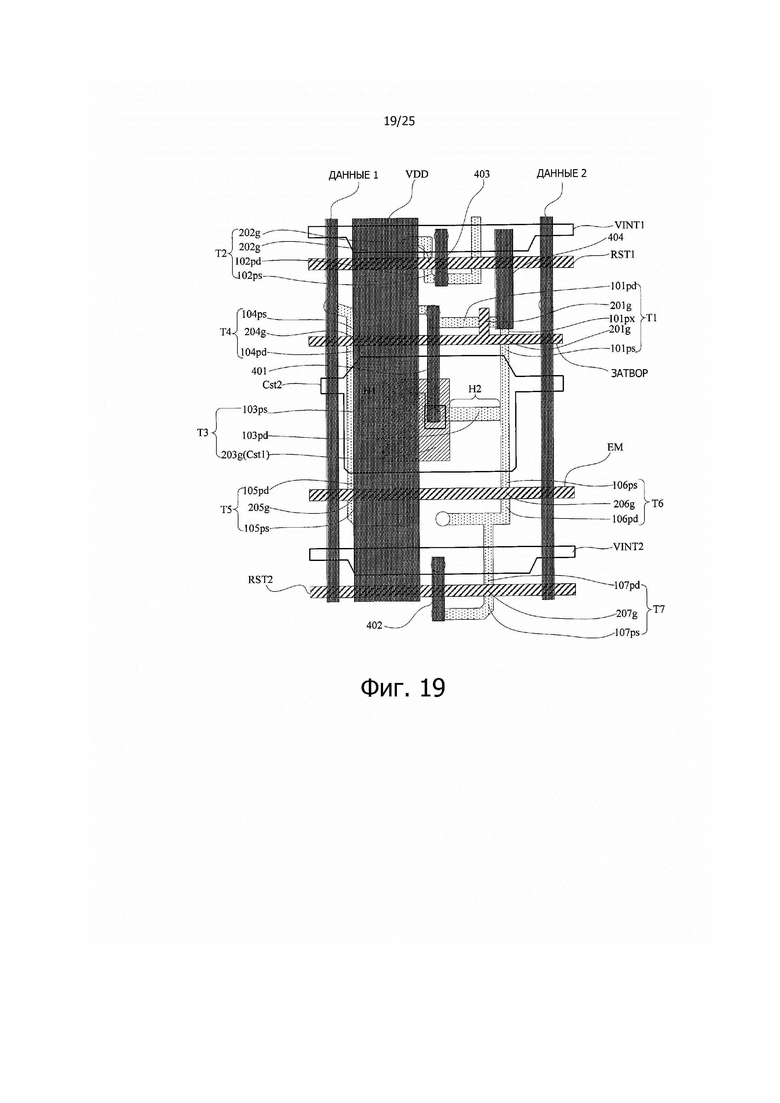

фиг.19 – схематичный вид, показывающий восьмую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.20 – схематичный вид, показывающий девятую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.21 – схематичный вид, показывающий десятую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.22 – вид в разрезе по линии D1-D2 (фиг.21);

фиг.23 – схематичный вид, показывающий расположение третьего металлического слоя;

фиг.24 – схематичный вид, показывающий вторую компоновку множества подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.25 – схематичный вид, показывающий явление взаимных перекрестных помех, возникающее на электроде затвора возбуждающего транзистора в предшествующем уровне техники;

фиг.26 – схематичный вид, показывающий одиннадцатую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.27 – схематичный вид, показывающий двенадцатую компоновку схемы возбуждения подпикселей в подложке дисплея согласно варианту осуществления настоящего раскрытия;

фиг.28 – вид в разрезе двух соседних схем возбуждения подпикселей по линии D1-D2 (фиг.21).

Осуществление изобретения

Для того, чтобы дополнительно объяснить подложку дисплея и устройство отображения, предусмотренные в вариантах осуществления настоящего раскрытия, настоящее раскрытие будет подробно описано ниже со ссылкой на чертежи.

В предшествующем уровне техники перекрестные помехи возникают в изделиях с OLED-дисплеями для различных ресурсов, и в основном перекрестные помехи возникают на возбуждающем транзисторе из-за рисунка линии передачи данных, окружающего возбуждающий транзистор в схеме возбуждения подпикселей. Более конкретно, во время размещения схемы возбуждения подпикселей различные транзисторы, имеющие другие функции, могут быть размещены вокруг возбуждающего транзистора в схеме возбуждения подпикселей, и каждый из этих транзисторов состоит из множества слоев проводящих рисунков. Кроме того, вокруг возбуждающего транзистора также размещены различные рисунки сигнальных линий для передачи разных сигналов. Во время работы схемы возбуждения подпикселей любое изменение сигналов на проводящих рисунках транзисторов и на рисунках сигнальных линий может легко привести к перекрестным помехам на возбуждающем транзисторе, и, таким образом, рабочие характеристики возбуждающего транзистора могут быть подвержены неблагоприятному влиянию.

В связи с вышеупомянутыми проблемами в результате проведенных исследований было обнаружено, что перекрестные помехи, которые влияют на рабочие характеристики возбуждающего транзистора, в основном включают в себя перекрестные помехи, возникающие из-за связи между рисунком линии передачи данных и электродом затвора возбуждающего транзистора, и перекрестные помехи, возникающие из-за связи между рисунком линии передачи данных и первым электродом возбуждающего транзистора.

Авторы изобретения настоящего раскрытия также обнаружили, что рисунок с фиксированным потенциалом может быть сформирован на первом электроде возбуждающего транзистора для того, чтобы экранировать рисунок с фиксированным потенциалом первого электрода возбуждающего транзистора и уменьшить эффект связи между рисунком линии передачи данных, расположенным в непосредственной близости от первого электрода возбуждающего транзистора, и первым электродом возбуждающего транзистора, тем самым уменьшая перекрестные помехи, создаваемые рисунком линии передачи данных для возбуждающего транзистора, и улучшая эффект отображения дисплея в изделии.

Следует отметить, что подложка дисплея, имеющая схему возбуждения подпикселей на основе 7T1C (то есть семь тонкопленочных транзисторов и один конденсатор), включена в один или несколько вариантов осуществления настоящего раскрытия. В другом варианте осуществления подложка дисплея может включать в себя другую схему возбуждения подпикселей, например, схему возбуждения подпикселей, содержащую более или менее семи тонкопленочных транзисторов и один или более конденсаторов.

Как показано на фиг.1, в некоторых вариантах осуществления настоящее раскрытие предусматривает подложку дисплея, которая включает в себя множество подпикселей. Каждый подпиксель может включать в себя рисунок GATE затворной линии, рисунок RST1 первой сигнальной линии сброса, рисунок VINT1 первой сигнальной линии инициализации, рисунок DATA линии передачи данных, рисунок EM сигнала управления излучением света, рисунок VDD сигнальной линии источника питания, рисунок RST2 второй сигнальной линии сброса и рисунок VINT2 второй сигнальной линии инициализации.

Схема возбуждения подпикселей каждого подпикселя может включать в себя первый транзистор T1, второй транзистор T2, третий транзистор T3, четвертый транзистор T4, пятый транзистор T5, шестой транзистор T6, седьмой транзистор T7 и накопительный конденсатор Cst. Кроме того, как показано на фиг.1, схема возбуждения подпикселей может дополнительно включать в себя первый конденсатор C1, который является паразитным конденсатором.

Выбирая одну схему возбуждения подпикселей в качестве примера, транзисторы схемы возбуждения подпикселей могут быть транзисторами P-типа. Первый транзистор T1 может иметь структуру с двумя затворами, электрод 201g затвора первого транзистора T1 может быть соединен с рисунком GATE затворной линии, электрод S1 истока первого транзистора T1 может быть соединен с электродом D3 стока третьего транзистора T3, и электрод D1 стока первого транзистора T1 может быть соединен с электродом 203g затвора третьего транзистора T3.

Второй транзистор T2 может иметь структуру с двумя затворами, электрод 202g затвора второго транзистора T2 может быть соединен с рисунком RST1 первой сигнальной линии сброса, электрод S2 истока второго транзистора T2 может быть соединен с рисунком VINT1 первой сигнальной линии инициализации, и электрод D2 стока второго транзистора T2 может быть соединен с электродом 203g затвора третьего транзистора T3.

Электрод 204g затвора четвертого транзистора T4 может быть соединен с рисунком GATE затворной линии, электрод S4 истока четвертого транзистора T4 может быть соединен с рисунком DATA линии передачи данных, и электрод D4 стока четвертого транзистора Т4 может быть соединен с электродом S3 истока третьего транзистора Т3.

Электрод 205g затвора пятого транзистора T5 может быть соединен с рисунком EM сигнальной линии управления излучением света, электрод S5 истока пятого транзистора T5 может быть соединен с рисунком VDD сигнальной линии источника питания, и электрод D5 стока пятого транзистора T5 может быть соединен с электродом S3 истока третьего транзистора T3.

Электрод 206g затвора шестого транзистора T6 может быть соединен с рисунком EM сигнальной линии управления излучением света, электрод S6 истока шестого транзистора T6 может быть соединен с электродом D3 стока третьего транзистора T3, и электрод D6 стока шестого транзистора T6 может быть соединен с анодом светоизлучающего элемента OLED.

Электрод 207g затвора седьмого транзистора T7 может быть соединен с рисунком RST2 второй сигнальной линии сброса, электрод D7 стока седьмого транзистора T7 может быть соединен с анодом светоизлучающего элемента OLED, и электрода S7 истока седьмого транзистора T7 может быть соединен с рисунком VINT2 второй сигнальной линии инициализации.

Первая электродная пластина Cst1 накопительного конденсатора Cst может быть соединена с электродом 203g затвора третьего транзистора T3, и вторая электродная пластина Cst2 накопительного конденсатора Cst может быть соединена с рисунком VDD сигнальной линии источника питания.

Как показано на фиг.2, во время работы схемы возбуждения подпикселей с вышеупомянутой структурой каждый рабочий период может включать в себя первую фазу P1 сброса, фазу P2 компенсации записи, вторую фазу P3 сброса и фазу P4 излучения света.

На первой фазе P1 сброса первый сигнал сброса, вводимый рисунком RST1 первой сигнальной линии сброса, может находиться на активном уровне для того, чтобы включить второй транзистор T2. Сигнал инициализации из рисунка VINT1 первой сигнальной линии инициализации может быть введен в электрод 203g затвора третьего транзистора T3, чтобы позволить напряжению Vgs затвор-исток, поддерживаемому на третьем транзисторе T3 в предыдущем кадре, быть равным нулю, тем самым обнуляя электрод 203g затвора третьего транзистора T3.

На фазе P2 компенсации записи первый сигнал сброса может находиться на неактивном уровне для того, чтобы выключить второй транзистор T2. Сигнал сканирования затвора, вводимый рисунком GATE затворной линии, может находиться на активном уровне для того, чтобы включать первый транзистор T1 и четвертый транзистор T4. Сигнал передачи данных может быть записан в рисунок линии передачи данных DATA и затем передан на электрод S3 истока третьего транзистора T3 через четвертый транзистор T4. Кроме того, когда первый транзистор T1 и четвертый транзистор T4 включены, третий транзистор T3 может иметь диодную структуру, поэтому первый транзистор T1, третий транзистор T3 и четвертый транзистор T4 могут взаимодействовать с целью компенсации порогового значения напряжение третьего транзистора Т3. Когда период времени компенсации достаточно велик, потенциал на электроде 203g затвора третьего транзистора T3 может в конечном итоге достичь Vdata + Vth, где Vdata – значение напряжения сигнала данных, и Vth – пороговое напряжение третьего транзистора T3.

На второй фазе P3 сброса сигнал сканирования затвора может находиться на неактивном уровне для того, чтобы выключить первый транзистор T1 и четвертый транзистор T4. Второй сигнал сброса, вводимый первой сигнальной линией RST2 сброса, может находиться на активном уровне для того, чтобы включить седьмой транзистор T7. Сигнал инициализации из рисунка VINT2 второй сигнальной линии инициализации может быть передан на анод светоизлучающего элемента OLED, чтобы управлять светоизлучающим элементом OLED таким образом, чтобы он не излучал свет.

На фазе P4 излучения света сигнал управления излучением света, записанный в структуру EM линий сигналов управления излучением света, может находиться на активном уровне для того, чтобы включить пятый транзистор T5 и шестой транзистор T6 и тем самым передать сигнал источника питания из рисунка VDD сигнальной линии источника питания на электрод S3 истока третьего транзистора T3. Кроме того, электрод 203g затвора третьего транзистора T3 поддерживается на уровне Vdata + Vth, поэтому третий транзистор T3 может быть включен, и напряжение затвор-исток третьего транзистора T3 может быть равным Vdata + Vth – VDD, где VDD – значение напряжения сигнала источника питания. Ток утечки, вырабатываемый в соответствии с напряжением затвор-исток, может протекать к аноду соответствующего светоизлучающего элемента OLED, чтобы заставить соответствующий светоизлучающий элемент OLED излучать свет.

Как показано на фиг.3, во время изготовления схемы возбуждения подпикселей компоновка пленочных слоев схемы возбуждения подпикселей будет описана следующим образом. Слой активной пленки, изолирующий слой затвора, первый металлический слой затвора, первый межслойный изолирующий слой, второй металлический слой затвора, второй межслойный изолирующий слой, первый металлический слой истока/стока и третий межслойный изолирующий слой могут быть размещены послойно друг над другом в указанном порядке в направлении от базовой подложки.

Как показано на фиг.4, слой активной пленки может использоваться для формирования области канала (например, 101pg-107pg), области формирования электрода истока (например, 101ps-107ps) и области формирования электрода стока (например, 101pd-107pd) каждого транзистора в схеме возбуждения подпикселей. Из-за эффекта легирования слои активной пленки, соответствующие области формирования электрода истока и области формирования электрода стока, могут иметь электропроводность выше, чем слой активной пленки, соответствующий области канала. Слой активной пленки может быть выполнен из аморфного кремния, поликремния или оксидного полупроводникового материала. Следует понимать, что каждая область формирования электрода истока и область формирования электрода стока может быть областью, легированной примесями n-типа или p-типа.

Кроме того, следует понимать, что слои активной пленки, соответствующие области формирования электрода истока и области формирования электрода стока, могут непосредственно служить в качестве соответствующего электрода истока и электрода стока; или электрод истока, контактирующий с областью формирования электрода истока, может быть выполнен из металлического материала, и электрод стока, контактирующий с областью формирования электрода стока, может быть выполнен из металлического материала.

Как показано на фиг.5, первый металлический слой затвора может использоваться для формирования электродов затвора (например, 201g-207g) транзисторов в схеме возбуждения подпикселей, а также рисунка GATE затворной линии, рисунка EM сигнальной линии управления излучением света, первого рисунка RST1 сигнальной линии сброса и рисунка RST2 второй сигнальной линии сброса подложки дисплея. Электрод 203g затвора третьего транзистора T3 в каждой схеме возбуждения подпикселей может быть повторно использован в схеме возбуждения подпикселей в качестве первой электродной пластины Cst1 накопительного конденсатора Cst.

Как показано на фиг.6, второй металлический слой затвора может использоваться для формирования второй электродной пластины Cst2 накопительного конденсатора Cst, а также рисунка VINT1 первой сигнальной линии инициализации и рисунка VINT2 второй сигнальной линии инициализации подложки дисплея.

Как показано на фиг.1, 3 и 7, первый металлический слой истока/стока может использоваться для формирования истоковых электродов (например, S1-S7) и стоковых электродов (например, D1-D7) транзисторов в схеме возбуждения подпикселей, а также рисунка линии передачи данных (например, DATA1 и DATA2) и рисунка VDD сигнальной линии источника питания подложки дисплея.

Более конкретно, снова обращаясь к фиг.3 и 7-10, электрод 201g затвора первого транзистора T1 может перекрывать область 101pg первого канала, электрод S1 истока первого транзистора T1 может быть расположен в первой области 101ps формирования электрода истока, и электрод D1 стока первого транзистора T1 может быть расположен в области 101pd формирования первого электрода стока.

Электрод 202g затвора второго транзистора T2 может перекрывать область 102pg второго канала, электрод S2 истока второго транзистора T2 может быть расположен во второй области 102ps формирования электрода истока, и электрод D2 стока второго транзистора T2 может быть расположен в области 102pd формирования второго электрода стока.

Электрод 203g затвора третьего транзистора T3 может перекрывать область 103pg третьего канала, электрод S3 истока третьего транзистора T3 может быть расположен в области 103ps формирования третьего электрода истока, и электрод D3 стока третьего транзистора T3 может быть расположен в области 103pd формирования третьего электрода стока.

Электрод 204g затвора четвертого транзистора T4 может перекрывать четвертую область 104pg канала, электрод S4 истока четвертого транзистора T4 может быть расположен в четвертой области 104ps формирования электрода истока, и электрод D4 стока четвертого транзистора T4 может быть расположен в области 104pd формирования четвертого электрода стока.

Электрод 205g затвора пятого транзистора T5 может перекрывать область 105pg пятого канала, электрод S5 истока пятого транзистора T5 может быть расположен в пятой области 105ps формирования электрода истока, и электрод D5 стока пятого транзистора T5 может быть расположен в области 105pd формирования пятого электрода стока.

Электрод 206g затвора шестого транзистора T6 может перекрывать область 106pg шестого канала, электрод S6 истока шестого транзистора T6 может быть расположен в области 106ps формирования шестого электрода истока, и электрод D6 стока шестого транзистора T6 может быть расположен в области 106pd формирования шестого электрода стока.

Электрод 207g затвора седьмого транзистора T7 может перекрывать седьмую область 106pg канала, электрод S7 истока седьмого транзистора T7 может быть расположен в седьмой области 107ps формирования электрода истока, и электрод D7 стока седьмого транзистора T7 может быть расположен в седьмой области 107pd формирования электрода стока.

Электрод 203g затвора третьего транзистора T3 может быть повторно использован в качестве первой электродной пластины Cst1 накопительного конденсатора Cst, и вторая электродная пластина Cst2 накопительного конденсатора Cst может быть соединена с рисунком VDD сигнальной линии источника питания.

Следует понимать, что соединительные линии 401, 402 и 403, показанные на фиг.1, могут быть сформированы первым металлическим слоем истока/стока, и их размещение показано на фиг.3 и 7. Первый конденсатор C1 на фиг.1 может быть паразитным конденсатором. Как показано на фиг.3, ортогональная проекция второй электродной пластины Cst2 накопительного конденсатора Cst на базовую подложку может перекрывать ортогональную проекцию участка соответствующей области 104pd формирования четвертого электрода стока, проходящего по направлению вниз к базовой подложке в области перекрытия, то есть которая сформирована в качестве первого конденсатора C1, и соответствующая область 104pd формирования четвертого электрода стока соответствует четвертому транзистору T4.

Кроме того, в подложке дисплея согласно вариантам осуществления настоящего раскрытия множество подпикселей может быть размещено в виде матрицы, то есть в множестве строк и столбцов. Каждая строка подпикселей может включать в себя множество подпикселей, размещенных во втором направлении, и каждый столбец подпикселей может включать в себя множество подпикселей, размещенных в первом направлении, пересекающем второе направление. Рисунок GATE затворной линии, рисунок RST1 первой сигнальной линии сброса, рисунок VINT1 первой сигнальной линии инициализации, рисунок EM сигнальной линии управления излучением света, каждый из рисунка RST2 второй сигнальной линии сброса и рисунка VINT2 второй сигнальной линии инициализации подпикселя может проходить во втором направлении, и каждый из рисунка DATA линии передачи данных и рисунка VDD сигнальной линии источника питания подпикселя может проходить в первом направлении.

Рисунки GATE затворной линии в одной и той же строке могут быть сформированы в виде одной затворной линии, рисунки RST1 первой сигнальной линии сброса в одной и той же строке могут быть сформированы как одно целое в виде одной первой сигнальной лини сброса, рисунки VINT1 первой сигнальной линии инициализации в одной и той же строке могут быть сформированы в виде одной первой сигнальной линии инициализации, рисунки EM сигнальной линии управления излучением света в одной и той же строке могут быть сформированы как единое целое в виде одной сигнальной линии управления излучением света, рисунки RST2 второй сигнальной линии сброса в одной и той же строке могут быть сформированы в виде одной второй сигнальной линии сброса, рисунки VINT2 второй сигнальной линии инициализации в одной и той же строке могут быть сформированы как единое целое в виде одной второй сигнальной линии инициализации, рисунки DATA линии передачи данных в одном том же столбце могут быть сформированы как единое целое в виде одной линии передачи данных, и рисунки VDD сигнальной линии источника питания в одном столбце могут быть сформированы как единое целое в виде одной сигнальной линии источника питания.

Чтобы упростить пространство компоновки подпикселей, вторая сигнальная линия сброса, соответствующая подпикселям в одной строке, может быть повторно использована в качестве первой сигнальной линии сброса, соответствующей подпикселям в следующей строке. Точно так же вторая сигнальная линия инициализации, соответствующая подпикселям в одной строке, может быть повторно использована в качестве первой сигнальной линии инициализации, соответствующей подпикселям в следующей строке.

Как показано на фиг.3, в некоторых вариантах осуществления, рассматривая в качестве примера схему возбуждения подпикселей в одном подпикселе, в первом направлении (например, направлении Y) электрод 204g затвора четвертого транзистора T4, электрод 201g затвора первого транзистора T1 и электрод 202g затвора второго транзистора T2 могут быть расположены на первой стороне электрода затвора возбуждающего транзистора (то есть электрода 203g затвора третьего транзистора T3), и электрод затвора седьмого транзистора T7, электрод 206g затвора шестого транзистора T6 и электрод затвора пятого транзистора T5 могут быть расположены на второй стороне электрода затвора возбуждающего транзистора. Например, первая сторона и вторая сторона электрода затвора возбуждающего транзистора могут быть двумя противоположными сторонами электрода затвора возбуждающего транзистора в первом направлении. Кроме того, первая сторона электрода затвора возбуждающего транзистора может быть верхней стороной электрода затвора возбуждающего транзистора, и вторая сторона электрода затвора возбуждающего транзистора может быть нижней стороной электрода затвора возбуждающего транзистора Т3. Например, нижняя сторона, то есть сторона подложки дисплея для соединения интегральной схемы (IC, ИС), может быть нижней стороной подложки дисплея, и сторона электрода затвора возбуждающего транзистора, ближняя к ИС, может быть нижней стороной электрода затвора возбуждающего транзистора. Верхняя сторона может быть стороной, противоположной нижней стороне, например, стороной электрода затвора возбуждающего транзистора, удаленной от ИС.

В некоторых вариантах осуществления настоящего раскрытия, как показано на фиг.3, во втором направлении (например, направлении X) электрод 204g затвора четвертого транзистора T4 и электрод 205g затвора пятого транзистора T5 могут быть расположены на третьей стороне электрода затвора возбуждающего транзистора, и электрод 201g затвора первого транзистора T1 и электрод 206g затвора шестого транзистора T6 могут быть расположены на четвертой стороне электрода затвора возбуждающего транзистора Т1. Например, третья сторона и четвертая сторона электрода затвора возбуждающего транзистора могут быть двумя противоположными сторонами электрода затвора возбуждающего транзистора во втором направлении X. Кроме того, третья сторона электрода затвора возбуждающего транзистора может быть левой стороной электрода затвора возбуждающего транзистора, и четвертая сторона электрода затвора возбуждающего транзистора может быть правой стороной электрода затвора возбуждающего транзистора. Например, относительно левой стороны и правой стороны в одном и том же подпикселе первый рисунок DATA1 линии передачи данных может быть расположен на левой стороне рисунка VDD сигнальной линии источника питания, и рисунок VDD сигнальной линии источника питания может быть расположен справа от первого рисунка DATA1 линии передачи данных.

Как показано на фиг.3 и 8, настоящее раскрытие предусматривает в некоторых вариантах осуществления подложку дисплея, которая включает в себя базовую подложку 50 и множество подпикселей, размещенных на базовой подложке 50 в виде матрицы. Подпиксель включает в себя: рисунок линии передачи данных (например, DATA1 на фиг.3), проходящий в первом направлении; рисунок сигнальной линии инициализации (например, VINT1 на фиг.3), включающий в себя участок, проходящий во втором направлении, пересекающем первое направление, и выполненный с возможностью передачи сигнала инициализации с фиксированным потенциалом; и схему возбуждения подпикселей. Схема возбуждения подпикселей включает в себя возбуждающий транзистор (например, T3 на фиг.3), первый транзистор T1, соединенный с электродом затвора возбуждающего транзистора, и первый экранирующий элемент 404, соединенный с рисунком сигнальной линии инициализации. Ортогональная проекция первого экранирующего элемента 404 на базовую подложку 50 может быть расположена между ортогональной проекцией первого транзистора T1 на базовую подложку 50 и ортогональной проекцией рисунка линии для целевой передачи данных (например, DATA2 на фиг.3) на базовую подложку 50. Следующий подпиксель, смежный с подпикселем во втором направлении, включает в себя рисунок линии для целевой передачи данных.

Более конкретно, как правило, подложка дисплея может включать в себя множество подпикселей, размещенных в виде матрицы, и каждый подпиксель может включать в себя рисунок линии передачи данных (например, DATA1 на фиг.3), проходящий в первом направлении, и рисунок сигнальной линии инициализации (например, VINT1 на фиг.3), по меньшей мере часть которого проходит во втором направлении. Рисунок линии передачи данных выполнен с возможностью передачи сигнала данных, и рисунок сигнальной линии инициализации выполнен с возможностью передачи сигнала инициализации с фиксированным потенциалом. Например, первое направление может включать в себя направление Y, и второе направление может включать в себя направление X.

Рисунок линии для целевой передачи данных может быть рисунком линии передачи данных следующего подпикселя, смежного с текущим подпикселем во втором направлении.

Каждый подпиксель может дополнительно включать в себя схемы возбуждения подпикселей и светоизлучающие элементы, соответствующие схемам возбуждения подпикселей, соответственно. Светоизлучающий элемент может включать в себя анод, слой органического светоизлучающего материала и катод, размещенные послойно друг над другом. Анод светоизлучающего элемента может быть соединен с соответствующей схемой возбуждения подпикселей, и светоизлучающий элемент может излучать свет под управлением возбуждающего сигнала, подаваемого из схемы возбуждения подпикселей.

Более конкретно, как показано на фиг.1, 3 и 4, когда схема возбуждения подпикселей включает в себя схему возбуждения подпикселей на основе 7T1C, электрод 203g затвора третьего транзистора T3 (то есть возбуждающий транзистор) может быть соединен с электродом D1 стока первого транзистора T1 через соединительную линию 401, и электрод D3 стока третьего транзистора T3 может быть соединен с электродом S1 истока первого транзистора T1. В направлении X минимальное расстояние по прямой линии между ортогональной проекцией области 101pg первого канала первого транзистора T1 на базовую подложку 50 и ортогональной проекцией рисунка линии для целевой передачи данных (например, DATA2 на фиг.3) на базовую подложку 50 может быть меньше минимального расстояния по прямой линии между ортогональной проекцией области 103pg третьего канала третьего транзистора T3 на базовую подложку 50 и ортогональной проекцией рисунка линии для целевой передачи данных на базовую подложку 50. Следует отметить, что минимальное расстояние по прямой линии между ортогональной проекцией области канала (например, первой области 101pg канала и третьей области 103pg канала) на базовую подложку 50 и ортогональной проекцией рисунка линии для целевой передачи данных (например, DATA2 на фиг.3) на базовую подложку 50 может относиться к минимальному расстоянию между краем ортогональной проекции области канала на базовую подложку 50, ближайшим к рисунку линии для целевой передачи данных, и ортогональной проекцией рисунка линии для целевой передачи данных (например, DATA2 на фиг.3) на базовую подложку 50.

В схеме возбуждения подпикселей с вышеупомянутой структурой при изменении сигнала передачи данных, передаваемого через рисунок линии для целевой передачи данных, могут ухудшиться рабочие характеристики первого транзистора T1. Так как первый транзистор T1 соединен с третьим транзистором T3 через соединительную линию 401, могут также ухудшиться рабочие характеристики третьего транзистора T3.

Согласно вариантам осуществления настоящего раскрытия схема возбуждения подпикселей снабжена первым экранирующим элементом 404, соединенным с рисунком сигнальной линии инициализации (например, VINT1 на фиг.3) для того, чтобы первый экранирующий элемент 404 имел такой же фиксированный потенциал, как у сигнала инициализации. Кроме того, ортогональная проекция первого экранирующего элемента 404 на базовую подложку 50 может быть расположена между ортогональной проекцией первого транзистора T1 на базовую подложку 50 и ортогональной проекцией рисунка линии для целевой передачи данных (например, DATA2 на фиг.3) на базовую подложку 50, так что можно уменьшить влияние, оказываемое через первый экранирующий элемент 404 и вызванное изменением сигнала, передаваемого через рисунок линии для целевой передачи данных, на рабочие характеристики первого транзистора T1, тем самым уменьшая влияние связи между электродом затвора (то есть, 203g) возбуждающего транзистора и рисунком линии для целевой передачи данных, уменьшая вертикальные перекрестные помехи и улучшая эффект отображения подложки дисплея во время отображения.

Кроме того, когда первый экранирующий элемент 404 соединен с рисунком сигнальной линии инициализации, можно, помимо обеспечения первого экранирующего элемента 404 с фиксированным потенциалом, увеличить напряжение на рисунке сигнальной линии инициализации и обеспечить более стабильное напряжение для сигнала инициализации, передаваемого в рисунке сигнальной линии инициализации, тем самым улучшая рабочие характеристики схемы возбуждения подпикселей.

Следует понимать, что, помимо соединения с рисунком сигнальной линии инициализации, первый экранирующий элемент 404 может быть также соединен с рисунком VDD сигнальной линии источника питания подпикселя для того, чтобы первый экранирующий элемент 404 имел такой же фиксированный потенциал, как у сигнала источника питания, передаваемого через рисунок VDD сигнальной линии источника питания.

Как показано на фиг.27, минимальное расстояние по прямой линии между ортогональной проекцией второго электрода возбуждающего транзистора (то есть электродом D3 стока третьего транзистора T3) на базовую подложку и ортогональной проекцией первого экранирующего элемента 404 на базовую подложку может быть равно L1, минимальное расстояние по прямой линии между ортогональной проекцией второго электрода возбуждающего транзистора на базовую подложку и ортогональной проекцией рисунка DATA2 линии передачи данных смежного подпикселя на базовую подложку может быть равно L2.

Длина канала (то есть области 103pg третьего канала) возбуждающего транзистора во втором направлении может быть равна L3, и L1≤L2≤L3.

Как показано на фиг.28, минимальное расстояние по прямой линии между вторым электродом возбуждающего транзистора и рисунком линии передачи данных (например, DATA2) смежного подпикселя может быть равно L4, минимальное расстояние по прямой линии между вторым электродом возбуждающего транзистора и первым экранирующим элементом может быть равно L5, и L5<L4.

Как показано на фиг.27, длина участка второго электрода возбуждающего транзистора, не перекрывающего первый экранирующий элемент 404 в первом направлении, может быть равна L6, длина первого экранирующего элемента 404 в первом направлении может быть равна L7, и L6≤L7.

Как показано на фиг.27, активный слой первого транзистора T1 может быть размещен в том же слое, что и активный слой возбуждающего транзистора (то есть третьего транзистора T3), поэтому активные слои могут быть сформированы с помощью единого процесса формирования рисунка.

Второй электрод возбуждающего транзистора может быть размещен в том же слое, что и шестой рисунок проводника, и сформирован как единое целое с ним, и второй экранирующий элемент 301 может быть размещен между активным слоем первого транзистора T1 и первым экранирующим элементом 404, поэтому минимальное расстояние по прямой линии между первым экранирующим элементом 404 и вторым электродом возбуждающего транзистора может быть больше, чем минимальное расстояние по прямой линии между вторым экранирующим элементом 301 и шестым рисунком проводников.

Первый экранирующий элемент 404 может быть размещен в том же слое, что и рисунок линии передачи данных (например, DATA2) смежного подпикселя, поэтому они могут быть сформированы с помощью единого процесса формирования рисунка. Минимальное расстояние по прямой линии между участком первого экранирующего элемента 404, проходящим в первом направлении, и вторым экранирующим элементом 301 может быть меньше минимального расстояния по прямой линии между рисунком линии передачи данных смежного подпикселя и вторым экранирующим элементом 301.

Когда первый экранирующий элемент 404 соединен с рисунком VDD сигнальной линии источника питания, и при этом поддерживается фиксированный потенциал первого экранирующего элемента 404, значение паразитной емкости, создаваемой рисунком VDD сигнальной линии источника питания, может увеличиваться. В это время RC-нагрузка рисунка VDD сигнальной линии источника питания может увеличиваться и, таким образом, препятствовать уменьшению вертикальных перекрестных помех.

Как показано на фиг.3, в некоторых вариантах осуществления настоящего раскрытия электрод 201g затвора первого транзистора T1 может быть сформирован как единое целое с рисунком GATE затворной линии, и электрод 201g затвора первого транзистора T1 может представлять собой участок результирующей интегральной структуры, способной образовывать область, перекрывающуюся со слоем активной пленки в направлении, перпендикулярном базовой подложке.

Как показано на фиг.3, в некоторых вариантах осуществления настоящего раскрытия множество подпикселей может быть размещено в множестве строк, и каждая строка подпикселей может включать в себя множество подпикселей, размещенных во втором направлении. Рисунки сигнальных линий инициализации подпикселей в одной строке могут быть последовательно соединены друг с другом для формирования сигнальной линии инициализации, соответствующей подпикселям в строке. Первый экранирующий элемент 404 может проходить в первом направлении и может быть соединен по меньшей мере с одной сигнальной линией инициализации.

Более конкретно, множество подпикселей может быть размещено в строках и столбцах, при этом каждая строка подпикселей может включать в себя множество подпикселей, размещенных во втором направлении, и каждый столбец подпикселей может включать в себя множество подпикселей, размещенных в первом направлении, пересекающем второе направление. Рисунки сигнальных линий инициализации подпикселей в одной строке могут быть последовательно соединены друг с другом для формирования сигнальной линии инициализации, соответствующей подпикселям в строке.

В случае, когда первый экранирующий элемент 404 проходит в первом направлении и подсоединен по меньшей мере к одной сигнальной линии инициализации, первый экранирующий элемент 404 позволяет уменьшить неблагоприятное влияние на рабочие характеристики первого транзистора T1 за счет изменения сигнала, передаваемого через рисунок линии для целевой передачи данных, тем самым уменьшая эффект связи между электродом затвора (то есть 203g) возбуждающего транзистора и рисунком линии для целевой передачи данных, уменьшая вертикальные перекрестные помехи и улучшая эффект отображения подложки дисплея во время отображения. Кроме того, можно увеличить напряжение на сигнальной линии инициализации и обеспечить более стабильное напряжение для сигнала инициализации, передаваемого через сигнальную линию инициализации, тем самым улучшая рабочие характеристики схемы возбуждения подпикселей.

Как показано на фиг.9, в некоторых вариантах осуществления настоящего раскрытия первый экранирующий элемент 404 может быть подключен к двум смежным сигнальным линиям инициализации.

Более конкретно, когда первый экранирующий элемент 404 подсоединен к сигнальным линиям инициализации, первый экранирующий элемент 404 может быть подсоединен к сигнальным линиям инициализации различными способами, и первый экранирующий элемент 404 может иметь различные структуры и размещаться различными способами. Например, как показано на фиг.3, первый экранирующий элемент 404 может быть подсоединен к двум смежным с ним сигнальным линиям инициализации. В этом способе размещения ортогональная проекция первого экранирующего элемента 404 на базовую подложку 50 может быть размещена не только между ортогональной проекцией первого транзистора T1 на базовую подложку 50 и ортогональной проекцией рисунка линии для целевой передачи данных на базовую подложку 50, но также между ортогональной проекцией соединительной линии 401 на базовую подложку 50 и ортогональной проекцией рисунка линии для целевой передачи данных на базовую подложку 50, а также между ортогональной проекцией возбуждающего транзистора (то есть третьего транзистора T3) на базовую подложку 50 и ортогональной проекцией рисунка линии для целевой передачи данных на базовую подложку 50.

Используя вышеупомянутый способ размещения, можно более эффективным образом уменьшить первые перекрестные помехи, возникающие между рисунком целевой сигнальной линии и первым транзистором T1, и вторые перекрестные помехи, возникающие между рисунком целевой сигнальной линии и соединительной линией 401, тем самым уменьшая непрямые перекрестные помехи на возбуждающем транзисторе, вызванные первыми и вторыми перекрестными помехами. Кроме того, с помощью вышеупомянутого способа размещения можно дополнительно уменьшить прямые перекрестные помехи между рисунком целевой сигнальной линии и возбуждающим транзистором, тем самым обеспечивая рабочие характеристики подложки дисплея более эффективным образом.

Снова обращаясь к фиг.3, в некоторых вариантах осуществления настоящего раскрытия первый экранирующий рисунок 404 может быть размещен в слое, отличном от рисунка сигнальной линии инициализации (например, VINT1 на фиг.3), и ортогональная проекция первого экранирующего элемента 404 на базовую подложку 50 может перекрывать ортогональную проекцию рисунка сигнальной линии инициализации на базовую подложку в первой области перекрытия, при этом первый экранирующий элемент 404 соединен с рисунком сигнальной линии инициализации через первое сквозное отверстие, размещенное в первой области перекрытия.

Более конкретно, первый экранирующий элемент 404 может быть размещен в том же слое, что и рисунок сигнальной линии инициализации, или в слое, отличном от него. Когда первый экранирующий элемент 404 размещен в слое, отличном от рисунка сигнальной линии инициализации, ортогональная проекция первого экранирующего элемента 404 на базовую подложку 50 может перекрывать ортогональную проекцию рисунка сигнальной линии инициализации на базовую подложку 50 в первой области перекрытия. Таким образом, первый экранирующий элемент 404 может быть соединен с сигнальной линией инициализации через первое сквозное отверстие в первой области перекрытия.

Следует понимать, что, когда первый экранирующий элемент 404 размещен в том же слое, что и рисунок сигнальной линии инициализации, может существовать по меньшей мере одно из следующих условий: первый экранирующий элемент 404 и рисунок сигнальной линии инициализации расположены в одной горизонтальной плоскости, первый экранирующий элемент 404 и рисунок сигнальной линии инициализации расположены в одном слое пленки, первый экранирующий элемент 404 и рисунок сигнальной линии инициализации расположены на поверхности одного и того же изоляционного слоя, удаленного от базовой подложки, первый экранирующий элемент 404 и рисунок сигнальной линии инициализации формируются с помощью единого процесса формирования рисунка.

Когда первый экранирующий элемент 404 размещен в слое, отличном от рисунка сигнальной линии инициализации, может существовать по меньшей мере одно из следующих условий: первый экранирующий элемент 404 и рисунок сигнальной линии инициализации не расположены на одном и том же слое пленки, и первый экранирующий элемент 404, и рисунок сигнальной линии инициализации не могут быть сформированы с помощью единого процесса формирования рисунка.

В некоторых вариантах осуществления настоящего раскрытия первый экранирующий элемент 404 может быть выполнен из того же материала, что и рисунок линии передачи данных (например, DATA1 на фиг.3).

В некоторых вариантах осуществления настоящего раскрытия подложка дисплея может включать в себя первый межслойный изоляционный слой, и первый экранирующий элемент 404 и рисунок линии передачи данных (например, DATA1 на фиг.3) могут быть размещены на поверхности первого межслойного изоляционного слоя, удаленного от базовой подложки.

Более конкретно, когда первый экранирующий элемент 404 размещен таким образом, как упомянуто выше, можно одновременно сформировать первый экранирующий элемент 404 и рисунок линии передачи данных с помощью единого процесса формирования рисунка на поверхности первого межслойного изоляционного слоя, удаленного от базовой подложки и исключить дополнительный процесс формирования рисунка для формирования первого экранирующего элемента 404, тем самым упрощая процесс изготовления подложки дисплея более эффективным образом и снижая стоимость изготовления.

Как показано на фиг.3, в некоторых вариантах осуществления настоящего раскрытия схема возбуждения подпикселей может дополнительно включать в себя второй транзистор T2, соединенный с электродом затвора возбуждающего транзистора. Второй транзистор T2 может включать в себя: первый рисунок полупроводника, второй рисунок полупроводника и третий рисунок полупроводника, соединенный с первым рисунком полупроводника и вторым рисунком полупроводника, причем электропроводность третьего рисунка проводника превышает электропроводность первого рисунка полупроводника и электропроводность второго рисунка полупроводника; и рисунок первого электрода затвора и рисунок второго электрода затвора, соединенные друг с другом, при этом ортогональная проекция рисунка первого электрода затвора на базовую подложку 50 частично перекрывает ортогональную проекцию первого рисунка полупроводника на базовую подложку 50, и ортогональная проекция рисунка второго электрода затвора на базовую подложку 50 частично перекрывает ортогональную проекцию второго рисунка полупроводника на базовую подложку 50. Ортогональная проекция рисунка третьего электрода затвора на базовую подложку 50 может не перекрывать ортогональную проекцию рисунка первого электрода затвора на базовую подложку 50 и ортогональную проекцию рисунка второго электрода затвора на базовую подложку 50. Ортогональная проекция третьего рисунка проводника на базовую подложку 50 может по меньшей мере частично перекрывать ортогональную проекцию рисунка сигнальной линии инициализации (например, VINT1 на фиг.3) на базовую подложку 50.

Более конкретно, как показано на фиг.7, второй транзистор T2 может иметь структуру с двумя затворами. Первый рисунок полупроводника и второй рисунок полупроводника второго транзистора могут образовывать область канала (соответствующую положению знака 102pg на фиг.7) второго транзистора T2, и третий рисунок 102px проводника второго транзистора может иметь электропроводность выше, чем у первого рисунка полупроводника и второго рисунка полупроводника из-за легирования третьего рисунка 102px проводника. Первый рисунок электродов затвора и второй рисунок электродов затвора второго транзистора T2 могут перекрывать первый рисунок полупроводника и второй рисунок полупроводника, соответственно, и вместе служить электродом 202g затвора второго транзистора T2.

Во втором транзисторе T2 с вышеупомянутой структурой, так как третий рисунок 102px проводника имеет превосходную электропроводность и не перекрывается рисунком электродов затвора, может легко появляться связь с другими соседними проводящими рисунками, и, таким образом, могут возникать перекрестные помехи. Согласно вариантам осуществления настоящего раскрытия, когда ортогональная проекция третьего рисунка проводника на базовую подложку 50 по меньшей мере частично перекрывает ортогональную проекцию рисунка сигнальной линии инициализации (например, VINT1 на фиг.3) на базовую подложку 50, рисунок сигнальной линии инициализации может экранировать третий рисунок 102px проводника. Так как сигнал инициализации с фиксированным потенциалом передается через рисунок сигнальной линии инициализации, это позволяет более эффективным образом уменьшить влияние связи между третьим рисунком 102px проводника и другими соседними проводящими рисунками, тем самым обеспечивая более стабильные рабочие характеристики подложки дисплея.

Как показано на фиг.4, в некоторых вариантах осуществления настоящего раскрытия схема возбуждения подпикселей может дополнительно включать в себя первый ответвляющийся элемент, отходящий от первого рисунка полупроводника и имеющий электропроводность выше, чем у первого рисунка полупроводника. Первый ответвляющийся элемент может включать в себя первый участок 61, второй участок 62 и третий участок 63. Каждый из первого участка 61 и третьего участка 63 могут проходить в первом направлении, и второй участок 62 может проходить во втором направлении. Конец второго участка 62 может быть соединен с первым участком 61, другой конец второго участка 62 может быть соединен с третьим участком 63, и конец третьего участка 63, удаленный от второго участка 62, может быть подсоединен к первому транзистору Т1.

Более конкретно, первый ответвляющийся элемент и первый рисунок полупроводника могут быть сформированы с помощью единого процесса формирования рисунка, и после формирования первого рисунка полупроводника первый ответвляющийся элемент может быть легирован таким образом, чтобы электропроводность первого ответвляющегося элемента была выше, чем у первого рисунка полупроводника.

После добавления первого экранирующего элемента 404 через первый ответвляющийся элемент с вышеупомянутой структурой можно дополнительно уменьшить влияние на рабочие характеристики первого транзистора T1 и рабочие характеристики второго транзистора T2, вызванное изменением сигнала, передаваемого через рисунок линии для целевой передачи данных, когда второй транзистор T2 соединен с первым транзистором T1 и электродом затвора возбуждающего транзистора через первый ответвляющийся элемент, тем самым уменьшая эффект связи между затвором электрода (то есть 203g) возбуждающего транзистора и рисунком линии для целевой передачи данных, уменьшая вертикальные перекрестные помехи и улучшая эффект отображения подложки дисплея во время отображения.

Как показано на фиг.3 и 4, в некоторых вариантах осуществления настоящего раскрытия первый транзистор T1 может включать в себя: четвертый рисунок полупроводника, пятый рисунок полупроводника и шестой рисунок проводника, соединенный с четвертым рисунком полупроводника и пятым рисунком полупроводника, причем электропроводность шестого рисунка проводника превышает электропроводность четвертого рисунка полупроводника и электропроводность пятого рисунка полупроводника; и третий рисунок электрода затвора и четвертый рисунок электрода затвора, соединенные друг с другом. Ортогональная проекция рисунка третьего электрода затвора на базовую подложку 50 может частично перекрывать ортогональную проекцию четвертого рисунка полупроводника на базовую подложку 50, ортогональная проекция рисунка четвертого электрода затвора на базовую подложку 50 может частично перекрывать ортогональную проекцию пятого рисунка электрода затвора на базовую подложку 50, и ортогональная проекция шестого рисунка проводника на базовую подложку 50 может не перекрывать ортогональную проекцию рисунка третьего электрода затвора на базовую подложку 50 и ортогональную проекцию рисунка четвертого электрода затвора на базовую подложку 50.

Более конкретно, как показано на фиг.4, первый транзистор может иметь структуру с двумя затворами. Четвертый рисунок полупроводника и пятый рисунок полупроводника первого транзистора могут образовывать область канала (соответствующую знаку 101pg на фиг.4) первого транзистора, и шестой рисунок 101px проводника первого транзистора может иметь электропроводность выше, чем у четвертого рисунка полупроводника и пятого рисунка полупроводника из-за легирования шестого рисунка 101px проводника. Третий рисунок электрода и четвертый рисунок электрода затвора первого транзистора могут перекрывать четвертый рисунок полупроводника и пятый рисунок полупроводника, соответственно, и вместе служить электродом 201g затвора первого транзистора T1.

Как показано на фиг.10, в некоторых вариантах осуществления настоящего раскрытия ортогональная проекция первого экранирующего элемента 404 на базовую подложку 50 может по меньшей мере частично перекрывать ортогональную проекцию шестого рисунка 101px проводника на базовую подложку 50.

Более конкретно, в первом транзисторе T1 с вышеупомянутой структурой, так как шестой рисунок 101px проводника имеет превосходную электропроводность и не перекрывается рисунком электрода затвора, может легко появляться связь с другими соседними проводящими рисунками, и вследствие этого могут возникать перекрестные помехи. Согласно вариантам осуществления настоящего раскрытия, когда ортогональная проекция первого экранирующего элемента 404 на базовую подложку 50 по меньшей мере частично перекрывает ортогональную проекцию шестого рисунка 101px проводника на базовую подложку 50, первый экранирующий элемент 404 может экранировать шестой рисунок 101px проводника. Кроме того, так как первый экранирующий элемент 404 имеет фиксированный потенциал, это позволяет более эффективным образом уменьшить влияние связи между шестым рисунком 101px проводника и другими проводящими рисунками, смежными с шестым рисунком 101px проводника, тем самым обеспечивая более стабильные рабочие характеристики подложки дисплея.

Как показано на фиг.11, 12 и 13, в некоторых вариантах осуществления настоящего раскрытия схема возбуждения подпикселей может дополнительно включать в себя второй экранирующий элемент 301, соединенный с первым экранирующим элементом 404, и ортогональная проекция второго экранирующего элемента 301 на базовую подложку 50 может по меньшей мере частично перекрывать ортогональную проекцию шестого рисунка 101px проводника на базовую подложку 50.

Более конкретно, когда ортогональная проекция второго экранирующего элемента 301 на базовую подложку 50 по меньшей мере частично перекрывает ортогональную проекцию шестого рисунка 101px проводника на базовую подложку 50, второй экранирующий элемент 301 может экранировать шестой рисунок 101px проводника. Кроме того, так как второй экранирующий элемент 301 соединен с первым экранирующим элементом 404, второй экранирующий элемент 301 может иметь фиксированный потенциал, поэтому он позволяет уменьшить влияние связи между шестым рисунком 101px проводника и другим проводящим рисунком, смежным с шестым рисунком 101px проводника, более эффективным образом, тем самым обеспечивая более стабильные рабочие характеристики подложки дисплея.

В подложке дисплея согласно вариантам осуществления настоящего раскрытия, так как каждый из первого экранирующего элемента 404 и второго экранирующего элемента 303 имеет фиксированный потенциал, можно предотвратить или уменьшить паразитную емкость между первым транзистором T1 и рисунком линии для целевой передачи данных (например, DATA2) более эффективным образом для того, чтобы эффективным образом предотвращать или уменьшать вертикальные перекрестные помехи.

Кроме того, ортогональная проекция второго экранирующего элемента 301 на базовую подложку 50 может перекрывать всю ортогональную проекцию шестого рисунка проводника на базовую подложку 50.

Более конкретно, когда ортогональная проекция второго экранирующего элемента 301 на базовую подложку 50 перекрывает всю ортогональную проекцию шестого рисунка 101px проводника на базовую подложку 50, второй экранирующий рисунок 301 может полностью экранировать шестой рисунок 101px проводника, так что можно в наибольшей степени уменьшить влияние связи между шестым рисунком 101px проводника и другими проводящими рисунками, смежными с шестым рисунком 101px проводника, тем самым повышая стабильность работы подложки дисплея более эффективным образом.

В некоторых вариантах осуществления настоящего раскрытия второй экранирующий элемент 301 и первый экранирующий элемент 404 могут быть размещены в разных слоях, и ортогональная проекция второго экранирующего элемента 301 на базовую подложку 50 может перекрывать ортогональную проекцию первого экранирующего элемента 404 на базовую подложку 50 во второй области перекрытия, при этом второй экранирующий элемент 301 соединен с первым экранирующим элементом 404 через второе сквозное отверстие, размещенное во второй области перекрытия.

Более конкретно, второй экранирующий элемент 301 может быть размещен в том же слое, что и первый экранирующий элемент 404, или в слое, отличном от него. Когда второй экранирующий элемент 301 размещен в слое, отличном от первого экранирующего элемента 404, ортогональная проекция второго экранирующего элемента 301 на базовую подложку 50 может перекрывать ортогональную проекцию первого экранирующего элемента 404 на базовую подложку 50 во второй области перекрытия. Таким образом, второй экранирующий элемент 301 может быть соединен с первым экранирующим элементом 404 через второе сквозное отверстие во второй области перекрытия.

В некоторых вариантах осуществления настоящего раскрытия второй экранирующий элемент 301 может быть выполнен из того же материала, что и рисунок сигнальной линии инициализации.

В некоторых вариантах осуществления настоящего раскрытия подложка дисплея может дополнительно включать в себя второй межслойный изоляционный слой, и второй экранирующий элемент 301 и рисунок сигнальной линии инициализации (например, VINT1 на фиг.3) могут быть размещены на поверхности второго межслойного изоляционного слоя, удаленного от базовой подложки.

Более конкретно, когда второй экранирующий элемент 301 и рисунок сигнальной линии инициализации выполнены из одного и того же материала, и второй экранирующий элемент 301 и рисунок сигнальной линии инициализации (например, VINT1 на фиг.3) размещены на поверхности второго межслойного изоляционного слоя, удаленной от базовой подложки, можно одновременно сформировать второй экранирующий элемент 301 и рисунок сигнальной линии инициализации с помощью единого процесса формирования рисунка и исключить дополнительный процесс формирования рисунка для формирования второго экранирующего элемента 301, тем самым упрощая процесс изготовления подложки дисплея более эффективным образом и снижая стоимость изготовления.

Как показано на фиг.3, в некоторых вариантах осуществления настоящего раскрытия подпиксель может дополнительно включать в себя рисунок VDD сигнальной линии источника питания, который включает в себя участок, проходящий в первом направлении. Схема возбуждения подпикселей может дополнительно включать в себя накопительный конденсатор Cst, первая электродная пластина Cst1 которого повторно используется в качестве электрода затвора возбуждающего транзистора, и вторая электродная пластина Cst2 которого соединена с рисунком VDD сигнальной линии источника питания и расположена на поверхности второго межслойного изоляционного слоя, удаленного от базовой подложки.

Более конкретно, накопительный конденсатор Cst схемы возбуждения подпикселей может включать в себя первую электродную пластину Cst1 и вторую электродную пластину Cst2, размещенные напротив друг друга. Первая электродная пластина Cst1 может быть соединена с электродом затвора возбуждающего транзистора, и вторая электродная пластина Cst2 может быть соединена с рисунком VDD сигнальной линии источника питания. Во время размещения накопительного конденсатора Cst первая электродная пластина Cst1 может быть непосредственно повторно использована в качестве электрода затвора возбуждающего транзистора. Таким образом, можно не только обеспечить соединение накопительного конденсатора Cst с электродом затвора возбуждающего транзистора, но также уменьшить пространство, занимаемое схемой возбуждения подпикселей, тем самым дополнительно улучшая разрешение подложки дисплея. Кроме того, когда вторая электродная пластина Cst2 накопительного конденсатора Cst размещена на поверхности второго межслойного изоляционного слоя, удаленного от базовой подложки, вторая электродная пластина Cst2 накопительного конденсатора Cst может быть сформирована с помощью единого процесса формирования рисунка одновременно со вторым экранирующим элементом 301 и рисунком сигнальной линии инициализации, что позволяет упростить процесс изготовления подложки дисплея более эффективным образом и снизить стоимость изготовления.

Как показано на фиг.14, в некоторых вариантах осуществления настоящего раскрытия подпиксель может дополнительно включать в себя рисунок сигнальной линии сброса (например, RST1 на фиг.3), проходящий во втором направлении, пересекающем первое направление. Схема возбуждения подпикселей может дополнительно включать в себя: первый проводящий соединительный элемент 405, ортогональная проекция которого на базовую подложку 50 по меньшей мере частично перекрывает ортогональную проекцию шестого рисунка 101px проводника на базовую подложку 50; и второй транзистор T2, первый электрод (например, электрод S2 истока) которого соединен с рисунком сигнальной линии инициализации (например, VINT1) через первый проводящий соединительный элемент 405, и второй электрод (например, электрод D2 стока) которого соединен с электродом затвора возбуждающего транзистора, и электрод 202g затвора соединен с рисунком сигнальной линии сброса (например, RST1).

Более конкретно, первый проводящий соединительный элемент 405 может быть выполнен из металлического материала и сформирован с помощью единого процесса формирования рисунка с рисунком линии передачи данных.

Когда ортогональная проекция первого проводящего соединительного элемента 405 на базовую подложку 50 по меньшей мере частично перекрывает ортогональную проекцию шестого рисунка 101px проводника на базовую подложку 50, первый проводящий соединительный элемент 405 может экранировать шестой рисунок 101px проводника. Кроме того, так как первый проводящий соединительный элемент 405 соединен с рисунком сигнальной линии инициализации, первый проводящий соединительный элемент 405 может иметь фиксированный потенциал, что позволяет уменьшить влияние связи между шестым рисунком 101px проводника и другими проводящими рисунками, смежными с шестым рисунком 101px проводника более эффективным образом, тем самым обеспечивая более стабильные рабочие характеристики подложки дисплея.