Предлагаемое изобретение относится к информационно-измерительной технике, в частности, к устройствам измерения электрического напряжения. Изобретение направлено на повышение точности преобразования напряжения в код в многотактных интегрирующих АЦП с суммированием результатов преобразования примыкающих частных циклов за счет оценки составляющей погрешности от краевых эффектов в начале и конце полного цикла преобразования и прямого введения поправки в цифровой форме в результат преобразования.

Известен интегрирующий аналого-цифровой преобразователь, содержащий формирователь весовой функции преобразуемого сигнала, выход которого соединен с перемножителем преобразуемого сигнала и его весовой функции, а на вход поступает сигнал с первого выхода устройства управления, которое также сигналом второго выхода управляет формирователем опорной весовой функции, выход которого соединен с перемножителем опорного сигнала и его весовой функции, полученный выходной сигнал которого как и выходной сигнал перемножителя преобразуемого сигнала и его весовой функции поступают на два входа сумматора, выход которого соединяется с входом интегратора, выходной сигнал которого поступает на первый вход устройства сравнения с пороговым уровнем, поступающим на второй вход, формируемым формирователем порогового уровня, на вход которого поступает сигнал с третьего выхода устройства управления, первый и второй входы которого соединяются с выходом устройства сравнения и выходом генератора опорной частоты соответственно, а четвертый выход - с цифровым счетчиком [1].

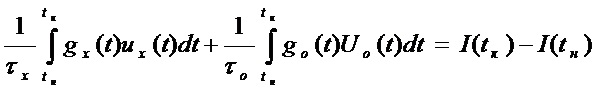

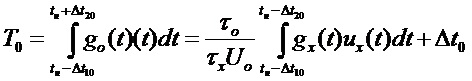

Уравнение преобразования известного устройства может быть представлено в следующем виде:

где ux(t) – преобразуемое напряжение; Uo -опорное (образцовое) напряжение; τx и τо – постоянные времени интегратора со стороны преобразуемого и опорного напряжений соответственно; gx(t) и go(t) – весовые функции; tн и tк – моменты начала и конца интервала интегрирования (времени преобразования); I(tн) и I(tк) – значения выходной величины интегратора в начале и конце полного цикла преобразования интегрирующего АЦП.

Наличие в правой части уравнения (1) разности I(tк) - I(tн) и является источником погрешности, которую принято называть погрешностью от краевых эффектов. На выходе цифрового интегратора формируется результат преобразования, выражаемый следующим соотношением, получающимся путем разрешения уравнения (1) относительно выходной величины

где ∆I = I(tк) - I(tн); ∆Iτo/Uo – абсолютное значение погрешности от краевых эффектов.

Таким образом, недостатком известного устройства [1] является наличие методической составляющей погрешности от краевых эффектов.

Устранение указанного недостатка возможно по известному способу интегрирующего аналого-цифрового преобразования напряжения [2], который заключается в интегрировании разности входного сигнала и промежуточного сигнала, получаемого с помощью импульсной модуляции путем переключения в тактируемый момент времени полярности опорного и порогового напряжений при пересечении интегралом указанной разности порогового уровня и получении кодового эквивалента преобразуемого напряжения путем подсчета импульсов опорной частоты, заполняющей импульсы промежуточного сигнала, при этом основной результат преобразования получается как кодовый эквивалент промежуточного сигнала в течение части полного цикла преобразования, состоящей из периодов импульсной модуляции, полностью укладывающихся в полный цикл преобразования, а кодовые эквиваленты промежуточных сигналов за периоды импульсной модуляции, приходящиеся на начало и конец полного цикла преобразования умножаются на относительное значение части периода импульсной модуляции, находящейся в пределах полного цикла преобразования, и полученные произведения прибавляются к основному результату преобразования.

Так как логические элементы, входящие в состав цифрового корректора результата преобразования, переключаются с задержкой tзад, то при изменении в некоторый момент времени комбинации входных сигналов выходные сигналы устройства (если они изменяются в результате этого) примут установившиеся значения только после того, как закончатся переходные процессы в соответствующих логических элементах. На пути от входов корректора к его выходам (счетчикам) отдельные логические и комбинационные элементы включены последовательно. Поэтому длительность переходных процессов будет зависеть от числа логических элементов, которые включены в такой цепочке. Применяемая в настоящее время методика определения tзад в логических элементах, предусматривающая использование при измерении цепочки включенных друг за другом однотипных логических элементов, позволяет при оценке общей задержки в такой цепочке суммировать задержки отдельных логических элементов. При оценке быстродействия комбинационно-логических цепей необходимо выявить ту цепочку логических элементов между входами и выходами устройства, которая будет задавать наибольшую задержку, и сложить между собой задержки логических элементов этой цепочки. Обычно она содержит наибольшее число включенных друг за другом от входов до выходов логических элементов. Поэтому в общем случае необходимо реализовывать цифровой корректор ИАЦП, содержащий минимальное количество последовательно включенных цифровых логических и комбинационных элементов.

Реализация цифрового корректора результата преобразования в неявной форме, реализованного в ИАЦП-прототипе [2], имеет до 6 последовательно включенных цифровых элементов (6 задержек срабатывания логических элементов), что ограничивает предельно достижимое быстродействие устройства, а их временная нестабильность - предельно достижимую точность ИАЦП. В предлагаемом устройстве суммирование кодирующих импульсов в полном цикле происходит в явной форме несколькими счетчиками импульсов, что снижает количество последовательно включенных логических элементов, а значит и временных задержек, до трёх. Данная особенность позволяет потенциально повысить быстродействие и точность устройства.

Таким образом, цель изобретения - повышение точности аналого-цифрового преобразования.

Поставленная цель достигается тем, что в преобразователь информации, содержащий формирователь весовой функции преобразуемого сигнала, выход которого соединен с перемножителем преобразуемого сигнала и его весовой функции, а на вход поступает сигнал с первого выхода устройства управления, которое также сигналом второго выхода управляет формирователем опорной весовой функции, выход которого соединен с перемножителем опорного сигнала и его весовой функции, полученный выходной сигнал которого как и выходной сигнал перемножителя преобразуемого сигнала и его весовой функции поступают на два входа сумматора, выход которого соединяется с входом интегратора, выходной сигнал которого поступает на первый вход устройства сравнения с пороговым уровнем, поступающим на второй вход, формируемым формирователем порогового уровня, на вход которого поступает сигнал с третьего выхода устройства управления, первый и второй входы которого соединяются с выходом устройства сравнения и выходом генератора опорной частоты соответственно, а четвертый выход с цифровым интегратором, вводятся узлы компенсации погрешности от краевых эффектов в цифровой форме, а именно, первый разрешающий логический элемент И, на входы которого поступают сигналы генератора опорной частоты и пятого выхода устройства управления, а выход соединен с первым входом первого счетчика кодирующих импульсов, второй вход которого соединяется с выходом второй логической И, на входы которой поступают сигналы с выхода устройства сравнения и пятого выхода устройства управления, а выход первого счетчика соединен с первым входом устройства ввода поправки, второй вход которого соединен с выходом второго счетчика импульсов, на первый вход которого поступает выходной сигнал третьей логической И, ко входам которой присоединены пятый выход устройства управления, выход устройства сравнения и выход генератора опорной частоты, а на второй вход второго счетчика импульсов поступает выходной сигнал четвертой логической И, входы которой соединены с выходом устройства сравнения и пятым выходом устройства управления, шестой выход которого соединен со вторым входом пятой логической И, первый вход которой соединен с выходом генератора опорной частоты, а выход с первым входом третьего счетчика импульсов, выход которого соединяется с третьим входом устройства ввода поправки, а второй вход третьего счетчика импульсов соединяется с выходом шестой логической И, на входы которой поступают сигналы с выхода устройства сравнения и с шестого выхода устройства управления, который соединен с третьим входом седьмой логической И, первые два входа которой подключены к выходам генератора опорной частоты и устройства сравнения, а выход к первому входу четвертого счетчика импульсов, выход которого соединяется с четвертым входом устройства ввода поправки, а второй вход четвертого счетчика импульсов подключен к выходу восьмой логической И, на входы которой поступают сигналы с выхода устройства сравнения и шестого выхода устройства управления, седьмой выход которого подключен ко второму входу девятой логической И, первый вход которой соединен с выходом генератора опорной частоты, а выход с первым входом пятого счетчика импульсов, выход которого соединяется с пятым входом устройства ввода поправки, а второй вход пятого счетчика импульсов подключен к выходу десятой логической И, на входы которой поступают сигналы с выхода устройства сравнения и седьмого выхода устройства управления, который соединен с третьим входом одиннадцатой логической И, первые два входа которой подключены к выходам устройства сравнения и генератора опорной частоты, а выход с первым входом шестого счетчика импульсов, выход которого соединяется с шестым входом устройства ввода поправки, а второй вход шестого счетчика импульсов подключен к выходу двенадцатой логической И, на входы которой поступают сигналы с выхода устройства сравнения и седьмого выхода устройства управления, восьмой выход которого подключен к второму входу тринадцатой логической И, первый вход которой соединяется с выходом генератора опорной частоты, а выход с первым входом седьмого счетчика импульсов, выход которого подключен к седьмому входу устройства ввода поправки, а на второй вход седьмого счетчика импульсов поступает выходной сигнал четырнадцатой логической И, входы которой подключены к выходу генератора опорной частоты и восьмому выходу устройства управления, который соединен с третьим входом пятнадцатой логической И, первые два входа которой подключены к выходам устройства сравнения и генератора опорной частоты, а выход с первым входом восьмого счетчика кодирующих импульсов, выход которого соединяется с восьмым входом устройства ввода поправки, а второй вход восьмого счетчика импульсов подключается к выходу шестнадцатой логической И, входы которой соединяются с выходом устройства сравнения и восьмым выходом устройства управления, четвертый выход которого подключен к входу цифрового интегратора, выходной сигнал которого поступает на девятый вход устройства ввода поправки, на выходе которого получается конечный результат интегрирующего аналого-цифрового преобразования с компенсацией погрешности в цифровой форме.

Техническим результатом является повышение точности преобразования за счет минимизации методической составляющей погрешности от краевых эффектов.

Описание работы заявляемого ИАЦП

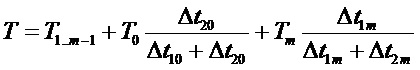

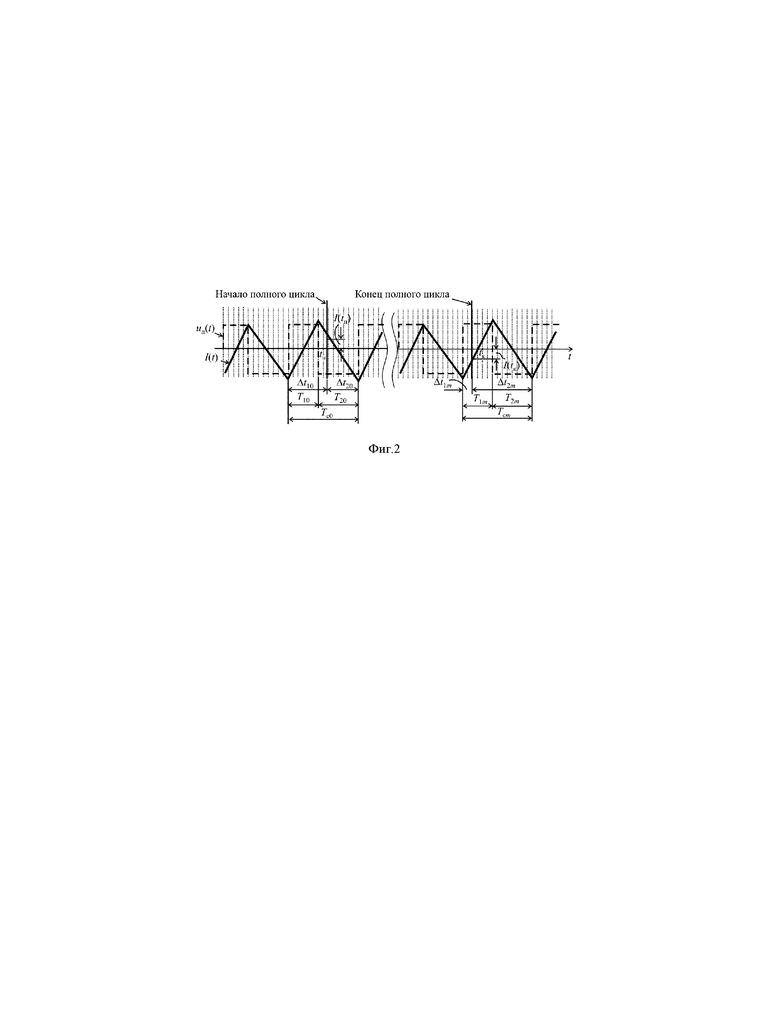

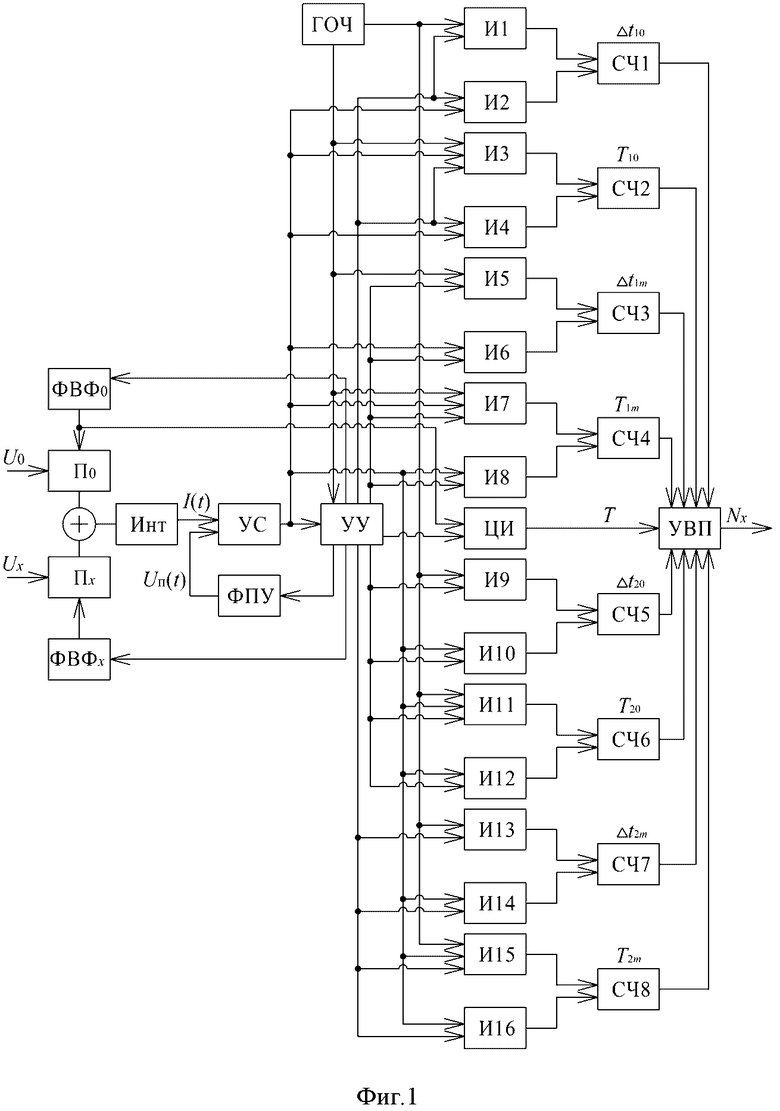

Работа предлагаемого устройства поясняется функциональной схемой и временными диаграммами, представленными на фиг.1 и фиг.2 соответственно.

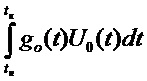

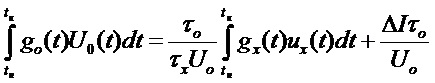

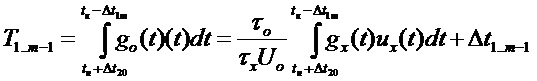

Для пояснения работы предлагаемого ИАЦП с коррекцией погрешности от краевых эффектов обратимся к временной диаграмме на фиг.2. Без учета 0-го и m-го интервалов интегрирования, которые приходятся на моменты начала tн и конца tк времени преобразования, результат преобразования определяется формулой

где ∆t1..m-1 – погрешность квантования.

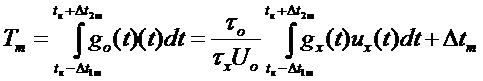

Формула (3) выражает результат преобразования без погрешности от краевых эффектов, он содержит лишь погрешность квантования, которая существенно меньше погрешности от краевых эффектов. Для определения полного результата преобразования за весь интервал интегрирования tк – tн необходимо учесть результаты преобразования T0 и Tm ,соответственно в 0-м и m-м периодах импульсной модуляции, приходящихся на начало и конец времени преобразования. Получим:

где ∆t0 и ∆tm - погрешности квантования.

Очевидно, что скорректированный результат преобразования ИАЦП (известного и предлагаемого устройств) выражается следующей формулой:

где T - скорректированная длительность полного цикла преобразования без погрешности от краевых эффектов; первое слагаемое - сумма длительностей промежуточных частных циклов, полностью входящих в полный цикл; второе слагаемое - длительность частного цикла в начале полного цикла; третье слагаемое - длительность частного цикла в конце полного цикла преобразования.

Реализация интегрирующего аналого-цифрового преобразования с цифровой коррекцией результата преобразования представляется целесообразной на основе ниже предлагаемого устройства, в котором в явной форме, соответствующей алгоритму цифровой коррекции [2], определяется и вводится поправка в результат преобразования полного цикла.

Структурная схема интегрирующего АЦП представлена на фиг.1 и содержит следующие блоки: 1 - формирователь весовой функции опорного сигнала, 4 - формирователь весовой функции преобразуемого сигнала, 2- блок умножения весовой функции на опорное напряжение, 3 - блок умножения весовой функции на преобразуемое напряжение, 4- сумматор, 5 - интегратор, 6 - устройство сравнения (УС), 7 - формирователь порогового уровня (ФПУ), 9 - устройство управления (УУ), 8 - генератор опорной частоты (ГОЧ), 18 - цифровой интегратор – реализуют классический интегрирующий АЦП, в котором осуществляется промежуточная импульсная модуляция напряжения в интервал времени. Блоки 10-26 - цифровые логические элементы И, блоки 27-34 – цифровые счетчики импульсов (ЦСИ), 35-устройство ввода поправки (УВП) - составляют цифровой корректор, который определяет цифровой эквивалент длительности выходного интервала времени за полный цикл преобразования с коррекцией погрешности от краевых эффектов в цифровой форме.

Перед входами каждого из счетчиков установлены разрешающие логические элементы И, поскольку каждый из счетчиков сохраняет результат подсчета кодирующих импульсов с ГОЧ 8 в определенный момент времени преобразования, который задается УУ 9. Все ЦСИ сбрасываются в исходное нулевое состояние передним фронтом выходного импульса УС 6, сбросы также происходят в разрешенные интервалы времени с УУ 9. Интервалы времени, определяемые счетчиками, на функциональной схеме подписаны над каждым счетчиком: ЦСИ 27 начинает подсчет импульсов тактовой частоты по сигналу с УС, соответствующему началу частного цикла и останавливает подсчет в момент начала нового полного цикла, ЦСИ 28 считает кодирующие импульсы, умещающиеся в интервалы высокого уровня сигнала с выхода УС 6, ЦСИ 29 и 30 функционируют аналогично ЦСИ 27 и 28, с той лишь разницей, что остановка счета происходит в конце полного цикла преобразования, т.е. сигнал управления имеет противоположный фронт, ЦСИ 31 считает импульсы с генератора ГОЧ 8 в течение длительности ∆t20, т.е. от начала полного цикла до переднего фронта импульса напряжения с выхода УС 6, счетчик 32 учитывает импульсы ГОЧ 8 в том же интервале и при высоком уровне текущего импульса УС 6, ЦСИ 33 считает импульсы ГОЧ 8 в течение длительности ∆t2m, т.е. от конца полного цикла до переднего фронта нового импульса с УС 6. ЦСИ 34 учитывает импульсы ГОЧ 8 в том же интервале и при высоком уровне текущего импульса УС 6. Блок УВП 35, исходя из поступивших кодовых эквивалентов интервалов времени, формирует поправку, которая вводится в итоговый результат преобразования.

С целью исследования линейности преобразования устройства была разработана имитационная модель ИАЦП. Результаты модельного эксперимента показали существенное улучшение точности преобразования. Так, в работе [2] модельная реализация схемы обеспечила сокращение методической составляющей погрешности от краевых эффектов до 0,4 кванта, а модельная реализация предлагаемого устройства обеспечила сокращение методической составляющей погрешности от краевых эффектов до 0,06 кванта, тем самым показав практически на порядок превосходящий результат.

В ходе исследования линейности функции преобразования были проведены замеры выходного кода при изменении входного сигнала от -1В до 1В с шагом 0,05В. Модель реализует 100 частных циклов в одном полном. При обработке выходных кодов, соответствующих 16 разрядам двоичного кода, получены следующие значения среднеквадратичной погрешности линейности преобразования в единицах младшего значащего разряда - 10,98698 и 0,05965 соответственно для моделирования без компенсации и с компенсацией. Таким образом, методическая составляющая погрешности от краевых эффектов сократилась в относительных единицах более чем в 180 раз. Полученные результаты подтверждают эффективность функционирования предлагаемого устройства интегрирующего аналого-цифрового преобразования напряжения с компенсацией погрешности от краевых эффектов в цифровой форме.

Литература

1. Шахов, Э. К. Интегрирующие развертывающие преобразователи / Э. К. Шахов, В. Д. Михотин. - М.: Энергоатомиздат. - 1986. - 144с.

2. Ашанин В.Н. Способ интегрирующего аналого-цифрового преобразования напряжения / Э. К. Шахов, В. Н. Ашанин, А. И. Надеев // Патент на изобретение РФ № 2294595. - БИ № 6. - 2007.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2005 |

|

RU2294595C1 |

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2005 |

|

RU2291559C1 |

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2005 |

|

RU2292642C1 |

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2006 |

|

RU2303327C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012132C1 |

| Способ аналого-цифрового преобразования с весовым интегрированием и устройство для его реализации | 1981 |

|

SU953722A1 |

| СПОСОБ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИЗМЕРИТЕЛЬНЫХ СИГНАЛОВ | 2009 |

|

RU2444125C2 |

| Сверхвысокочастотный радиометр | 1989 |

|

SU1686388A1 |

| Способ определения наличия успокоения механической системы | 1990 |

|

SU1755059A1 |

| Интегрирующий аналого-цифровой преобразователь | 1987 |

|

SU1628204A1 |

Изобретение относится к информационно-измерительной технике, в частности, к устройствам измерения электрического напряжения. Техническим результатом является повышение точности преобразования напряжения в код за счет оценки составляющей погрешности от краевых эффектов в многотактных интегрирующих АЦП с суммированием результатов преобразования в примыкающих частных циклах в начале и конце полного цикла преобразования и прямого введения поправки в цифровой форме в результат преобразования. Устройство содержит формирователь весовой функции опорного сигнала, формирователь весовой функции преобразуемого сигнала, блок умножения весовой функции на опорное напряжение, блок умножения весовой функции на преобразуемое напряжение, сумматор, интегратор, устройство сравнения, формирователь порогового уровня, устройство управления, генератор опорной частоты, цифровой интегратор, цифровые логические элементы И, цифровые счетчики импульсов, устройство ввода поправки. 2 ил.

Интегрирующий аналого-цифровой преобразователь напряжения, содержащий формирователь весовой функции преобразуемого сигнала, выход которого соединен с перемножителем преобразуемого сигнала и его весовой функции, а на вход поступает сигнал с первого выхода устройства управления, которое также сигналом второго выхода управляет формирователем опорной весовой функции, выход которого соединен с перемножителем опорного сигнала и его весовой функции, полученный выходной сигнал которого как и выходной сигнал перемножителя преобразуемого сигнала и его весовой функции поступают на два входа сумматора, выход которого соединяется с входом интегратора, выходной сигнал которого поступает на первый вход устройства сравнения с пороговым уровнем, поступающим на второй вход, формируемым формирователем порогового уровня, на вход которого поступает сигнал с третьего выхода устройства управления, первый и второй входы которого соединяются с выходом устройства сравнения и выходом генератора опорной частоты соответственно, а четвертый выход с цифровым интегратором, отличающийся тем, что вводятся узлы компенсации погрешности от краевых эффектов в цифровой форме, а именно, первый разрешающий логический элемент И, на входы которого поступают сигналы генератора опорной частоты и пятого выхода устройства управления, а выход соединен с первым входом первого счетчика кодирующих импульсов, второй вход которого соединяется с выходом второй логической И, на входы которой поступают сигналы с выхода устройства сравнения и пятого выхода устройства управления, а выход первого счетчика соединен с первым входом устройства ввода поправки, второй вход которого соединен с выходом второго счетчика импульсов на первый вход которого поступает выходной сигнал третьей логической И, ко входам которой присоединены пятый выход устройства управления, выход устройства сравнения и выход генератора опорной частоты, а на второй вход второго счетчика импульсов поступает выходной сигнал четвертой логической И, входы которой соединены с выходом устройства сравнения и пятым выходом устройства управления, шестой выход которого соединен со вторым входом пятой логической И, первый вход которой соединен с выходом генератора опорной частоты, а выход с первым входом третьего счетчика импульсов, выход которого соединяется с третьим входом устройства ввода поправки, а второй вход третьего счетчика импульсов соединяется с выходом шестой логической И, на входы которой поступают сигналы с выхода устройства сравнения и с шестого выхода устройства управления, который соединен с третьим входом седьмой логической И, первые два входа которой подключены к выходам генератора опорной частоты и устройства сравнения, а выход к первому входу четвертого счетчика импульсов, выход которого соединяется с четвертым входом устройства ввода поправки, а второй вход четвертого счетчика импульсов подключен к выходу восьмой логической И, на входы которой поступают сигналы с выхода устройства сравнения и шестого выхода устройства управления, седьмой выход которого подключен ко второму входу девятой логической И, первый вход которой соединен с выходом генератора опорной частоты, а выход с первым входом пятого счетчика импульсов, выход которого соединяется с пятым входом устройства ввода поправки, а второй вход пятого счетчика импульсов подключен к выходу десятой логической И, на входы которой поступают сигналы с выхода устройства сравнения и седьмого выхода устройства управления, который соединен с третьим входом одиннадцатой логической И, первые два входа которой подключены к выходам устройства сравнения и генератора опорной частоты, а выход с первым входом шестого счетчика импульсов, выход которого соединяется с шестым входом устройства ввода поправки, а второй вход шестого счетчика импульсов подключен к выходу двенадцатой логической И, на входы которой поступают сигналы с выхода устройства сравнения и седьмого выхода устройства управления, восьмой выход которого подключен к второму входу тринадцатой логической И, первый вход которой соединяется с выходом генератора опорной частоты, а выход с первым входом седьмого счетчика импульсов, выход которого подключен к седьмому входу устройства ввода поправки, а на второй вход седьмого счетчика импульсов поступает выходной сигнал четырнадцатой логической И, входы которой подключены к выходу генератора опорной частоты и восьмому выходу устройства управления, который соединен с третьим входом пятнадцатой логической И, первые два входа которой подключены к выходам устройства сравнения и генератора опорной частоты, а выход с первым входом восьмого счетчика кодирующих импульсов, выход которого соединяется с восьмым входом устройства ввода поправки, а второй вход восьмого счетчика импульсов подключается к выходу шестнадцатой логической И, входы которой соединяются с выходом устройства сравнения и восьмым выходом устройства управления, четвертый выход которого подключен к входу цифрового интегратора, выходной сигнал которого поступает на девятый вход устройства ввода поправки, на выходе которого получается конечный результат интегрирующего аналого-цифрового преобразования с компенсацией погрешности в цифровой форме.

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2005 |

|

RU2294595C1 |

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2005 |

|

RU2291559C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2496228C1 |

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2011 |

|

RU2457617C1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 6285310 B1, 04.09.2001. | |||

Авторы

Даты

2020-07-03—Публикация

2018-11-29—Подача