Изобретение относится к цифровой вычислительной технике, в частности к недвоичной технике, и предназначено для создания устройства, реализуемого в среде полупроводниковой интегральной электроники и выполняющего функции Троичной Пороговой Логики.

Известной успешной реализацией недвоичных цифровых устройств являются троичные ЦВМ "Сетунь" и "Сетунь-70" [1, 2]. Логические элементы этих ЦВМ, выполняющие функции Троичной Пороговой Логики [9], изготавливаются на базе электромагнитной техники [9], имеют низкое быстродействие, большие потребляемую мощность и размеры. Элементы ЦВМ "Сетунь" не реализуются в среде интегральной электроники.

Известен функциональный аналог элементов ЦВМ "Сетунь" "Пороговый Элемент Троичной Логики" (ПЭТЛ) [3]. ПЭТЛ реализуется в среде интегральной электроники на основе технологий изготовления интегральных схем эмиттерно-связанной логики (ИС-ЭСЛ) [10].

На ПЭТЛ можно создавать троичные цифровые устройства используя ПЭТЛ-схемотехнику [3, 4, 5, 6, 7, 8], в арсенале которой имеется набор типовых решений и узлов.

Заявляемое изобретение описывает совместимый по интерфейсу аналог ПЭТЛ, реализуемый на основе технологий изготовления интегральных схем на токовых зеркалах (ИС-ТЗ) [11].

Целью изобретения является создание устройства, выполняющего функции Троичной Пороговой Логики и имеющего совместимый с ПЭТЛ интерфейс, на основе технологий, отличных от используемых для изготовления ПЭТЛ.

В результате увеличится выбор возможностей создания троичных устройств с помощью ПЭТЛ-схемотехники.

Наиболее близкими техническими решениями к заявляемому изобретению являются группа изобретений: "Пороговый Элемент Троичной Логики и устройства на его основе" [3]. Эта группа не поддерживает изготовление устройств Троичной Пороговой Логики на токовых зеркалах.

Раскрытие изобретения

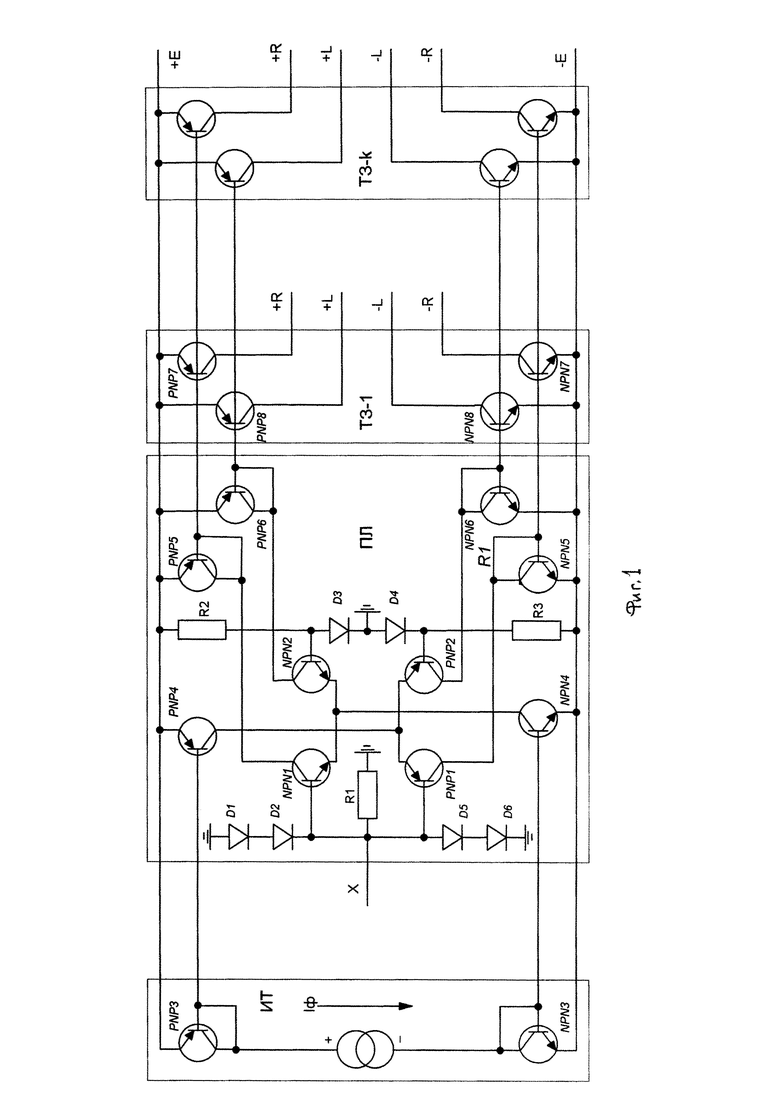

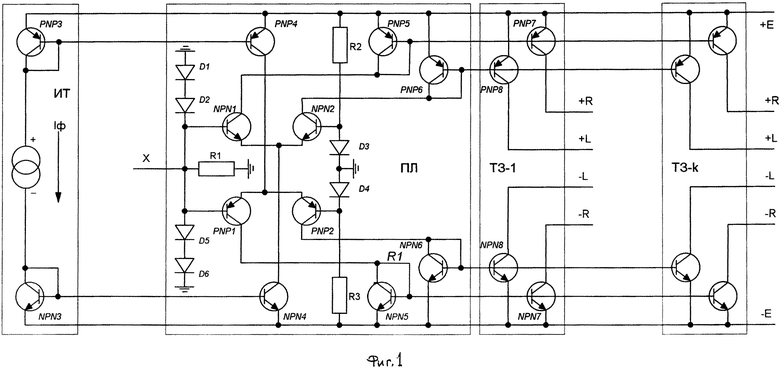

Пороговый Элемент Троичной Логики на Токовых Зеркалах (ПЭТЛ-ТЗ) содержит блок Источника постоянного Тока Iф (ИТ), блок Пороговой Логики (ПЛ) и по меньшей мере один блок Токовых Зеркал (ТЗ).

Коллектор и база транзистора PNP3 и база транзистора PNP4 соединены с положительным выводом источника тока Iф, коллектор и база транзисторов NPN3 и база транзистора NPN4 соединены с отрицательным выводом источника тока Iф.

Коллектор транзистора PNP4 соединен с эмиттерами транзисторов PNP1 и PNP2, коллектор транзистора NPN4 соединен с эмиттерами транзисторов NPN1 и NPN2, коллектор и база транзистора PNP5 соединены с коллектором транзистора NPN1, коллектор и база транзистора PNP6 соединены с коллектором транзистора NPN2, коллектор и база транзистора NPN5 соединены с коллектором транзистора PNP1, коллектор и база транзистора NPN6 соединены с коллектором транзистора PNP2.

Базы транзисторов PNP1 и NPN1, анод диода D5 и катод диода D2 подключены ко входу X ПЭТЛ-ТЗ и через резистор R1 к земле, анод диода D2 подключен к катоду диода D1, катод диода D5 подключен к аноду диода D6. Аноды диодов D1 и D4 и катоды диодов D3 и D6 подключены к земле, анод диода D3 и база транзистора NPN2 через резистор R2 подключены к шине +Е, катод диода D4 и база транзистора PNP2 через резистор R3 подключены к шине -Е,

База транзистора PNP7 соединена с базой транзистора PNP5, база транзистора PNP8 соединена с базой транзистора PNP6, коллекторы транзисторов PNP7 и PNP8 соединены соответственно с выходами +R и +L ПЭТЛ-ТЗ, база транзистора NPN7 соединена с базой транзистора NPN5, база транзистора NPN8 соединена с базой транзистора NPN6, коллекторы транзисторов NPN7 и NPN8 соединены соответственно с выходами и -R и -L ПЭТЛ-ТЗ.

Эмиттеры j-х транзисторов PNP соединены с шиной +Е, эмиттеры j-х транзисторов NPN соединены с шиной -Е (j=3, 4…8).

На Фиг. 1 изображен Пороговый Элемент Троичной Логики на Токовых Зеркалах (ПЭТЛ-ТЗ).

Проектирование устройств на ПЭТЛ-ТЗ предполагает использование ПЭТЛ-схемотехники - набора элементов, узлов, правил их соединения, приемов, типовых решений и изобразительных средств, поддерживающих создание цифровых устройств, работающих в троичной системе с цифрами +1, 0, -1.

ПЭТЛ-схемотехника отличается от других схемотехник. Она описана в [3, 4, 5, 6, 7, 8]. Краткие сведения приведены ниже.

1. Троичные значения (триты) +1, 0, -1 на физическом уровне представлены дискретными токами +Iф, 0, -Iф.

2. ПЭТЛ-ТЭ имеет 1 вход и группу из 4-х выходов: +R, +L, -L, -R.

3. На входе ПЭТЛ-ТЭ происходит алгебраическое сложение разнополярных дискретных токов +Iф, и -Iф и формируется трит X. Если число +Iф больше числа -Iф-Х=+1, если число +Iф меньше числа -Iф-Х=-1, если число +Iф равно числу -Iф-Х=0.

4. ПЭТЛ-ТЭ может иметь более одной группы выходов. Значения на одноименных выходах тождественны.

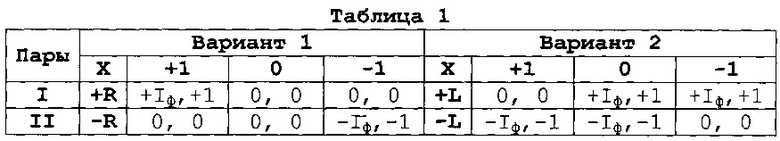

Трит X на входе ПЭТЛ-ТЭ представлен на его выходах парами двузначных компонент: +R, -R и +L, -L. Соответствие значений X и пар приведено в Таблице 1 в тритах и в терминах токов +Iф, 0, -Iф. Пары пронумерованы римскими цифрами, варианты пар - арабскими.

В ПЭТЛ-схемотехнике используются сопоставимые термины из двоичных схемотехник и из лексикона "Сетуней".

Сложение разнополярных дискретных токов +Iф и -Iф на входах элементов и объединение их выходов являются приемами ПЭТЛ-схемотехники. Например, объединяя +R и -R, получим на выходе повторение входного трита X, объединяя +L и -L - его нециклическую инверсию НЕ X, объединяя +R и +L или -R и -L - постоянные значения +1 или -1. Практикуется объединение выходов разных ПЭТЛ.

Функционирование ПЭТЛ-ТЗ

Схема Порогового Элемента Троичной Логики на Токовых Зеркалах (ПЭТЛ-ТЗ) представлена на Фиг. 1. Схема симметрична относительно горизонтальной оси визуально и электрически, поскольку в ней используются комплементарные PNP и NPN транзисторы. В симметричных цепях схемы напряжения имеют разные знаки, а токи противоположно направлены.

ПЭТЛ-ТЗ состоит из Источника Тока (ИТ), блока Пороговой Логики (ПЛ) и Токовых Зеркал (ТЗ-1 - ТЗ-k).

Постоянный ток Iф от ИТ поступает в ПЛ через два токовых зеркала. Транзисторы PNP3 и NPN3 - управляющие, транзисторы PNP4 и NPN4 - "отражающие". Их коллекторные токи поступают в эмиттеры двух транзисторных пар: PNP1, PNP2 и NPN1, NPN2.

Напряжения на базах PNP2 и NPN2 отличаются от нуля на величину прямого напряжения соответственно на диодах D4 и D3.

Разнополярные входные токи +Iф и -Iф суммируются на резисторе R1. Напряжение на X ограничивается снизу и сверху на уровне двойного прямого падения на диодах D1, D2 и D5, D6. Это необходимо если |ΔIф|>1, где ΔIф = (число +Iф) - (число -Iф). При равном числе +Iф и -Iф напряжение на Х=0 и токи, втекающие в эмиттеры PNP1, PNP2 и NPN1, NPN2, проходят через PNP2 и NPN2, поскольку PNP1 и NPN1 заперты по базам. Если (число +Iф) > (числа -Iф), напряжение на Х>0, закрывается NPN2 и открывается NPN1, если (число +Iф) < (числа -Iф), напряжение на Х<0, закрывается PNP2 и открывается PNP1.

Коллекторы NPN1, NPN2, PNP2, PNP1 соединены с управляющими входами четырех токовых зеркал (коллекторы PNP5, PNP6, NPN6, NPN5). Транзисторы PNP7, PNP8, NPN8, NPN7 - "отражающие". Их коллекторные токи, являющиеся двузначными компонентами X (см. Таблицу 1), поступают на выходы +R, +L, -L, -R ПЭТЛ-ТЗ.

Литература

1. Брусенцов Н.П., Маслов С.П., Розин В.П., Тишулина A.M. Малая цифровая вычислительная машина "Сетунь". - М.: Изд-во Московского университета, 1965, 145 с.

2. Брусенцов Н.П., Жоголев Е.А., Маслов С.П., Рамиль Альварес X. Опыт создания троичных цифровых машин. // Компьютеры в Европе. Прошлое, настоящее и будущее. - Киев: Феникс, 1998. С. 67-71.

3. Маслов С.П. Пороговый элемент троичной логики и устройства на его основе. Патент РФ на изобретение RU №2394366 C1. Зарегистрирован: 10.07.2010.

4. Маслов С.П. Узел троичной схемотехники и дешифраторы - переключатели на его основе. Патент РФ на изобретение RU №2461122 C1. Зарегистрирован: 10.09.2012.

5. Маслов С.П. Троичный D-триггер (варианты). Патент РФ на изобретение RU №2510129 C1. Зарегистрирован: 20.03.2014.

6. Маслов С.П. Троичный Т-триггер и Троичный реверсивный счетчик на его основе. Патент РФ на изобретение RU №2562370 C1. Зарегистрирован: 11.08.2015.

7. Маслов С.П. Троичный реверсивный регистр сдвига. Патент РФ на изобретение RU №2585263 C1. Зарегистрирован: 27.05.2016.

8. Маслов С.П. Троичная схемотехника. Тематический сборник №13 "Программные системы и инструменты", М.: Изд-во факультета ВМиК МГУ, 2012. С. 152-158.

9. Брусенцов Н.П. Пороговая реализация трехзначной логики электромагнитными средствами. // Вычислительная техника и вопросы кибернетики. Вып. 9. - М.: Изд-во Моск. ун-та, 1972. С. 3-35.

10. Шило В.Л. Популярные цифровые микросхемы. Изд-во "Металлург", Челябинское отд., 1989, 352 с.: (Массовая радиобиблиотека Вып. 1111), С. 285-295

11. Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 2-е. - М.: Изд-во БИНОМ. 2014, 704 с. С. 96-99

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ТРОИЧНОЙ СХЕМОТЕХНИКИ НА ТОКОВЫХ ЗЕРКАЛАХ | 2017 |

|

RU2648565C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| ТРОИЧНЫЙ D-ТРИГГЕР (ВАРИАНТЫ) | 2012 |

|

RU2510129C1 |

| ТРОИЧНЫЙ ПОРАЗРЯДНЫЙ УМНОЖИТЕЛЬ | 2016 |

|

RU2631166C1 |

| ТРОИЧНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 2017 |

|

RU2642408C1 |

| УСТРОЙСТВО ТРОИЧНОГО СЛОЖЕНИЯ И ВЫЧИТАНИЯ | 2017 |

|

RU2645279C1 |

| ТРОИЧНЫЙ ПОЛНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР (ВАРИАНТЫ) | 2016 |

|

RU2616887C1 |

| ТРОИЧНЫЙ РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 2015 |

|

RU2585263C1 |

| ТРОИЧНЫЙ Т-ТРИГГЕР И ТРОИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК НА ЕГО ОСНОВЕ | 2014 |

|

RU2562370C2 |

| УЗЕЛ ТРОИЧНОЙ СХЕМОТЕХНИКИ И ДЕШИФРАТОРЫ-ПЕРЕКЛЮЧАТЕЛИ НА ЕГО ОСНОВЕ | 2011 |

|

RU2461122C1 |

Изобретение относится к цифровой вычислительной технике, в частности к недвоичной технике, и предназначено для создания цифровых устройств троичной логики. Техническим результатом является реализация порогового элемента троичной логики на токовых зеркалах. Устройство содержит 16 транзисторов, 6 диодов, 3 резистора и источник тока. 1 ил., 1 табл.

Пороговый элемент троичной логики на токовых зеркалах (ПЭТЛ-ТЗ), содержащий блок источника тока IФ (ИТ), блок пороговой логики (ПЛ) и по меньшей мере один блок токовых зеркал (ТЗ), причем блок ИТ состоит из транзистора PNP типа, транзистора NPN типа и источника тока IФ, причем блок ПЛ состоит из пяти транзисторов PNP типа и пяти транзисторов NPN типа, шести диодов и трех резисторов, причем блоки ТЗ состоят из двух транзисторов PNP типа и двух транзисторов NPN типа, причем коллектор и база третьего и база четвертого транзисторов PNP типа соединены с положительным выводом источника тока IФ, причем коллектор и база третьего и база четвертого транзисторов NPN типа соединены с отрицательным выводом источника тока IФ, причем коллектор четвертого транзистора PNP типа соединен с эмиттерами первого и второго транзисторов PNP типа, причем коллектор четвертого транзистора NPN типа соединен с эмиттерами первого и второго транзисторов NPN типа, причем коллектор и база пятого транзистора PNP типа соединены с коллектором первого транзистора NPN типа, причем коллектор и база шестого транзистора PNP типа соединены с коллектором второго транзистора NPN типа, причем коллектор и база пятого транзистора NPN типа соединены с коллектором первого транзистора PNP типа, причем коллектор и база шестого транзистора NPN типа соединены с коллектором второго транзистора PNP типа, причем базы первых транзисторов PNP и NPN типа, анод пятого и катод второго диодов подключены ко входу X ПЭТЛ-ТЗ и через первый резистор к земляной шине, причем анод второго диода подключен к катоду первого диода, причем катод пятого диода подключен к аноду шестого диода, причем аноды первого и четвертого диодов, катоды третьего и шестого диодов подключены к земляной шине, анод третьего диода и база второго транзистора NPN типа через второй резистор подключены к шине положительного питания +Е, причем катод четвертого диода и база второго транзистора PNP типа через третий резистор подключены к шине отрицательного питания -Е, причем база седьмого транзистора PNP типа соединена с базой пятого транзистора PNP типа, причем база восьмого транзистора PNP типа соединена с базой шестого транзистора PNP типа, причем коллекторы седьмого и восьмого транзисторов PNP типа соединены соответственно с положительными R и L выходами ПЭТЛ-ТЗ, причем база седьмого транзистора NPN типа соединена с базой пятого транзистора NPN типа, причем база восьмого транзистора NPN типа соединена с базой шестого транзистора NPN типа, причем коллекторы седьмого и восьмого транзисторов NPN типа соединены соответственно с отрицательными R и L выходами ПЭТЛ-ТЗ, причем эмиттеры j-х транзисторов PNP типа соединены с шиной положительного питания +Е, причем эмиттеры j-х транзисторов NPN типа соединены с шиной отрицательного питания -Е, причем j=3, 4…8.

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| УЗЕЛ ТРОИЧНОЙ СХЕМОТЕХНИКИ И ДЕШИФРАТОРЫ-ПЕРЕКЛЮЧАТЕЛИ НА ЕГО ОСНОВЕ | 2011 |

|

RU2461122C1 |

| Элемент К-значной пороговой логики | 1980 |

|

SU936428A1 |

| JPH 3160820 A, 10.07.1991 | |||

| US 5017817 A, 21.05.1991 | |||

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

Авторы

Даты

2017-05-11—Публикация

2016-06-17—Подача