Группа изобретений относится к устройствам цифровой вычислительной техники, в частности к недвоичной схемотехнике. Создан троичный логический элемент на биполярных комплементарных ненасыщенных транзисторах, на базе которого реализованы устройства троичной логики, такие как формирователь трехзначных констант, троичный повторитель, троичный нециклический инвертор, троичные схемы "ИЛИ", "И" и Троичный полусумматор.

Перспективным направлением развития вычислительной техники является использование отличных от двоичной систем счисления, позволяющих сделать недвоичный компьютер более совершенным математико-логическим инструментом, чем двоичный. Одно из препятствий на этом пути заключается в отсутствии недвоичных логических элементов, реализованных на современной технологической основе, и проверенных схемотехнических решений, касающихся устройства узлов недвоичных компьютеров.

Особое место среди недвоичных систем счисления занимает симметричная троичная система с цифрами -1, 0, +1, которая нашла практическое воплощение в троичных ЭВМ "Сетунь" [1, 2]. Схемные и структурные решения, использованные в них и проверенные практически, могут найти применение в современной цифровой технике.

Известны пороговые элементы троичной логики (ПЭТЛ), на которых построены ЭВМ "Сетунь" [3]. Характерной особенностью ПЭТЛ является представление троичных значений -1, 0, +1 дискретными фиксированными токами -Iф, 0, +Iф, выполнение пороговых функций троичной логики путем алгебраического сложения токов (ампервитков) во входных цепях элементов, возможность разделять троичные значения на их двузначные компоненты, возможность составлять троичные значения из их двузначных компонент. ПЭТЛ выполнены на основе электромагнитной техники на магнитных сердечниках с ППГ [4], обладают низким быстродействием и не могут быть реализованы средствами современных интегральных полупроводниковых технологий.

Прототипом изобретения является двоичный элемент эмиттерно-связанной логики (ЭСЛ) [5]. Элементы ЭСЛ выполнены на биполярных ненасыщенных n-p-n транзисторах и реализуются средствами современных интегральных технологий. Они содержат детали и узлы, входящие в состав предлагаемого порогового элемента троичной логики. В существующем виде ЭСЛ-схемотехника не оперирует с разнополярными токами и не обеспечивает выполнения пороговых функций не только троичной, но и двоичной логик. Для осуществления этих функций существующий двоичный ЭСЛ-элемент модифицируется путем прибавления к его схеме симметричной комплементарной схемы на p-n-p транзисторах. Модифицированный элемент оперирует с разнополярными токами, используемыми также, в отличие от прототипа, в качестве сигналов межэлементных связей, поддерживает алгебраическое суммирование этих сигналов во входной цепи.

Техническим результатом изобретения является повышение технологичности изготовления и быстродействия пороговых элементов троичной логики с одновременным снижением их размеров и энергопотребления.

Предлагаемые пороговые элементы троичной логики характеризуются следующим.

1. Троичные -1, 0, +1 на входе и выходах элемента представляются фиксированными токами -Iф, 0, +Iф.

2. Обеспечивается алгебраическое суммирование токов во входной цепи.

3. Обеспечивается разделение троичного значения на двузначные компоненты.

4. Обеспечивается объединение двузначных компонент в троичное значение.

5. Обеспечивается подключение к выходу элемента нескольких входов.

Раскрытие изобретения

Первым аспектом изобретения является Пороговый элемент троичной логики, содержащий блок эмиттерных повторителей и от одного до m блоков токовых переключателей, причем блок эмиттерных повторителей состоит из двух эмиттерных повторителей, один из которых включает третий резистор и первый транзистор p-n-p типа, другой - пятый резистор и второй транзистор n-p-n типа, коллекторы упомянутых транзисторов соединены между собой и подключены к общей шине элемента, а эмиттеры первого и второго транзисторов p-n-p типа и n-p-n типа через соответствующие резисторы соединены соответственно с шинами положительного и отрицательного питания элемента, вход блока эмиттерных повторителей является входом элемента, который предназначен для подачи токовых сигналов и соединен с первым выводом первого резистора, подключенным к анодам второго и третьего диодов и катодам первого и четвертого диодов, причем катод третьего и анод четвертого диодов и второй вывод первого резистора соединены с общей шиной элемента, анод первого диода соединен с базой первого транзистора p-n-p типа одного из эмиттерных повторителей и через второй резистор с шиной положительного питания элемента, с шиной отрицательного питания которого соединен через четвертый резистор катод второго диода и база второго транзистора n-p-n типа другого из эмиттерных повторителей, эмиттеры первого и второго транзисторов блока эмиттерных повторителей подключены к базам третьего транзистора p-n-p типа и четвертого транзистора n-p-n типа блока токовых переключателей соответственно, коллекторы которых и коллекторы пятого и шестого транзисторов p-n-p и n-p-n типа являются с первой по четвертую выходными шинами элемента, эмиттеры третьего и пятого транзисторов p-n-p типа через первый источник тока соединены с шиной положительного питания элемента, эмиттеры четвертого и шестого транзисторов n-p-n типа через второй источник тока соединены с шиной отрицательного питания элемента, база пятого транзистора p-n-p типа соединена с источником положительного опорного напряжения элемента, база шестого транзистора n-p-n соединена с источником отрицательного опорного напряжения элемента.

Вторым аспектом изобретения является Двухвходовая схема "И", которая содержит пять идентичных элементов троичной логики, первая и вторая выходные шины первого и второго, вторая и четвертая выходные шины третьего и первая и третья выходные шины четвертого пороговых элементов троичной логики соединены с общей шиной устройства, входы первого и второго пороговых элементов троичной логики являются входами троичных переменных устройства, третьи выходы первого и второго пороговых элементов троичной логики объединены со второй и четвертой выходными шинами пятого порогового элемента троичной логики и соединены с входом третьего порогового элемента троичной логики, четвертые выходные шины первого и второго пороговых элементов троичной логики объединены с первой и третьей выходными шинам пятого порогового элемента троичной логики и соединены с входом четвертого порогового элемента троичной логики, вторая выходная шина которого объединена с первой выходной шиной третьего порогового элемента троичной логики и является инверсным выходом устройства, прямым выходом которого является третья выходная шина третьего порогового элемента троичной логики, объединенного с четвертой выходной шиной четвертого порогового элемента троичной логики.

Третьим аспектом изобретения является схема Троичного полусумматора, которая содержит четыре элемента троичной логики с одним и два элемента троичной логики с двумя блоками токовых переключателей, при этом первые и вторые выходные шины первого и второго пороговых элементов троичной логики с одним блоком токовых переключателей объединены и соединены с входом четвертого порогового элемента троичной логики с одним блоком токовых переключателей, первая и вторая выходные шины которого объединены с первыми выходными шинами первого и второго блоков токовых переключателей первого элемента троичной логики с двумя блоками токовых переключателей, со вторыми выходными шинами первого и второго блоков токовых переключателей второго элемента троичной логики с двумя блоками токовых переключателей и является выходом суммы устройства, третьи выходные шины первого, второго и вторая и четвертая выходные шины третьего пороговых элементов троичной логики с одним блоком токовых переключателей объединены и соединены с входом первого элемента троичной логики с двумя блоками токовых переключателей, третья выходная шина второго блока токовых переключателей которого является выходной шиной переноса устройства и объединена с четвертой выходной шиной первого блока токовых переключателей второго блока троичной логики с двумя блоками токовых переключателей, вход которого объединен с третьей и первой выходными шинами третьего порогового элемента троичной логики с одним блоком токовых переключателей и четвертыми выходными шинами первого и второго пороговых элементов троичной логики с одним блоком токовых переключателей, третья, вторая, четвертая выходные шины первого блока токовых переключателей и вторая и четвертая выходные шины второго блока токовых переключателей первого порогового элемента троичной логики с двумя блоками токовых переключателей объединены с первой и третьей выходными шинами первого и второго блоков токовых переключателей второго элемента троичной логики с двумя блоками токовых переключателей, с четвертой выходной шиной второго блока токовых переключателей второго порогового элемента троичной логики с двумя блоками токовых переключателей и общей шиной устройства, входы первого и второго пороговых элементов троичной логики с одним блоком токовых переключателей соединены со входами первого и второго слагаемых устройства.

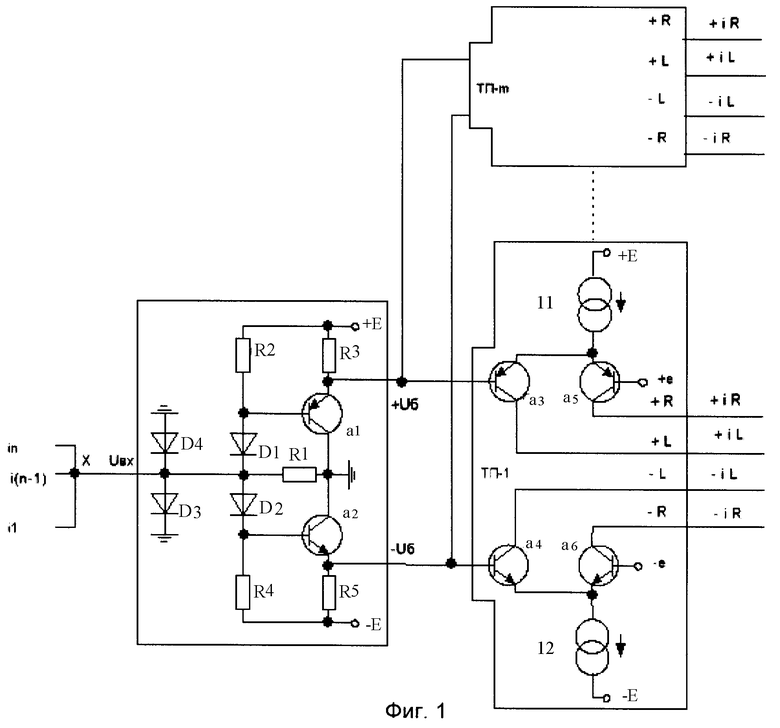

На фиг.1 представлена электрическая схема Порогового элемента троичной логики. Фиг.2 содержит эпюры сигналов, иллюстрирующих работу элемента. На фиг.3 представлены варианты реализации простейших функций троичной логики. На Фиг.4 показана Двухвходовая троичная схема "И". На фиг.5 дается схема Троичного полусумматора.

Элемент пороговой троичной логики (Фиг.1) состоит из блоков: блока эмиттерных повторителей (ЭП) и подключенных в параллель к ЭП m блоков токовых переключателей (ТП-1 - ТП-m). В состав элемента должен входить по крайней мере один блок ТП.

ЭП состоит из двух эмиттерных повторителей, один из которых включает в себя n-p-n транзистор Q2 и резистор R5, другой - p-n-p транзистор Q1 и резистор R3.

Каждый блок ТП состоит из двух переключателей тока: один выполнен на n-p-n транзисторах Q4, Q6, другой - на p-n-p транзисторах Q3, Q5. Токи фиксированной величины Iф формируются источниками тока I1 и I2. Управление переключателями тока осуществляется от ЭП по базам транзисторов Q3, Q4. Базы транзисторов Q5, Q6 подключены соответственно к источникам опорного напряжения +e и -e. (Входящие в состав элемента блоки ЭП и ТП, источники тока I1 и I2, формирователи опорных напряжений +e и -e могут быть выполнены методами и приемами из арсенала ЭСЛ-схемотехники [5]).

Переключаемые токи (+iR, +iL, -iL, -iR) фиксированной величины Iф с коллекторов транзисторов Q5, Q3, Q4, Q6 поступают на третий +R, первый +L, второй -L и четвертый -R выходы элемента соответственно. В зависимости от числа m блоков ТП элемент может иметь m комплектов выходов (+R, +L, -L, -R), при этом сигналы на одноименных выходных шинах идентичны.

К входу элемента могут быть подключены в параллель от 1 до n выходных шин предшествующих элементов, по каждой из которых поступает дискретный токовый сигнал ik, имеющий, вообще говоря, одно из трех значений (ik=+Iф,, ik=0, ik=-Iф). Ток, равный алгебраической сумме входных токов, протекает по резистору R1 и создает на нем падение напряжения Uвх, которое ограничивается сверху и снизу диодами D4 и D3. Uвх со сдвигами, равными прямым падениям напряжения на диодах D1 и D2 в результате протекания по ним токов, задаваемого резисторами R2 и R4, поступают на базы транзисторов Q1 и Q2 соответственно. Напряжения +Uб с эмиттера транзистора Q1 и -Uб с эмиттера Q2 и подаются соответственно на базы транзисторов Q3 и Q4 в блоках ТП и управляют переключателями тока.

Пороговый элемент троичной логики может находиться в одном из трех состояний. Если алгебраическая сумма входных токов нулевая - Uвх=0. Если втекающих токов больше, чем вытекающих, Uвх>0, в противном случае Uвх<0.

Если Uвх=0, то +Uб<+e, а -Uб>-e и токи, формируемые источниками тока I1 и I2, протекают соответственно по коллекторным цепям транзисторов Q3 и Q4. Если Uвх>0, то +Uб>+e и происходит переключение тока из коллекторной цепи транзистора Q3 в коллекторную цепь транзистора Q5. Если Uвх<0, то -Uб<-e и происходит переключение тока из коллекторной цепи транзистора Q4 в коллекторную цепь транзистора Q6.

Сказанное выше является описанием функционирования предлагаемого элемента как электрической схемы и иллюстрируется эпюрами внешних и внутренних сигналов, приведенными на Фиг.2, а также таблицей 1.

В логических терминах функционирование элемента описывается следующим образом: (терминология троичной схемотехники не устоялась, поэтому используемые здесь названия для логических функций условны. Они заимствованы из двоичной логики и из набора терминов, приведенных в описаниях ЭВМ "Сетунь" [1]. Во избежание двусмысленности следует руководствоваться таблицами истинности).

На вход X элемента поступают n дискретных трехзначных сигналов, значение каждого из которых +1, 0 или -1.

n=n+1+n-1+n0

где n+1 - число сигналов, текущие значения которых +1,

n-1 - число сигналов, текущие значения которых -1,

n0 - число сигналов, текущие значения которых 0.

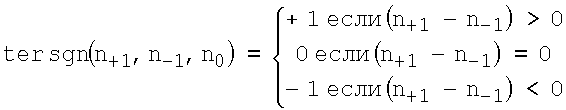

Выполняемое элементом преобразование описывается функцией tersgn(n+1, n-1, n0) трехзначной пороговой логики [3], определенной следующим образом:

Дискретные значения (n+1-n-1): -n,…-2, -1, 0, +1, +2,…+n

Троичная переменная tersgn(n+1, n-1, n0) представлена на выходах элемента двумя парами ее двузначных компонент - двухразрядных двоичных значений [+R, -R] и [+L, -L]. Соответствие значений компонент значениям tersgn(n+1, n-1, n0) дано в таблице 2.

Соединение выходов элемента друг с другом и с выходами других элементов и преобразование tersgn(n+1, n-1, n0) составляет арсенал средств, позволяющих реализовывать на предлагаемых пороговых элементах троичной логики различные логические и технологические функции.

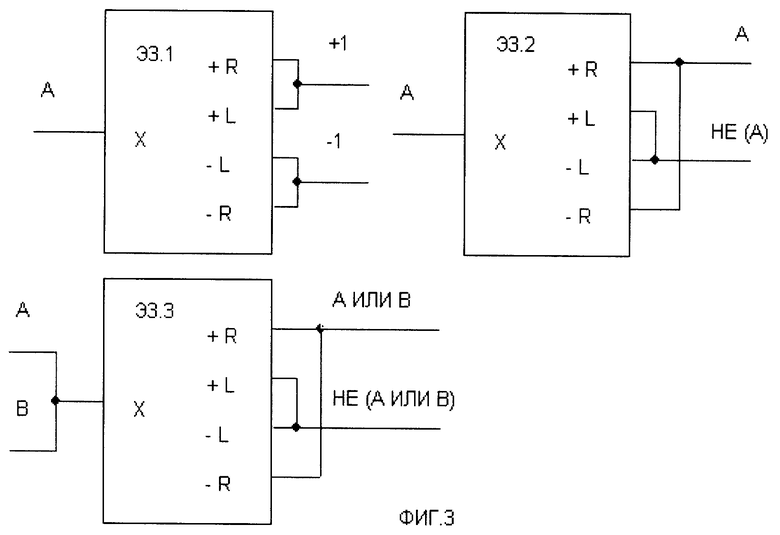

На Фиг.3 показаны три варианта реализации простейших функций на одном элементе. Варианты различаются способами соединения выходов и количеством подключаемых входов. (На Фиг.3 и далее пороговые элементы изображаются в виде прямоугольников со входами X и одним или несколькими комплектами выходов +R, +L, -L, -R. В последнем случае внутри прямоугольника указывается число блоков ТП в элементе).

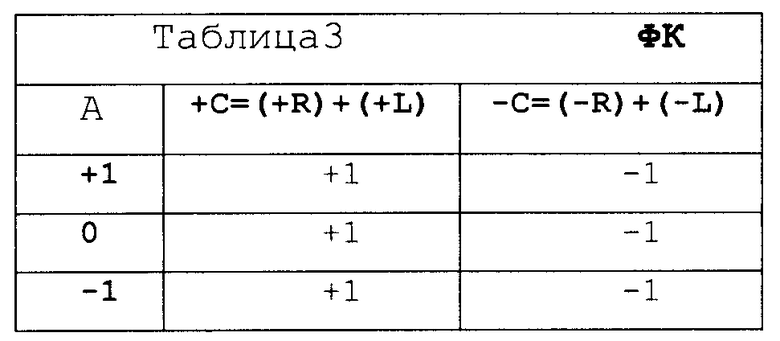

Элемент Э3.1 реализует функцию "формирователя констант" (ФК). Он имеет 2 выхода: +1 и -1. При любом троичном значении на входе на его выходах постоянно выставлены +1 и -1 (дискретные токи фиксированной величины +Iф и -Iф). Назначение ФК - задавать в нужных точках схемы постоянное троичное значение:+1 и -1. (Таким способом осуществляют привязку требуемой точки устройства к заданному логическому значению, используя стандартный узел).

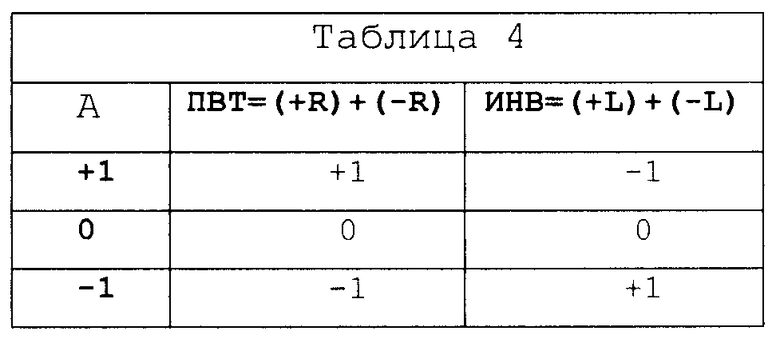

Элемент Э3.2 имеет один вход (A) и два выхода: повторитель входной переменной A (ПВТ) и троичный циклический инвертор входной переменной A (ИНВ).

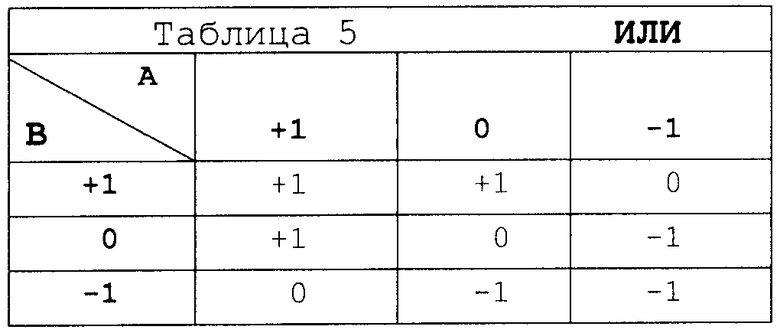

Элемент Э3.3 является троичной двухвходовой (входы A и B) схемой ИЛИ. Она имеет два выхода - прямой и инверсный: А ИЛИ В, и НЕ(А ИЛИ В).

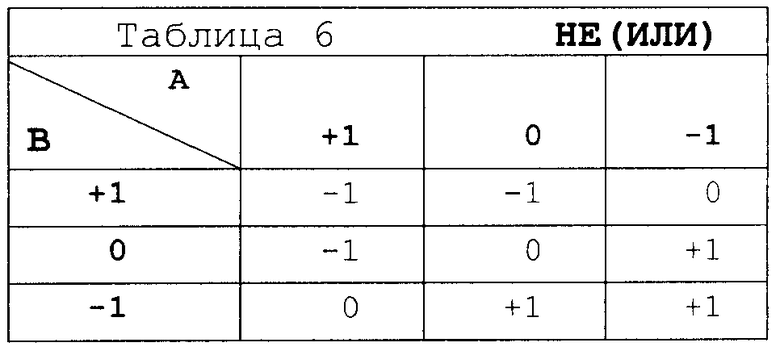

В таблицах 3, 4, 5 и 6 приведены таблицы истинности для схем Фиг.3.

Для реализации троичных логических и операционных структур, вообще говоря, используют несколько элементов. Схемотехника пороговых элементов троичной логики имеет две особенности: троичность и использование дискретных токовых сигналов (СТ-сигналы) вместо дискретных сигналов напряжения (СН-сигналы) в традиционных полупроводниковых схемотехниках (ТТЛ, КМОП и др.).

Троичность: трехзначные сигналы (-1, 0, +1) в схеме могут фигурировать в явном виде и в виде их двузначных компонент. Двузначные компоненты +R, -R, +L, -L (представленные токовыми сигналами на выходах элементов) могут объединяться. В схемах на Фиг.3 объединение осуществляется на выходе элемента, в котором произошло разделение. В более сложных схемах троичное значение, вообще говоря, может формироваться путем объединения двузначных компонент, поступивших с выходов разных элементов. Для реализации некоторых функций могут потребоваться предварительные преобразования двузначных компонент по отдельности.

Особенности СН-элементов и их отличия от СТ-элементов

У СН-элементов высокоомные входы и низкоомные выходы. К их выходам можно подключать в параллель несколько входов, а сами выходы, как правило, нельзя объединять. Для СН-схемотехник типичны элементы с несколькими входами и одним выходом.

У СТ-элементов высокоомные выходы и низкоомные входы. Выходы элементов объединять можно, а входы - нельзя. Для подключения к одному выходу СТ-элемента нескольких входов их следует соединять не в параллель, а последовательно. У элементов "Сетуни", функциональным аналогом которых является предлагаемый элемент, входами являются изолированные обмотки сердечников с ППГ, проблем с последовательным соединением которых не возникает. В интегральной полупроводниковой электронике нет аналогов изолированных обмоток. Поэтому в полупроводниковой СТ-схемотехнике, если требуется подать сигнал с выхода элемента на несколько входов других элементов, используют вариант элемента с несколькими тождественными комплектами выходов (см. Фиг.1 для m≥2). Для СТ-схемотехник типичны элементы с одним входом и несколькими выходами.

Чтобы облегчить чтение схем на СТ-элементах в дальнейшем используется следующий изобразительный прием: сборка выходов обозначается вертикальной линией, у верхнего конца которой стоит либо наименование элемента, ко входу которого эта сборка подключена, либо название формируемого сигнала. Слева от линии располагаются элементы, выходы которых задействованы в данной сборке, справа - элемент (либо выход всей схемы), на который поступает сформированный на сборке сигнал.

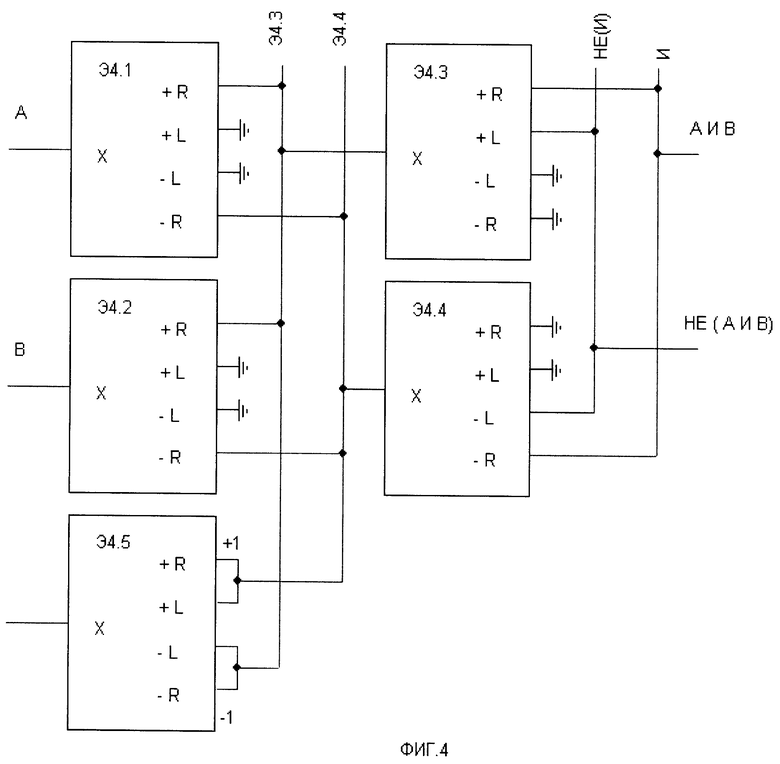

На Фиг.4 показана троичная двухвходовая (входы A и B) схема "И". Она имеет два выхода - прямой и инверсный: A И B и НЕ(A И B). Схема "И" содержит пять идентичных элементов: Э4.1, Э4.2, Э4.3, Э4.4, Э4.5.

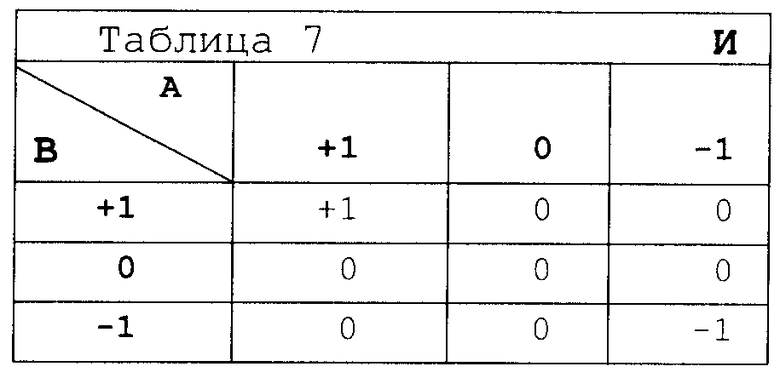

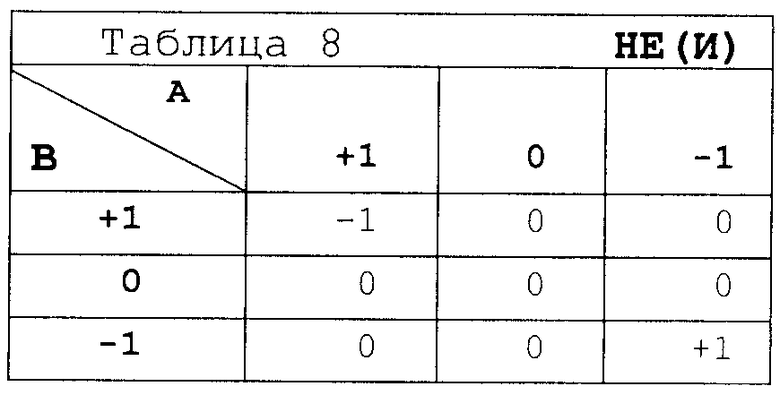

В таблицах 7 и 8 содержатся таблицы истинности для троичной двухвходовой схемы "И".

Элементы Э4.1 и Э4.2 разделяют троичные переменные A и B на их двузначные компоненты. Элемент Э4.5 используется как формирователь констант (ФК). Пары +R и -R от Э4.1 и Э4.2 образуют две сборки, к которым также подключены выходы -1 и +1 от ФК. На сборке +R всегда имеется -1 от ФК, создающая отрицательный порог, а на сборке -R имеется +1 от ФК, создающая положительный порог. Если A=B=+1, отрицательный порог преодолевается и +1 появляется на входе Э4.3, или, если A=B=-1, преодолевается положительный порог и -1 появляется на входе Э4.4. Выход +R элемента Э4.3 образует сборку с выходом -R элемента Э4.4. На ней формируется трехзначный сигнал троичное - A И B. На сборке выходов +L и -L формируется сигнал НЕ(A И B).

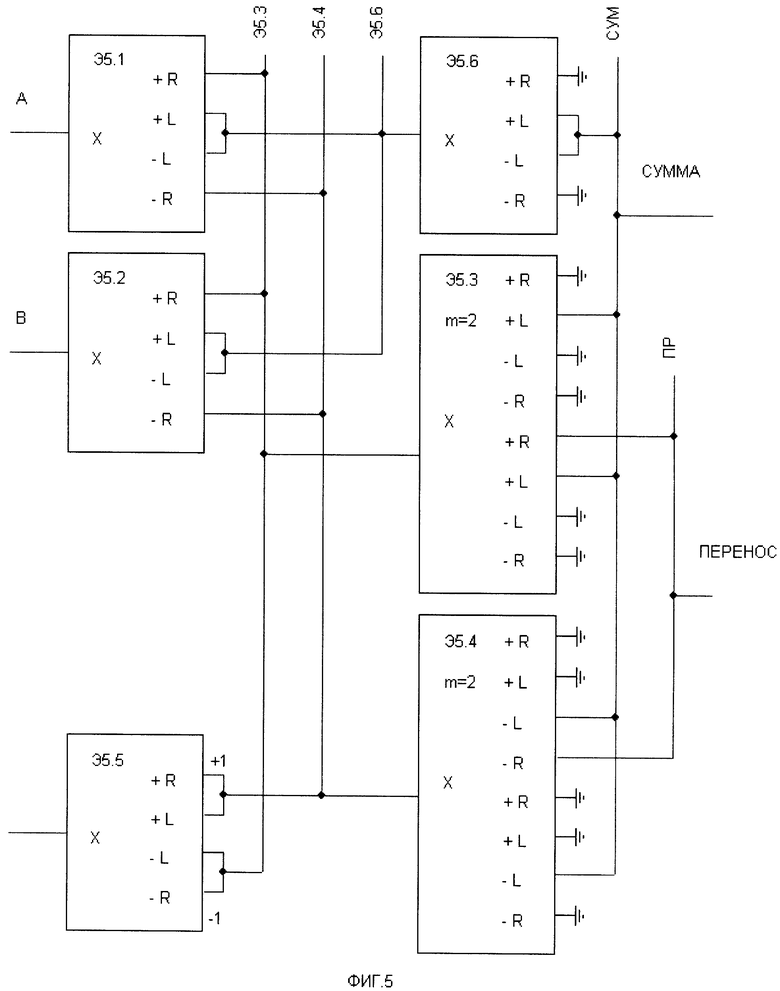

На Фиг.5 представлен Троичный полусумматор. Его схема содержит пять идентичных элементов с одним блоком токовых переключателей (m=1): Э5.1, Э5.2, Э5.3, Э5.4, Э5.5 и два идентичных элемента с двумя блоками токовых переключателей (m=2): Э5.3, Э5.4.

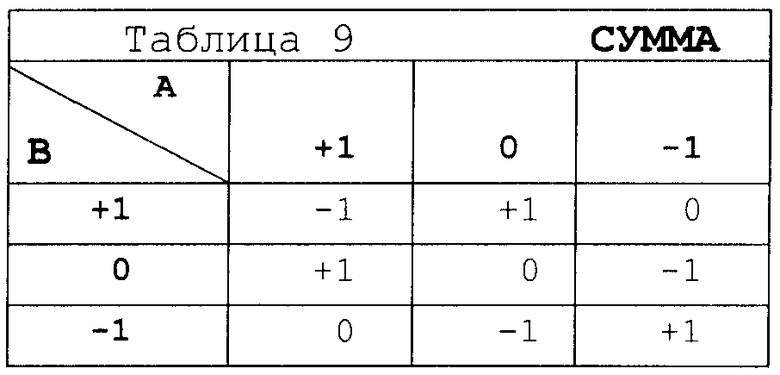

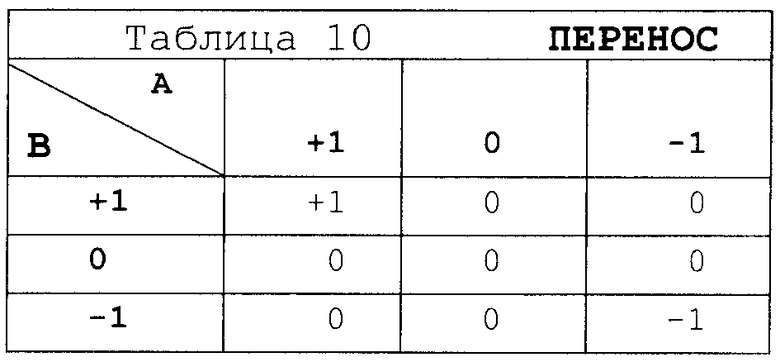

В таблицах 9 и 10 приводятся таблицы истинности для выходов СУММА и ПЕРЕНОС Троичного полусумматора.

Элементы Э5.1 и Э5.2 разделяют троичные переменные A и B на их двузначные компоненты. Элемент Э5.5 используется как формирователь констант (ФК). Пары +R и -R от Э5.1 и Э5.2 образуют две сборки, к которым также подключены выходы -1 и +1 от ФК. На сборке +R всегда имеется -1 от ФК, создающая отрицательный порог, а на сборке -R имеется +1 от ФК, создающая положительный порог. Если A=B=+1, отрицательный порог преодолевается и +1 появляется на входе Э5.3, или, если A=B=-1, преодолевается положительный порог и -1 появляется на входе Э5.4. Выход +R элемента Э5.3 образует сборку с выходом -R элемента Э5.4. На ней формируется трехзначный сигнал ПЕРЕНОС.

На вход элемента Э5.6 со сборки, объединяющей выходы +L и -L элементов Э5.1 и Э5.2, поступают два трехзначных сигнала, инверсных переменным A и B. На сборке выходов +L и -L Э5.6 формируется прямой сигнал A ИЛИ B. Сигнал A ИЛИ B отличается от сигнала СУММА в двух случаях: A=B=+1 и A=B=-1. В этих случаях значения сигнала СУММА инверсны значениям сигнала A ИЛИ B. Чтобы сформировать требуемый сигнал СУММА на сборку СУММА подается удвоенный инвертированный сигнал ПЕРЕНОС, который формируется путем объединения одноименных сигналов +L и -L с выходов элементов Э5.3 и Э5.4. Для удвоения (формирования сигналов +2Iф и -2Iф) используют элементы Э5.3 и Э5.4 в варианте с двумя ТП и двумя комплектами выходов (m=2).

Литература

1. Брусенцов Н.П., Маслов С.П., Розин В.П., Тишулина А.М. Малая цифровая вычислительная машина "Сетунь". - М.: Изд-во Московского университета, 1965. 145 с. http://www.vntb.ru/files/Setun.pdf.

2. Брусенцов Н.П., Жоголев Е.А. Структура и алгоритм функционирования малой вычислительной машины. // Вычислительная техника и вопросы кибернетики. Вып.8. Л.: Изд-во Ленингр. ун-та, 1971. С.34-51.

3. Брусенцов Н.П. Пороговая реализация трехзначной логики электромагнитными средствами. // Вычислительная техника и вопросы кибернетики. Вып.9. - М.: Изд-во Моск. ун-та, 1972. С.3-35. (Текст статьи доступен по запросу с адреса: mailto:spmaslov@gmail.com).

4. Брусенцов Н.П. Электромагнитные цифровые устройства с однопроводной передачей трехзначных сигналов. - В кн.: Магнитные элементы автоматики и вычислительной техники. XIV Всесоюзное совещание (Москва, сентябрь 1972 г.). М., "Наука", 1972, с.242 - 244.

5. Шило В.Л. Популярные цифровые микросхемы. Изд-во "Металлург", Челябинское отд., 1989, 352 с. (Массовая радиобиблиотека Вып.1111), с.285-295.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ НА ТОКОВЫХ ЗЕРКАЛАХ | 2016 |

|

RU2618901C1 |

| УСТРОЙСТВО ТРОИЧНОЙ СХЕМОТЕХНИКИ НА ТОКОВЫХ ЗЕРКАЛАХ | 2017 |

|

RU2648565C1 |

| ТРОИЧНЫЙ РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 2015 |

|

RU2585263C1 |

| УСТРОЙСТВО ТРОИЧНОГО СЛОЖЕНИЯ И ВЫЧИТАНИЯ | 2017 |

|

RU2645279C1 |

| УЗЕЛ ТРОИЧНОЙ СХЕМОТЕХНИКИ И ДЕШИФРАТОРЫ-ПЕРЕКЛЮЧАТЕЛИ НА ЕГО ОСНОВЕ | 2011 |

|

RU2461122C1 |

| ТРОИЧНЫЙ Т-ТРИГГЕР И ТРОИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК НА ЕГО ОСНОВЕ | 2014 |

|

RU2562370C2 |

| ТРОИЧНЫЙ D-ТРИГГЕР (ВАРИАНТЫ) | 2012 |

|

RU2510129C1 |

| ТРОИЧНЫЙ ПОЛНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР (ВАРИАНТЫ) | 2016 |

|

RU2616887C1 |

| ТРОИЧНЫЙ ПОРАЗРЯДНЫЙ УМНОЖИТЕЛЬ | 2016 |

|

RU2631166C1 |

| ТРОИЧНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 2017 |

|

RU2642408C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для реализации на ненасыщенных комплементарных биполярных транзисторах троичных логических устройств. Техническим результатом изобретения является повышение технологичности изготовления и быстродействия пороговых элементов троичной логики с одновременным снижением их размеров и энергопотребления. Для этого пороговый элемент состоит из двух блоков: блока эмиттерных повторителей (ЭП) и подключенных в параллель к ЭП m блоков токовых переключателей (ТП-1 - ТП-m). ЭП реализованы на n-р-n транзисторе Q2 и р-n-р транзисторе Q1, резисторах R5 и R3. Первый повторитель включен между шиной "ОБЩ" и шиной питания "-Е", второй - между шиной питания "+Е" и шиной "ОБЩ". Каждый блок ТП содержит 2 переключателя тока на n-р-n транзисторах Q4, Q6 и р-n-р транзисторах Q3, Q5. Токи фиксированной величины Iф формируются источниками тока I1 и I2, подключенными соответственно к шинам питания "+Е" и "-Е". Управление переключателями тока осуществляется от ЭП по базам транзисторов Q3, Q4. Базы транзисторов Q5, Q6 подключены к источникам опорного напряжения +е и -е. Изобретение также раскрывает Двухвходовое устройство "И" троичной логики и Устройство "Троичный полусумматор", выполненные на основе пороговых элементов троичной логики. 3 н.п. ф-лы, 5 ил., 10 табл.

1. Пороговый элемент троичной логики, содержащий блок эмиттерных повторителей и, по меньшей мере, один блок токовых переключателей, причем блок эмиттерных повторителей состоит из двух эмиттерных повторителей, один из которых включает третий резистор и первый транзистор р-n-р типа, другой - пятый резистор и второй транзистор n-р-n типа, коллекторы упомянутых транзисторов соединены между собой и подключены к общей шине элемента, а эмиттеры первого и второго транзисторов р-n-р типа и n-р-n типа через соответствующие резисторы соединены соответственно с шинами положительного и отрицательного питания элемента, вход блока эмиттерных повторителей является входом элемента, который предназначен для подачи токовых сигналов и соединен с первым выводом первого резистора, подключенным к анодам второго и третьего диодов и катодам первого и четвертого диодов, причем катод третьего и анод четвертого диодов и второй вывод первого резистора соединены с общей шиной элемента, анод первого диода соединен с базой первого транзистора р-n-р типа одного из эмиттерных повторителей и через второй резистор с шиной положительного питания элемента, с шиной отрицательного питания которого соединен через четвертый резистор катод второго диода и база второго транзистора n-р-n типа другого из эмиттерных повторителей, эмиттеры первого и второго транзисторов блока эмиттерных повторителей подключены к базам третьего транзистора р-n-р типа и четвертого транзистора n-p-n типа блока токовых переключателей соответственно, коллекторы которых и коллекторы пятого и шестого транзисторов р-n-р и n-p-n типа являются с первой по четвертую выходными шинами элемента, эмиттеры третьего и пятого транзисторов р-n-р типа через первый источник тока соединены с шиной положительного питания элемента, эмиттеры четвертого и шестого транзисторов n-p-n типа через второй источник тока соединены с шиной отрицательного питания элемента, база пятого транзистора р-n-р типа соединена с источником положительного опорного напряжения элемента, база шестого транзистора n-p-n соединена с источником отрицательного опорного напряжения элемента.

2. Двухвходовое устройство "И" троичной логики, содержащее пять пороговых элементов троичной логики по п.1, первая и вторая выходные шины первого и второго, вторая и четвертая выходные шины третьего и первая и третья выходные шины четвертого пороговых элементов троичной логики соединены с общей шиной устройства, входы первого и второго пороговых элементов троичной логики являются входами троичных переменных устройства, третьи выходы первого и второго пороговых элементов троичной логики объединены со второй и четвертой выходными шинами пятого порогового элемента троичной логики и соединены с входом третьего порогового элемента троичной логики, четвертые выходные шины первого и второго пороговых элементов троичной логики объединены с первой и третьей выходными шинам пятого порогового элемента троичной логики и соединены с входом четвертого порогового элемента троичной логики, вторая выходная шина которого объединена с первой выходной шиной третьего порогового элемента троичной логики и является инверсным выходом устройства, прямым выходом которого является третья выходная шина третьего порогового элемента троичной логики, объединенного с четвертой выходной шиной четвертого порогового элемента троичной логики.

3. Устройство троичный полусумматор, содержащее четыре пороговых элемента троичной логики с одним и два элемента троичной логики с двумя блоками токовых переключателей, при этом первые и вторые выходные шины первого и второго пороговых элементов троичной логики с одним блоком токовых переключателей объединены и соединены с входом четвертого порогового элемента троичной логики с одним блоком токовых переключателей, первая и вторая выходные шины которого объединены с первыми выходными шинами первого и второго блоков токовых переключателей первого элемента троичной логики с двумя блоками токовых переключателей, со вторыми выходными шинами первого и второго блоков токовых переключателей второго элемента троичной логики с двумя блоками токовых переключателей и является выходом суммы устройства, третьи выходные шины первого, второго и вторая и четвертая выходные шины третьего пороговых элементов троичной логики с одним блоком токовых переключателей объединены и соединены с входом первого элемента троичной логики с двумя блоками токовых переключателей, третья выходная шина второго блока токовых переключателей которого является выходной шиной переноса устройства и объединена с четвертой выходной шиной первого блока токовых переключателей второго блока троичной логики с двумя блоками токовых переключателей, вход которого объединен с третьей и первой выходными шинами третьего порогового элемента троичной логики с одним блоком токовых переключателей и четвертыми выходными шинами первого и второго пороговых элементов троичной логики с одним боком токовых переключателей, третья, вторая, четвертая выходные шины первого блока токовых переключателей и вторая и четвертая выходные шины второго блока токовых переключателей первого порогового элемента троичной логики с двумя блоками токовых переключателей объединены с первой и третьей выходными шинами первого и второго блоков токовых переключателей второго элемента троичной логики с двумя блоками токовых переключателей, с четвертой выходной шиной второго блока токовых переключателей второго порогового элемента троичной логики с двумя блоками токовых переключателей и общей шиной устройства, входы первого и второго пороговых элементов троичной логики с одним блоком токовых переключателей соединены с входами первого и второго слагаемых устройства.

| Элемент троичной логики | 1980 |

|

SU892729A1 |

| УНИВЕРСАЛЬНЫЙ МОСТОВОЙ ИНВЕРТИРУЮЩИЙ СУММАТОР | 2007 |

|

RU2331105C1 |

| ТРОИЧНЫЙ ПОТЕНЦИАЛЬНЫЙ ТРИГГЕР | 0 |

|

SU369715A1 |

| US 5610537 A, 11.03.1997 | |||

| US 6339347 B1, 15.01.2002 | |||

| Инструмент для выделения и отрезания нерва | 1984 |

|

SU1183084A1 |

Авторы

Даты

2010-07-10—Публикация

2009-05-28—Подача