ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННЫЕ ЗАЯВКИ

[0001] Заявка испрашивает приоритет китайской патентной заявки № 201720002380.1, поданной 3 января 2017 г., раскрытие которой в полном объеме включено в данное описание в порядке ссылки как часть настоящей заявки.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0002] Примеры настоящего изобретения относятся к схеме освобождения заряда, подложке дисплея, устройству отображения и его способу освобождения заряда.

УРОВЕНЬ ТЕХНИКИ

[0003] Жидкокристаллический дисплей (LCD) включает в себя подложку цветовых фильтров (CF), подложку матрицы, и жидкие кристаллы, расположенный между подложкой CF и подложкой матрицы, подложка цветовых фильтров (CF) и подложка матрицы располагается напротив друг друга.

[0004] Например, общий электрод сформирован на базовой подложке подложки CF, множество поперечно расположенных затворных линий и множество продольно расположенных линий данных сформированы на базовой подложке подложки матрицы, причем затворные линии и линии данных пересекаются друг с другом для формирования множества пиксельных областей, и тонкопленочный транзистор (TFT) и пиксельный электрод сформированы в каждой из множества пиксельных областей. Например, TFT включает в себя затворный электрод, соединенный с затворной линией, истоковый электрод, соединенный с линией данных, и стоковый электрод, соединенный с пиксельным электродом. Когда отображающая панель управляется для отображения изображения, TFT может включаться путем подачи напряжения на затворный электрод по затворной линии, пиксельное напряжение подается на пиксельный электрод через линию данных, истоковый электрод и стоковый электрод, и общее напряжение подается на общий электрод. Жидкие кристаллы вращаются под действием пиксельного напряжения и общего напряжения, благодаря чему, отображающая панель может отображать изображение. Когда не требуется управлять отображающей панелью для отображения изображения, жидкие кристаллы не вращаются благодаря остановке подачи напряжения на пиксельный электрод и общий электрод, благодаря чему, отображающая панель может находиться в состоянии черного экрана.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0005] Примеры настоящего изобретения обеспечивают схему освобождения заряда, подложку дисплея, устройство отображения и его способ освобождения заряда.

[0006] По меньшей мере, один пример настоящего изобретения обеспечивает схему освобождения заряда, содержащую: контроллер, подсхему освобождения заряда и первый проводник, причем подсхема освобождения заряда, соответственно, соединена с контроллером, первым проводником и вторым проводником в активной зоне подложки матрицы, и подсхема освобождения заряда выполнена с возможностью пропускания тока через первый проводник и второй проводник под управлением контроллера, чтобы заряды на втором проводнике могли переходить в первый проводник.

[0007] Согласно схеме освобождения заряда, обеспеченной примером настоящего изобретения, второй проводник содержит, по меньшей мере, одну затворную линию, контроллер содержит первую линию управления, и подсхема освобождения заряда содержит первый блок освобождения заряда, и при этом первый блок освобождения заряда, соответственно, соединен с, по меньшей мере, одной затворной линией, первой линией управления и первым проводником, и первый блок освобождения заряда выполнен с возможностью пропускания тока через первый проводник и, по меньшей мере, одну затворную линию согласно сигналу управления на первой линии управления.

[0008] Согласно схеме освобождения заряда, обеспеченной примером настоящего изобретения, второй проводник содержит множество затворных линий, первый блок освобождения заряда содержит множество первых транзисторов, первая линия управления перпендикулярна к затворной линии, и множество первых транзисторов находится во взаимно-однозначном соответствии с множеством затворных линий; затворный электрод каждого из множества первых транзисторов соединен с первой линией управления, первый электрод каждого из множества первых транзисторов соединен с одной затворной линией во множестве затворных линий, и второй электрод каждого из множества первых транзисторов соединен с первым проводником.

[0009] Согласно схеме освобождения заряда, обеспеченной примером настоящего изобретения, второй проводник содержит, по меньшей мере, одну линию данных, контроллер содержит вторую линию управления, и подсхема освобождения заряда содержит второй блок освобождения заряда; и второй блок освобождения заряда, соответственно, соединен с, по меньшей мере, одной линией данных, второй линией управления и первым проводником, и второй блок освобождения заряда выполнен с возможностью пропускания тока через первый проводник и, по меньшей мере, одну линию данных согласно сигналу управления на второй линии управления.

[0010] Согласно схеме освобождения заряда, обеспеченной примером настоящего изобретения, второй проводник содержит множество линий данных, второй блок освобождения заряда содержит множество вторых транзисторов, вторая линия управления перпендикулярна к линии данных, и множество вторых транзисторов находится во взаимно-однозначном соответствии с множеством линий данных; и затворный электрод каждого из множества вторых транзисторов соединен со второй линией управления, первый электрод каждого из множества вторых транзисторов соединен с одной линией данных во множестве линий данных, и второй электрод каждого из множества вторых транзисторов соединен с первым проводником.

[0011] Согласно схеме освобождения заряда, обеспеченной примером настоящего изобретения, второй проводник дополнительно содержит, по меньшей мере, один пиксельный электрод, контроллер дополнительно содержит третью линию управления, и подсхема освобождения заряда дополнительно содержит третий блок освобождения заряда, и третий блок освобождения заряда, соответственно, соединен с затворной линией и третьей линией управления в подложке матрицы, и третий блок освобождения заряда выполнен с возможностью записывать сигнал управления на третьей линии управления в затворную линию для пропускания тока через каждый пиксельный электрод и линию данных, соединенную с пиксельным электродом.

[0012] Согласно схеме освобождения заряда, обеспеченной примером настоящего изобретения, третий блок освобождения заряда содержит множество третьих транзисторов, причем множество третьих транзисторов находится во взаимно-однозначном соответствии с множеством затворных линий в подложке матрицы, и второй проводник содержит множество пиксельных электродов, соединенных с каждой затворной линией, и третья линия управления перпендикулярна к затворной линии, и оба затворный электрод и первый электрод каждого из множества третьих транзисторов соединены с третьей линией управления, и второй электрод каждого из множества третьих транзисторов соединен с одной затворной линией во множестве затворных линий.

[0013] Согласно схеме освобождения заряда, обеспеченной примером настоящего изобретения, объем первого проводника больше, чем у второго проводника.

[0014] Согласно схеме освобождения заряда, обеспеченной примером настоящего изобретения, первый проводник является линией общего электрода или линией электрода хранения.

[0015] По меньшей мере, один пример настоящего изобретения обеспечивает подложку дисплея, содержащую любую из вышеописанных схем освобождения заряда.

[0016] По меньшей мере, один пример настоящего изобретения обеспечивает устройство отображения, содержащее отображающую панель, в которой отображающая панель содержит любую из вышеописанных подложек дисплея.

[0017] По меньшей мере, один пример настоящего изобретения обеспечивает способ освобождения заряда устройства отображения по п. 11, содержащий: подачу сигнала управления на контроллер, когда отображающая панель находится в состоянии черного экрана, пропускание тока через первый проводник и второй проводник под управлением контроллера, и обеспечение возможности зарядам на втором проводнике переходить в первый проводник.

[0018] Согласно способу, обеспеченному примером настоящего изобретения, первый проводник является линией общего электрода или линией электрода хранения, и второй проводник является, по меньшей мере, одним из затворной линии, линии данных и пиксельным электродом.

[0019] Согласно схеме освобождения заряда, обеспеченной примером настоящего изобретения, объем первого проводника больше, чем у второго проводника.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0020] Для наглядной иллюстрации технического решения примеров изобретения, чертежи примеров будут кратко описаны ниже; очевидно, что описанные чертежи относятся только к некоторым примерам изобретения. Специалисты в данной области техники также может получить другие чертежи на основании этих чертежей без использования творческих способностей.

[0021] Фиг. 1 - схема структуры, иллюстрирующая схему освобождения заряда, обеспеченную примером настоящего изобретения;

[0022] фиг. 2A - схема, демонстрирующая структуру подложки матрицы;

[0023] фиг. 2B - схема, демонстрирующая структуру другой подложки матрицы;

[0024] фиг. 3 - схема, демонстрирующая структуру другой схемы освобождения заряда, обеспеченной примером настоящего изобретения;

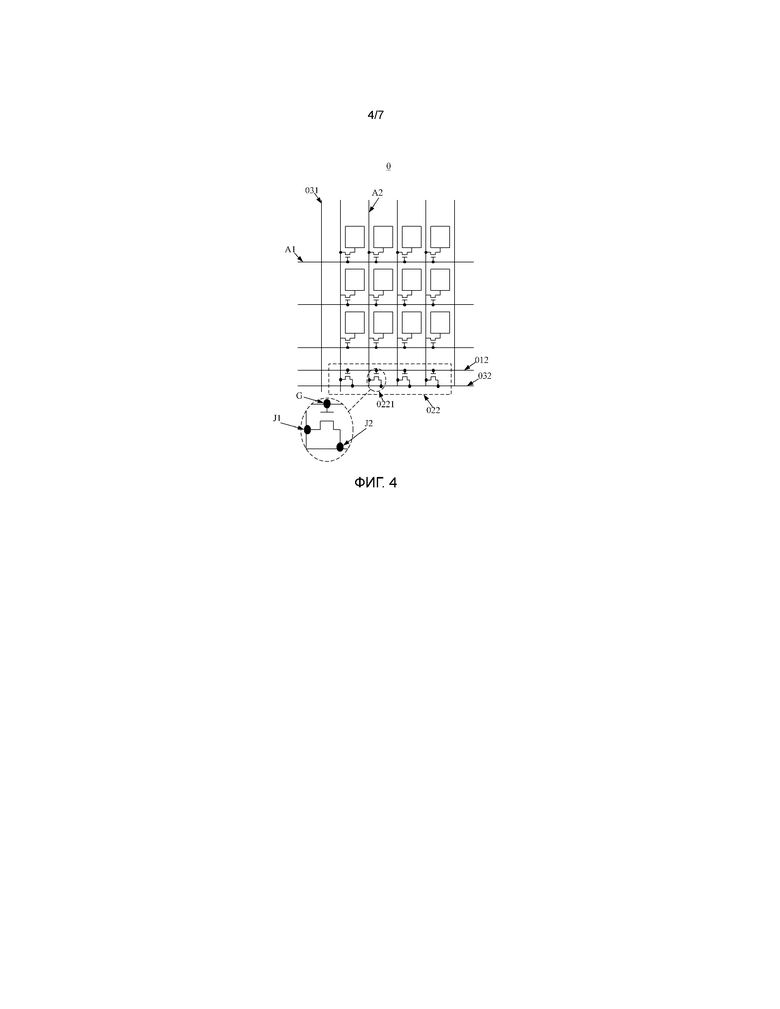

[0025] фиг. 4 - схема, демонстрирующая структуру еще одной схемы освобождения заряда, обеспеченной примером настоящего изобретения;

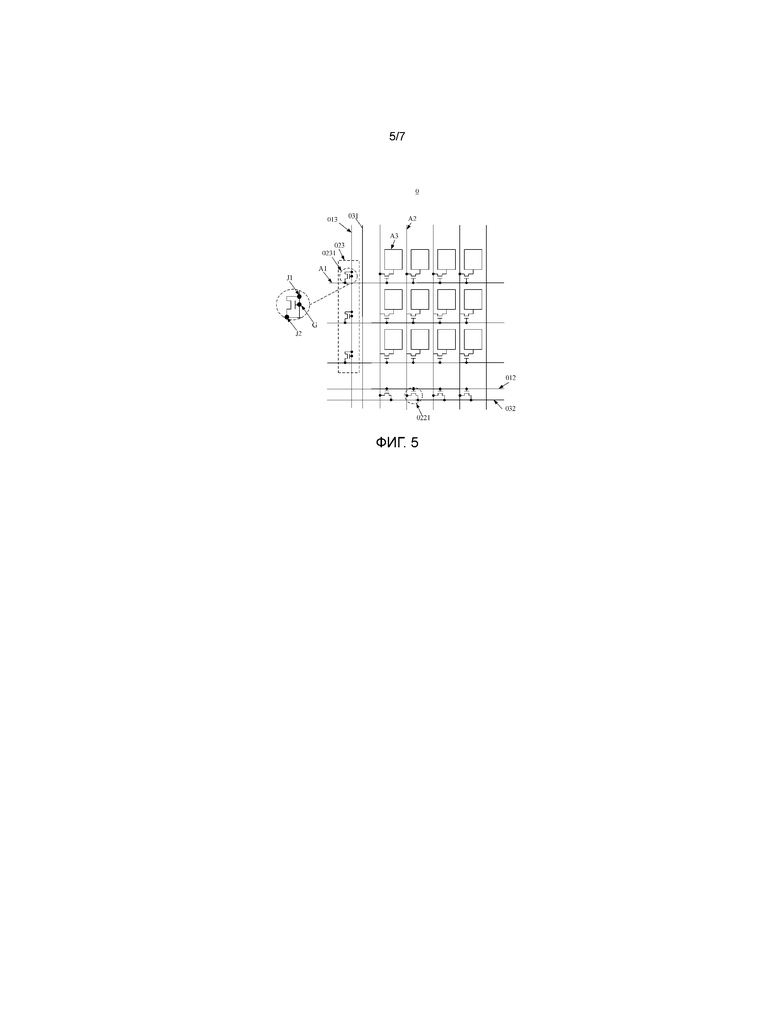

[0026] фиг. 5 - схема, демонстрирующая структуру еще одной схемы освобождения заряда, обеспеченной примером настоящего изобретения;

[0027] фиг. 6 - схема, демонстрирующая структуру схемы освобождения заряда, обеспеченной другим примером настоящего изобретения; и

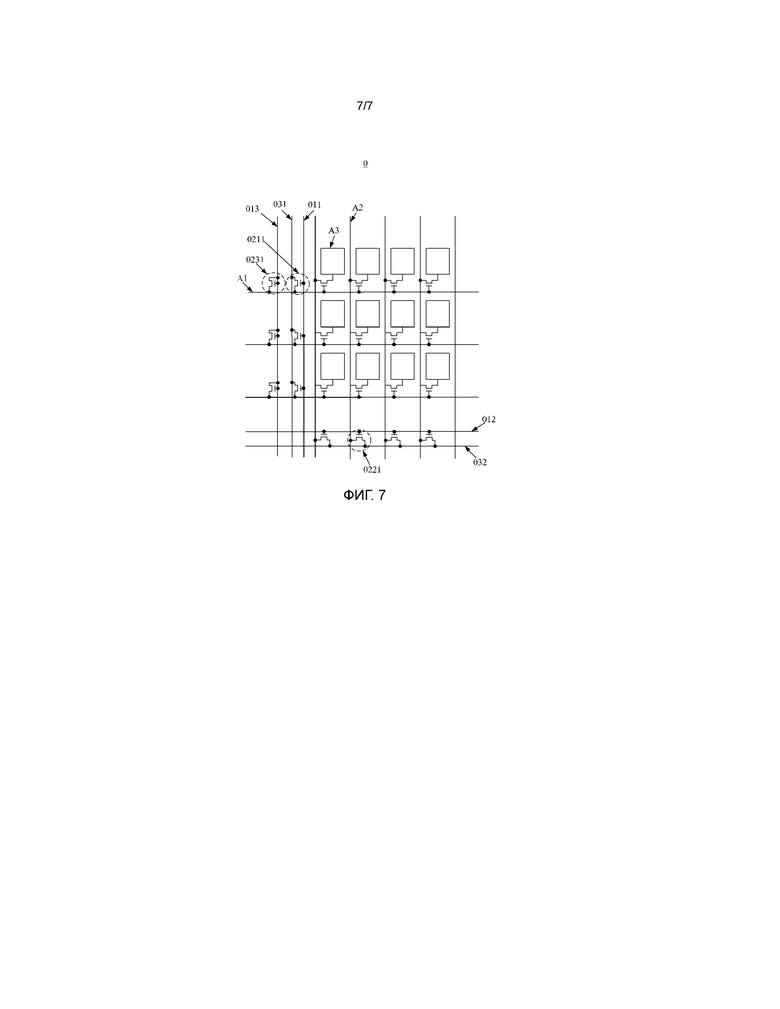

[0028] фиг. 7 - схема, демонстрирующая структуру другой схемы освобождения заряда, обеспеченной другим примером настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ

[0029] Для пояснения задач, технических деталей и преимуществ примеров изобретения, технические решения примеров будут наглядно и полностью описаны в связи с чертежами, относящимися к примерам изобретения. Очевидно, описанные примеры составляют лишь часть, но не все примеры изобретения. На основании описанных здесь примеров, специалисты в данной области техники может получить другой(ие) пример(ы), без использования творческих способностей, которые подлежат включению в объем изобретения.

[0030] Если не задано обратное, все используемые здесь технические и научные термины имеют те же смысловые значения, которые известны специалисту в области техники, к которой относится настоящее изобретение. Термины ʺпервыйʺ, ʺвторойʺ, и т.д., которые используются в настоящем изобретении, не призваны указывать какую-либо последовательность, величину или важность, но предназначены для различения различных компонентов. Кроме того, употребление терминов в единственном числе не призвано ограничивать величину, но указывает наличие, по меньшей мере, одного. Термины ʺсодержатʺ, ʺсодержащийʺ, ʺвключать в себяʺ, ʺвключающий в себяʺ и т.д., призваны указывать, что элементы или объекты упомянутые перед этими терминами, охватывают элементы или объекты и их эквиваленты, перечисленные после этих терминов, но не исключают другие элементы или объекты. Выражения ʺсоединятьʺ, ʺсоединенныйʺ, и т.д., не призваны задавать физическое соединение или механическое соединение, но может включать в себя электрическое соединение, прямо или косвенно. ʺНаʺ, ʺподʺ, ʺсправаʺ, ʺслеваʺ и пр. используются только для указания соотношения относительного положения, и когда положение описанного объекта изменяется, соотношение относительного положения может изменяться соответственно.

[0031] Когда отображающей панелью не требуется управлять для отображения изображения, поскольку некоторые заряды будут оставаться на частичных проводниках (например, затворных линиях и линиях данных) в активной зоне подложки матрицы, когда напряжение подается в предыдущий момент, частичные жидкие кристаллы все же будут вращаться, поэтому отображающая панель в состоянии черного экрана будет отображать яркие пятна.

[0032] Транзисторы, применяемые во всех примерах настоящего изобретения, могут быть все TFT, полевые транзисторы (FET) или другие элементы с одинаковыми характеристиками. Ввиду функции в схеме, транзисторы, применяемые в примерах настоящего изобретения, в основном, являются переключающими транзисторами. Поскольку истоковый электрод и стоковый электрод применяемого здесь переключающего транзистора симметричны, истоковый электрод и стоковый электрод могут меняться местами. В примерах настоящего изобретения, чтобы различать два электрода транзистора за исключением затворного электрода, истоковый электрод именуется первым электродом, и стоковый электрод именуется вторым электродом. Согласно форме на фигуре, затворный электрод располагается посередине транзистора, истоковый электрод располагается на конце ввода сигнала, и стоковый электрод располагается на конце вывода сигнала. Кроме того, переключающий транзистор, применяемый в примерах настоящего изобретения, включает в себя, по меньшей мере, один из переключающего транзистора P-типа и переключающего транзистора N-типа. Переключающий транзистор P-типа включается, когда затворный электрод находится на низком уровне и отключается когда затворный электрод находится на высоком уровне. Переключающий транзистор N-типа включается, когда затворный электрод находится на высоком уровне и отключается когда затворный электрод находится на низком уровне.

[0033] На фиг. 1 показана схема, демонстрирующая структуру схемы 0 освобождения заряда, обеспеченную примером настоящего изобретения. Как показано на фиг. 1, схема 0 освобождения заряда может включать в себя: контроллер 01, подсхему 02 освобождения заряда и первый проводник 03. Подсхема 02 освобождения заряда, соответственно, соединена с контроллером 01, первым проводником 03 и вторым проводником A в активной зоне подложки матрицы. Контроллер 01 может быть модулем управления. Подсхема 02 освобождения заряда может быть модулем освобождения заряда.

[0034] Подсхема 02 освобождения заряда выполнена с возможностью пропускания тока через первый проводник 03 и второй проводник A под управлением контроллера 01, чтобы заряды на втором проводнике A могли переходить в первый проводник 03. Например, первый проводник 03 может быть заземлен.

[0035] Например, в схеме освобождения заряда, обеспеченной примером настоящего изобретения, подсхема 02 освобождения заряда, соответственно, соединена с контроллером 01 и первым проводником 03, и подсхема 02 освобождения заряда выполнена с возможностью пропускания тока через первый проводник 03 и второй проводник A в активной зоне подложки матрицы согласно функции контроллера 01, благодаря чему, заряд на втором проводнике A может переходить на первый проводник 03, таким образом, снижая количество зарядов на втором проводнике A в активной зоне подложки матрицы, для уменьшения вероятности поворота жидких кристаллов, когда отображающая панель находится в состоянии черного экрана, и уменьшения количества ярких пятен на отображающей панели в состоянии черного экрана.

[0036] На фиг. 2A показана схема, демонстрирующая структуру подложки 1 матрицы. Как показано на фиг. 2A, подложка 1 матрицы может включать в себя базовую подложку 100, множество затворных линий A1 и множество линий A2 данных сформированы в активной зоне Y базовой подложки 100 и изолированы друг от друга и пересекаются друг с другом для формирования множества пиксельных областей. Транзистор A4 и пиксельный электрод A3 сформированы в каждой из множества пиксельных областей, затворный электрод транзистора A4 соединен с затворной линией A1 благодаря чему, формируется пиксельная область, истоковый электрод транзистора A4 соединен с линией A2 данных, благодаря чему, формируется пиксельная область, и стоковый электрод транзистора A4 соединен с пиксельным электродом A3 в пиксельной области. Например, первая линия 031 общего электрода и вторая линия 032 общего электрода сформированы в неактивной зоне (а именно, краевой зоне) базовой подложки 100. Например, первая линия 031 общего электрода перпендикулярна к затворной линии A1, и вторая линия 032 общего электрода перпендикулярна к линии A2 данных. Например, первая линия 031 общего электрода изолирована от затворной линии A1, и вторая линия 032 общего электрода изолирована от линии A2 данных. Например, линия данных выполнена с возможностью ввода сигнала данных в пиксель, и сигнал данных, например, включает в себя напряжение шкалы серого. Например, затворная линия выполнена с возможностью ввода сигнала затвора в транзистор, и сигнал затвора, например, включает в себя напряжение затвора.

[0037] Как показано на фиг. 2B, множество линий A0 электрода хранения может дополнительно формироваться в активной зоне Y базовой подложки 100, и каждая из множества линий A0 электрода хранения может проходить через строку пиксельных областей и параллельна затворной линии A1.

[0038] Например, как показано на фиг. 2A и 2B, транзисторы A4 располагаются в матрице, каждая из множества затворных линий соединена со строкой транзисторов A4, каждая из множества линий данных соединена со столбцом транзисторов A4, и каждый пиксельный электрод соединен с транзистором A4. Пиксельный электрод, соответствующий каждой затворной линии, представляет собой: пиксельный электрод, соединенный с затворной линией через транзистор A4. Линия данных, соответствующая каждому пиксельному электроду, представляет собой: линия данных, соединенная с пиксельным электродом через транзистор A4.

[0039] Например, объем первого проводника 03 может быть больше, чем у второго проводника A. В этот момент, поскольку объем первого проводника 03 велик, количество зарядов, которые могут переноситься первым проводником 03, также велико, поэтому первый проводник 03 может нести больше зарядов для второго проводника A. Например, ширина линии первого проводника 03 может быть больше, чем у второго проводника A, поэтому количество зарядов, которые могут переноситься первым проводником 03, велико. В порядке иллюстрации, подложка матрицы может включать в себя базовую подложку, и множественные провода могут быть сформированы на базовой подложке, линия общего электрода и линия электрода хранения широки, и другие провода (например, затворная линия и линия данных) узки, первый проводник 03 может быть линией общего электрода или линией электрода хранения на подложке матрицы, и второй проводник A может быть любым проводником в активной зоне подложки матрицы, например, второй проводник A может быть затворной линией, линией данных или пиксельным электродом.

[0040] Ниже будет приведено описание схемы освобождения заряда, обеспеченной примерами настоящего изобретения с учетом того, что первый проводник является линией общего электрода на подложке матрицы и второй проводник, соответственно, является затворной линией, линией данных или пиксельным электродом на подложке матрицы в порядке примера.

[0041] В первом аспекте, второй проводник может включать в себя, по меньшей мере, одну затворную линию, контроллер может включать в себя первую линию управления, подсхема освобождения заряда может включать в себя первый блок освобождения заряда, и первый блок освобождения заряда, соответственно, соединен с, по меньшей мере, одной затворной линией, первой линией управления и первым проводником, и первый блок освобождения заряда выполнен с возможностью пропускания тока через первый проводник и, по меньшей мере, одну затворную линию согласно сигналу управления на первой линии управления.

[0042] На фиг. 3 показана схема, демонстрирующая структуру схемы 0 освобождения заряда, обеспеченную примером настоящего изобретения. Как показано на фиг. 3, второй проводник может включать в себя множество затворных линий A1, первый блок 021 освобождения заряда может включать в себя множество первых транзисторов 0211, и множество первых транзисторов 0211 находится во взаимно-однозначном соответствии с множеством затворных линий A1. Затворный электрод G каждого из множества первых транзисторов 0211 соединен с первой линией 011 управления, первый электрод J1 каждого из множества первых транзисторов 0211 соединен с затворной линией A1, соответствующей первому транзистору, второй электрод J2 каждого из множества первых транзисторов 0211 соединен с первой линией 031 общего электрода, перпендикулярной к затворной линии A1, и первая линия 011 управления перпендикулярна к затворной линии A1. Например, первая линия 011 управления изолирована от затворной линии A1.

[0043] Когда отображающей панелью требуется управлять так, чтобы она находилась в состоянии черного экрана, сигнал управления может вводиться в первую линию 011 управления, благодаря чему, каждый из множества первых транзисторов 0211 во множестве первых транзисторов 0211 может находиться во включенном состоянии (а именно, первый электрод J1 и второй электрод J2 каждого из множества первых транзисторов 0211 находятся во включенном состоянии), и затем каждый из множества первых транзисторов 0211 пропускает ток через затворную линию A1 и первую линию 031 общего электрода, которые соединены первым транзистором. В этот момент, если существуют остаточные заряды на затворной линии A1, остаточные заряды могут течь к первой линии 031 общего электрода, поэтому количество зарядов на затворной линии A1 может уменьшаться. В этот момент, первым проводником для переноса зарядов на втором проводнике является первая линия 031 общего электрода. Когда отображающая панель находится в состоянии черного экрана, количество зарядов на затворной линии мало, что препятствует вращению жидких кристаллов под действием напряжения, во избежание отображения ярких пятен на отображающей панели, и для решения проблемы отображения ярких пятен отображающей панелью в состоянии черного экрана.

[0044] Во втором аспекте, второй проводник может включать в себя, по меньшей мере, одну линию данных, контроллер может включать в себя вторую линию управления, подсхема освобождения заряда может включать в себя второй блок освобождения заряда, и второй блок освобождения заряда может быть соответственно соединен с, по меньшей мере, одной линией данных, второй линией управления и первым проводником, и второй блок освобождения заряда выполнен с возможностью пропускания тока через первый проводник и, по меньшей мере, одну линию данных согласно сигналу управления на второй линии управления.

[0045] На фиг. 4 показана схема, демонстрирующая структуру еще одной схемы 0 освобождения заряда, обеспеченной примером настоящего изобретения. Как показано на фиг. 4, по меньшей мере, одна линия данных во втором проводнике может включать в себя множество линий A2 данных, второй блок 022 освобождения заряда может включать в себя множество вторых транзисторов 0221, и множество вторых транзисторов 0221 может находиться во взаимно-однозначном соответствии с множеством линий A2 данных. Затворный электрод G каждого из множества вторых транзисторов 0221 соединен со второй линией 012 управления, первый электрод J1 каждого из множества вторых транзисторов 0221 соединен с линией A2 данных, соответствующей второму транзистору, и второй электрод J2 каждого из множества вторых транзисторов 0221 соединен со второй линией 032 общего электрода, перпендикулярной к линии A2 данных. Например, вторая линия 012 управления может быть перпендикулярна к линии A2 данных.

[0046] Когда отображающей панелью требуется управлять так, чтобы она находилась в состоянии черного экрана, сигнал управления может вводиться во вторую линию 012 управления, благодаря чему, каждый из множества вторых транзисторов 0221 может находиться во включенном состоянии для пропускания тока через линию A2 данных и вторую линию 032 общего электрода, которые соединены вторым транзистором. В этот момент, если существуют остаточные заряды на линии A2 данных, остаточные заряды могут течь во вторую линию 032 общего электрода, поэтому количество зарядов на линии A2 данных может уменьшаться. В этот момент, первый проводник для переноса зарядов на втором проводнике является второй линией 032 общего электрода. Когда отображающая панель находится в состоянии черного экрана, количество зарядов на линии данных мало, что препятствует вращению жидких кристаллов под действием напряжения во избежание отображения ярких пятен на отображающей панели.

[0047] В третьем аспекте, на основании второго аспекта, второй проводник может дополнительно включать в себя, по меньшей мере, один пиксельный электрод, контроллер может дополнительно включать в себя третью линию управления, подсхема освобождения заряда может дополнительно включать в себя третий блок освобождения заряда, и третий блок освобождения заряда может быть соответственно соединен с затворной линией и третьей линией управления в подложке матрицы, и третий блок освобождения заряда выполнен с возможностью записывать сигнал управления на третьей линии управления в затворную линию для пропускания тока через пиксельный электрод и линию данных, соответствующую пиксельному электроду.

[0048] На фиг. 5 показана схема, демонстрирующая структуру еще одной схемы 0 освобождения заряда, обеспеченной примером настоящего изобретения. Как показано на фиг. 5, на основании фиг. 4, подсхема освобождения заряда может дополнительно включать в себя третий блок 023 освобождения заряда, третий блок 023 освобождения заряда может включать в себя множество третьих транзисторов 0231, которые находятся во взаимно-однозначном соответствии с множеством затворных линий A1 в подложке матрицы, по меньшей мере, один пиксельный электрод во втором проводнике может включать в себя множество пиксельных электродов A3, соответствующих каждой затворной линии A1, оба затворный электрод G и первый электрод J1 каждого из множества третьих транзисторов 0231 соединены с третьей линией 013 управления, второй электрод J2 каждого из множества третьих транзисторов 0231 соединен с затворной линией A1, соответствующей третьему транзистору 0231, и третья линия 013 управления может быть перпендикулярна к затворной линии A1.

[0049] Когда отображающей панелью требуется управлять так, чтобы она находилась в состоянии черного экрана, сигнал управления также может вводиться в третью линию 013 управления, благодаря чему, каждый из множества третьих транзисторов 0231 может находиться во включенном состоянии. Таким образом, сигнал управления на третьей линии 013 управления может вводиться в затворную линию A1, соответствующую третьему транзистору 0231 вдоль первого электрода и второго электрода третьего транзистора 0231, и транзисторы в пиксельных областях, соединенных с затворной линией A1, включены, и, таким образом, пиксельный электрод A3, соответствующий затворной линии A1, и линия A2 данных, соответствующая пиксельному электроду A3, могут соединяться друг с другом. Например, сигнал управления также может вводиться во вторую линию 012 управления, благодаря чему, каждый из множества вторых транзисторов 0221 может находиться во включенном состоянии для пропускания тока через линию A2 данных и вторую линию 032 общего электрода, которые соединены вторым транзистором. В этот момент, если существуют остаточные заряды на пиксельном электроде A3, остаточные заряды могут течь в линию A2 данных и затем течь во вторую линию 032 общего электрода, поэтому количество зарядов на линии A2 данных и пиксельном электроде A3 может уменьшаться. В этот момент, первый проводник для переноса зарядов на втором проводнике является второй линией 032 общего электрода. Когда отображающая панель находится в состоянии черного экрана, количество зарядов на линии данных и пиксельном электроде мало, что препятствует вращению жидких кристаллов под действием напряжения во избежание отображения ярких пятен на отображающей панели.

[0050] В четвертом аспекте, на фиг. 6 показана схема, демонстрирующая структуру схемы 0 освобождения заряда, обеспеченную другим примером настоящего изобретения. Как показано на фиг. 6, второй проводник включает в себя множество затворных линий A1 и множество линий A2 данных на подложке матрицы, и схема 0 освобождения заряда может включать в себя множество первых транзисторов 0211, множество вторых транзисторов 0221, первую линию 011 управления, вторую линию 012 управления, первую линию 031 общего электрода и вторую линию 032 общего электрода.

[0051] Например, первая линия 031 общего электрода перпендикулярна к затворной линии A1 и параллельна линии A2 данных, первая линия 011 управления параллельна первой линии 031 общего электрода, вторая линия 032 общего электрода перпендикулярна к линии A2 данных и параллельна затворной линии A1, вторая линия 012 управления параллельна второй линии 032 общего электрода, множество первых транзисторов 0211 находится во взаимно-однозначном соответствии с множеством затворных линий A1, и множество вторых транзисторов 0221 находится во взаимно-однозначном соответствии с множеством линий A2 данных. Затворный электрод каждого из множества первых транзисторов 0211 соединен с первой линией 011 управления, первый электрод каждого из множества первых транзисторов 0211 соединен с затворной линией A1, соответствующей первому транзистору, и второй электрод каждого из множества первых транзисторов 0211 соединен с первой линией 031 общего электрода. Затворный электрод каждого из множества вторых транзисторов 0221 соединен со второй линией 012 управления, первый электрод каждого из множества вторых транзисторов 0221 соединен с линией A2 данных, соответствующей второму транзистору, и второй электрод каждого из множества вторых транзисторов 0221 соединен со второй линией 032 общего электрода.

[0052] Когда отображающей панелью требуется управлять так, чтобы она находилась в состоянии черного экрана, сигнал управления может вводиться в первую линию 011 управления, благодаря чему, каждый из множества первых транзисторов 0211 может находиться во включенном состоянии для пропускания тока через затворную линию A1 и первую линию 031 общего электрода, которые соединены первым транзистором. В этот момент, если существуют остаточные заряды на затворной линии A1, остаточные заряды могут течь к первой линии 031 общего электрода, поэтому количество зарядов на затворной линии A1 может уменьшаться. Сигнал управления также может вводиться во вторую линию 012 управления, благодаря чему, каждый из множества вторых транзисторов 0221 может находиться во включенном состоянии для пропускания тока через линию A2 данных и вторую линию 032 общего электрода, которые соединены вторым транзистором. В этот момент, если существуют остаточные заряды на линии A2 данных, остаточные заряды могут течь во вторую линию 032 общего электрода, поэтому количество зарядов на линии A2 данных может уменьшаться. В этот момент, первым проводником для переноса зарядов на втором проводнике является первая линия 031 общего электрода и вторая линия 032 общего электрода. Когда отображающая панель находится в состоянии черного экрана, количество зарядов на линии данных мало.

[0053] В пятом аспекте, на фиг. 7 показана схема, демонстрирующая структуру другой схемы 0 освобождения заряда обеспеченный другим примером настоящего изобретения. Как показано на фиг. 7, второй проводник включает в себя множество затворных линий A1, множество линий A2 данных и множество пиксельных электродов A3 на подложке матрицы, и схема 0 освобождения заряда может включать в себя множество первых транзисторов 0211, множество вторых транзисторов 0221, множество третьих транзисторов 0231, первую линию 011 управления, вторую линию 012 управления, третью линию 013 управления, первую линию 031 общего электрода и вторую линию 032 общего электрода.

[0054] Например, первая линия 031 общего электрода перпендикулярна к затворной линии A1 и параллельна линии A2 данных, обе первая линия 011 управления и третья линия 013 управления параллельны первой линии 031 общего электрода и расположены вблизи первой линии 031 общего электрода. Например, первая линия 011 управления располагается на стороне первой линии 031 общего электрода вблизи активной зоны, и третья линия 013 управления располагается на стороне первой линии 031 общего электрода на удалении от активной зоны. Вторая линия 032 общего электрода перпендикулярна к линии A2 данных и параллельна затворной линии A1. Вторая линия 012 управления параллельна второй линии 032 общего электрода и располагается вблизи второй линии 032 общего электрода, например, располагается на стороне второй линии 032 общего электрода вблизи активной зоны.

[0055] Множество первых транзисторов 0211 находится во взаимно-однозначном соответствии с множеством затворных линий A1, множество вторых транзисторов 0221 находится во взаимно-однозначном соответствии с множеством линий A2 данных, и множество третьих транзисторов 0231 находится во взаимно-однозначном соответствии с множеством затворных линий A1. Затворный электрод каждого из множества первых транзисторов 0211 соединен с первой линией 011 управления, первый электрод каждого из множества первых транзисторов 0211 соединен с затворной линией A1, соответствующей первому транзистору, и второй электрод каждого из множества первых транзисторов 0211 соединен с первой линией 031 общего электрода. Затворный электрод каждого из множества вторых транзисторов 0221 соединен со второй линией 012 управления, первый электрод каждого из множества вторых транзисторов 0221 соединен с линией A2 данных, соответствующей второму транзистору, и второй электрод каждого из множества вторых транзисторов 0221 соединен со второй линией 032 общего электрода. Оба затворный электрод и первый электрод каждого из множества третьих транзисторов 0231 соединены с третьей линией 013 управления, и второй электрод каждого из множества третьих транзисторов 0231 соединен с затворной линией A1, соответствующей третьему транзистору.

[0056] Когда отображающей панелью требуется управлять так, чтобы она находилась в состоянии черного экрана, сигнал управления может вводиться в первую линию 011 управления, благодаря чему, каждый из множества первых транзисторов 0211 может находиться во включенном состоянии для пропускания тока через затворную линию A1 и первую линию 031 общего электрода, которые соединены первым транзистором. В этот момент, если существуют остаточные заряды на затворной линии A1, остаточные заряды могут течь к первой линии 031 общего электрода, поэтому количество зарядов на затворной линии A1 может уменьшаться.

[0057] Например, сигнал управления также может вводиться во вторую линию 012 управления, благодаря чему, каждый из множества вторых транзисторов 0221 может находиться во включенном состоянии для пропускания тока через линию A2 данных и вторую линию 032 общего электрода, которые соединены вторым транзистором. В этот момент, если существуют остаточные заряды на линии A2 данных, остаточные заряды могут течь во вторую линию 032 общего электрода, поэтому количество зарядов на линии A2 данных может уменьшаться. Когда отображающая панель находится в состоянии черного экрана, количество зарядов на линии данных мало.

[0058] Кроме того, сигнал управления также может вводиться в третью линию 013 управления, благодаря чему, каждый из множества третьих транзисторов 0231 может находиться во включенном состоянии. Таким образом, сигнал управления на третьей линии 013 управления может вводиться в затворную линию A1, соответствующую третьему транзистору 0231 вдоль первого электрода и второго электрода третьего транзистора 0231, и пиксельный электрод A3, соответствующий затворной линии A1, и линия A2 данных, соответствующая пиксельному электроду A3, могут соединяться друг с другом. В этот момент, если существуют остаточные заряды на пиксельном электроде A3, остаточные заряды могут течь в линию A2 данных и затем течь во вторую линию 032 общего электрода, поэтому количество зарядов на линии A2 данных и пиксельном электроде A3 может уменьшаться.

[0059] В этот момент, первым проводником для переноса зарядов на втором проводнике является первая линия 031 общего электрода и вторая линия 032 общего электрода. Когда отображающая панель находится в состоянии черного экрана, количество зарядов на проводнике (например, затворной линии, линии данных и пиксельном электроде) в активной зоне подложки матрицы мало, что препятствует вращению жидких кристаллов под действием напряжения во избежание отображения ярких пятен на отображающей панели.

[0060] Например, в примере настоящего изобретения, компоненты с тем же направлением удлинения могут быть сформированы в одном и том же слое. Например, по меньшей мере, две из линии A2 данных, первой линии 031 общего электрода, первой линии 011 управления и третьей линии 013 управления могут быть сформированы в одном и том же слое, например, располагаться в первом слое. По меньшей мере, две из затворной линии A1, второй линии 012 управления и второй линии 032 общего электрода могут быть сформированы в одном и том же слое, например, располагаться во втором слое. Например, изолирующий слой может располагаться между первым слоем и вторым слоем, благодаря чему, две линии электрически не соединены в точке пересечения.

[0061] Например, в примерах настоящего изобретения, два компонента могут быть соединены друг с другом через транзистор. Например, черные точки на фигурах могут обозначать электрическое соединение. Например, в прилагаемых чертежах, две пересекающиеся линии изолированы друг от друга в точке пересечения.

[0062] В итоге, в схеме освобождения заряда, обеспеченной примером настоящего изобретения, подсхема освобождения заряда, соответственно, соединена с контроллером и первым проводником, и подсхема освобождения заряда выполнена с возможностью пропускания тока через первый проводник и второй проводник в активной зоне подложки матрицы под действием контроллера, благодаря чему, заряды на втором проводнике могут переходить на первый проводник, таким образом, снижая количество зарядов на втором проводнике в активной зоне подложки матрицы, для уменьшения вероятности поворота жидких кристаллов, когда отображающая панель находится в состоянии черного экрана, и уменьшения количества ярких пятен на отображающей панели в состоянии черного экрана.

[0063] Пример настоящего изобретения дополнительно обеспечивает подложку дисплея, которая может включать в себя любую схему освобождения заряда, как показано на фиг. 1, фиг. 3, фиг. 4, фиг. 5, фиг. 6 или фиг. 7.

[0064] Кроме того, пример настоящего изобретения дополнительно обеспечивает отображающую панель, которая может включать в себя подложку дисплея, снабженную любой схемой освобождения заряда как показано на фиг. 1, фиг. 3, фиг. 4, фиг. 5, фиг. 6 или фиг. 7. Например, подложка дисплея может быть подложкой матрицы. Например, отображающая панель может дополнительно включать в себя противоположную подложку, расположенную напротив подложки матрицы. Например, противоположная подложка может быть подложкой CF, но без ограничения ими. В фактическом применении, подложка дисплея также может может быть противоположной подложкой. Никаких ограничений не будет установлено здесь в примерах настоящего изобретения.

[0065] Кроме того, пример настоящего изобретения дополнительно обеспечивает устройство отображения, которое включает в себя отображающую панель. Подложка дисплея в отображающей панели может включать в себя любую схему освобождения заряда как показано на фиг. 1, фиг. 3, фиг. 4, фиг. 5, фиг. 6 или фиг. 7. Устройством отображения может быть любой продукт или компонент с функцией отображения, например, панель LCD, электронная бумага, панель на органических светодиодах (OLED), панель на органических светодиодах с активной матрицей (AMOLED), мобильный телефон, планшетный PC, телевизор, дисплей, компьютер-ноутбук, цифровая фоторамка или навигатор.

[0066] По меньшей мере, пример настоящего изобретения дополнительно обеспечивает способ освобождения заряда устройства отображения, который включает в себя освобождение зарядов с использованием любой вышеописанной схемы освобождения заряда. Способ включает в себя: подачу сигнала управления на контроллер, когда отображающая панель находится в состоянии черного экрана, пропускание тока через первый проводник и второй проводник под управлением контроллера, и обеспечение возможности зарядам на втором проводнике переходить в первый проводник.

[0067] Например, когда отображающая панель находится в состоянии черного экрана, устройство отображения находится в дежурном состоянии.

[0068] Выше описаны лишь конкретные реализации настоящего изобретения, и объем защиты настоящего изобретения не ограничивается ими. Любые изменения или замены в техническом объеме настоящего изобретения, которые специалисты в данной области техники могут легко предложить, подлежат включению в объем защиты настоящего изобретения. Поэтому объем защиты настоящего изобретения должен основываться на объеме защиты формулы изобретения.

Изобретение относится к схемам освобождения заряда. Технический результат заключается в снижении количества ярких точек на отображающей панели в состоянии черного экрана. Схема освобождения заряда содержит: контроллер, подсхему освобождения заряда и первый проводник. Подсхема освобождения заряда по отдельности соединена с контроллером, первым проводником и вторым проводником в области эффективного отображения подложки матрицы. Подсхема освобождения заряда выполнена с возможностью пропускания тока через первый проводник и второй проводник под управлением контроллера, благодаря чему заряд во втором проводнике переходит на первый проводник. 4 н. и 10 з.п. ф-лы, 8 ил.

1. Схема освобождения заряда, содержащая: контроллер, подсхему освобождения заряда и первый проводник, причем подсхема освобождения заряда соединена с контроллером, первым проводником и вторым проводником соответственно, причем второй проводник расположен в активной зоне подложки матрицы, и

подсхема освобождения заряда выполнена с возможностью пропускания тока через первый проводник и второй проводник под управлением контроллера, чтобы заряды на втором проводнике могли переходить в первый проводник;

причем второй проводник содержит по меньшей мере одну линию данных, контроллер содержит вторую линию управления и подсхема освобождения заряда содержит второй блок освобождения заряда и

причем второй блок освобождения заряда соединен с по меньшей мере одной линией данных, второй линией управления и первым проводником соответственно и второй блок освобождения заряда выполнен с возможностью пропускания тока через первый проводник и по меньшей мере одну линию данных согласно сигналу управления на второй линии управления.

2. Схема освобождения заряда по п. 1, в которой второй проводник содержит по меньшей мере одну затворную линию, контроллер содержит первую линию управления и подсхема освобождения заряда содержит первый блок освобождения заряда, и

причем первый блок освобождения заряда соединен с по меньшей мере одной затворной линией, первой линией управления и первым проводником соответственно и первый блок освобождения заряда выполнен с возможностью пропускания тока через первый проводник и по меньшей мере одну затворную линию согласно сигналу управления на первой линии управления.

3. Схема освобождения заряда по п. 2, в которой второй проводник содержит множество затворных линий, первый блок освобождения заряда содержит множество первых транзисторов, первая линия управления перпендикулярна к затворной линии и множество первых транзисторов находится во взаимно-однозначном соответствии с множеством затворных линий;

причем затворный электрод каждого из множества первых транзисторов соединен с первой линией управления, первый электрод каждого из множества первых транзисторов соединен с одной затворной линией во множестве затворных линий и второй электрод каждого из множества первых транзисторов соединен с первым проводником.

4. Схема освобождения заряда по п. 2 или 3, в которой второй проводник содержит множество линий данных, второй блок освобождения заряда содержит множество вторых транзисторов, вторая линия управления перпендикулярна к линии данных и множество вторых транзисторов находится во взаимно-однозначном соответствии с множеством линий данных; и

причем затворный электрод каждого из множества вторых транзисторов соединен со второй линией управления, первый электрод каждого из множества вторых транзисторов соединен с одной линией данных во множестве линий данных и второй электрод каждого из множества вторых транзисторов соединен с первым проводником.

5. Схема освобождения заряда по п. 4, в которой второй проводник дополнительно содержит по меньшей мере один пиксельный электрод, контроллер дополнительно содержит третью линию управления и подсхема освобождения заряда дополнительно содержит третий блок освобождения заряда, и

причем третий блок освобождения заряда соединен с затворной линией и третьей линией управления в подложке матрицы соответственно и третий блок освобождения заряда выполнен с возможностью записывать сигнал управления на третьей линии управления в затворную линию для пропускания тока через каждый пиксельный электрод и линию данных, соединенную с пиксельным электродом.

6. Схема освобождения заряда по п. 5, в которой вторая линия управления изолирована от третьей линии управления.

7. Схема освобождения заряда по п. 5 или 6, в которой третий блок освобождения заряда содержит множество третьих транзисторов, причем множество третьих транзисторов находится во взаимно-однозначном соответствии с множеством затворных линий в подложке матрицы, и второй проводник содержит множество пиксельных электродов, соединенных с каждой затворной линией, и третья линия управления перпендикулярна к затворной линии, и

причем оба затворный электрод и первый электрод каждого из множества третьих транзисторов соединены с третьей линией управления и второй электрод каждого из множества третьих транзисторов соединен с одной затворной линией во множестве затворных линий.

8. Схема освобождения заряда по любому из пп. 1-7, в которой объем первого проводника больше, чем у второго проводника.

9. Схема освобождения заряда по любому из пп. 1-8, в которой первый проводник является линией общего электрода или линией электрода хранения.

10. Подложка дисплея, содержащая схему освобождения заряда по любому из пп. 1-9.

11. Устройство отображения, содержащее отображающую панель, причем отображающая панель содержит подложку дисплея по п. 10.

12. Способ освобождения заряда устройства отображения по п. 11, содержащий этапы, на которых:

подают сигнал управления на контроллер, когда отображающая панель находится в состоянии черного экрана, пропускают ток через первый проводник и второй проводник под управлением контроллера и позволяют зарядам на втором проводнике переходить в первый проводник,

причем этап, на котором пропускают ток через первый проводник и второй проводник под управлением контроллера, содержит этап, на котором:

вводят сигнал управления во вторую линию управления и позволяют зарядам на по меньшей мере одной линии данных переходить в первый проводник.

13. Способ по п. 12, в котором первый проводник является линией общего электрода или линией электрода хранения и второй проводник является по меньшей мере одним из затворной линии, линии данных и пиксельным электродом.

14. Способ по п. 12 или 13, в котором объем первого проводника больше, чем у второго проводника.

| CN 204667021 U1, 29.03.2015 | |||

| CN 104297969 A, 21.01.2015 | |||

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| ПОДЛОЖКА С АКТИВНОЙ МАТРИЦЕЙ, СПОСОБ ИЗГОТОВЛЕНИЯ ПОДЛОЖКИ С АКТИВНОЙ МАТРИЦЕЙ, ЖИДКОКРИСТАЛЛИЧЕСКАЯ ПАНЕЛЬ, СПОСОБ ИЗГОТОВЛЕНИЯ ЖИДКОКРИСТАЛЛИЧЕСКОЙ ПАНЕЛИ, ЖИДКОКРИСТАЛЛИЧЕСКИЙ ДИСПЛЕЙ, БЛОК ЖИДКОКРИСТАЛЛИЧЕСКОГО ДИСПЛЕЯ И ТЕЛЕВИЗИОННЫЙ ПРИЕМНИК | 2009 |

|

RU2468403C1 |

Авторы

Даты

2020-09-28—Публикация

2017-11-08—Подача