ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННУЮ ЗАЯВКУ

По данной заявке испрашивается приоритет китайской патентной заявки CN201710364479.0 поданной 22 мая 2017 г., раскрытие которой, таким образом, включено посредством ссылки в полном объеме.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к области технологии дисплеев и, в частности, к защитной схеме, подложке матрицы и панели отображения.

УРОВЕНЬ ТЕХНИКИ

Когда панель отображения жидкокристаллического дисплея на тонкопленочных транзисторах (TFT-LCD) испытывает перебой в питании, поскольку электрические заряды на линиях данных своевременно не высвобождаются, в панели отображения с высокой степенью вероятности происходит накопление заряда, приводящее к мерцанию отключения. Когда электрические заряды внутри панели отображения накапливаются до определенной степени, происходит электростатический разряд между линиями данных, который может повреждать устройство тонкопленочного транзистора, что приводит к отказу функции отображения жидкокристаллической панели отображения.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Вариант осуществления настоящего изобретения предусматривает защитную схему, подложку матрицы и панель отображения.

Согласно аспекту вариантов осуществления настоящего изобретения, предусмотрена защитная схема для панели отображения, содержащая:

подсхему управления, имеющую первый конец, электрически подключенный к контакту ввода напряжения, и второй конец, выполненный с возможностью вывода сигнала общего напряжения, подаваемого с контакта ввода напряжения; и

разрядную подсхему, имеющую первый конец, электрически подключенный ко второму концу подсхемы управления, и второй конец, электрически подключенный к по меньшей мере одной линии данных;

причем разрядная подсхема высвобождает электрические заряды по по меньшей мере одной линии данных под управлением сигнала общего напряжения, подаваемого от подсхемы управления.

В одном варианте осуществления, подсхема управления дополнительно содержит: первый тонкопленочный транзистор и второй тонкопленочный транзистор; оба первый электрод и затворный электрод первого тонкопленочного транзистора электрически подключены к контакту ввода напряжения, и второй электрод первого тонкопленочного транзистора электрически подключен к первому электроду второго тонкопленочного транзистора; и второй электрод второго транзистора электрически подключен к первому электроду первого тонкопленочного транзистора, и оба первый электрод и затворный электрод второго тонкопленочного транзистора электрически подключены к линии выходного сигнала разрядной подсхемы.

В одном варианте осуществления, линия выходного сигнала содержит множество линий сигнала, соединенных параллельно друг с другом.

В одном варианте осуществления, разрядная подсхема содержит матрицу третьих тонкопленочных транзисторов, и каждый третий тонкопленочный транзистор имеет оба первый электрод и затворный электрод, электрически подключенные к линии сигнала, соответствующей ряду, в котором располагается третий тонкопленочный транзистор, из множества линий сигнала, и второй электрод, электрически подключенный к линии данных, соответствующей столбцу, в котором располагается третий тонкопленочный транзистор, из по меньшей мере одной линии данных.

В одном варианте осуществления, разрядная подсхема дополнительно содержит множество линий распределения заряда, соединенных параллельно друг с другом.

В одном варианте осуществления, разрядная подсхема содержит матрицу третьих тонкопленочных транзисторов, и каждый третий тонкопленочный транзистор имеет первый электрод, электрически подключенный к линии распределения заряда, соответствующей столбцу, в котором располагается третий тонкопленочный транзистор, из множества линий распределения заряда, второй электрод, электрически подключенный к линии данных, соответствующей столбцу, в котором располагается третий тонкопленочный транзистор, из по меньшей мере одной линии данных, и затворный электрод, электрически подключенный к линии сигнала, соответствующей ряду, в котором располагается третий тонкопленочный транзистор, из множества линий сигнала.

В одном варианте осуществления, разрядная подсхема содержит матрицу третьих тонкопленочных транзисторов, каждый третий тонкопленочный транзистор имеет первый электрод, электрически подключенный к линии данных, смежной с первым электродом, из по меньшей мере одной линии данных, второй электрод, электрически подключенный к линии данных, смежной со вторым электродом, из по меньшей мере одной линии данных, и затворный электрод, электрически подключенный к линии сигнала, соответствующей ряду, в котором располагается третий тонкопленочный транзистор, из множества линий сигнала.

В одном варианте осуществления, потенциал множества линий распределения заряда является плавающим потенциалом.

В одном варианте осуществления, первым тонкопленочным транзисторов является тонкопленочный транзистор n-типа или тонкопленочный транзистор p-типа, вторым тонкопленочным транзистором является тонкопленочный транзистор p-типа или тонкопленочный транзистор n-типа, и третьим тонкопленочным транзистором является тонкопленочный транзистор n-типа или тонкопленочный транзистор p-типа.

Согласно другому аспекту вариантов осуществления настоящего изобретения, предусмотрена подложка матрицы, содержащая вышеупомянутую защитную схему, которая обеспечена у контакта ввода сигнала линии сигнала подложки матрицы и/или с противоположной стороны контакта ввода сигнала линии сигнала.

Согласно еще одному аспекту вариантов осуществления настоящего изобретения, предусмотрена панель отображения, содержащая вышеупомянутую подложку матрицы.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Чтобы более наглядно проиллюстрировать технические решения согласно вариантам осуществления настоящего изобретения, чертежи вариантов осуществления будут кратко описаны ниже. Очевидно, что чертежи в нижеследующем описании относятся только к некоторым вариантам осуществления настоящего изобретения и не призваны ограничивать настоящее изобретение.

Фиг. 1 - схема, демонстрирующая структуру защитной схемы согласно варианту осуществления настоящего изобретения;

фиг. 2 - схема, демонстрирующая структуру защитной схемы согласно другому варианту осуществления настоящего изобретения;

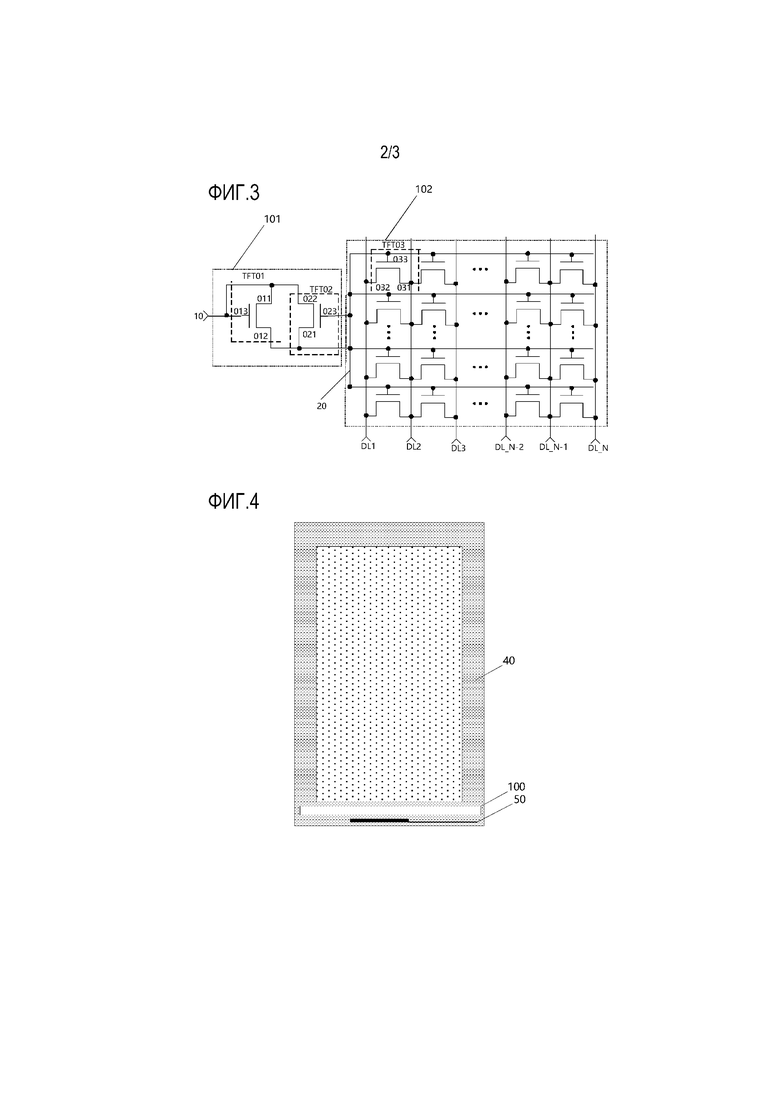

фиг. 3 - схема, демонстрирующая структуру защитной схемы согласно еще одному варианту осуществления настоящего изобретения;

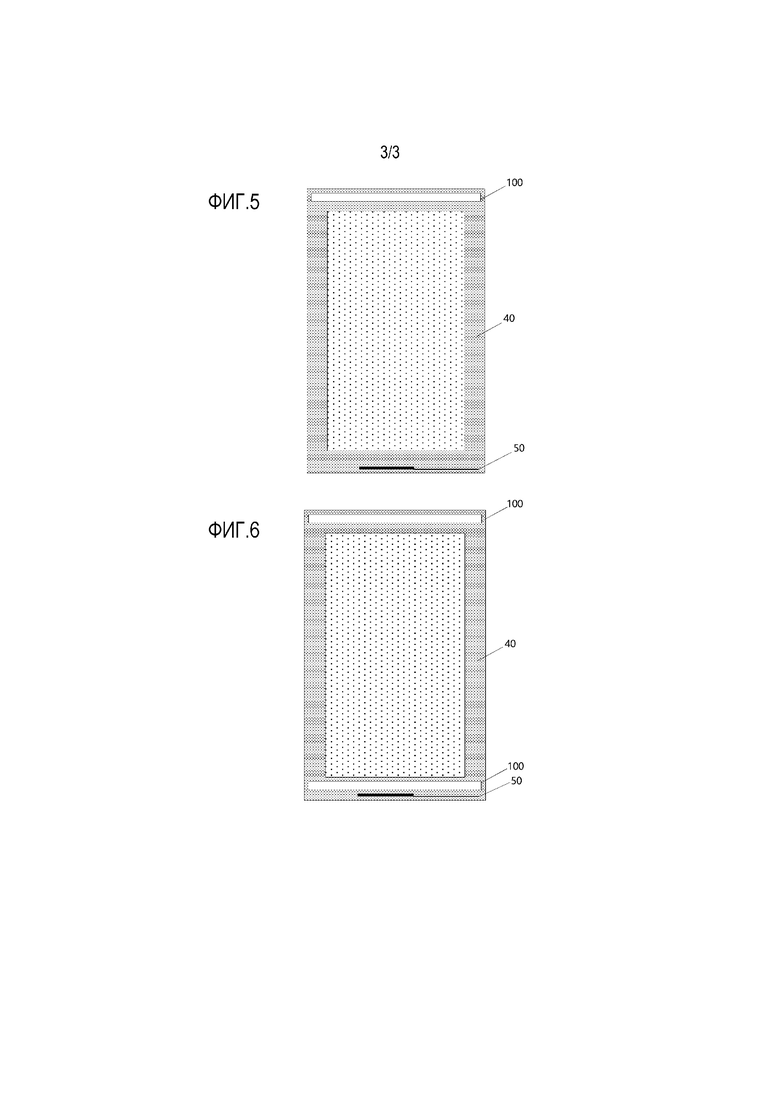

фиг. 4 - схема, демонстрирующая защитную схему, обеспеченную на контакте ввода сигнала линии данных, согласно варианту осуществления настоящего изобретения;

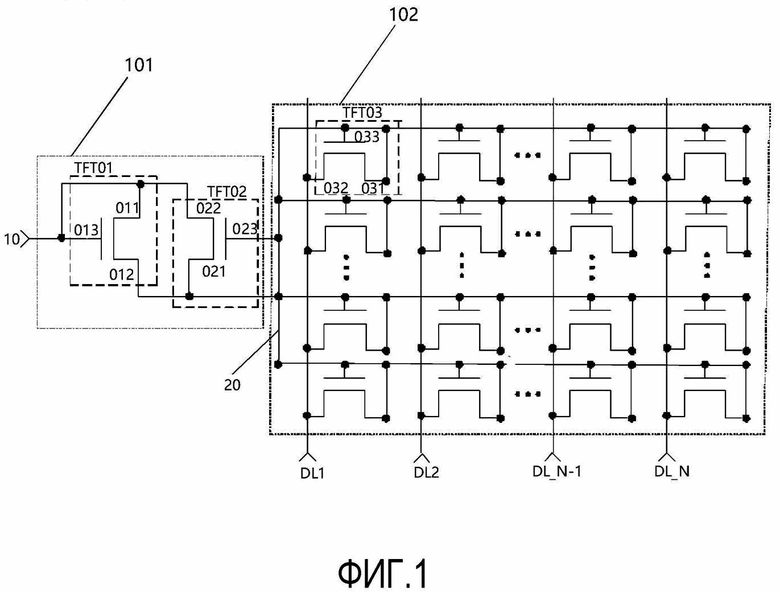

фиг. 5 - схема, демонстрирующая защитную схему, обеспеченную на противоположной стороне контакта ввода сигнала линии данных, согласно другому варианту осуществления настоящего изобретения;

фиг. 6 - схема, демонстрирующая защитные схемы, обеспеченные у контакта ввода сигнала линии данных и с противоположной стороны контакта ввода сигнала линии данных, согласно еще одному варианту осуществления настоящего изобретения;

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

Для пояснения задач, технических решений и преимуществ вариантов осуществления настоящего изобретения, технические решения согласно вариантам осуществления настоящего изобретения будут наглядно и полностью описаны ниже совместно с чертежами согласно вариантам осуществления настоящего изобретения. Очевидно, что описанные варианты осуществления являются некоторыми из вариантов осуществления настоящего изобретения, и не всеми вариантами осуществления. Все остальные варианты осуществления, полученные специалистами в данной области техники на основании описанных вариантов осуществления настоящего изобретения без применения творческих способностей, находятся в объеме настоящего изобретения.

Если не задано обратное, технические термины или научные термины, используемые в настоящем изобретении следует понимать в обычном значении, признанном специалистами в данной области техники. Слова "первый", "второй" и пр., используемые в настоящем изобретении, не обозначают какой-либо порядок, количество или важность, но используются для различения разных компонентов. Слово "содержащий" или "включающий в себя" и пр., следует понимать в том смысле, что элемент, который располагается до слова, включает в себя элемент(ы), перечисленные после слова и его эквивалентов, и не исключают другого(их) элемент(ов). Слово "подключенный к" или "соединенный с" и пр. не ограничиваются физическими или механическими соединениями, но могут включать в себя электрические соединения, прямые или косвенные. "Верхний", "нижний", "левый", "правый", и т.д. используются только для указания относительного позиционного соотношения, и когда абсолютная позиция объекта, подлежащего описанию, изменяется, относительное позиционное соотношение также может изменяться соответственно.

В настоящем изобретении, тонкопленочный транзистор (TFT) сокращенно обозначается как TFT. Соответственно, первый тонкопленочный транзистор сокращенно обозначается как TFT01, второй тонкопленочный транзистор сокращенно обозначается как TFT02, и третий тонкопленочный транзистор сокращенно обозначается как TFT03. Кроме того, в настоящем изобретении, истоковый электрод и стоковый электрод можно использовать взаимозаменяемо.

Согласно вариантам осуществления настоящего изобретения, предусмотрена защитная схема. Согласно фиг. 1, защитная схема включает в себя подсхему 101 управления и разрядную подсхему 102. Подсхема 101 управления включает в себя TFT01 и TFT02. Оба затворный электрод и истоковый электрод TFT01 электрически подключены к контакту 10 ввода напряжения, и контакт 10 ввода напряжения обеспечивает сигнал общего напряжения. Стоковый электрод TFT01 электрически подключен к истоковому электроду TFT02. Стоковый электрод TFT02 электрически подключен к истоковому электроду TFT01, и оба истоковый электрод и затворный электрод TFT02 электрически подключены к линии 20 выходного сигнала разрядной подсхемы 102. Линия 20 выходного сигнала разрядной подсхемы 102 включает в себя множество линий сигнала, соединенных параллельно друг с другом. TFT01 и TFT02 подсхемы 101 управления выполнены с возможностью вывода сигнала общего напряжения, подаваемого от контакта 10 ввода напряжения в линию 20 выходного сигнала разрядной подсхемы 102.

Разрядная подсхема 102 включает в себя матрицу TFT03, и количество столбцов TFT03 в матрице соответствует количеству линий данных. Стоковый электрод каждого TFT03 в каждом столбце TFT03 электрически подключен к линии данных, соответствующей столбцу, и оба истоковый электрод и затворный электрод TFT03 электрически подключены к линии 20 выходного сигнала разрядной подсхемы 102. TFT03 выполнен с возможностью разряда электрических зарядов на линии данных в линию 20 выходного сигнала разрядной подсхемы 102 под управлением сигнала общего напряжения, подаваемого из подсхемы 101 управления.

Подложка матрицы панели отображения может включать в себя базовую подложку, защитную схему, пиксельный блок и затворную линию и линию данных, сформированную на базовой подложке. Согласно вариантам осуществления настоящего изобретения, линия выходного сигнала разрядной подсхемы в защитной схеме установлена в том же слое, что и затворная линия, причем линия выходного сигнала включает в себя множество линий сигнала, соединенных параллельно друг с другом. Оба затворный электрод и истоковый электрод TFT02 подсхемы управления электрически подключены к линии выходного сигнала. Оба затворный электрод и истоковый электрод TFT03 разрядной подсхемы электрически подключены к линии сигнала, соответствующей ряду, в котором располагается TFT03, из множества линий сигнала, и стоковый электрод TFT03 электрически подключен к линии данных, соответствующей столбцу, в котором располагается TFT03, из линий данных.

Во время отключения питания панели отображения, контакт управления сигналом затворного электрода управляет отключением тонкопленочного транзистора пиксельного блока по затворной линии. В это время, электрические заряды на линии данных не высвобождаются своевременно, и происходит накопление заряда. Поскольку пиксельный блок не может немедленно прекратить работу, панель отображения имеет такие проблемы, как мерцание отключения, повреждение электростатическим разрядом и пр.

Согласно вариантам осуществления настоящего изобретения, оба затворный электрод и истоковый электрод TFT03 разрядной подсхемы 102 электрически подключены к контакту 10 ввода напряжения по линии 20 выходного сигнала разрядной подсхемы и через подсхему 101 управления, тогда как стоковый электрод TFT03 электрически подключен к линии данных. Линия 20 выходного сигнала разрядной подсхемы 102 и контакт 10 ввода напряжения сформированы на базовой подложке подложки матрицы. При условии, что используется защитная схема согласно вариантам осуществления настоящего изобретения, если накопление заряда происходит на линии данных во время отключения питания панели отображения, контакт 10 ввода напряжения обеспечивает сигнал общего напряжения, для включения TFT01 и TFT02 подсхемы 101 управления, и линия 20 выходного сигнала разрядной подсхемы 102 управляется для вывода сигнала общего напряжения, для включения TFT03 разрядной подсхемы 102, и электрические заряды на линии данных высвобождаются в линию 20 выходного сигнала разрядной подсхемы 102 через TFT03. Это позволяет избежать возникновения мерцания и повреждения электростатическим разрядом панели отображения, вследствие невозможности полного и быстрого высвобождения электрических зарядов на линии данных.

Согласно вариантам осуществления настоящего изобретения, TFT01, TFT02 и TFT03 может быть тонкопленочным транзистором n-типа или тонкопленочным транзистором p-типа. Если TFT01, TFT02 и TFT03 являются тонкопленочными транзисторами n-типа, TFT01, TFT02 и TFT03 включаются, когда контакт 10 ввода напряжения подает высокоуровневый сигнал общего напряжения. Если TFT01, TFT02 и TFT03 являются тонкопленочными транзисторами p-типа, TFT01, TFT02 и TFT03 включаются, когда контакт 10 ввода напряжения подает низкоуровневый сигнал общего напряжения.

Согласно вариантам осуществления настоящего изобретения, предусмотрена защитная схема. Согласно фиг. 2, защитная схема включает в себя подсхему 101 управления и разрядную подсхему 102. Подсхема 101 управления включает в себя TFT01 и TFT02. Оба затворный электрод и истоковый электрод TFT01 электрически подключены к контакту 10 ввода напряжения, и контакт 10 ввода напряжения обеспечивает сигнал общего напряжения. Стоковый электрод TFT01 электрически подключен к истоковому электроду TFT02. Стоковый электрод TFT02 электрически подключен к истоковому электроду TFT01, и оба стоковый электрод и затворный электрод TFT02 электрически подключены к линии 20 выходного сигнала разрядной подсхемы 102. Линия 20 выходного сигнала разрядной подсхемы 102 включает в себя множество линий сигнала, соединенных параллельно друг с другом. TFT01 и TFT02 выполнены с возможностью вывода сигнала общего напряжения в линию 20 выходного сигнала разрядной подсхемы 102 под управлением сигнала общего напряжения, подаваемого от контакта 10 ввода напряжения.

Разрядная подсхема 102 включает в себя матрицу TFT03, и количество столбцов TFT03 в матрице соответствует количеству линий данных. Стоковый электрод каждого TFT03 электрически подключен к линии данных, соответствующей столбцу, в котором располагается TFT, и затворный электрод TFT03 электрически подключен к линии 20 сигнала, соответствующей ряду, в котором располагается TFT03, из множества линий 20 сигнала. Разрядная подсхема 102 дополнительно включает в себя множество линий 30 распределения заряда, соединенных параллельно друг с другом, истоковый электрод каждого из TFT03 электрически подключен к линии 30 распределения заряда, соответствующей столбцу, в котором располагается TFT03, из линий 30 распределения заряда. TFT03 выполнены с возможностью разряда электрических зарядов на линии данных в линии 30 распределения заряда под управлением сигнала общего напряжения, выводимого подсхемой 101 управления.

Подложка матрицы панели отображения может включать в себя базовую подложку, защитную схему, пиксельный блок и затворную линию и линию данных, сформированную на базовой подложке. Согласно вариантам осуществления настоящего изобретения, линия 20 выходного сигнала разрядной подсхемы в защитной схеме установлена в том же слое, что и затворная линия, и линия 30 распределения заряда установлена в том же слое, что и линия данных. Линия 20 выходного сигнала включает в себя множество линий сигнала, соединенных параллельно друг с другом, и оба затворный электрод и истоковый электрод TFT02 подсхемы управления электрически подключены к линии выходного сигнала. Истоковый электрод TFT03 разрядной подсхемы электрически подключен к линии данных, затворный электрод TFT03 электрически подключен к линии сигнала, и стоковый электрод TFT03 электрически подключен к линии 30 распределения заряда.

Во время отключения питания панели отображения, контакт управления сигналом затворного электрода управляет отключением тонкопленочного транзистора пиксельного блока по затворной линии. В это время, электрические заряды на линии данных не высвобождаются своевременно, и происходит накопление заряда. Поскольку пиксельный блок не может немедленно прекратить работу, панель отображения имеет такие проблемы, как мерцание отключения, повреждение электростатическим разрядом и пр.

Согласно вариантам осуществления настоящего изобретения, затворный электрод TFT03 разрядной подсхемы 102 электрически подключен к контакту 10 ввода напряжения по линии 20 выходного сигнала разрядной подсхемы 102 и через подсхему 101 управления, и стоковый электрод TFT03 электрически подключен к линии данных, и истоковый электрод TFT03 электрически подключен к линии 30 распределения заряда. Линия 20 выходного сигнала и линия 30 распределения заряда разрядной подсхемы 102 и контакт 10 ввода напряжения сформированы на базовой подложке подложки матрицы. При условии, что используется защитная схема согласно вариантам осуществления настоящего изобретения, если накопление заряда происходит на линии данных во время отключения питания панели отображения, контакт 10 ввода напряжения обеспечивает сигнал общего напряжения, для включения TFT01 и TFT02 подсхемы 101 управления, и линия 20 выходного сигнала разрядной подсхемы 102 выводит сигнал общего напряжения, для включения TFT03 разрядной подсхемы 102, и электрические заряды на линии данных высвобождаются в линию 30 распределения заряда разрядной подсхемы 102 через TFT03. Это позволяет избежать возникновения мерцания и повреждения электростатическим разрядом панели отображения, вследствие невозможности полного и быстрого высвобождения электрических зарядов на линии данных.

Согласно варианту осуществления настоящего изобретения, TFT01, TFT02 и TFT03 может быть тонкопленочным транзистором n-типа или тонкопленочным транзистором p-типа. Если TFT01, TFT02 и TFT03 являются тонкопленочными транзисторами n-типа, TFT01, TFT02 и TFT03 включаются, когда контакт 10 ввода напряжения подает высокоуровневый сигнал общего напряжения. Если TFT01, TFT02 и TFT03 являются тонкопленочными транзисторами p-типа, TFT01, TFT02 и TFT03 включаются, когда контакт 10 ввода напряжения подает низкоуровневый сигнал общего напряжения.

Согласно вариантам осуществления настоящего изобретения, предусмотрена защитная схема. Согласно фиг. 3, защитная схема включает в себя подсхему 101 управления и разрядную подсхему 102. Подсхема 101 управления включает в себя TFT01 и TFT02. Оба затворный электрод и истоковый электрод TFT01 электрически подключены к контакту 10 ввода напряжения, и контакт 10 ввода напряжения обеспечивает сигнал общего напряжения. Стоковый электрод TFT01 электрически подключен к истоковому электроду TFT02. Стоковый электрод TFT02 электрически подключен к истоковому электроду TFT01. Оба истоковый электрод и затворный электрод TFT02 электрически подключены к линии 20 выходного сигнала разрядной подсхемы 102. Линия 20 выходного сигнала разрядной подсхемы 102 включает в себя множество линий сигнала, соединенных параллельно друг с другом. TFT01 и TFT02 выполнены с возможностью вывода сигнала общего напряжения в линию 20 выходного сигнала разрядной подсхемы 102 под управлением сигнала общего напряжения, подаваемого от контакта 10 ввода напряжения.

Разрядная подсхема 102 включает в себя матрицу TFT03, и количество столбцов TFT03 в матрице соответствует количеству линий данных. Оба истоковый электрод и стоковый электрод TFT03 электрически подключены к соседствующим с ними линиям данных, соответственно, и затворный электрод TFT03 электрически подключен к линии сигнала, соответствующей ряду, в котором располагается TFT03, из множества линий сигнала. TFT03 выполнен с возможностью нейтрализации положительные и отрицательные заряды на соседних линиях данных под управлением сигнала общего напряжения, выводимого подсхемой 101 управления.

Подложка матрицы панели отображения включает в себя базовую подложку, защитную схему, пиксельный блок и затворную линию и линию данных, сформированную на базовой подложке. Согласно вариантам осуществления настоящего изобретения, линия 20 выходного сигнала разрядной подсхемы в защитной схемы установлена в том же слое, что и затворная линия, причем линия 20 выходного сигнала включает в себя множество линий выходного сигнала, соединенных параллельно друг с другом. Оба затворный электрод и истоковый электрод TFT02 подсхемы управления в защитной схеме электрически подключены к линии выходного сигнала. Оба истоковый электрод и стоковый электрод TFT03 разрядной подсхемы электрически подключены к соседствующим с ними линиям данных, соответственно, и затворный электрод TFT03 электрически подключен к линии сигнала, соответствующей ряду, в котором располагается TFT03, из множества линий сигнала.

Во время отключения питания панели отображения, контакт управления сигналом затворного электрода управляет отключением тонкопленочного транзистора пиксельного блока по затворной линии. В это время, электрические заряды на линии данных не высвобождаются своевременно, и происходит накопление заряда. Поскольку пиксельный блок не может немедленно прекратить работу, панель отображения имеет такие проблемы, как мерцание отключения, повреждение электростатическим разрядом и пр.

Согласно варианту осуществления настоящего изобретения, затворный электрод TFT03 разрядной подсхемы 102 электрически подключен к контакту 10 ввода напряжения по линии 20 выходного сигнала разрядной подсхемы 102 и через подсхему 101 управления. Стоковый электрод и истоковый электрод TFT03 электрически подключены к соседствующим с ними линиям данных, соответственно. Линия 20 выходного сигнала разрядной подсхемы 102 и контакт 10 ввода напряжения сформированы на базовой подложке подложки матрицы. При условии, что защитная схема согласно варианту осуществления настоящего изобретения используется на подложке матрицы, если накопление заряда происходит на линии данных во время отключения питания панели отображения, контакт 10 ввода напряжения обеспечивает сигнал общего напряжения, для включения TFT01 и TFT02 подсхемы 101 управления, благодаря чему, линия 20 выходного сигнала разрядной подсхемы 102 выводит сигнал общего напряжения. Сигнал общего напряжения управляет включением TFT03 разрядной подсхемы 102, что позволяет нейтрализовать положительные и отрицательные заряды на соседних линиях данных. Это позволяет избежать возникновения мерцания и повреждения электростатическим разрядом панели отображения, вследствие невозможности полного и быстрого высвобождения электрических зарядов по линии данных.

Согласно вариантам осуществления настоящего изобретения, TFT01, TFT02 и TFT03 может быть тонкопленочным транзистором n-типа или тонкопленочным транзистором p-типа. Если TFT01, TFT02 и TFT03 являются тонкопленочными транзисторами n-типа, TFT01, TFT02 и TFT03 включаются, когда контакт 10 ввода напряжения подает высокоуровневый сигнал общего напряжения. Если TFT01, TFT02 и TFT03 являются тонкопленочными транзисторами p-типа, TFT01, TFT02 и TFT03 включаются, когда контакт 10 ввода напряжения подает низкоуровневый сигнал общего напряжения.

Согласно вариантам осуществления настоящего изобретения, предусмотрено панель отображения, которая включает в себя по меньшей мере одну из защитных схем согласно любому из вышеупомянутых вариантов осуществления.

В настоящем изобретении, защитная схема предусмотрена на подложке матрицы в жидкокристаллической панели отображения, например, структура защитной схемы такая, как показано на фиг. 1 - фиг. 3. Согласно фиг. 4, защитная схема 100 может быть обеспечена у контакта ввода сигнала линии данных микросхемы 50 возбуждения линии данных в подложке 40 матрицы жидкокристаллической панели отображения. Согласно фиг. 5, защитная схема 100 также может располагаться с противоположной стороны контакта ввода сигнала микросхемы 50 возбуждения линии данных в подложке 40 матрицы жидкокристаллической панели отображения. Согласно фиг. 6, защитная схема 100 также может располагаться как у контакта ввода сигнала линии данных, так и с противоположной стороны контакта ввода сигнала линии данных микросхемы 50 возбуждения линии данных в подложке 40 матрицы жидкокристаллической панели отображения.

Порядковый номер вышеописанных вариантов осуществления настоящего изобретения используется только в целях описания и не представляет достоинства и недостатки вариантов осуществления.

Вышеприведенное описание является только некоторыми вариантами осуществления настоящего изобретения и не призвано ограничивать настоящее изобретение. Любые модификации, эквивалентные замены, усовершенствования и т.д. в сущности и принципах настоящего изобретения подлежат включению в объем защиты настоящего изобретения.

Изобретение относится к области технологии дисплеев. Технический результат заключается в предотвращении отказа функции отображения жидкокристаллической панели отображения. Предусмотрены защитная схема, подложка матрицы и панель отображения. Защитная схема включает в себя: подсхему управления, имеющую первый конец, электрически подключенный к контакту ввода напряжения, и второй конец, выполненный с возможностью вывода сигнала общего напряжения, подаваемого с контакта ввода напряжения; и разрядную подсхему, имеющую первый конец, электрически подключенный ко второму концу подсхемы управления, и второй конец, электрически подключенный к по меньшей мере одной линии данных. Разрядная подсхема высвобождает электрические заряды по меньшей мере одной линии данных под управлением сигнала общего напряжения, подаваемого от подсхемы управления. 3 н. и 8 з.п. ф-лы, 6 ил.

1. Защитная схема для панели отображения, содержащая:

подсхему управления, имеющую первый конец, электрически подключенный к контакту ввода напряжения, и второй конец, выполненный с возможностью вывода сигнала общего напряжения, подаваемого с контакта ввода напряжения; и

разрядную подсхему, имеющую первый конец, электрически подключенный ко второму концу подсхемы управления, и второй конец, электрически подключенный к по меньшей мере одной линии данных;

причем разрядная подсхема высвобождает электрические заряды по по меньшей мере одной линии данных под управлением сигнала общего напряжения, подаваемого из подсхемы управления.

2. Защитная схема по п. 1, в которой подсхема управления дополнительно содержит:

первый тонкопленочный транзистор и второй тонкопленочный транзистор;

причем оба первый электрод и затворный электрод первого тонкопленочного транзистора электрически подключены к контакту ввода напряжения, и второй электрод первого тонкопленочного транзистора электрически подключен к первому электроду второго тонкопленочного транзистора; и

второй электрод второго тонкопленочного транзистора электрически подключен к первому электроду первого тонкопленочного транзистора, и оба первый электрод и затворный электрод второго тонкопленочного транзистора электрически подключены к линии выходного сигнала разрядной подсхемы.

3. Защитная схема по п. 1, в которой линия выходного сигнала содержит множество линий сигнала, соединенных параллельно друг с другом.

4. Защитная схема по п. 3, в которой разрядная подсхема содержит матрицу третьих тонкопленочных транзисторов, и каждый третий тонкопленочный транзистор имеет оба первый электрод и затворный электрод, электрически подключенные к линии сигнала, соответствующей ряду, в котором расположен третий тонкопленочный транзистор, из множества линий сигнала, и второй электрод, электрически подключенный к линии данных, соответствующей столбцу, в котором располагается третий тонкопленочный транзистор, из по меньшей мере одной линии данных.

5. Защитная схема по п. 3, в которой разрядная подсхема дополнительно содержит множество линий распределения заряда, соединенных параллельно друг с другом.

6. Защитная схема по п. 5, в которой разрядная подсхема содержит матрицу третьих тонкопленочных транзисторов, и каждый третий тонкопленочный транзистор имеет первый электрод, электрически подключенный к линии распределения заряда, соответствующей столбцу, в котором располагается третий тонкопленочный транзистор, из множества линий распределения заряда, второй электрод, электрически подключенный к линии данных, соответствующей столбцу, в котором располагается третий тонкопленочный транзистор, из по меньшей мере одной линии данных, и затворный электрод, электрически подключенный к линии сигнала, соответствующей ряду, в котором располагается третий тонкопленочный транзистор, из множества линий сигнала.

7. Защитная схема по п. 3, в которой разрядная подсхема содержит матрицу третьих тонкопленочных транзисторов, каждый третий тонкопленочный транзистор имеет первый электрод, электрически подключенный к линии данных, смежной с первым электродом, из по меньшей мере одной линии данных, второй электрод, электрически подключенный к линии данных, смежной со вторым электродом, из по меньшей мере одной линии данных, и затворный электрод, электрически подключенный к линии сигнала, соответствующей ряду, в котором располагается третий тонкопленочный транзистор, из множества линий сигнала.

8. Защитная схема по п. 5, в которой потенциал множества линий распределения заряда является плавающим потенциалом.

9. Защитная схема по любому из пп. 1-7, в которой первым тонкопленочным транзистором является тонкопленочный транзистор n-типа или тонкопленочный транзистор p-типа, вторым тонкопленочным транзистором является тонкопленочный транзистор p-типа или тонкопленочный транзистор n-типа, и третьим тонкопленочным транзистором является тонкопленочный транзистор n-типа или тонкопленочный транзистор p-типа.

10. Подложка матрицы, содержащая защитную схему по любому из пп. 1-9, которая обеспечена у контакта ввода сигнала линии сигнала подложки матрицы и/или противоположной стороны контакта ввода сигнала линии сигнала.

11. Панель отображения, содержащая подложку матрицы по п. 10.

| CN 102592552 A, 18.07.2012 | |||

| CN 103345898 A, 09.10.2013 | |||

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| CN 106356033 A, 25.01.2017 | |||

| RU 2011129667 A, 27.01.2013. | |||

Авторы

Даты

2020-09-08—Публикация

2017-11-23—Подача