Изобретение относится к испытательной технике и может быть использовано для диагностики функционирования микросхем оперативной памяти во всех отраслях микроэлектроники и радиотехники.

Актуальность проверки электронных компонентов не только сохраняется, но и даже увеличивается в связи с появлением многочисленных подделок на рынке, возникновением новых типов микросхем и увеличением степени интеграции. Острой в последние годы стала проблема испытания интегральных схем оперативной памяти. Алгоритмы функционального контроля микросхем ОЗУ разработаны достаточно давно (см. Л7 - Л15), но они не удовлетворяют современным потребностям, так как требуется минимум 2^n обращений к ячейкам памяти, где n - число бит. В этом случае проверка одной микросхемы ОЗУ емкостью 8×1024К (1 Мб) при времени доступа 40 нс занимает 19 часов, а испытание ОЗУ емкостью 1 Гб с аналогичными параметрами займет несколько лет! При этом проверять требуется большие партии микросхем за одну-две недели. Другой проблемой является оборудование для функциональной проверки микросхем ОЗУ. В наши дни есть достаточно много тестеров цифровых микросхем, предусматривающих функциональный и параметрический контроль (см. Л1-Л6).

Известные из уровня техники тестерные системы (Л1-Л6) обладают рядом недостатков применительно к функциональному контролю микросхем ОЗУ.

Первый заключается в том, что необходимо формировать файл функционального контроля в виде последовательности векторов, определяющих или контролирующих состояние на каждом выводе микросхемы, что делает написание программы очень длительным процессом, особенно при использовании современных алгоритмов. Часто просто не хватает памяти у тестерной системы для желаемой длины последовательности векторов.

Второй заключается в невозможности проведения испытаний на максимальной рабочей частоте микросхемы для многих тестерных систем.

Другая, не менее важная проблема, это слишком высокая стоимость такого оборудования, поэтому задействовать его на длительный период для проверки нескольких микросхем оперативной памяти экономически не выгодно.

Так возникла задача создания дешевой системы тестирования микросхем ОЗУ, в которой уже заложены быстрые алгоритмы поиска неисправностей, и не требуется каждый раз писать сложную программу для каждого типа микросхем памяти или составлять последовательность векторов.

Техническим результатом заявленного изобретения является увеличение функциональных возможностей, возможность быстро и непрерывно осуществлять полный функциональный контроль микросхем большой емкости, возможность проверки нескольких ОЗУ одновременно, сокращение времени испытаний, а также удешевление самой конструкции и снижение энергопотребления.

Технический результат заявленного изобретения достигается тем, что система функционального тестирования корпусированных микросхем оперативно запоминающих устройств большой емкости содержит микроконтроллер с встроенной flash памятью и с двумя аналогово-цифровыми преобразователями (АЦП), преобразователь интерфейса USB в UART, генератор на 100 МГц, датчик температуры микроконтроллера, источники питания на 1,7 Вольт, 2,5 Вольт, 3,3 Вольт, 5,0 Вольт, блок выбора источника питания, блок измерения тока потребления, блок проверки контактирования выводов тестируемых микросхем ОЗУ, преобразователь уровня напряжения управляющих входов тестируемых микросхем ОЗУ, преобразователь уровня напряжения шины адреса тестируемых микросхем ОЗУ, персональный компьютер (ПК), блок питания, драйвер, компаратор, нагрузка для каждой из n линий шины данных тестируемых микросхем ОЗУ, где n - целое число больше 1, m цифровых датчиков температуры микросхем ОЗУ, закрепленных на корпусе тестируемых микросхем ОЗУ, где m - целое число больше 1, при этом ПК посредством USB интерфейса через преобразователь интерфейса USB в UART соединен с микроконтроллером, два вывода микроконтроллера соединены с двумя управляющими входами блока выбора источника питания, который на основании соответствующих управляющих сигналов подключает требуемый источник питания на 1,7 Вольт, или 2,5 Вольт, или 3,3 Вольт, или 5,0 Вольт соответственно, восемнадцать выводов микроконтроллера соединены с восемнадцатью входами блока проверки контактирования выводов тестируемых микросхем ОЗУ, который отключает напряжение питание от тестируемых микросхем ОЗУ и подает напряжение питание на общий вывод тестируемых микросхем ОЗУ, другие восемнадцать выводов микроконтроллера соединены с восемнадцатью входами преобразователя уровня напряжения управляющих входов тестируемых микросхем ОЗУ, двадцать четыре вывода микроконтроллера соединены с двадцатью четырьмя входами преобразователя уровня напряжения шины адреса тестируемых микросхем ОЗУ, цифровые датчики температуры тестируемых микросхем ОЗУ, закрепленные на корпусе микросхем ОЗУ, посредством I2C интерфейса соединены с первым входом микроконтроллера, второй вход микроконтроллера соединен с выходом датчика температуры, третий вход микроконтроллера соединен с выходом генератора на 100 МГц, первый выход блока измерения тока потребления соединен с первым АЦП микроконтроллера, второй выход блока измерения тока потребления соединен со вторым входом блока проверки контактирования выводов тестируемых микросхем ОЗУ, выход блока выбора источника питания соединен с входом блока измерения тока потребления, выход блока проверки контактирования выводов тестируемых микросхем ОЗУ соединен с входом второго АЦП микроконтроллера, драйвер, компаратор, нагрузка для каждой линии шины данных тестируемых микросхем ОЗУ соединены посредством LVDS интерфейсов с четвертым, пятым и шестым входом микроконтроллера соответственно, блок питания соединен со всеми элементами системы.

Следует отметить, что в процессе разработки были дополнительно заложены следующие конструктивные операции:

- контроль контактирования всех выводов тестируемых микросхем;

- измерение потребляемого тока;

- возможность выбора напряжения питания (1,7 В, 2,5 В, 3,3 В, 5 В);

- возможность устанавливать напряжения высокого и низкого уровня на выходе драйверов (в диапазоне от -1 В до 7 В);

- возможность устанавливать диапазоны высокого и низкого уровня у компараторов (в диапазоне от -1 В до 7 В);

- возможность устанавливать ток нагрузки (до 50 мА на один вывод микросхемы);

- контроль температуры на корпусе каждой тестируемой микросхемы;

- подключение к ПК посредством USB интерфейса;

- возможность выбора частоты, на которой производится тестирование (до 100 МГц (200 Мбит));

- ведение базы данных с результатами проведенных измерений;

- возможность выбора одного или нескольких алгоритмов тестирования;

- возможность параллельной проверки 20 микросхем.

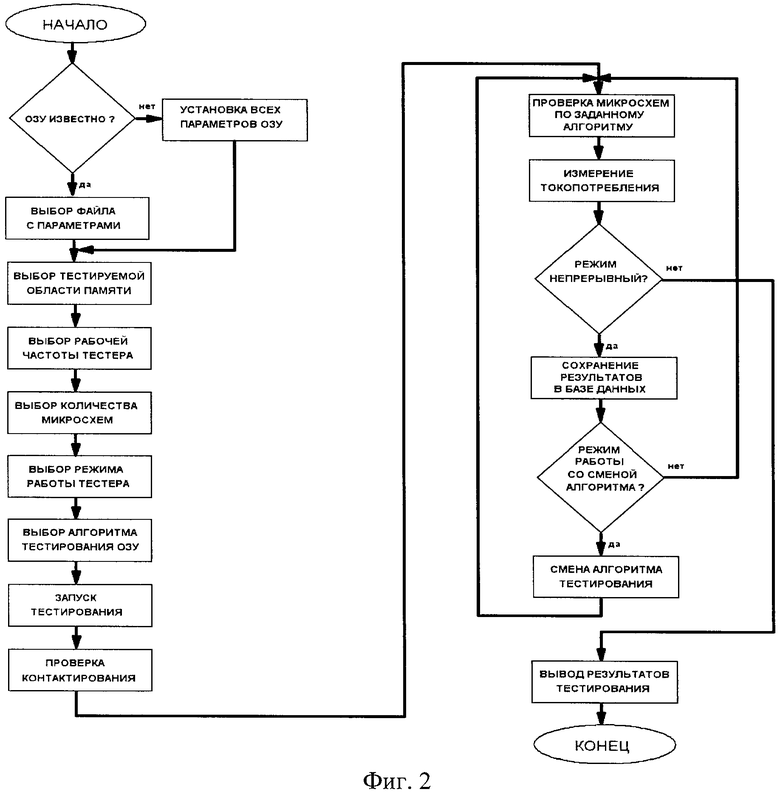

На фиг.1 представлена структурная схема системы функционального тестирования корпусированных микросхем ОЗУ, в состав которой входят:

1 - персональный компьютер (ПК);

2 - блок питания;

3 - преобразователь интерфейса USB в UART;

4 - источник питания на 5,0 Вольт;

5 - источник питания на 3,3 Вольт;

6 - источник питания на 2,5 Вольт;

7 - источник питания на 1,7 Вольт;

8 - блок выбора источника питания;

9 - генератор на 100 МГц;

10 - датчик температуры микроконтроллера;

11 - микроконтроллер с встроенной flash памятью и с двумя аналогово-цифровыми преобразователями (АЦП);

12 - блок измерения тока потребления;

13, 14, 15 - драйвер, компаратор, нагрузка для каждой из n линий шины данных тестируемых микросхем ОЗУ, где n - целое число больше 1;

16 - преобразователь уровня напряжения управляющих входов тестируемых микросхем ОЗУ;

17 - преобразователь уровня напряжения шины адреса тестируемых микросхем ОЗУ;

18 - блок проверки контактирования выводов тестируемых микросхем ОЗУ;

19 - m цифровых датчиков температуры микросхем ОЗУ, закрепленных на корпусе тестируемых микросхем ОЗУ, где m - целое число больше 1;

20 - шина данных микросхем ОЗУ;

21 - шина адреса микросхем ОЗУ;

22 - управляющие входы микросхем ОЗУ;

23 - питание микросхем ОЗУ.

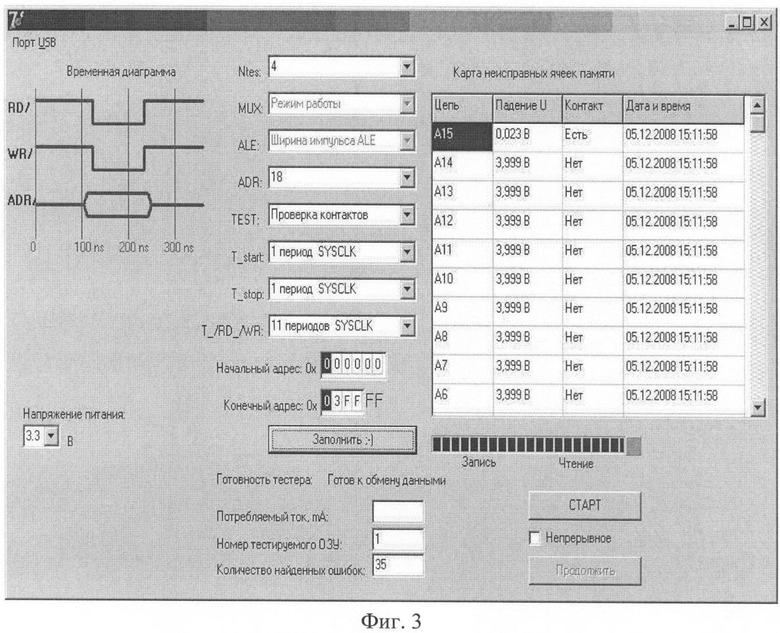

На фиг.2 представлена блок-схема программного обеспечения.

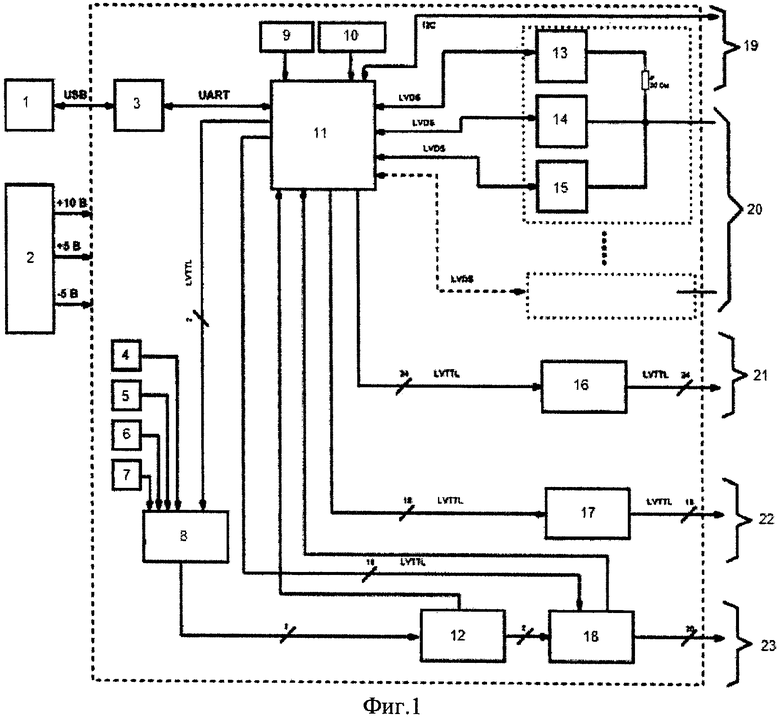

На фиг.3 представлен интерфейс программного обеспечения.

Принцип работы тестера заключается в следующем.

С персонального компьютера поступают сигналы по интерфейсу USB, содержащие информацию обо всех параметрах тестируемой микросхемы ОЗУ, а также обо всех условиях проводимого тестирования и выбранном алгоритме. Через преобразователь интерфейса USB в UART данная информация по интерфейсу UART попадает в микроконтроллер, который обрабатывает ее и подает управляющие сигналы на блок выбора источника питания, на основании которых происходит подключение требуемого источника к испытуемой микросхеме ОЗУ. Микроконтроллер подает сигналы на преобразователи уровня напряжений и драйверы, которые определяют уровни логической «1» и логического «0» на управляющих входах и шине адреса испытуемой микросхемы ОЗУ. Также микроконтроллер осуществляет деление частоты для достижения требуемых временных параметров, формирует управляющие сигналы для компаратора и нагрузки, устанавливающие требуемые барьеры компарирования и нагрузочные токи высокого и низкого уровня для выходов шины данных испытуемой микросхемы ОЗУ.

После выполнения подготовительных действий, приведенных выше, микроконтроллер подает сигналы на блок проверки контактирования, который отключает напряжение питания от испытуемой микросхемы ОЗУ и подает напряжение питания на общий вывод испытуемой микросхемы.

Микроконтроллером контролируется контактирование всех выводов микросхемы ОЗУ. После проверки контактирования микроконтроллер посредством UART интерфейса отправляет сигналы на персональный компьютер, проходящие через преобразователь USB-UART, содержащие информацию о неисправных контактах. Если проверка контактирования прошла успешно, то персональный компьютер отправляет сигналы по USB интерфейсу, проходящие через преобразователь USB-UART на микроконтроллер и содержащие информацию о выбранном оператором алгоритме функционального тестирования и временных характеристиках. После поступления сигналов на микроконтроллер начинается выполнение функционального тестирования, в процессе которого микроконтроллером формируются испытательные воздействия с соответствующими алгоритму временными задержками, поступающие на испытуемую микросхему ОЗУ через преобразователи уровня напряжений и драйверы с соответствующими логическими уровнями. Результаты проводимого функционального контроля получает микроконтроллер через компараторы при подключенной нагрузке.

После функционального контроля каждых 256 адресов с соответствующим числом ячеек памяти микроконтроллер отправляет на персональный компьютер сигналы посредством UART интерфейса, проходящие на персональный компьютер через преобразователь USB-UART, содержащие отчет о количестве и типе выявленных неисправностей функционирования испытуемой микросхемы ОЗУ. Результаты проведенных испытаний отправляются на ПК и хранятся в базе данных, а графический интерфейс позволяет наглядно выводить эти результаты.

Во flash память микроконтроллера (МК) загружена программа, содержащая готовые алгоритмы испытания микросхем оперативной памяти (см., например, Л16-Л18), а также всевозможные интерфейсы и ключевые флаги, необходимые для работы с периферийными устройствами.

После подачи напряжения питания на тестер супервизором формируется сигнал сброса и происходит запуск программы из flash памяти микроконтроллера. Согласно программе выполняется инициализация портов и интерфейсов микроконтроллера. После программа выходит в цикл ожидания команды с UART интерфейса. Запускается программа на ПК для работы с данным тестером, которая посылает запрос через USB о готовности тестера к работе. Данный запрос преобразуется интерфейсным микроконтроллером USB-UART в запрос на UART интерфейс МК, который в свою очередь дает ответ о готовности к работе. После подтверждения исправности тестера в программном обеспечении (ПО) требуется задать все основные параметры испытуемой микросхемы памяти:

- Разрядность шины данных.

- Разрядность шины адреса.

- Мультиплексированный или немультиплексированный режим.

- Напряжение питания.

- Уровни напряжений логических «0» и «1», передаваемых с тестера.

- Уровни компараторов, принимающих сигналы с испытуемой микросхемы.

- Нагрузка, подключаемая параллельно компараторам, для «0» и «1», передаваемых с испытуемой микросхемы.

- Всевозможные временные параметры (время доступа, задержка между сигналами обращения и т.д.).

- Частота, на которой проводятся испытания.

- Тестируемая область памяти.

- Алгоритм функционального тестирования.

Все указанные выше данные, необходимые для корректной работы тестера с данной микросхемой памяти, записываются в регистры микроконтроллера и автоматически извлекаются им в ходе выполнения программы. Сразу подключается необходимый источник питания, настройки драйверов, компараторов и нагрузки активируют соответствующие режимы СБИС, контролирующих выводы шины данных. Настройки для конкретного типа микросхем ОЗУ можно сохранить в виде файла и извлекать по мере необходимости.

После ввода всех параметров тестер автоматически приступает к контролю контактирования выводов микросхемы, так как плохой контакт может привести к выявлению несуществующей неисправности. Также контролируется контактирование выводов питания, что отличает его от многих функциональных тестеров. При отсутствии контакта в цепи питания микросхема на КМОП структурах продолжает функционировать, питаясь через входы-выходы, но показывает заниженные временные и нагрузочные характеристики. Результаты проверки контактирования отображаются в виде таблицы в ПО. Если контроль проведен успешно, то оператор выбирает нужный алгоритм тестирования и нажимает кнопку «Пуск». Микроконтроллер (МК), получив команду на испытание, активирует подпрограмму данного функционального контроля и передает сигналы на шину данных посредством LVDS интерфейса. На остальные шины и входы испытуемой микросхемы сигналы передаются LVTTL уровнями с портов МК через преобразователи уровня, делающих логическую «1», пропорциональную напряжению питания микросхемы ОЗУ. В ПО отражается процент оставшегося времени испытания, отражаются найденные неисправности в табличной форме, индицируется ток потребления испытуемой микросхемы и ее температура. Ток потребления измеряется токовым датчиком в цепи питания, а результат получается посредством измерения падения напряжения на датчике, встроенном в МК АЦП. Температура измеряется цифровыми датчиками, закрепляемыми на корпусе микросхемы и передающими результат измерения на МК посредством I2C интерфейса. После выполнения испытания ПО выдает окно с результатами, а тестер выходит в режим ожидания команды от ПК. Для проведения испытаний электротермотренировки и безотказности предусмотрена возможность непрерывного функционального контроля микросхемы ОЗУ с автоматическим перебором алгоритмов испытания. На ПК сохраняется база данных с измерениями тока потребления микросхемы памяти и ее температуры, а также найденными ошибками. Драйвер может формировать сигнал и переходить в состояние с частотой 100 МГц при амплитуде до 7В.

При использовании тестера не требуется составлять программу, формирующую сигналы и контролирующую выводы испытуемой микросхемы, а алгоритмы тестирования уже заложены в программу микроконтроллера и требуется только задать параметры микросхемы. Также осуществляется контроль контактирования всех выводов микросхемы памяти, а в процессе испытания измеряется ток потребления и температура испытуемой микросхемы. Интерфейс ПО для работы с тестером позволяет оператору запустить испытание нового типа микросхем памяти за несколько минут, установив параметры согласно ТУ на данный тип ОЗУ.

В отличие от большинства тестерных систем была введена проверка контактирования выводов питания, так как МОП структуры могут функционировать, питаясь через входы/выходы, но демонстрируют при этом низкие временные характеристики и плохие нагрузочные способности.

Основными задачами при разработке интерфейса программы (фиг.3) были обеспечение максимальной простоты и наглядности для оператора, обработка всех возможных исключений во избежание зависаний или ошибок программы, сохранение всех результатов в файлах базы данных с указанием точного времени, даты и условий, при которых произошло измерение, возможность автоматического составления отчета о проведенных испытаниях и измерениях в формате Excel. Сначала программа предлагает выбрать напряжение питания микросхемы оперативной памяти, адресное пространство, проверяемую область, время доступа к ячейке памяти и некоторые задержки, мультиплексирование шины данных, количество проверяемых микросхем и алгоритм тестирования. Выпадающие меню позволяют быстро выбрать нужные значения, а временная диаграмма наглядно отображает выбранные вами значения в реальном времени. Предусмотрена возможность сохранения всех настроек в файле для определенного типа памяти, чтобы в дальнейшем при проверке таких же микросхем просто загрузить файл настроек.

Если в процессе выполнения тестовой программы при функциональном контроле обнаруживается более 256 неисправностей, то программа приостанавливает работу и спрашивает о целесообразности дальнейшей проверки такой микросхемы. Предусмотрена в интерфейсе и галочка «непрерывно», необходимая для проведения испытаний на безотказность, когда ОЗУ находится в климатической камере при +100°С и относительной влажности воздуха 98%, и непрерывно осуществляется контроль функционирования и измерение параметров в течение 300 часов.

Заявленный тестер позволяет быстро осуществлять полный функциональный контроль новых микросхем ОЗУ большой емкости. Для удешевления конструкции, снижения энергопотребления и уменьшения габаритов прибора микросхемы драйвер, компаратор и нагрузка использовались для обслуживания только выводы шины данных испытуемой микросхемы, так как остальные выводы являются только входами, и для них установлены только преобразователи уровня.

Это сильно отличает данный тестер от приведенных выше аналогов, так как у него нет возможности опрашивать и нагружать любой вывод микросхемы, но зато обработка результатов компараторов и программируемые нагрузки выводов шины данных возможны в процессе функционального контроля на максимальной частоте, что позволяет оценить не только статические параметры микросхемы ОЗУ, но и динамические.

Проведенные испытания показали удобство и быстроту функционального тестера ОЗУ, а так же подтвердили его возможность по обнаружению ошибок с помощью быстрых алгоритмов поиска.

Источники информации

1. «Formula 2К» фирмы «Форм», Россия (www.form.ru) - (Л1).

2. «Integra J750» фирмы «Teradyne», США (www.integra-tech.com) -(Л2).

3. «MicroATE Semicon Tester» фирмы «Qmax Test Equipments», США (www.qmaxtest.com) - (Л3).

4. «S680» фирмы «Keithley», США (www.keithley.com) - (Л4).

5. «ВТЦМ-32» фирмы Трейлер, Россия (www.stanok.cncinfo.ru) - (Л5).

6. «Волна» фирмы «ЦНИИИА», Россия (www.cime.ru) - (Л6).

7. Техника оптимизации программ. Эффективное использование памяти //Касперски К., BHV, 2003 - (Л7).

8. VLSI test: memory test // Agrawal&Bushnell, 2005 - (Л8).

9. Functional RAM testing // Cristian Landrault, 2006 - (Л9).

10. Fault coverage analysis of RAM test algorithms // Marc Riedel, McGill University, Montreal, Canada, 2006 - (Л10).

11. Transistor-Level Fault Analysis and Test Algorithm Development for Ternary Dynamic Content Addressable Memories // Derek Wright and Manoj Sachdev, Dept. of Electrical & Computer Engineering, University of Waterloo, Waterloo, Ontario, Canada, 2008 - (Л11).

12. An Efficient Built-in Self-Test Algorithm Neighborhood Pattern and Bit-Line-Sensitive Faults in High-Density Memories // Dong-Chual Kang, Sung Min Park, and Sang-Bock Cho, ETRI Journal, Volume 26, Number 6, December 2004 - (Л12).

13. Manifestation of Precharge Faults in High Speed DRAM Devices // Delft University of Technology, Faculty of ЕЕ, Mathematics and CS Laboratory of Computer Engineering, Mekelweg 4, 2628 CD Delft, The Netherlands, 2005 - (Л13).

14. Efficient Neighborhood Pattern-Sensitive Fault Test Algorithm for Semiconductor Memories // Kuo-Liang Cheng, Ming-Fu Tsai and Cheng-Wen Wu, LARC NTHU, 2004 - (Л14).

15. Design of a LOW Cost IC Tester // American Journal of Applied Sciences 2(4), 2005 - (Л15).

16. Fault coverage analysis of RAM test algorithms // Marc Riedel, McGill University, Montreal, Canada, 2006 - (Л16).

17. An Efficient Built-in Self-Test Algorithm Neighborhood Pattern-and Bit-Line-Sensitive Faults in High-Density Memories // Dong-Chual Kang, Sung Min Park, and Sang-Bock Cho, ETRI Journal, Volume 26, Number 6, December 2004 - (Л17).

18. Transistor-Level Fault Analysis and Test Algorithm Development for Ternary Dynamic Content Addressable Memories // Derek Wright and Manoj Sachdev, Dept. of Electrical & Computer Engineering, University of Waterloo, Waterloo, Ontario, Canada, 2008 (Л18).

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ тестирования микросхем энергонезависимой памяти и устройство для его осуществления | 2023 |

|

RU2821349C1 |

| СИСТЕМА ФУНКЦИОНАЛЬНОГО ТЕСТИРОВАНИЯ КАРТ ПОЛУПРОВОДНИКОВОЙ ПАМЯТИ | 2012 |

|

RU2524858C2 |

| КОНТРОЛЛЕР УПРАВЛЕНИЯ И МОНИТОРИНГА | 2018 |

|

RU2699064C1 |

| ТЕСТЕР-ВЕРИФИКАТОР ЗАКАЗНЫХ СБИС | 2021 |

|

RU2777449C1 |

| Способ локализации дефектов короткого замыкания выводов микросхем JTAG интерфейсом и устройство для его осуществления | 2018 |

|

RU2703493C1 |

| Метод приема синхронных данных старт-стопным интерфейсом | 2020 |

|

RU2733923C1 |

| Плата-переходник для установки в базовые устройства с процессорным модулем форм-фактора COM EXPRESS | 2024 |

|

RU2838350C1 |

| Способ потактового управления несколькими шаговыми двигателями с помощью персонального компьютера по каналу USB и устройство для его осуществления | 2018 |

|

RU2704486C1 |

| ПЕРЕНОСНОЙ ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2015 |

|

RU2612072C1 |

| Устройство для проверки спутниковой антенны комплекса КЛУБ-У | 2024 |

|

RU2828299C1 |

Изобретение относится к испытательной технике и может быть использовано для диагностики функционирования микросхем оперативной памяти во всех отраслях микроэлектроники и радиотехники. Техническим результатом является осуществление полного функционального контроля микросхем большой емкости, возможность проверки нескольких ОЗУ одновременно, сокращение времени испытаний, а также удешевление самой конструкции и снижение энергопотребления. Система содержит микроконтроллер с встроенной flash памятью и с двумя аналогово-цифровыми преобразователями (АЦП), преобразователь интерфейса USB в UART, генератор на 100 МГц, датчик температуры микроконтроллера, источники питания на 1,7 Вольт, 2,5 Вольт, 3,3 Вольт, 5,0 Вольт, блок выбора источника питания, блок измерения тока потребления, блок проверки контактирования выводов тестируемых микросхем ОЗУ, преобразователь уровня напряжения управляющих входов тестируемых микросхем ОЗУ, преобразователь уровня напряжения шины адреса тестируемых микросхем ОЗУ, персональный компьютер (ПК), блок питания, драйвер, компаратор, нагрузку для каждой из n линий шины данных тестируемых микросхем ОЗУ, m цифровых датчиков температуры микросхем ОЗУ, закрепленных на корпусе тестируемых микросхем ОЗУ. 3 ил.

Система функционального тестирования корпусированных микросхем оперативно запоминающих устройств большой емкости содержит: микроконтроллер с встроенной flash памятью и с двумя аналогово-цифровыми преобразователями (АЦП), преобразователь интерфейса USB в UART, генератор на 100 МГц, датчик температуры микроконтроллера, источники питания на 1,7 В, 2,5 В, 3,3 В, 5,0 В, блок выбора источника питания, блок измерения тока потребления, блок проверки контактирования выводов тестируемых микросхем ОЗУ, преобразователь уровня напряжения управляющих входов тестируемых микросхем ОЗУ, преобразователь уровня напряжения шины адреса тестируемых микросхем ОЗУ, персональный компьютер (ПК), блок питания, драйвер, компаратор, нагрузка для каждой из n линий шины данных тестируемых микросхем ОЗУ, где n - целое число, больше 1, m цифровых датчиков температуры микросхем ОЗУ, закрепленных на корпусе тестируемых микросхем ОЗУ, где m - целое число, больше 1, при этом ПК посредством USB интерфейса через преобразователь интерфейса USB в UART соединен с микроконтроллером, два вывода микроконтроллера соединены с двумя управляющими входами блока выбора источника питания, который на основании соответствующих управляющих сигналов подключает требуемый источник питания на 1,7 В или 2,5 В или 3,3 В или 5,0 В соответственно, восемнадцать выводов микроконтроллера соединены с восемнадцатью входами блока проверки контактирования выводов тестируемых микросхем ОЗУ, который отключает напряжение питание от тестируемых микросхем ОЗУ и подает напряжение питание на общий вывод тестируемых микросхем ОЗУ, другие восемнадцать выводов микроконтроллера соединены с восемнадцатью входами преобразователя уровня напряжения управляющих входов тестируемых микросхем ОЗУ, двадцать четыре вывода микроконтроллера соединены с двадцатью четырьмя входами преобразователя уровня напряжения шины адреса тестируемых микросхем ОЗУ, цифровые датчики температуры тестируемых микросхем ОЗУ, закрепленные на корпусе микросхем ОЗУ, посредством I2C интерфейса соединены с первым входом микроконтроллера, второй вход микроконтроллера соединен с выходом датчика температуры, третий вход микроконтроллера соединен с выходом генератора на 100 МГц, первый выход блока измерения тока потребления соединен с первым АЦП микроконтроллера, второй выход блока измерения тока потребления соединен со вторым входом блока проверки контактирования выводов тестируемых микросхем ОЗУ, выход блока выбора источника питания соединен с входом блока измерения тока потребления, выход блока проверки контактирования выводов тестируемых микросхем ОЗУ соединен с входом второго АЦП микроконтроллера, драйвер, компаратор, нагрузка для каждой линии шины данных тестируемых микросхем ОЗУ соединены посредством LVDS интерфейсов с четвертым, пятым и шестым входом микроконтроллера соответственно, блок питания соединен со всеми элементами системы.

| Транспортир-треугольник | 1946 |

|

SU68705A1 |

| СПОСОБ ОТБРАКОВКИ КМОП ИНТЕГРАЛЬНЫХ СХЕМ ПО УРОВНЯМ НАДЕЖНОСТИ | 1992 |

|

RU2046365C1 |

| СПОСОБ КОНТРОЛЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1990 |

|

RU2018148C1 |

| Устройство для контроля интегральных микросхем памяти | 1984 |

|

SU1226532A1 |

| DE 102007004555 А1, 31.07.2008 | |||

| US 2009058438 A1, 05.03.2009. | |||

Авторы

Даты

2011-12-27—Публикация

2009-11-10—Подача