Изобретение относится к области радиотехники и связи, в частности к устройствам квазикогерентного приема дискретно-кодированных многочастотных радиосигналов, и может найти применение в информационных радиоканалах систем управления беспилотными летательными аппаратами, в частности в активных и полуактивных радиолокационных системах летательных аппаратов (ЛА), в устройствах синхронизации радиолиний телеуправления ЛА.

Известны дискриминаторы задержки сложных сигналов различного вида. Например, в [см. Тузов Г.И. Статистическая теория приема сложных сигналов. - М.: Сов. радио, 1977, гл. 4, стр. 168…244] описаны различные варианты построения дискриминаторов для фазокодоманипулированных сигналов.

Наиболее близким по технической сущности к заявляемому объекту, является дискриминатор для синхронизации по задержке В-частотного дискретно-кодированного сигнала (см. Патент №2223607 МПК H04L 7/02), выбранный в качестве прототипа.

Известный дискриминатор содержит последовательно соединенные смеситель, первый вход которого является входом дискриминатора, первый фильтр, выход которого является выходом дискриминатора, первый управляющий элемент, перестраиваемый генератор несущей частоты, фазовращатель на 90°, первый и второй перемножители, первый сумматор, второй фильтр, второй управляющий элемент и генератор опорного сигнала, выход которого подключен ко вторым входам смесителя и первого перемножителя, а также последовательно соединенные третий перемножитель и четвертый перемножитель, выход которого подключен ко второму входу первого сумматора, при этом первый вход третьего перемножителя соединен с выходом генератора опорной частоты, а также содержит объединенные первыми входами с входом дискриминатора пятый и шестой перемножители, выход пятого перемножителя подключен ко второму входу второго перемножителя, а выход шестого перемножителя подключен ко второму входу четвертого перемножителя, вторые входы третьего и пятого перемножителей подключены ко входу фазовращателя на 90°, первый вход первого перемножителя соединен со вторым входом шестого перемножителя.

Устройство-прототип обеспечивает исключение ошибок слежения за задержкой, вызванных осциллирующим характером дискриминационной характеристики. Однако, за счет использования аналоговой элементной базы точность и надежность известного дискриминатора не в полной мере удовлетворяет требованиям, предъявляемым к аппаратуре военного назначения.

Отмеченное обстоятельство является существенным недостатком прототипа.

Задача настоящего изобретения заключается в увеличении точности синхронизации дискриминатора и надежности.

Поставленная задача решается за счет того, что в дискриминатор для синхронизации по задержке В-частотного дискретно-кодированного сигнала, содержащий, как и прототип, первый, второй, третий, четвертый, пятый и шестой перемножители, первый сумматор и управляющий элемент, при этом выход первого сумматора подключен к первым входам первого и пятого перемножителей, выходы которых подключены к первым входам соответственно второго и четвертого перемножителей, к вторым входам которых подключены выходы соответственно шестого и третьего перемножителей, первые входы которых объединены, причем второй вход пятого перемножителя объединен со вторым входом шестого перемножителя, второй вход первого перемножителя объединен со вторым входом третьего перемножителя, в отличие от прототипа, введены два делителя на два, симметричный мультивибратор, второй сумматор, элемент И, реверсивный счетчик, В делителей частоты и формирователь импульсов, вход которого является входом дискриминатора, а выход формирователя импульсов подключен к первым входам третьего и шестого перемножителей, а выходы второго и четвертого перемножителей подключены соответственно к первому и второму входам второго сумматора, при этом выход второго сумматора подключен к первому входу элемента И, выход которого подключен к счетному входу реверсивного счетчика, управляющие входы которого объединены с первым и вторым входами второго сумматора, выход реверсивного счетчика подключен к первому входу управляющего элемента, выход которого через В делителей частоты подключены к В входам первого сумматора, выход которого является выходом дискриминатора, а прямой и инверсный выходы симметричного мультивибратора через первый и второй делители на два подключены к вторым входам соответственно первого и пятого перемножителей, причем второй вход третьего перемножителя объединен с вторыми входами элемента И и управляющего элемента.

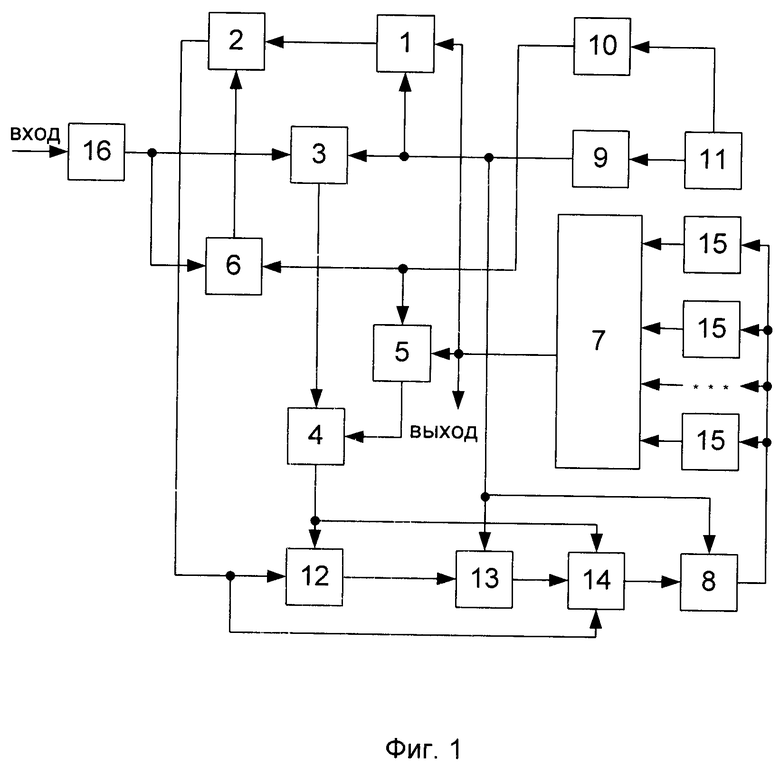

Сущность изобретения поясняется чертежом на фиг. 1, где представлена структурная схема предлагаемого дискриминатора.

Дискриминатор для синхронизации по задержке дискретно-кодированного В-частотного сигнала, содержащий первый 1, второй 2, третий 3, четвертый 4, пятый 5 и шестой 6 перемножители, первый сумматор 7 и управляющий элемент 8, при этом выход первого сумматора 7 подключен к первым входам первого 1 и пятого 5 перемножителей, выходы которых подключены к первым входам соответственно второго 2 и четвертого 4 перемножителей, к вторым входам которых подключены выходы соответственно шестого 6 и третьего 3 перемножителей, первые входы которых объединены, причем второй вход пятого 5 перемножителя объединен со вторым входом шестого 6 перемножителя, второй вход первого 1 перемножителя объединен со вторым входом третьего 3 перемножителя. В отличие от прототипа в него введены два делителя на два 9 и 10, симметричный мультивибратор 11, второй сумматор 12, элемент И 13, реверсивный счетчик 14, В делителей частоты 15 и формирователь импульсов 16, вход которого является входом дискриминатора, а выход формирователя импульсов 16 подключен к первым входам третьего 3 и шестого 6 перемножителей, выходы второго 2 и четвертого 4 перемножителей подключены соответственно к первому и второму входам второго сумматора 12, при этом выход второго сумматора 12 подключен к первому входу элемента И 13, выход которого подключен к счетному входу реверсивного счетчика 14, управляющие входы которого объединены с первым и вторым входами второго сумматора 12, а выход реверсивного счетчика 14 подключен к первому входу управляющего элемента 8, выход которого через В делителей частоты 15 подключены к В входам первого сумматора 7, выход которого является выходом дискриминатора, а прямой и инверсный выходы симметричного мультивибратора 11 через первый 9 и второй 10 делители на два подключены к вторым входам соответственно первого 1 и пятого 5 перемножителей, причем второй вход пятого 5 перемножителя объединен с вторыми входами элемента И 13 и управляющего элемента 8.

Устройство работает следующим образом.

Так же как и в прототипе на вход заявляемого устройства поступает В-частотный дискретно-кодированный сигнал, представляющий собой совокупность одновременно передаваемых гармонических составляющих различных частот. Этот сигнал проходит через формирователь импульсов 16, который может быть выполнен, например, в виде жесткого ограничителя [см. Алексеенко А.Г., Коломбет Е.А., Стародуб Г.И. Применение прецизионных аналоговых ИС. - М. Радио и связь, 1981, стр. 194]. Образованная при этом последовательность прямоугольных импульсов поступает на первые входы перемножителей 3 и 6 соответственно. На другие входы перемножителей 3 и 6 поступает опорный меандр. Этот меандр формируется с помощью симметричного мультивибратора 11, частота повторения которого установлена равной удвоенной частоте синхронизации. Импульсы с прямого и инверсного выходов мультивибратора 11 через делители 9 и 10 частоты на два в виде сдвинутых на  периода частоты синхронизации

периода частоты синхронизации  последовательностей поступают на вторые входы перемножителей 3 и 6. Последовательность перемножения сигналов в перемножителях 1, 2, 4 и 5 аналогична устройству-прототипу при этом на вторые входы перемножителей 1 и 5 поступает оценочное значение принятого дискретно-кодированного В-частотного сигнала (в цифровом виде). В результате на выходах перемножителей 2 и 4 формируются два сигнала, которые управляют реверсом счетчика 14, на счетный вход которого через элемент И 13 поступает последовательность опорного меандра с выхода делителя 9. Разрешение на элемент И 13 подается с сумматора 12 по модулю два только в тот момент, когда на выходах перемножителей 2 и 4 присутствуют сигналы разных знаков. Эта операция, тождественная операции вычитания, обеспечивает работоспособность реверсивного счетчика 14, который осуществляет интегрирование разности, т.е. формирование дискриминационной характеристики. В управляющем элементе 8 в зависимости от знака рассогласования осуществляется либо добавление импульсов в поступающую на его вход последовательность опорного меандра, либо вычитание. Образованные на выходе элемента 8 импульсы поступают на входы В делителей 15 частоты с коэффициентом деления n/В (где n-номер гармонической составляющей дискретно-кодированного В-частотного сигнала), с выходов которых они поступают на входы сумматора 7, выход которого соединен с соответствующими входами перемножителей 1 и 5 для формирования оценочного значения задержки принятого сигнала.

последовательностей поступают на вторые входы перемножителей 3 и 6. Последовательность перемножения сигналов в перемножителях 1, 2, 4 и 5 аналогична устройству-прототипу при этом на вторые входы перемножителей 1 и 5 поступает оценочное значение принятого дискретно-кодированного В-частотного сигнала (в цифровом виде). В результате на выходах перемножителей 2 и 4 формируются два сигнала, которые управляют реверсом счетчика 14, на счетный вход которого через элемент И 13 поступает последовательность опорного меандра с выхода делителя 9. Разрешение на элемент И 13 подается с сумматора 12 по модулю два только в тот момент, когда на выходах перемножителей 2 и 4 присутствуют сигналы разных знаков. Эта операция, тождественная операции вычитания, обеспечивает работоспособность реверсивного счетчика 14, который осуществляет интегрирование разности, т.е. формирование дискриминационной характеристики. В управляющем элементе 8 в зависимости от знака рассогласования осуществляется либо добавление импульсов в поступающую на его вход последовательность опорного меандра, либо вычитание. Образованные на выходе элемента 8 импульсы поступают на входы В делителей 15 частоты с коэффициентом деления n/В (где n-номер гармонической составляющей дискретно-кодированного В-частотного сигнала), с выходов которых они поступают на входы сумматора 7, выход которого соединен с соответствующими входами перемножителей 1 и 5 для формирования оценочного значения задержки принятого сигнала.

Технический результат от использования предлагаемого дискриминатора для синхронизации по задержке В-частотного дискретно-кодированного сигнала заключается, в отличие от прототипа, в повышении точности синхронизации дискриминатора. Введение новых элементов в заявляемый дискриминатор позволяет использовать в нем цифровой алгоритм обработки сигналов, реализуемый цифровыми элементами, которые отличаются от аналоговых большими надежностью и точностью. Кроме того, упрощается сопряжение дискриминатора с цифровыми устройствами системы управления, так как указанное сопряжение может производиться без использования аналого-цифрового преобразования.

Все вновь вводимые элементы широко используются в устройствах радиолокации и связи, описаны в литературе и их практическая реализация не вызывает трудностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискриминатор для синхронизации по задержке B-частотного дискретно-кодированного сигнала | 2024 |

|

RU2839073C1 |

| Дискриминатор для синхронизации по задержке В-частотного дискретно-кодированного сигнала | 2023 |

|

RU2811561C1 |

| Дискриминатор для синхронизации по задержке В-частотного дискретно-кодированного сигнала | 2021 |

|

RU2762717C1 |

| ДИСКРИМИНАТОР ДЛЯ СИНХРОНИЗАЦИИ ПО ЗАДЕРЖКЕ В-ЧАСТОТНОГО ДИСКРЕТНО-КОДИРОВАННОГО СИГНАЛА | 2002 |

|

RU2223607C1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| ДИСКРИМИНАТОР ДЛЯ СИНХРОНИЗАЦИИ ПО ЗАДЕРЖКЕ В-ЧАСТОТНОГО ДИСКРЕТНО-КОДИРОВАННОГО СИГНАЛА | 2011 |

|

RU2479139C1 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЧАСТОТОЙ ШУМОПОДОБНЫХ СИГНАЛОВ | 2007 |

|

RU2325041C1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2548010C1 |

Изобретение может найти применение в информационных радиоканалах систем управления беспилотными летательными аппаратами. Технический результат - повышение точности синхронизации дискриминатора. Для этого предложен дискриминатор для синхронизации по задержке дискретно-кодированного В-частотного сигнала, который содержит первый, второй, третий, четвертый, пятый и шестой перемножители, первый сумматор и управляющий элемент, при этом выход первого сумматора подключен к первым входам первого и пятого перемножителей, выходы которых подключены к первым входам соответственно второго и четвертого перемножителей, ко вторым входам которых подключены выходы соответственно шестого и третьего перемножителей, первые входы которых объединены, причем второй вход пятого перемножителя объединен со вторым входом шестого перемножителя, второй вход первого перемножителя объединен со вторым входом третьего перемножителя два делителя на два, симметричный мультивибратор, второй сумматор, элемент И, реверсивный счетчик, В делителей частоты и формирователь импульсов, вход которого является входом дискриминатора, а выход формирователя импульсов подключен к первым входам третьего и шестого перемножителей. 1 ил.

Дискриминатор для синхронизации по задержке дискретно-кодированного В-частотного сигнала, содержащий первый, второй, третий, четвертый, пятый и шестой перемножители, первый сумматор и управляющий элемент, при этом выход первого сумматора подключен к первым входам первого и пятого перемножителей, выходы которых подключены к первым входам соответственно второго и четвертого перемножителей, ко вторым входам которых подключены выходы соответственно шестого и третьего перемножителей, первые входы которых объединены, причем второй вход пятого перемножителя объединен со вторым входом шестого перемножителя, второй вход первого перемножителя объединен со вторым входом третьего перемножителя, отличающийся тем, что в него введены два делителя на два, симметричный мультивибратор, второй сумматор, элемент И, реверсивный счетчик, В делителей частоты и формирователь импульсов, вход которого является входом дискриминатора, а выход формирователя импульсов подключен к первым входам третьего и шестого перемножителей, а выходы второго и четвертого перемножителей подключены соответственно к первому и второму входам второго сумматора, при этом выход второго сумматора подключен к первому входу элемента И, выход которого подключен к счетному входу реверсивного счетчика, управляющие входы которого объединены с первым и вторым входами второго сумматора, выход реверсивного счетчика подключен к первому входу управляющего элемента, выход которого через В делителей частоты подключены к В входам первого сумматора, выход которого является выходом дискриминатора, а прямой и инверсный выходы симметричного мультивибратора через первый и второй делители на два подключены ко вторым входам соответственно первого и пятого перемножителей, причем второй вход пятого перемножителя объединен с вторыми входами элемента И и управляющего элемента.

| ДИСКРИМИНАТОР ДЛЯ СИНХРОНИЗАЦИИ ПО ЗАДЕРЖКЕ В-ЧАСТОТНОГО ДИСКРЕТНО-КОДИРОВАННОГО СИГНАЛА | 2002 |

|

RU2223607C1 |

| ДИСКРИМИНАТОР ДЛЯ СИНХРОНИЗАЦИИ ПО ЗАДЕРЖКЕ В-ЧАСТОТНОГО ДИСКРЕТНО-КОДИРОВАННОГО СИГНАЛА | 2011 |

|

RU2479139C1 |

| US 8036307 B2, 11.10.2011 | |||

| ДИСКРИМИНАТОР СИСТЕМЫ СИНХРОНИЗАЦИИ | 0 |

|

SU356808A1 |

Авторы

Даты

2021-08-27—Публикация

2020-11-03—Подача