Изобретение относится к области радиотехники и может использоваться в широкополосных системах радиосвязи и радионавигации с шумоподобными сигналами с минимальной частотной модуляцией и дополнительной BOC-модуляцией (Binary Offset Carrier).

Известно устройство для корреляционного приема шумоподобных сигналов с минимальной частотной манипуляцией, содержащее блок фазовой синхронизации, включающий фазовый дискриминатор, петлевой фильтр и подстраиваемый генератор несущей частоты, блок кодовой синхронизации, который содержит временной дискриминатор, петлевой фильтр, управляемый тактовый генератор, формирователь опорных сигналов, управляемый фазовращатель, генератор кода, дешифратор, синтезатор квадратурных сигналов [Патент RU №2307474 С1, МПК H04L 27/227, 27.09.2007].

Недостаток известного устройства - невысокая помехоустойчивость, обусловленная применением некогерентной системы слежения за задержкой сигнала.

Известно устройство для корреляционного приема шумоподобных сигналов с минимальной частотной манипуляцией и дополнительной модуляцией ВОС, содержащее блок фазовой синхронизации, включающий фазовый дискриминатор, содержащий семь перемножителей, вычитатель, сумматор, два интегратора и решающий блок, подстраиваемый генератор несущей частоты, петлевой фильтр, блок кодовой синхронизации, который содержит временной дискриминатор, петлевой фильтр, управляемый тактовый генератор, формирователь опорных сигналов, управляемый фазовращатель, генератор кода, дешифратор, синтезатор квадратурных сигналов и блок устранения неоднозначности, который содержит четыре перемножителя, четыре вычитателя, два интегратора, два фильтра нижних частот и командный блок [Патент RU №2431919 С1, МПК Н04В 1/10, 2006.01].

Недостаток известного устройства - значительные аппаратурные затраты, связанные с устранением аномальных ошибок кодовой синхронизации.

Наиболее близким техническим решением к предлагаемому является корреляционный приемник шумоподобных сигналов с минимальной частотной манипуляцией, содержащий блок фазовой синхронизации, включающий фазовый дискриминатор, первый петлевой фильтр и подстраиваемый генератор несущей частоты, а также блок кодовой синхронизации, включающий когерентный временной дискриминатор, второй петлевой фильтр, управляемый фазовращатель, делитель частоты, генератор кода, дешифратор и синтезатор опорных квадратурных сигналов [Патент RU №2374776 С2, МПК H04L 27/14, 2006.01].

Недостаток известного устройства - невысокая точность кодовой синхронизации вследствие аномальных ошибок, обусловленных многозначностью фазовой синхронизации.

Предлагаемое изобретение призвано решить задачу повышения точности кодовой синхронизации корреляционного приемника шумоподобных сигналов с минимальной частотной модуляцией.

Поставленная задача решается тем, что в корреляционном приемнике шумоподобных сигналов с минимальной частотной модуляцией, содержащем блок фазовой синхронизации, включающий фазовый дискриминатор, содержащий первый и второй перемножители, сигнальные входы которых объединены и являются входом корреляционного приемника, третий, четвертый, пятый и шестой перемножители, вычитатель и первый сумматор, первый и второй интеграторы, входы которых подключены к выходам вычитателя и первого сумматора соответственно, решающий блок, вход которого подключен к выходу первого интегратора, а выход которого соединен с опорным входом седьмого перемножителя, сигнальный вход которого подключен к выходу второго интегратора, а к выходу которого подключены последовательно соединенные первый петлевой фильтр и подстраиваемый генератор несущей частоты, квадратурные выходы которого соединены соответственно с опорными входами первого и второго перемножителей, при этом сигнальные входы третьего и пятого, четвертого и шестого перемножителей попарно объединены и подключены к выходам соответственно первого и второго перемножителей, выходы третьего и четвертого, пятого и шестого перемножителей объединены соответственно через вычитатель и первый сумматор, блок кодовой синхронизации, включающий последовательно соединенные временной дискриминатор, содержащий последовательно соединенные второй сумматор, третий интегратор и восьмой перемножитель, опорный вход которого подключен к выходу решающего блока, второй петлевой фильтр и управляемый фазовращатель, другой вход которого подключен к выходу делителя частоты, входом соединенного с первым квадратурным выходом подстраиваемого генератора несущей частоты, а также генератор кода, к дополнительным выходам которого подключен дешифратор, к выходу которого подключены синхронизирующие входы первого, второго и третьего интеграторов, синтезатор квадратурных сигналов, подключенный по входу к выходу генератора кода, согласно изобретению блок кодовой синхронизации дополнительно содержит девятый и десятый перемножители, сигнальные входы которых подключены к выходам соответственно первого и второго перемножителей, а выходы которых объединены через второй сумматор, и формирователь опорных сигналов, содержащий последовательно соединенные первый знаковый элемент, вход которого подключен к первому выходу синтезатора квадратурных сигналов, и элемент задержки, второй знаковый элемент, вход которого подключен ко второму выходу синтезатора квадратурных сигналов, делитель частоты на два, фазовращатель на π/2, инвертор, а также одиннадцатый, двенадцатый, тринадцатый и четырнадцатый перемножители, при этом первые входы одиннадцатого и тринадцатого, двенадцатого и четырнадцатого перемножителей попарно объединены и подключены соответственно к выходам элемента задержки и второго знакового элемента, вторые входы одиннадцатого и четырнадцатого, двенадцатого и тринадцатого перемножителей попарно объединены и подключены соответственно к выходам фазовращателя на π/2 и инвертора, входы которых объединены и подключены к выходу делителя частоты на два, который входом подключен к выходу управляемого фазовращателя, а к выходам одиннадцатого и двенадцатого перемножителей соответственно подключены попарно объединенные опорные входы третьего и шестого, четвертого и пятого перемножителей фазового дискриминатора, к выходам тринадцатого и четырнадцатого перемножителей соответственно подключены опорные входы девятого и десятого перемножителей временного дискриминатора.

Введение перечисленных узлов с описанными связями позволяет по сравнению с прототипом повысить точность кодовой синхронизации корреляционного приемника шумоподобных сигналов с минимальной частотной модуляцией.

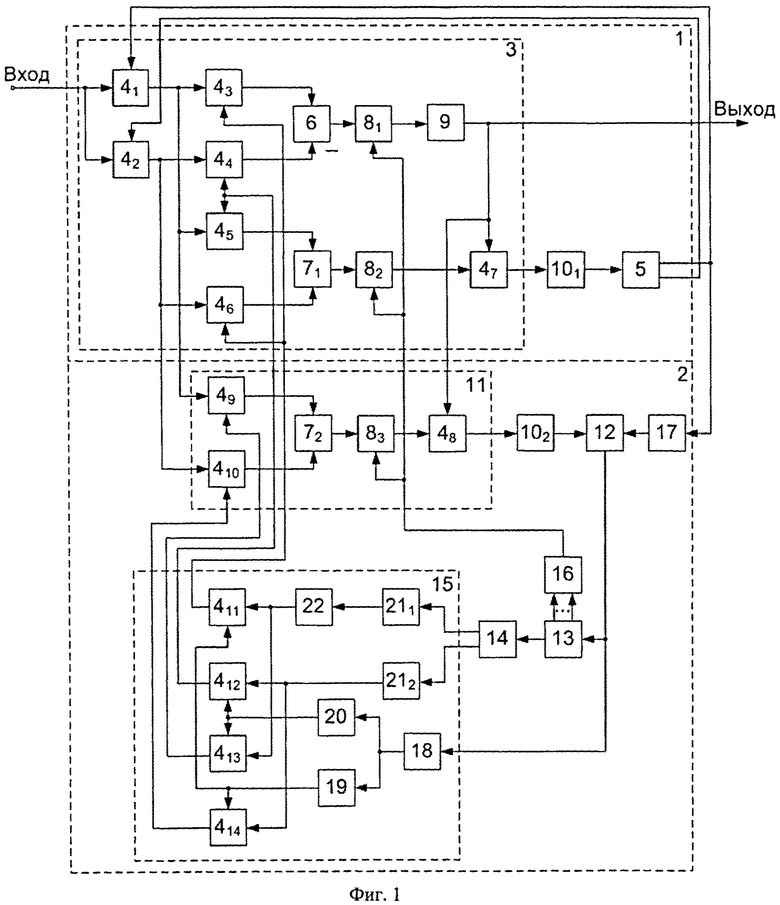

На фиг.1 приведена функциональная схема заявляемого устройства. Корреляционный приемник шумоподобных сигналов с минимальной частотной модуляцией содержит блок 1 фазовой синхронизации, вход которого является и входом корреляционного приемника, и блок 2 кодовой синхронизации.

Блок 1 фазовой синхронизации содержит фазовый дискриминатор 3, включающий первый 41 и второй 42 перемножители, сигнальные входы которых объединены, а опорные входы подключены соответственно к квадратурным выходам подстраиваемого генератора 5 несущей частоты в блоке 1 фазовой синхронизации. Фазовый дискриминатор 3 содержит также третий 43, четвертый 44, пятый 45, шестой 46 и седьмой 47 перемножители, вычитатель 6 и первый сумматор 71, первый и второй интеграторы 81 и 82, решающий блок 9. При этом сигнальные входы третьего 43 и пятого 45, четвертого 44 и шестого 46 перемножителей попарно объединены и подключены соответственно к выходам первого 41 и второго 42 перемножителей. Выходы третьего 43 и четвертого 44, пятого 45 и шестого 46 перемножителей объединены соответственно через вычитатель 6 и первый сумматор 71, к выходам которых подключены соответственно первый 81 и второй 82 интеграторы. Сигнальный вход седьмого перемножителя 47 подключен к выходу второго интегратора 82, опорный вход перемножителя 47 подключен к выходу решающего блока 9, входом соединенного с выходом первого интегратора 81, а выход перемножителя 47 подключен к входу первого петлевого фильтра 101, выходом соединенного с входом подстраиваемого генератора 5 несущей частоты. При этом выход решающего блока 9 является и выходом корреляционного приемника.

Блок 2 кодовой синхронизации содержит последовательно соединенные временной дискриминатор 11 и второй петлевой фильтр 102, выход которого соединен с управляющим входом управляемого фазовращателя 12, к выходу которого подключены последовательно соединенные генератор 13 кода и синтезатор 14 квадратурных сигналов. Блок 2 кодовой синхронизации содержит также формирователь 15 опорных сигналов, дешифратор 16, подключенный по входу к дополнительным выходам генератора 13 кода, делитель 17 частоты, вход которого соединен с первым квадратурным выходом подстраиваемого генератора 5 несущей частоты, а к выходу которого подключен сигнальный вход управляемого фазовращателя 12.

Временной дискриминатор 11 содержит второй сумматор 72, к выходу которого подключены последовательно соединенные третий интегратор 83 и восьмой перемножитель 48, а также девятый 49 и десятый 410 перемножители, сигнальные входы которых подключены соответственно к выходам первого 41 и второго 42 перемножителей в блоке 1 фазовой синхронизации, а выходы объединены через второй сумматор 72. При этом синхронизирующий вход интегратора 83 соединен с синхронизирующими входами интеграторов 81 и 82 и подключен к выходу дешифратора 16, а перемножитель 48 опорный входом подключен к выходу решающего блока 9, а выходом - соединен с входом второго петлевого фильтра 102.

Формирователь 15 опорных сигналов включает делитель 18 частоты на два, вход которого соединен с выходом управляемого фазовращателя 12, а выход которого подключен к объединенным входам фазовращателя 19 на π/2 и инвертора 20. Формирователь 15 опорных сигналов содержит также знаковые элементы 211 и 212, подключенные по входу соответственно к выходам синтезатора 14 квадратурных сигналов, элемент 22 задержки, входом соединеный с выходом знакового элемента 211, а также одиннадцатый 411, двенадцатый 412, тринадцатый 413 и четырнадцатый 414 перемножители. При этом первые входы одиннадцатого 411 и тринадцатого 413, двенадцатого 412 и четырнадцатого 414 перемножителей попарно объединены и подключены соответственно к выходам элемента 22 задержки и второго знакового элемента 212, а вторые входы перемножителей 411 и 414, 412 и 413 попарно объединены и подключены соответственно к выходам фазовращателя 19 на π/2 и инвертора 20. К выходам одиннадцатого 411 и двенадцатого 412 перемножителей соответственно подключены попарно объединенные опорные входы перемножителей 43 и 46, 44 и 45 фазового дискриминатора 3, а к выходам тринадцатого 413 и четырнадцатого 414 перемножителей соответственно подключены опорные входы перемножителей 49 и 410 временного дискриминатора 11.

Корреляционный приемник шумоподобных сигналов (ШПС) с минимальной частотной модуляцией работает следующим образом. Входной шумоподобный сигнал, модулированный цифровым сообщением D(t)∈[1, -1], поступает на перемножители 41 и 42, где перемножается с опорными квадратурными сигналами соответственно cos(ω0t) и sin(ω0t) частоты ω0, равной средней частоте ШПС. Указанные сигналы вырабатываются подстраиваемым генератором 5 несущей частоты в блоке 1 фазовой синхронизации. Квадратурные видеочастотные сигналы с выходов перемножителей 41 и 42 поступают на попарно объединенные сигнальные входы перемножителей соответственно 43 и 45, 44 и 46 фазового дискриминатора 3, где перемножаются с опорными видеочастотными сигналами, генерируемыми формирователем 15 опорных сигналов блока 2 кодовой синхронизации. При идеальной кодовой синхронизации опорные сигналы являются точными копиями квадратурных видеочастотных компонентов I(t) и Q(t) принимаемого ШПС.

Результаты перемножения квадратурных составляющих входного и опорных сигналов объединяются в вычитателе 6 и сумматоре 71, образуя соответственно «косинусную» и «синусную» квадратурные составляющие, пропорциональные cos(φ) и sin(φ), где φ - фазовая ошибка системы синхронизации (составляющие удвоенной частоты ω0 подавляются при последующей обработке). Интеграторы 81 и 82 в квадратурных каналах фазового дискриминатора 3 осуществляют интегрирование поступающих на их входы квадратурных составляющих сжатого по спектру сигнала на интервалах, равных периоду Тп повторения ШПС. Сброс интеграторов 81 и 82 осуществляется с шагом Tп синхроимпульсами, вырабатываемыми дешифратором 16 в блоке 2 кодовой синхронизации.

Результаты z1 и z2 интегрирования в квадратурных каналах фазового дискриминатора 3, пропорциональные cos(φ) и sin(φ) соответственно, поступают на выходной перемножитель 47, формирующий сигнал ошибки Zд(φ), пропорциональный фазовому рассогласованию принимаемого ШПС и опорных сигналов частоты ω0. При этом составляющая z2 поступает на сигнальный вход перемножителя 47 непосредственно, а составляющая z1 поступает на опорный вход перемножителя 47 через решающий блок 9. Последний осуществляет оценку информационного символа путем преобразования sign(z1) (знаковая функция), благодаря чему исключается влияние цифровой модуляции ШПС сообщением D(t) на формирование сигнала ошибки. Выход решающего блока 9 является выходом корреляционного приемника (выходом демодулятора цифрового сообщения D(t)).

Выходной сигнал петлевого фильтра 101 сглаживающего флуктуации сигнала ошибки Zд(φ), обусловленные действием шума, используется для управления частотой и фазой опорных сигналов, формируемых подстраиваемым генератором 5 несущей частоты.

Блок 2 кодовой синхронизации работает следующим образом. Квадратурные видеочастотные сигналы с выходов перемножителей 41 и 42 поступают на сигнальные входы перемножителей соответственно 49 и 410 временного дискриминатора 11, где перемножаются с опорными сигналами, вырабатываемыми формирователем 15 опорных сигналов. При идеальной кодовой синхронизации опорные сигналы Iоп(t) и Qоп(t) перемножителей 49 и 410 являются точными копиями квадратурных видеочастотных компонентов соответственно Q(t) и 1(t) принимаемого ШПС.

Результаты перемножения квадратурных составляющих входного и опорных сигналов объединяются в сумматоре 72, образуя составляющую, пропорциональную временному рассогласованию τ принимаемого и опорных видеочастотных сигналов. Выходной сигнал сумматора 72 интегрируется на интервалах, равных периоду Тп повторения ШПС, в результате чего на выходе интегратора 83 образуется сигнал ошибки Zд(τ), пропорциональный значению производной от автокорреляционной функции видеочастотного ШПС. Сигнал ошибки на текущем периоде ШПС поступает на сигнальный вход перемножителя 48, с помощью которого исключается влияние цифровой модуляции ШПС сообщением D(t). Достигается это путем подачи на опорный вход перемножителя 48 оценки информационного символа с выхода решающего блока 9. Петлевой фильтр 102 сглаживает флуктуации сигнала ошибки, формируя управляющий сигнал для управляемого фазовращателя 12. Меандровый сигнал тактовой частоты fт формируется делителем 17 частоты путем деления несущей частоты f0:

fт=f0/m, где m - целое.

На вход генератора 13 кода сигнал тактовой частоты поступает через управляемый фазовращатель 12.

Формируемая генератором 13 кода кодовая последовательность поступает на вход синтезатора 14 квадратурных сигналов, определяя знак приращения фазы π/2 на интервалах, равных длительности Т элемента кода. Дешифратор 16, подключенный к генератору 13 кода, формирует синхроимпульсы с частотой повторения

Fп=1/Тп

для интеграторов 81, 82 и 83 фазового и временного дискриминаторов 3 и 11.

Формирователь 15 опорных сигналов работает следующим образом. На входы знаковых элементов 211 и 212 поступают видеочастотные сигналы I4T(t) и Q4T(t) соответственно с выходов синтезатора 14 квадратурных сигналов. Сигналы I4T(t) и Q4T(t) представляют собой действительную и мнимую составляющие комплексной огибающей ШПС с минимальной частотной модуляцией. Элементы каждого из сигналов имеют вид полуволны косинуса частоты fт/4, причем каждый k-й элемент сигнала Q4T(t) запаздывает на Т относительно k-го элемента сигнала I4T(t). На выходах знаковых элементов 211 и 212 выделяются кодовые последовательности соответственно С(t) и S(t) с элементами длительности 2T, принимающими значения 1 или (-1).

Для формирования квадратурных видеочастотных компонентов I(t) и Q(t) опорного ШПС с дополнительной ВОС-модуляцией необходимо обеспечить временной сдвиг сигнала Q(t) относительно сигнала I(t) на четверть периода колебания полутактовой частоты fт/2, вырабатываемого делителем 18 частоты на два. Для этого в канал формирования кодовой последовательности С включен элемент 22 задержки на T/2. Кодовая последовательность С c выхода элемента 22 задержки и кодовая последовательность S с выхода знакового элемента 212 поступают соответственно на первые входы перемножителей 411 и 413, 412 и 414, на вторые входы которых подаются квадратурные составляющие колебания полутактовой частоты fт/2 с выходов соответственно фазовращателя 19 на π/2 и инвертора 20. На выходах перемножителей 411 и 412 формируются квадратурные опорные сигналы I(t) и Q(t) (с формой элементов каждого из сигналов в виде волны синуса частоты fт/2), которые подаются соответственно на опорные входы перемножителей 43 и 46, 44 и 45 фазового дискриминатора 3 в блоке 1 фазовой синхронизации.

Опорные сигналы для временного дискриминатора 11 в блоке 2 кодовой синхронизации формируются аналогично опорным сигналам I(t) и Q(t) фазового дискриминатора 3, с той лишь разницей, что квадратурные составляющие полутактовой частоты fт/2 меняются местами: для формирования сигнала Iоп(t) используется колебание с выхода инвертора 20, а для формирования сигнала Qоп(t) - колебание с выхода фазовращателя 19 на π/2. С выходов перемножителей 413 и 414 опорные сигналы Iоп(t) и Qоп(t) подаются соответственно на опорные входы перемножителей 49 и 410 временного дискриминатора 11.

В установившемся режиме работы точность кодовой синхронизации определяется фазовой ошибкой системы синхронизации. В силу периодичности дискриминационной характеристики фазового дискриминатора в установившемся режиме возможна статическая ошибка, кратная полупериоду T0/2 несущей частоты. Для ее устранения (устранения многозначности фазовой синхронизации) используется контур регулирования, включающий временной дискриминатор 11, петлевой фильтр 102 и управляемый фазовращатель 12. При наличии статической ошибки вырабатывается управляющий сигнал, пропорциональный временному рассогласованию. Под действием этого сигнала колебание тактовой частоты сдвигается на целое число полупериодов T0/2 в сторону опережения или запаздывания в зависимости от величины и знака управляющего сигнала, поступающего на управляемый фазовращатель 12 с выхода петлевого фильтра 102.

При этом ошибка слежения за задержкой в блоке кодовой синхронизации определяет достоверность правильного устранения многозначности фазовой синхронизации, при котором отсутствуют аномальные ошибки, кратные полупериоду T0/2 несущей частоты.

Ошибка слежения за задержкой обратно пропорциональна эффективной ширине спектра сигнала, которая при использовании ШПС с дополнительной ВОС-модуляцией возрастает в два и более раз по сравнению с ШПС без ВОС-модуляции [Помехоустойчивость временных дискриминаторов шумоподобных сигналов с фазовой и частотной модуляцией /В.Н. Бондаренко, А.Г. Клевлин, В.И. Кокорин. // Радиотехника и электроника. - 2012. - Т.57. - №1. - С.59-66].

По сравнению с устройством-прототипом предлагаемое устройство позволяет повысить точность кодовой синхронизации корреляционного приемника шумоподобных сигналов с минимальной частотной модуляцией за счет повышения достоверности правильного устранения многозначности фазовой синхронизации.

Заявляемое устройство может быть реализовано на современной цифровой элементной базе, в частности, с использованием программируемых логических интегральных схем (ПЛИС).

Пример реализации синтезатора квадратурных сигналов с использованием накапливающего сумматора (аккумулятора фазы) и постоянного запоминающего устройства для хранения отсчетов квадратурных сигналов приведен в монографии [Цифровые системы фазовой синхронизации / М.И. Жодзишский, С.Ю. Сила-Новицкий, В.А. Прасолов и др.; Под ред. М.И. Жодзишского. - М.: Сов. Радио, 1980. - С.55-57].

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| СПОСОБ ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2012 |

|

RU2486683C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ С НЕПРЕРЫВНОЙ ФАЗОЙ | 2006 |

|

RU2323536C1 |

| СПОСОБ ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2009 |

|

RU2420005C1 |

Изобретение относится к области радиотехники и может использоваться в широкополосных системах радиосвязи и радионавигации с шумоподобными сигналами с минимальной частотной модуляцией и дополнительной BOC-модуляцией (Binary Offset Carrier). Технический результат заключается в повышении точности кодовой синхронизации корреляционного приемника шумоподобных сигналов с минимальной частотной модуляцией за счет повышения достоверности правильного устранения многозначности фазовой синхронизации. Корреляционный приемник шумоподобных сигналов с минимальной частотной модуляцией содержит блок фазовой синхронизации, блок кодовой синхронизации, включающий временной дискриминатор, генератор кода, к дополнительным выходам которого подключен дешифратор, синтезатор квадратурных сигналов и формирователь опорных сигналов, обеспечивающий устранение аномальных ошибок фазовой синхронизации, кратных полупериоду T0/2 несущей частоты. 1 ил.

Корреляционный приемник шумоподобных сигналов с минимальной частотной модуляцией, содержащий блок фазовой синхронизации, включающий фазовый дискриминатор, содержащий первый и второй перемножители, сигнальные входы которых объединены и являются входом корреляционного приемника, третий, четвертый, пятый и шестой перемножители, вычитатель и первый сумматор, первый и второй интеграторы, входы которых подключены к выходам вычитателя и первого сумматора соответственно, решающий блок, вход которого подключен к выходу первого интегратора, а выход которого соединен с опорным входом седьмого перемножителя, сигнальный вход которого подключен к выходу второго интегратора, а к выходу которого подключены последовательно соединенные первый петлевой фильтр и подстраиваемый генератор несущей частоты, квадратурные выходы которого соединены соответственно с опорными входами первого и второго перемножителей, при этом сигнальные входы третьего и пятого, четвертого и шестого перемножителей попарно объединены и подключены к выходам соответственно первого и второго перемножителей, выходы третьего и четвертого, пятого и шестого перемножителей объединены соответственно через вычитатель и первый сумматор, блок кодовой синхронизации, включающий последовательно соединенные временной дискриминатор, содержащий последовательно соединенные второй сумматор, третий интегратор и восьмой перемножитель, опорный вход которого подключен к выходу решающего блока, второй петлевой фильтр и управляемый фазовращатель, другой вход которого подключен к выходу делителя частоты, входом соединенного с первым квадратурным выходом подстраиваемого генератора несущей частоты, а также генератор кода, к дополнительным выходам которого подключен дешифратор, выходом соединенный с синхронизирующими входами первого, второго и третьего интеграторов, и синтезатор квадратурных сигналов, подключенный по входу к выходу генератора кода, отличающийся тем, что в блок кодовой синхронизации введены девятый и десятый перемножители, сигнальные входы которых подключены к выходам соответственно первого и второго перемножителей, а выходы которых объединены через второй сумматор, формирователь опорных сигналов, содержащий последовательно соединенные первый знаковый элемент, вход которого подключен к первому выходу синтезатора квадратурных сигналов, и элемент задержки, второй знаковый элемент, вход которого подключен к второму выходу синтезатора квадратурных сигналов, делитель частоты на два, фазовращатель на π/2, инвертор, а также одиннадцатый, двенадцатый, тринадцатый и четырнадцатый перемножители, при этом первые входы одиннадцатого и тринадцатого, двенадцатого и четырнадцатого перемножителей попарно объединены и подключены соответственно к выходам элемента задержки и второго знакового элемента, вторые входы одиннадцатого и четырнадцатого, двенадцатого и тринадцатого перемножителей попарно объединены и подключены соответственно к выходам фазовращателя на π/2 и инвертора, входы которых объединены и подключены к выходу делителя частоты на два, вход которого подключен к выходу управляемого фазовращателя, а к выходам одиннадцатого и двенадцатого перемножителей соответственно подключены попарно объединенные опорные входы третьего и шестого, четвертого и пятого перемножителей фазового дискриминатора, к выходам тринадцатого и четырнадцатого перемножителей соответственно подключены опорные входы девятого и десятого перемножителей временного дискриминатора.

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

| Способ получения мыла | 1946 |

|

SU70695A2 |

Авторы

Даты

2015-04-10—Публикация

2014-01-09—Подача