Изобретение относится к области вычислительной техники и коммуникационных систем и может быть использовано при создании высокопроизводительных вычислительных систем (ВВС).

Вычислительные сети ВВС принято разделять на две группы: с прямой (direct) топологией и непрямой (indirect) топологией (Dally W., Towles В. Principles and Practices of Interconnection Networks. San Francisco. Morgan Kaufmann Publishers, 2004. Глава 3.1.2.).

Вычислительные сети с непрямой топологией имеют небольшой диаметр, зависящий от количества уровней в графе топологии, и соответственно высокие коммуникационные характеристики. Однако дальнейшее уменьшение диаметра вычислительной сети обеспечивается только уменьшением количества уровней, которое достигается ростом количества сетевых портов в коммутаторах, а, следовательно, значительным увеличении их стоимости и использованием дорогостоящих технологий. К непрямым топологиям относится, например, часто используемая в существующих ВВС, как зарубежных, так и отечественных, топология утолщенное дерево (Fat Tree [ресурс интернет] 10.07.2020 https://sites.google.com/site/exemsenko/6-topologia-kommunikacionnyh-setej-multiprocessornyh-sistem-sovremennye-superkomputery-i-vs-primenenie-ih-v-socialno-sfere).

Вычислительные сети с прямой топологией, наоборот, отличаются дешевизной комплектующих (коммутаторы, как правило, имеют небольшое число сетевых портов) и простотой расширения, в основном не зависящей от количества портов. Но это обуславливает значительное увеличение диаметра вычислительной сети и средней длины пути сообщения, повышает вероятность конфликтов сообщений и соответственно снижает пропускную способность, т.е. ухудшает коммуникационные характеристики всей вычислительной сети в целом. К вычислительным сетям с прямой топологией, относятся широко известные топологии вычислительных сетей Mesh (Ячеистая, [ресурс интернет] 10.07.2020 https://ru.wikipedia.org/wiki/%D0%AF%Dl%87%D0%B5%D0%B8%Dl%810/oD1%82%D0%B0%D1%82%D1%82%D0%BF%D0%BF%D0%BE%D0%BB%D 0%BE%D0%B3%D0%B8%Dl%8F), Top (Torus), Гиперкуб (Hypercub) ([ресурс интернет] 10.07.2020 https://sites.google.com/site/exemsenko/6-topologia-kommunikacionnyh-setej-multiprocessornyh-sistem-sovremennye-superkomputery-i-vs-primenenie-ih-v-socialno-sfere) и ТОФУ (TOFU [ресурс интернет] 10.07.2020 https://www.osp.ru/os/2009/10/11180288/).

Известна вычислительная сеть ВВС (Roberto  Crispin

Crispin  Maria E.

Maria E.  Pedro

Pedro  & Jose Duato// The K-ary N-direct S-indirect family of topologies for large-scale interconnection network, опубликовано 05.02.2016, The Journal of Supercomputing volume 72, pages 1035-1062, [ресурс интернет] http://doi.org/10.1007/s11227-016-1640-z), образующая гибридное семейство топологий K-ary N-direct S-indirect.

& Jose Duato// The K-ary N-direct S-indirect family of topologies for large-scale interconnection network, опубликовано 05.02.2016, The Journal of Supercomputing volume 72, pages 1035-1062, [ресурс интернет] http://doi.org/10.1007/s11227-016-1640-z), образующая гибридное семейство топологий K-ary N-direct S-indirect.

Семейство топологий K-ary N-direct S-indirect представляет собой попытку совместить в вычислительной сети лучшие черты прямых и непрямых топологий, т.е. добиться значительного улучшения коммуникационных характеристик вычислительных сетей, таких как диаметр, стоимость и энергозатратность при обеспечении высокой пропускной способности. В вычислительной сети с топологией K-ary N-direct S-indirect используется два типа коммуникационных устройств: роутер (адаптер) и коммутатор.

Известная вычислительная сеть ВВС содержит вычислительные узлы, каждый из которых содержит соответствующий роутер и один или несколько вычислительных модулей, включающих один или несколько арифметических процессоров. Вычислительные узлы располагаются (номеруются) ортогонально по измерениям (координатным направлениям), аналогично прямым топологиям Mesh или Torus. Связь между вычислительными узлами, находящимися в одном измерении происходит либо с помощью одиночных коммутаторов либо с помощью нескольких коммутаторов, объединенных по какой либо топологии, например, Fat Tree. Роутер обеспечивает связь вычислительных модулей с сетью и смену измерений при передаче транзитных сообщений. Свое название семейство топологий K-ary N-direct S-indirect получило от трех основных своих параметров: К - количество вычислительных узлов в одном измерении, N - количество измерений в прямой топологии и S - количество уровней коммутации в непрямом участке топологии. Данная вычислительная сеть ВВС выбрана в качестве наиболее близкого аналога.

Главным недостатком наиболее близкого аналога является то, что вычислительная сеть ВВС, созданная по топологии K-ary N-direct S-indirect, имеет низкую связность равную количеству задействованных сетевых портов роутера, а, следовательно, и низкую надежность. Например, при организации вычислительной сети с двумерной топологией K-ary N-direct S-indirect у каждого роутера используется только два сетевых порта и, следовательно, значение связности равно двум. В случае отказа любого канала связи, в вычислительной сети возникает «висячая вершина». Хотя вычислительный узел и роутер исправны, роутер теряет способность передавать транзитные сообщения. В вычислительной сети ВВС с топологией K-ary N-direct S-indirect алгоритм обхода таких неисправностей довольно сложен и трудно реализуем на практике. Увеличение связности при фиксированном количестве вычислительных узлов достигается за счет увеличения числа измерений в вычислительной сети. Это ведет к увеличению диаметра вычислительной сети, поскольку с каждым новым измерением диаметр вычислительной сети увеличивается на два «транзитных участка» («транзитный участок» - это участок вычислительной сети расположенный между двумя коммуникационными устройствами), а, следовательно, это приводит к увеличению задержки при передаче сообщений и увеличению стоимости вычислительной сети.

Еще одним недостатком известной вычислительной сети является то, что минимальная длина маршрута равна двум «транзитным участкам», а значит, сообщение проходит минимум три коммуникационных устройства, что увеличивает среднюю дистанцию проходимою сообщениями, что также приводит к увеличению задержки при передаче сообщений.

Технической проблемой является создание вычислительной сети высокопроизводительной вычислительной системы с высокой пропускной способностью и надежностью, которая обеспечивает меньшие затраты на коммуникацию сообщений между вычислительными узлами.

Техническими результатами, на достижение которых направлено изобретение, являются увеличение пропускной способности, повышение надежности и снижение стоимости вычислительной сети.

Технические результаты достигаются тем, что в вычислительной сети ВВС, содержащей вычислительные узлы, каждый из которых включает адаптерный блок и Μ вычислительных модулей, включающих арифметические процессоры, где Μ=1, 2, …, при этом вычислительные узлы расположены (пронумерованы) ортогонально по N измерениям, где N=1, 2, …, в каждом измерении расположены до К вычислительных узлов, где К=2, 3, …, вычислительные узлы, расположенные в одном измерении, кроме первого измерения, соединены между собой посредством соединения соответствующих им адаптерных блоков через соответствующий коммутаторный блок или соответствующую коммутаторную сборку, новым является то, что в первом измерении вычислительные узлы соединены между собой по полносвязной топологии посредством соединения двунаправленными каналами связи соответствующих сетевых портов соответствующих адаптерных блоков.

В заявляемой вычислительной сети ВВС используется два типа коммуникационных устройств: адаптерный блок (АБ) и коммутаторный блок (КБ), имеющие по n сетевых портов, где n=1, 2…. Заявляемая вычислительная сеть образует топологию MKNS, что означает модернизированная KNS. Одновременно Μ в названии - определяет количество вычислительных модулей в вычислительном узле. К - определяет количество вычислительных узлов в измерениях топологии MKNS (в первом измерении значение максимального количества вычислительных узлов равно n-2, в остальных измерениях количество вычислительных узлов неограниченно) в разных измерениях количество вычислительных узлов может быть разным, нумерация вычислительных узлов и соответственно АБ в каждом измерении начинается с 0. N - определяет количество используемых измерений (координатных направлений) в топологии MKNS (до четырех измерений). S - определяет количество уровней в непрямом участке топологии MKNS (один уровень при использовании коммутаторного блока, два или три уровня при использовании коммутаторной сборки (КСб)). Каждый вычислительный узел идентифицируется его координатой в вычислительной сети.

В заявляемой вычислительной сети ВВС за счет соединения вычислительных узлов в первом измерении между собой по полносвязной топологии («каждый с каждым») диаметр вычислительной сети уменьшается на один «транзитный участок», что ведет к увеличению пропускной способности. Одновременно с этим увеличивается связность вычислительной сети, приводящая к повышению ее надежности, обеспечивающейся большим количеством альтернативных маршрутов. Минимальная связность SVmin в описываемой схеме вычисляется по следующей формуле:

SVmin=(K1-l)+(N-l);

где К1 - количество вычислительных узлов в первом измерении,

N - количество измерений.

Уменьшение количества используемых коммутаторных блоков приводит к уменьшению стоимости вычислительной сети ВВС.

Для организации в первом измерении полносвязной топологии задействованы с первого по n-3 порты каждого АБ, поэтому максимальное количество вычислительных узлов в этом измерении равно n-2. Для организации передачи информационных пакетов между адаптерными блоками вычислительных узлов, расположенных в первом измерении, используется (n-3)×(n-2)/2 двунаправленных каналов связи, подключенных определенным образом.

Порт n-2 каждого АБ используется для связи с соответствующим КБ или КСб, которые обеспечивают передачу сообщений во втором измерении топологии MKNS. Порт n-1 каждого АБ используется для связи с соответствующим КБ или КСб, которые обеспечивают передачу сообщений в третьем измерении топологии MKNS. Порт n каждого АБ используется для связи с соответствующим КБ или КСб, которые обеспечивают передачу сообщений в четвертом измерении топологии MKNS.

В одном измерении топологии MKNS могут быть использованы либо КБ, либо КСб. В разных измерениях топологии MKNS могут использоваться, как КБ, так и КСб. Использование в одном измерении топологии MKNS вместо КБ КСб добавляет к диаметру топологии вычислительной сети по два «транзитных участка» на каждое измерение, в котором использовалась КСб.

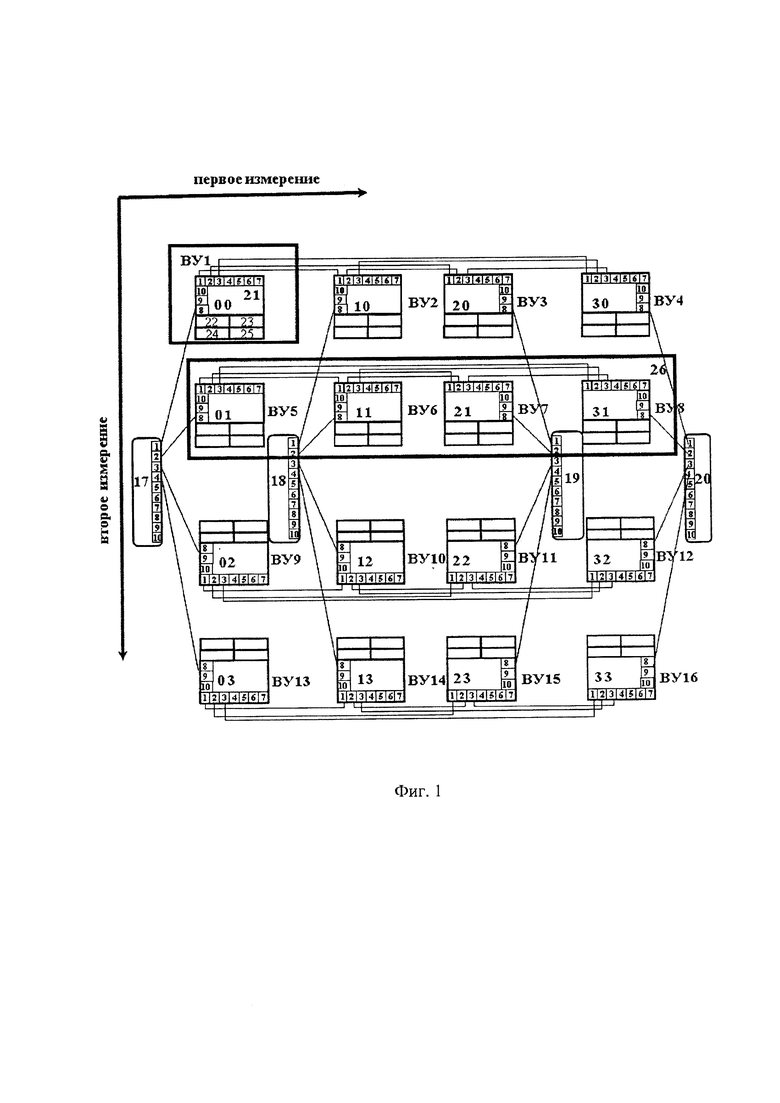

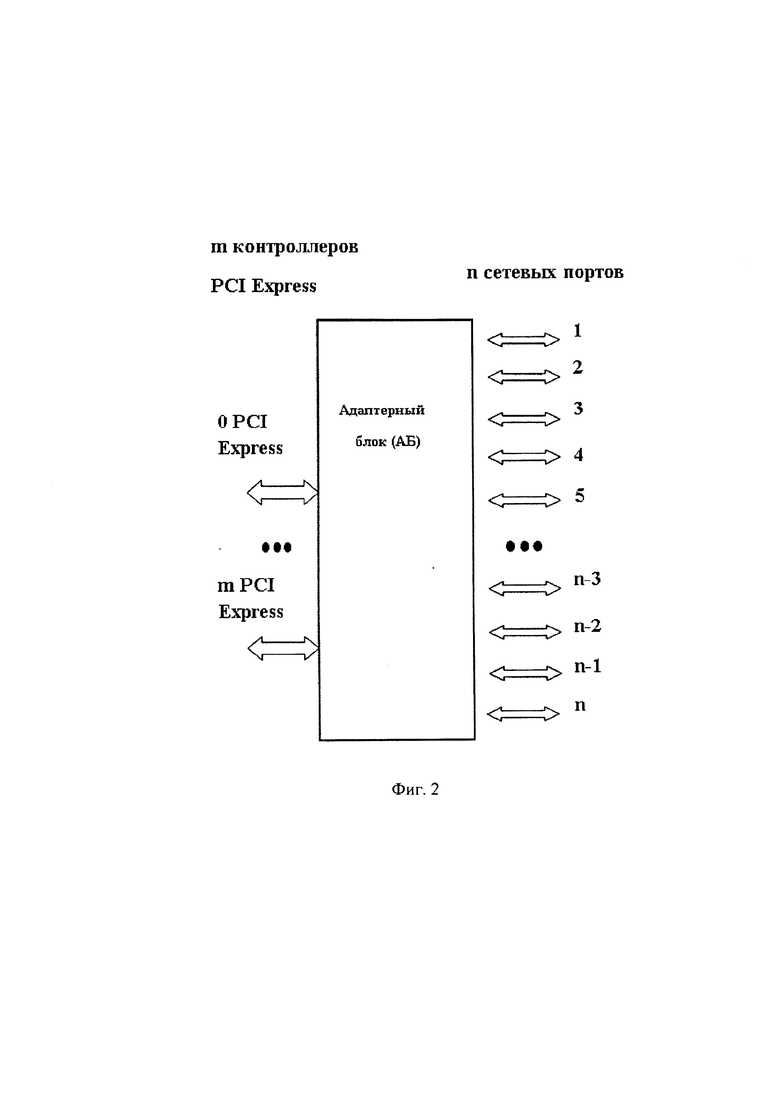

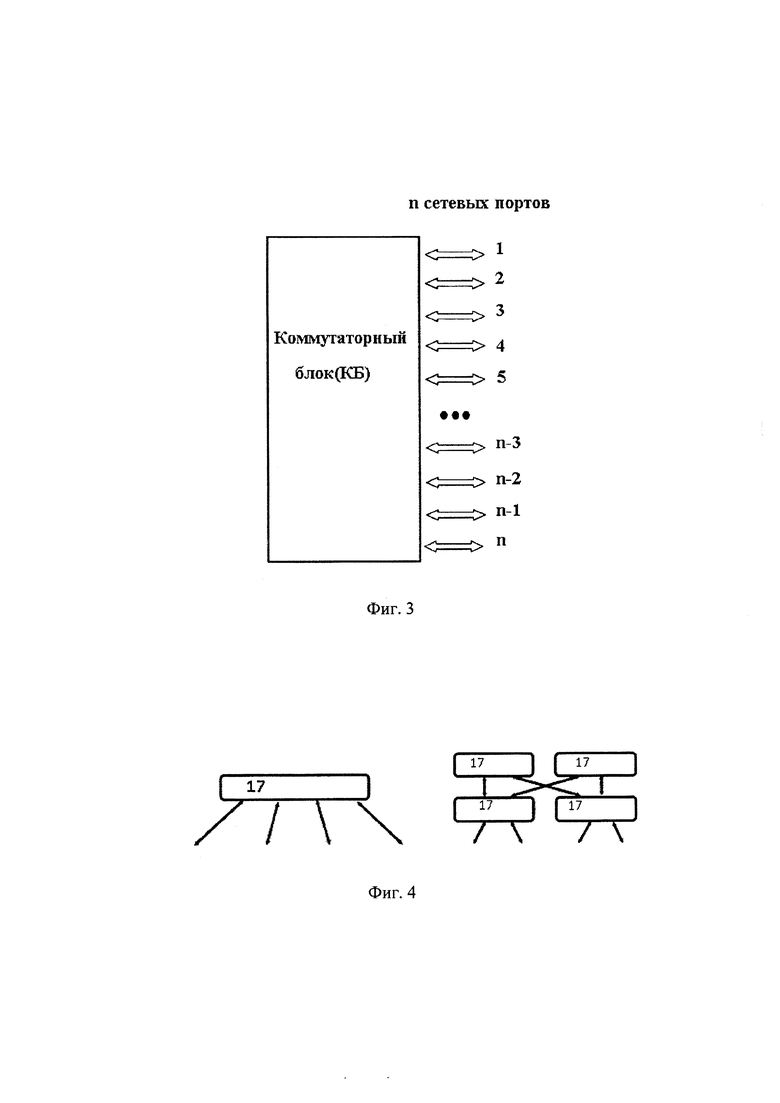

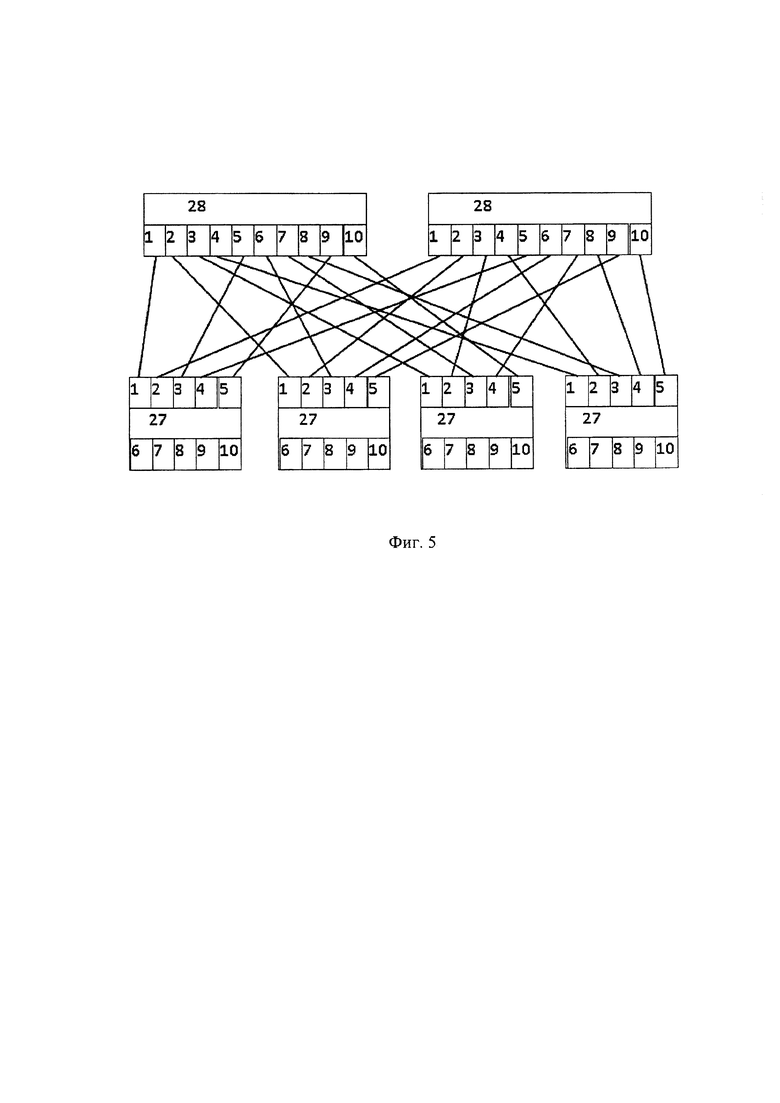

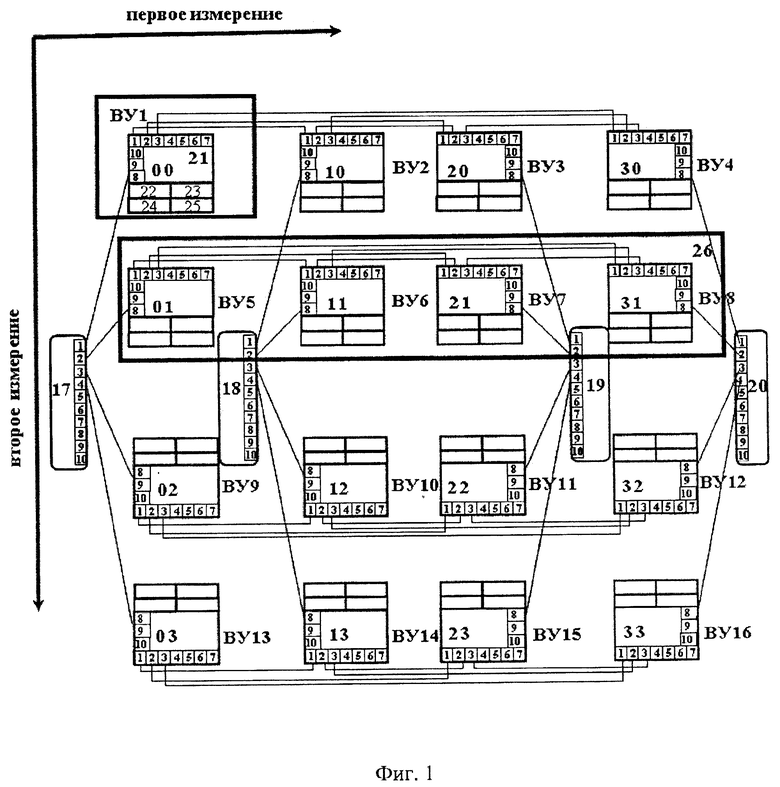

На фиг. 1 представлена блок-схема вычислительной сети ВВС при Μ=2, где Μ - количество вычислительных модулей в одном ВУ; N=2, где N -количество измерений; К=4, где К - количество вычислительных узлов в одном измерении; S=1, где S - количество уровней коммутации в непрямом участке топологии, на фиг. 2 представлен адаптерный блок, на фиг. 3 - коммутаторный блок, на фиг. 4 - представлены возможные варианты коммутации в непрямом участке топологии, на фиг. 5 представлен вариант коммутаторной сборки.

Вычислительная сеть ВВС (фиг. 1) включает вычислительные узлы ВУ1, ВУ2, …, ВУ16 расположенные (пронумерованные) ортогонально в два измерения и коммутаторные блоки 17, 18, 19, 20.

Каждый вычислительный узел (ВУ) ВУ1 (ВУ2, ВУ3,..., ВУ16) содержит соответствующий адаптерный блок 21 и два соответствующих вычислительных модуля (ВМ) 24 и 25. Вычислительные модули 24 и 25 связываются с соответствующим адаптерным блоком 21 через порты PCI Express 22 (РСI0) и 23 (РС11) соответственно. Каждый вычислительный узел ВУ1 (ВУ2, ВУ3,..., ВУ16) идентифицируется его координатой в вычислительной сети.

Вычислительные узлы ВУ1, ВУ 2,..., ВУ16 связываются между собой с использованием двух коммуникационных устройств: соответствующего адаптерного блока (АБ) и соответствующего коммутаторного блока (КБ).

Каждый адаптерный блок 21 (фиг.2) содержит полноматричный коммутатор обеспечивающий коммутацию m контроллеров PCI Express и n сетевых портов. Нумерация сетевых портов в адаптерном блоке начинается с единицы. Адаптерный блок предназначен для реализации интерфейса между вычислительными модулями, входящими в вычислительный узел, и вычислительной сетью, также адаптерный блок обеспечивает смену измерений при передаче транзитных сообщений между вычислительными узлами. Функционал адаптерного блока соответствует функционалу роутера у вычислительной сети наиболее близкого аналога.

Каждый коммутаторный блок 17 (18, 19, 20) (фиг.3) содержит полноматричный коммутатор обеспечивающий коммутацию n сетевых портов. Нумерация сетевых портов в коммутаторном блоке начинается с единицы. Коммутаторный блок 17 (18, 19, 20) обеспечивает транзит сообщений между вычислительными узлами, находящимися в одном измерении (кроме первого измерения). Функционал коммутаторного блока соответствует функционалу коммутатора у вычислительной сети наиболее близкого аналога.

В первом измерении 26 (фиг.1) вычислительным узлам ВУ5, ВУ6, ВУ7, ВУ8 присвоены соответственно координаты (идентификаторы) (0,1); (1,1); (2,1); (3,1), у которых одинаковое значение второй координаты.

Вычислительные узлы ВУ5, ВУ6, ВУ7, ВУ8 соединены между собой по полносвязной топологии «каждый с каждым» посредством соединения двунаправленными каналами связи соответствующих сетевых портов соответствующих адаптерных блоков.

Во втором измерении (фиг. 1) вычислительным узлам ВУ2, ВУ6, ВУ10, ВУ14 присвоены соответствующие координаты (1,0); (1,1); (1,2); (1,3), у которых одинаковое значение первой координаты. Вычислительные узлы ВУ2, ВУ6, ВУ10, ВУ14 соединены между собой посредством соединения соответствующих им адаптерных блоков через коммутаторный блок 18.

Во втором, третьем и четвертом измерениях адаптерные блоки 21 вычислительных узлов ВУ1 (ВУ2, ВУ3, …, ВУ16) объединены посредством либо одного коммутаторного блока, либо с помощью коммутаторной сборки (фиг. 4). Количество сетевых портов коммутаторного блока (равное n) ограничивает количество применяемых вычислительных узлов во втором, третьем и четвертом измерениях. Для снятия этого ограничения применяют коммутаторные сборки, позволяющие не ограничивать количество вычислительных узлов в данных измерениях.

На фиг. 5 приведен вариант реализации двухуровневой коммутаторной сборки по топологии Fat Tree (утолщенное дерево). Коммутаторные блоки 27 образуют первый уровень коммутаторной сборки. Их сетевые порты с номерами 6-10 предназначены для соединения с адаптерными блоками вычислительных узлов, а сетевые порты с номерами 1-5 предназначены для соединения с соответствующими сетевыми портами коммутаторных блоков 28 второго уровня по непрямой топологии Fat Tree. Такая коммутаторная сборка, состоящая из коммутаторных блоков, имеющих по n сетевых портов, позволяет связать во втором, третьем и четвертом измерениях вычислительной сети до 2×n вычислительных узлов. К достоинству коммутаторной сборки можно отнести то, что она не уменьшает такую коммуникационную характеристику, как ширина бисекции.

Вычислительная сеть высокопроизводительной вычислительной системы работает следующим образом.

Предварительно каждому ВМ присваивается порядковый номер в ВУ и каждому ВУ присваивается соответствующий идентификатор (координаты по измерениям), которые однозначно определяют позиции передающих и принимающих устройств в вычислительной сети.

Передача информации между вычислительными узлами с совпадающими координатами означает передачу информации между вычислительными модулями, подключенными к одному вычислительному узлу, только через АБ этого вычислительного узла. Например, передача информации из ВМ 25, расположенного в ВУ1, в ВМ 24, расположенный в ВУ1, имеющих одинаковые координаты, осуществляется следующим образом. Из ВМ 25 (ВУ1) через соответствующий порт 23 (PCI 1) информация передается в АБ 21(ВУ1) и далее через порт 22 (PCI 0) в ВМ 24 (ВУ1).

Передача информации между вычислительными узлами, у которых координаты отличаются только в первом измерении, происходит следующим образом. Информация из ВМ источника одного ВУ через соответствующий PCI порт 23 или 22 передается в его АБ, затем через соответствующий сетевой порт этого АБ информация передается в соответствующий сетевой порт АБ другого ВУ, а затем через соответствующий PCI порт 22 или 23 в ВМ приемник. Например, передача информации из ВМ 25, расположенного в ВУ1, в ВМ 24, расположенный в ВУ3, имеющих координаты, отличающиеся только в первом измерении, осуществляется следующим образом. Из ВМ 25 (ВУ1) через соответствующий порт 23 (PCI 1) информация передается в АБ 21(ВУ1), далее через сетевой порт 2 этого АБ21(ВУ1) информация передается в сетевой порт 1 АБ21(ВУ3) и далее через порт 22 (PCI 0) в ВМ 24 (ВУ3).

Передача информации между вычислительными узлами, у которых координаты отличаются либо только во втором, либо только в третьем, либо только в четвертом измерениях, происходят следующим образом. Информация из ВМ источника одного ВУ через соответствующий PCI порт 23 или 22 передается в его АБ, затем через соответствующий данному измерению сетевой порт этого АБ информация передается в соответствующий сетевой порт соответствующего КБ, из которого через соответствующий сетевой порт передается в соответствующий сетевой порт АБ другого ВУ, а затем через соответствующий PCI порт 22 или 23 в ВМ приемник. Например, передача информации из ВМ 24 (ВУ1) в ВМ 25 (ВУ9), имеющих координаты, отличающиеся только во втором измерении, осуществляется следующим образом. Из ВМ 24 (ВУ1) через соответствующий порт 22 (РСI0) информация передастся в АБ21(ВУ1), далее через сетевой порт 8 этого АБ21(ВУ1) информация передается в сетевой порт 1 КБ 17, далее через его сетевой порт 3 в сетевой порт8 АБ21(ВУ9), и далее через соответствующий порт 23 (РСI21) в ВМ 25 (ВУ9).

Передача информации между вычислительными узлами, у которых координаты отличаются в нескольких измерениях, происходят следующим образом. Информация из ВМ источника одного ВУ через соответствующий PCI порт 23 или 22 передается в его АБ, в котором происходит сравнение координат текущего ВУ и ВУ приемника. Сравнение начинается с первого по порядку измерения. Если не совпали значения координат в первом измерении, то через соответствующий сетевой порт этого АБ информация передается в соответствующий сетевой порт АБ другого ВУ. Иначе, если не совпали значения координат для второго, или третьего, или четвертого измерения, то через соответствующий данному измерению сетевой порт этого АБ информация передается в соответствующий сетевой порт соответствующего КБ, из которого через соответствующий сетевой порт передается в соответствующий сетевой порт АБ другого ВУ. В достигнутом АБ снова происходит процесс сравнения координат уже этого текущего ВУ и ВУ приемника. Процесс передачи информации от ВУ к ВУ повторяется, пока координата достигнутого ВУ не совпадает с координатой ВУ приемника тогда через соответствующий PCI порт 22 или 23 адаптерного блока информация будет отправлена в ВМ приемник. Например, передача информации из ВМ 24 (ВУ1) в ВМ 24 (ВУ11), имеющих координаты, отличающиеся в двух измерениях, осуществляется следующим образом. Из ВМ 24 (ВУ1) через соответствующий порт 22(РСI0) информация передается в АБ21(ВУ1), далее порт 2 этого АБ21(ВУ1) информация передается в сетевой порт 1 АБ21(В3). В АБ21(ВУ3) происходит через сетевой смена измерения передачи информации, через сетевой порт 8 этого АБ21(ВУ3) информация передается в сетевой порт 1 КБ 19, далее через его сетевой порт 3 в сетевой порт 8 АБ 21(ВУ11) и далее через порт 22 соответствующего РСI0 в ВМ 24(ВУ11).

| название | год | авторы | номер документа |

|---|---|---|---|

| МУЛЬТИПРОЦЕССОРНАЯ СИСТЕМА | 2015 |

|

RU2614926C2 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2017 |

|

RU2677363C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2022 |

|

RU2798443C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С МНОГОУРОВНЕВОЙ ПОДСИСТЕМОЙ МОНИТОРИНГА И УПРАВЛЕНИЯ | 2018 |

|

RU2699254C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2019 |

|

RU2713757C1 |

| КЛАСТЕРНАЯ СИСТЕМА С ПРЯМОЙ КОММУТАЦИЕЙ КАНАЛОВ | 2011 |

|

RU2461055C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С МНОГОУРОВНЕВОЙ ПОДСИСТЕМОЙ МОНИТОРИНГА И АВТОМАТИЧЕСКИМ УПРАВЛЕНИЕМ | 2020 |

|

RU2748454C1 |

| Высокопроизводительная вычислительная платформа на базе процессоров с разнородной архитектурой | 2016 |

|

RU2635896C1 |

| ВЕКТОРНОЕ ВЫЧИСЛИТЕЛЬНОЕ ЯДРО | 2023 |

|

RU2819403C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ | 2018 |

|

RU2686004C1 |

Изобретение относится к области вычислительной техники и коммуникационных систем. Техническим результатом является увеличение пропускной способности вычислительной сети за счет уменьшения ее диаметра. Технический результат достигается за счет того, что вычислительная сеть организуется таким образом, при котором вычислительные узлы, включающие адаптерный блок и один или несколько вычислительных модулей с арифметическими процессорами, располагаются ортогонально от одного до четырех измерений. Связь между вычислительными узлами, находящимися в первом измерении происходит с помощью адаптерных блоков, объединенных двунаправленными каналами связи по полносвязной топологии без использования коммутаторных блоков. В других измерениях вычислительные узлы и соответствующие им адаптерные блоки объединяются с помощью коммутаторных блоков или с помощью коммутаторных сборок, представляющих собой набор коммутаторных блоков. 5 ил.

Вычислительная сеть высокопроизводительной вычислительной системы, содержащая вычислительные узлы, каждый из которых включает адаптерный блок и Μ вычислительных модулей, включающих арифметические процессоры, где Μ=1, 2, …, при этом вычислительные узлы расположены ортогонально по N измерениям, где N=1, 2, …, в каждом измерении расположены до К вычислительных узлов, где К=2, 3, …, вычислительные узлы, расположенные в одном измерении, кроме первого измерения, соединены между собой посредством соединения соответствующих им сетевых портов соответствующих адаптерных блоков через соответствующие сетевые порты соответствующего коммутаторного блока или соответствующей коммутаторной сборки, отличающаяся тем, что в первом измерении вычислительные узлы соединены между собой по полносвязной топологии посредством соединения двунаправленными каналами связи соответствующих сетевых портов соответствующих адаптерных блоков.

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Токарный резец | 1924 |

|

SU2016A1 |

| МНОГОПРОЦЕССОРНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2012 |

|

RU2502126C1 |

Авторы

Даты

2021-09-03—Публикация

2020-12-28—Подача