ОБЛАСТЬ ТЕХНИКИ

Настоящее техническое решение относится к области компьютерных сетей, а именно к технологиям передачи информации через сеть, в частности, к способу организации сетевого процессорного устройства.

УРОВЕНЬ ТЕХНИКИ

Указанный способ организации сетевого процессорного устройства позволяет передавать информацию в программно-конфигурируемых сетях на скорости, необходимой для работы в режиме многопортовой коммутации на уровне агрегации сети. Одной из основных проблем при работе в программно-конфигурируемых сетях является необходимость настройки на новые протоколы передачи данных. Представленное изобретение предлагает одно из возможных решений указанной проблемы. Сетевое процессорное устройство, разработанное на основе предложенного способа организации сетевого процессорного устройства, может использоваться в сетевых коммутаторах и маршрутизаторах.

Из уровня техники известен источник информации US 7,715,449 B1, опубликованный 11.05.2010, раскрывающий систему для сохранения порядка передачи пакетов, где сетевое устройство включает буфер данных планирования для временного хранения информации о пакете, соответствующий каждому из множества принятых пакетов, буфер данных планирования для хранения информации о пакете для одного из принятых пакетов на основе времени отправки для принятых пакетов и планировщик для сохранения порядка прохождения пакетов через устройство, путем определения времени отправки для каждого из полученных пакетов и планирования принятых пакетов для передачи в соответствующие моменты времени отправки, планировщик определяет время отправки одного из полученных пакетов на основе отметки времени окончания одного пакета.

Из уровня техники известен источник информации US 7,8264,69 B1, опубликованный 02.11.2010, раскрывающий способ использования памяти в сетевых устройствах. Заявленный способ содержит шаги, на которых принимают входящие сетевые пакеты с помощью сетевого устройства. Назначают сетевым устройством сетевые пакеты одной из множества очередей приоритета FIFO, поддерживаемых сетевым устройством, на основе одной или нескольких характеристик приоритета сетевых пакетов. Записывают сетевые пакеты в буфер записи, связанный с приоритетной очередью. Назначают первую из множества страниц памяти одной из очередей приоритетов, которым были назначены сетевые пакеты, при этом каждая из множества страниц памяти содержит блок непрерывного адресного пространства памяти; считывают сетевые пакеты из буфера записи. Сохраняют каждый сетевой пакет из буфера записи на первую страницу памяти в порядке FIFO путем последовательной записи сетевых пакетов в том порядке, в котором были приняты сетевые пакеты, в последовательные ячейки памяти на первой странице памяти. Создают метаданные для каждого из сетевых пакетов, при этом метаданные содержат ссылку на ячейку памяти на первой странице памяти соответствующего сетевого пакета. Ставят метаданные для каждого из сетевых пакетов в приоритетную очередь.

Предлагаемое решение отличается от известных из уровня техники тем, что осуществляют обработку заголовков пакетов в программируемом многостадийном конвейере с фиксированным временем исполнения стадий, а также в предлагаемом решении присутствует возможность сокращения времени коммутации путем отключения стадий.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Технической проблемой, на решение которой направлено заявленное решение, является создание способа и системы организации сетевого процессорного устройства, которые охарактеризованы в независимых пунктах формулы. Дополнительные варианты реализации настоящего изобретения представлены в зависимых пунктах изобретения.

Технический результат заключается в обеспечении сохранения разметки произвольных сетевых транспортных протоколов, без снижения значения пропускной способности сетевого процессорного устройства.

Заявленный результат достигается за счет работы способа организации сетевого процессорного устройства, содержащий этапы, на которых:

посредством буферизирующего логического устройства входной очереди принимают по меньшей мере один сетевой пакет, осуществляют подсчет и проверку циклических контрольных сумм, передают по меньшей мере один сетевой пакет в разделитель памяти;

в разделителе памяти отделяют заголовок от неизменяемых данных по меньшей мере одного сетевого пакета и отправляют заголовок и метаданные по меньшей мере одного сетевого пакета в вычислительный конвейер, неизменяемые данные по меньшей мере одного сетевого пакета отправляют в основную память;

в вычислительном конвейере обрабатывают заголовок по меньшей мере одного сетевого пакета и его метаданные, при этом вычислительный конвейер работает в одном из режимов, где первый режим заключается в обработке заголовка по меньшей мере одного сетевого пакета по полям и его изменение в соответствии с актуальными правилами обработки пакетов, а второй режим - в операции копирования состояния памяти предыдущего блока вычислительного конвейера в память следующего блока или в буфер исходящей очереди;

в буфер исходящей очереди заголовков, поступает заголовок по меньшей мере одного сетевого пакета, буфер исходящей очереди осуществляет отправку метаданных заголовка по меньшей мере одного сетевого пакета в планировщик отправки и осуществляет запись заголовка по меньшей мере одного сетевого пакета, разделенного по времени, в основную память;

в планировщик отправки поступает сигнал о наличии в буфере исходящей очереди заголовка по меньшей мере одного сетевого пакета, планировщик отправки определяет очередность отправки и осуществляет отправку заголовка по меньшей мере одного сетевого пакета в основную память;

в основной памяти осуществляют конкатенацию неизменяемых данных и полученного заголовка по меньшей мере одного сетевого пакета и отправляют полученный по меньшей мере один сетевой пакет в по меньшей мере одно буферизирующее логическое устройство выходной очереди;

по меньшей мере одно буферизирующее логическое устройство выходной очереди передает полученный сетевой пакет на MAC-интерфейсы.

В частном варианте реализации предлагаемого способа, нахождение по меньшей мере одного сетевого пакета в буферизирующем логическом устройстве входной очереди зависит от размера сетевого пакета и от состояния вычислительного конвейера.

В другом частном варианте реализации предлагаемого способа, нахождение по меньшей мере одного сетевого пакета в буферизирующем логическом устройстве выходной очереди зависит от размера сетевого пакета.

В другом частном варианте реализации предлагаемого способа, в случае несоответствия контрольной суммы буферизирующее логическое устройство сбрасывает сетевой пакет.

В другом частном варианте реализации предлагаемого способа, по меньшей мере: размер сетевого пакета, размер заголовка сетевого пакета, отметка времени, идентификатор входного порта сетевого пакета, идентификаторы выходных портов, резерв.

В другом частном варианте реализации предлагаемого способа, вычислительный конвейер состоит из по меньшей мере одного вычислительного блока, имеющего тактово-детерминистическую модель работы с памятью и со стадиями вычислительного конвейера.

В другом частном варианте реализации предлагаемого способа, на выходе из конвейера сетевой пакет сбрасывают, если метаданные обрабатываемого заголовка сетевого пакета не содержат информацию об идентификаторах выходных портов в соответствующем поле.

В другом частном варианте реализации предлагаемого способа, способ дополнительно содержит этап, на котором заголовок по меньшей мере одного сетевого пакета, после обработки вычислительным конвейером отправляют на повторную обработку.

В другом частном варианте реализации предлагаемого способа, способ дополнительно содержит этап, на котором отправляют заголовок по меньшей мере одного сетевого пакета после обработки вычислительным конвейером ко внешним системам управления.

Заявленный технический результат также достигается за счет системы организации сетевого процессорного устройства, содержащей:

по меньшей мере одно буферизирующее устройство входной очереди;

разделитель памяти;

вычислительный конвейер;

интерфейс записи в основную память;

основную память;

буфер исходящей очереди;

планировщик отправки;

управляющий порт;

по меньшей мере одно буферизирующее устройство выходной очереди.

ОПИСАНИЕ ЧЕРТЕЖЕЙ

Реализация изобретения будет описана в дальнейшем в соответствии с прилагаемыми чертежами, которые представлены для пояснения сути изобретения и никоим образом не ограничивают область изобретения. К заявке прилагаются следующие чертежи:

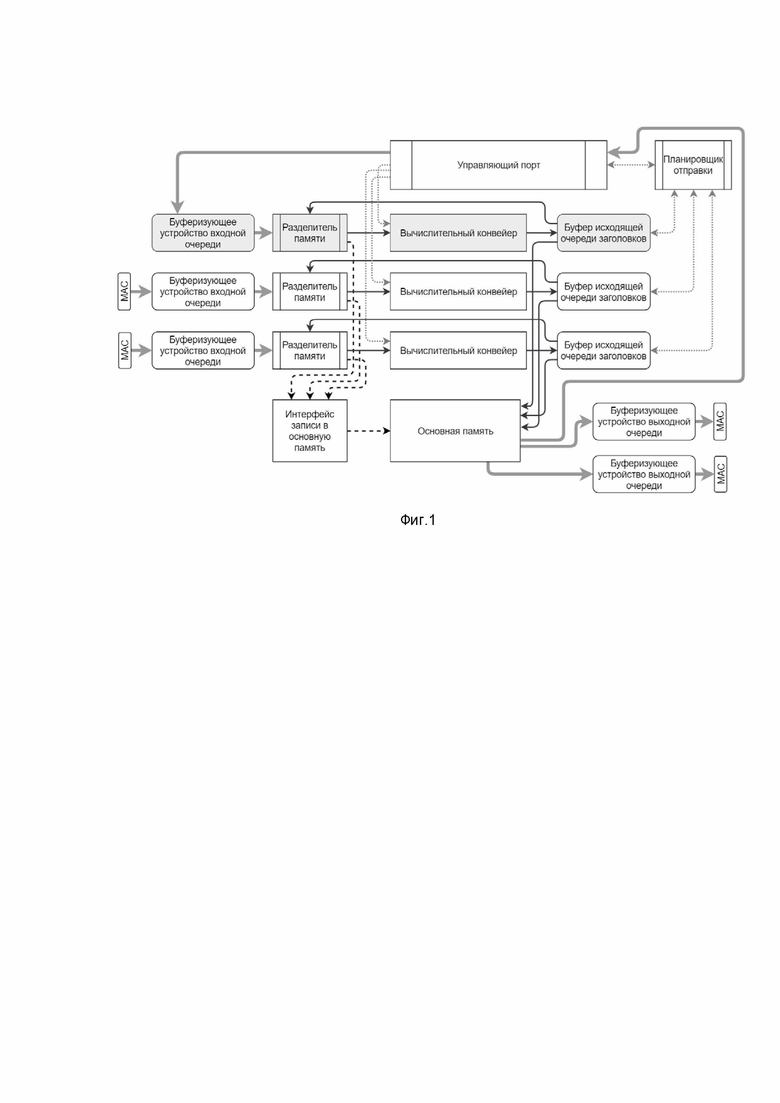

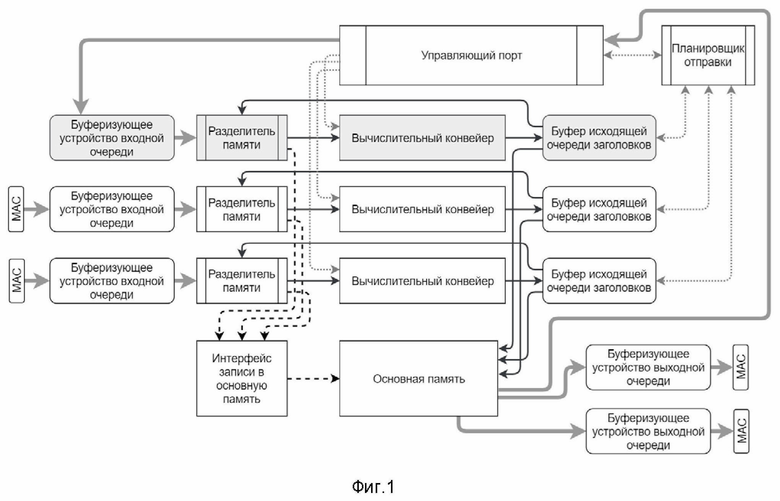

Фиг.1, иллюстрирует структурную схему организации сетевого процессорного устройства.

ДЕТАЛЬНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

В приведенном ниже подробном описании реализации изобретения приведены многочисленные детали реализации, призванные обеспечить отчетливое понимание настоящего изобретения. Однако, квалифицированному в предметной области специалисту, будет очевидно каким образом можно использовать настоящее изобретение, как с данными деталями реализации, так и без них. В других случаях хорошо известные методы, процедуры и компоненты не были описаны подробно, чтобы не затруднять излишне понимание особенностей настоящего изобретения.

Кроме того, из приведенного изложения будет ясно, что изобретение не ограничивается приведенной реализацией. Многочисленные возможные модификации, изменения, вариации и замены, сохраняющие суть и форму настоящего изобретения, будут очевидными для квалифицированных в предметной области специалистов.

Предлагаемое решение позволяет поддерживать разметку произвольных сетевых транспортных протоколов, в том числе не принятых к формализации на настоящий момент без снижения значения пропускной способности изделия.

Предлагаемое решение позволяет организовать обработку заголовков пакетов в программируемом конвейере с фиксированным временем исполнения стадий, а также присутствует возможность сокращения времени коммутации путем отключения стадий.

На каждой стадии конвейера имеется локальная память команд, содержащая в том числе таблицы и поисковые структуры внутри микрокода, при этом большие поисковые структуры могут быть распределены по стадиям конвейера. Вычислительные элементы стадий могут быть функционально не специализированы, иметь одинаковый набор команд. При такой организации, время работы устройства предсказуемо и позволяет провести, неблокирующее работу сетевого процессорного устройства, обновление микрокода и таблиц поиска с хост-системы (например, модуль управления коммутатора, маршрутизатора).

Предлагаемый способ организации сетевого процессорного устройства осуществляется за счет системы организации сетевого процессорного устройства, проиллюстрированной на Фиг.1 и содержащей следующие логические блоки: по меньшей мере одно буферизирующее устройство входной очереди; разделитель памяти; вычислительный конвейер; интерфейс записи в основную память; основную память; буфер исходящей очереди; планировщик отправки; управляющий порт; по меньшей мере одно буферизирующее устройство выходной очереди.

Посредством буферизирующего логического устройства входной очереди принимают по меньшей мере один сетевой пакет, осуществляют подсчет и проверку циклических контрольных сумм, посредством имеющейся в нем группы арифметико-логических устройств с собственной памятью микрокоманд и передают по меньшей мере один сетевой пакет в разделитель памяти. Время нахождения пакета в буферизирующем логическом устройстве входной очереди зависит от размера пакета и от состояния конвейера (обновление микрокода/нормальные операции).

В разделителе памяти отделяют заголовок от неизменяемых данных по меньшей мере одного сетевого пакета и отправляют заголовок и метаданные по меньшей мере одного сетевого пакета в вычислительный конвейер, неизменяемые данные по меньшей мере одного сетевого пакета отправляют в основную память.

Под отделение заголовка пакета от неизменимых данных (тела пакета) понимается смещения фиксированного размера, определяемого в рамках обновления микрокода.

В качестве метаданных выступает битовая строка, содержащая, например, следующую информацию: размер пакета, размер заголовка пакета, отметка времени, идентификатор входного порта пакета, идентификаторы выходных портов или иную связанную информацию, а также резерв, в том числе для нужд разработчика программы обработки пакетов (конечный автомат микрокода). Часть метаданных имеет неопределенное (нулевое) значение на данном этапе обработки, например, идентификаторы выходных портов пакета. Метаданные связаны с заголовком пакета на протяжении обработки в вычислительном конвейере и нахождении в буфере исходящей очереди заголовков.

Вычислительный конвейер обрабатывает полученный заголовок по меньшей мере одного сетевого пакета и его метаданные. Вычислительные блоки вычислительного конвейера обладают набором команд, позволяющих осуществлять обработку сетевых пакетов (например, имеют архитектуру RISC). Вычислительные блоки имеют тактово-детерминистичную модель работы с памятью и со стадиями вычислительного конвейера.

Вычислительный конвейер работает двух режимах. Первый режим заключается в разборе заголовка по меньшей мере одного сетевого пакета по полям и его изменении в соответствии с актуальными правилами обработки пакетов. Программа (в виде микрокода), находящаяся в памяти стадии конвейера и выполняемая ей, представляет собой правила обработки пакетов. Обновление микрокода в соответствии с описанной ниже процедурой меняет программу. Если обновление микрокода стадии начинается после обработки текущего пакета, актуальными все же для него будут правила “старой”, еще не обновленной программы. Для пакета, обрабатываемого стадией после процедуры обновления микрокода, актуальными будут “новые” правила. Второй режим заключается в операции копирования состояния памяти предыдущего блока вычислительного конвейера в память следующего блока или в буфер исходящей очереди. Данный режим способствует уменьшению времени прохождения конвейера обрабатываемым элементом пакета (заголовком) за счет изменения функционирования блоков вычислительного конвейера, а именно приостановки обработки заголовка.

Неизменяемые данные по меньшей мере одного сетевого пакета отправляют в основную память посредством интерфейса записи в основную память. Интерфейс записи в основную память является счетчиком/аллокатором свободных ячеек памяти в основной памяти и интерфейсом записи в основную память, при записи неизменяемого содержимого пакета в основную память интерфейс записи возвращает упорядоченную последовательность адресов, соответствующую ячейкам, в которых размещаются элементы пакета, добавляемые в метаданные заголовка. Освобождение ячеек происходит при сигнализировании основной памятью адреса ячейки после пересылки ее содержимого в один или несколько выходных портов основной памяти.

Из вычислительного конвейера заголовок поступает в буфер исходящей очереди заголовков, который осуществляет отправку метаданных заголовка по меньшей мере одного сетевого пакета в планировщик отправки и осуществляет запись заголовка по

меньшей мере одного сетевого пакета, разделенного по времени, в основную память.

Далее в планировщик отправки поступает сигнал о наличии в буфере исходящей очереди заголовка по меньшей мере одного сетевого пакета, планировщик отправки определяет очередность отправки пакетов на основе метаданных о пересылаемых пакетах и осуществляет отправку заголовка по меньшей мере одного сетевого пакета в основную память. Очередность отправки определяется в соответствии с выбранным алгоритмом планирования очередей. Планировщик отправки позволяет менять алгоритм планирования очередей.

Основная память осуществляет хранение неизменяемых тел пакетов, конкатенацию (склеивание) тела пакета и заголовка после окончания обработки последнего и передачу сформированного пакета в одну или несколько выходных очередей. Основную память следует рассматривать, как реализацию in-memory switch, адресация со стороны разделителя памяти и буфера исходящей очереди осуществляется поячеечно, размер ячейки фиксирован и составляет 256 байт.

сетевой пакет на MAC-интерфейсы. Время нахождение по меньшей мере одного сетевого пакета в буферизирующем логическом устройстве выходной очереди зависит от размера сетевого пакета.

Управляющий порт является интерфейсом к внешней, относительно сетевого процессорного устройства, системе с процессором общего назначения (например, модуль управления коммутатора, маршрутизатора) и выполняет функции обновления микрокода вычислительного конвейера, пересылки пакетов в MAC-интерфейс системы общего назначения, сбора статистики и контроля жизненного цикла периферии микросхемы.

Каждому физическому порту ставится в соответствие вычислительный конвейер. Это означает, что для каждого MAC-интерфейса ресивера физического порта имеется буферизующее устройство входной очереди, разделитель памяти, вычислительный конвейер и буфер исходящей очереди заголовков. С другой стороны, для каждого MAC-интерфейса трансивера физического порта имеется буферизующее устройство выходной очереди.

Сетевое процессорное устройство может иметь дополнительный конвейер, предназначенный для обработки трафика, введённого через MAC-интерфейс управляющего порта, не имеющего соответствия физическим портам сетевого процессорного устройства (Фиг. 1, дополнительный конвейер выделен цветом). По характеристикам этот конвейер не отличается от конвейеров обработки, соответствующих входным портам. В варианте исполнения сетевого процессорного устройства без дополнительного конвейера трафик, введённый через управляющий порт, может обрабатываться в одном из конвейеров.

Загрузка микрокода в вычислительный конвейер может осуществляться без остановки конвейера. В рамках обработки фиктивного заголовка, обрабатываемого конвейером через периодические промежутки времени (например, в тактах), заголовок пакета по конвейеру не передается, однако зарезервирован интервал времени (например, в тактах), равный или меньший времени обработки настоящего заголовка пакета. Обновление микрокода (перезапись микрокода стадий) осуществляется во время обработки фиктивного пакета. Таким образом, стадии конвейера обновляют микрокод последовательно, что позволяет избежать остановки конвейера или сброса пакетов.

Далее будут расписаны примеры работы сетевого процессорного устройства.

Пример 1. Сетевой пакет поступает через MAC-интерфейс в буферизующее устройство входной очереди. В случае выявления ошибок, таких как несовпадение контрольной суммы, устройство может сбросить пакет на данном этапе обработки. Далее пакет поступает в разделитель памяти, осуществляющий отделение заголовка пакета и его отправку в вычислительный конвейер, тело пакета передается в основную память. Вычислительный конвейер выполняет обработку заголовка пакета в соответствии с актуальными правилами обработки пакетов (конечным автоматом в микрокоде конвейера). На выходе из конвейера пакет может быть сброшен, если метаданные, ассоциированные с обрабатываемым заголовком пакета, не содержат информацию об идентификаторах портов, на которые необходимо отправить пакет. Иначе - заголовок пакета поступает из вычислительного конвейера в буфер исходящей очереди заголовков. Планировщик отправки получает сигнал о наличии в буфере заголовка пакета и идентификаторах его выходных портов. В соответствии с построенным планировщиком расписанием отправки, заголовок пакета передается из буфера исходящей очереди заголовков в основную память, где происходит конкатенация с ранее отделенным телом пакета и дальнейшая передача пакета в буферизующие устройства выходных очередей, соответствующие портам, на которые необходимо отправить обрабатываемый пакет. Буферизующие устройства выходных очередей передают пакет на MAC-интерфейс.

Пример 2. Отправка заголовка пакета после прохождения вычислительного конвейера на повторную обработку (рециркуляция, или разворот пакета) в вычислительном конвейере.

Связанные с заголовком метаданные могут содержать особое поле, позволяющее сигнализировать о необходимости отправки на повторную обработку заголовка пакета (например, зарезервированный идентификатор выходного порта). В случае установки такого поля (выходного порта рециркуляции) в вычислительном конвейере заголовок и связанные метаданные передаются из буфера исходящей очереди заголовков в разделитель памяти одного из конвейеров, например, того же самого конвейера. При данной процедуре основная память, получив сигнал о рециркуляции, может выполнять дополнительные операции, например, дублирование тела обрабатываемого пакета. Разделитель памяти повторно передает заголовок пакета и связанные метаданные в вычислительный конвейер. При данной процедуре следует сохранять значения метаданных заголовка, какими они были при поступлении в буфер исходящей очереди заголовков, кроме, идентификаторов выходных портов.

Пример 3. Отправка заголовка пакета после прохождения вычислительного конвейера ко внешней системе управления (например, модуль управления коммутатора, маршрутизатора).

Связанные с заголовком метаданные могут содержать особое поле, позволяющее сигнализировать о необходимости отправки заголовка пакета после прохождения вычислительного конвейера ко внешней системе управления (например, зарезервированный идентификатор выходного порта). В случае установки такого поля (выходного порта управления) основная память передает пакет внешней системе управления через MAC-интерфейс управляющего порта.

В настоящих материалах заявки было представлено предпочтительное раскрытие осуществление заявленного технического решения, которое не должно использоваться как ограничивающее иные, частные воплощения его реализации, которые не выходят за рамки испрашиваемого объема правовой охраны и являются очевидными для специалистов в соответствующей области техники.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ДАННЫХ С ВОЗМОЖНОСТЬЮ ОСУЩЕСТВЛЕНИЯ ВЗАИМОДЕЙСТВИЯ С OpenFlow КОНТРОЛЛЕРОМ | 2014 |

|

RU2584471C1 |

| СПОСОБ РАСПРЕДЕЛЕНИЯ НАГРУЗКИ В МНОГОЯДЕРНОЙ СИСТЕМЕ | 2017 |

|

RU2703188C1 |

| УПРАВЛЯЮЩЕЕ УСТРОЙСТВО И СПОСОБ УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПОТОКА ВИДЕОДАННЫХ ПО СЕТИ НА СЕТЕВОЕ ПОЛЬЗОВАТЕЛЬСКОЕ УСТРОЙСТВО | 2013 |

|

RU2571732C2 |

| Пакетная сеть для мультипроцессорных систем и способ коммутации с использованием такой сети | 2018 |

|

RU2703231C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ВЫЧИСЛИТЕЛЬНЫМИ УСТРОЙСТВАМИ УСКОРИТЕЛЯ ВЫВОДА НЕЙРОННЫХ СЕТЕЙ | 2024 |

|

RU2832408C1 |

| БУФЕРИЗАЦИЯ ВОСПРОИЗВЕДЕНИЯ В СИСТЕМЕ РАСПРЕДЕЛЕНИЯ КОНТЕНТА, ТРАНСЛИРУЕМОГО В ПРЯМОМ ЭФИРЕ | 2017 |

|

RU2745113C2 |

| ФИЛЬТРАЦИЯ И МАРШРУТИЗАЦИЯ ФРАГМЕНТИРОВАННЫХ ДЕЙТАГРАММ В СЕТИ ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2363108C2 |

| КОНВЕЙЕР ОБРАБОТКИ СООБЩЕНИЙ ДЛЯ ПОТОКОВ | 2004 |

|

RU2363982C2 |

| ЧАСТНЫЕ ПСЕВДОНИМЫ КОНЕЧНЫХ ТОЧЕК ДЛЯ ИЗОЛИРОВАННЫХ ВИРТУАЛЬНЫХ СЕТЕЙ | 2015 |

|

RU2669525C1 |

| СПОСОБ ВЕРОЯТНОСТНОГО ВЗВЕШЕННОГО СПРАВЕДЛИВОГО ОБСЛУЖИВАНИЯ ОЧЕРЕДЕЙ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 2022 |

|

RU2777035C1 |

Изобретение относится к области компьютерных сетей. Технический результат заключается в обеспечении сохранения разметки произвольных сетевых транспортных протоколов без снижения значения пропускной способности сетевого процессорного устройства. Посредством буферизирующего логического устройства входной очереди принимают по меньшей мере один сетевой пакет, осуществляют подсчет и проверку циклических контрольных сумм, передают по меньшей мере один сетевой пакет в разделитель памяти. В разделителе памяти отделяют заголовок от неизменяемых данных по меньшей мере одного сетевого пакета и отправляют заголовок и метаданные по меньшей мере одного сетевого пакета в вычислительный конвейер, неизменяемые данные по меньшей мере одного сетевого пакета отправляют в основную память. В вычислительном конвейере обрабатывают заголовок по меньшей мере одного сетевого пакета и его метаданные, при этом вычислительный конвейер работает в одном из режимов, где первый режим заключается в обработке заголовка по меньшей мере одного сетевого пакета по полям и его изменение в соответствии с актуальными правилами обработки пакетов, а второй режим - в операции копирования состояния памяти предыдущего блока вычислительного конвейера в память следующего блока или в буфер исходящей очереди. В буфер исходящей очереди заголовков поступает заголовок по меньшей мере одного сетевого пакета, буфер исходящей очереди осуществляет отправку метаданных заголовка по меньшей мере одного сетевого пакета в планировщик отправки и осуществляет запись заголовка по меньшей мере одного сетевого пакета, разделенную по времени, в основную память. В планировщик отправки поступает сигнал о наличии в буфере исходящей очереди заголовка по меньшей мере одного сетевого пакета, планировщик отправки определяет очередность отправки и осуществляет отправку заголовка по меньшей мере одного сетевого пакета в основную память. В основной памяти осуществляют конкатенацию неизменяемых данных и полученного заголовка по меньшей мере одного сетевого пакета и отправляют полученный по меньшей мере один сетевой пакет в по меньшей мере одно буферизирующее логическое устройство выходной очереди. Буферизирующее логическое устройство выходной очереди передает полученный сетевой пакет на MAC-интерфейсы. 2 н. и 8 з.п. ф-лы, 1 ил.

1. Способ работы сетевого процессорного устройства, содержащий этапы, на которых:

посредством буферизирующего логического устройства входной очереди принимают по меньшей мере один сетевой пакет, осуществляют подсчет и проверку циклических контрольных сумм, передают по меньшей мере один сетевой пакет в разделитель памяти;

в разделителе памяти отделяют заголовок от неизменяемых данных по меньшей мере одного сетевого пакета и отправляют заголовок и метаданные по меньшей мере одного сетевого пакета в вычислительный конвейер, неизменяемые данные по меньшей мере одного сетевого пакета отправляют в основную память;

в вычислительном конвейере обрабатывают заголовок по меньшей мере одного сетевого пакета и его метаданные, при этом вычислительный конвейер работает в одном из режимов, где первый режим заключается в обработке заголовка по меньшей мере одного сетевого пакета по полям и его изменение в соответствии с актуальными правилами обработки пакетов, а второй режим - в операции копирования состояния памяти предыдущего блока вычислительного конвейера в память следующего блока или в буфер исходящей очереди;

в буфер исходящей очереди заголовков поступает заголовок по меньшей мере одного сетевого пакета, буфер исходящей очереди осуществляет отправку метаданных заголовка по меньшей мере одного сетевого пакета в планировщик отправки и осуществляет запись заголовка по меньшей мере одного сетевого пакета, разделенного по времени, в основную память;

в планировщик отправки поступает сигнал о наличии в буфере исходящей очереди заголовка по меньшей мере одного сетевого пакета, планировщик отправки определяет очередность отправки и осуществляет отправку заголовка по меньшей мере одного сетевого пакета в основную память;

в основной памяти осуществляют конкатенацию неизменяемых данных и полученного заголовка по меньшей мере одного сетевого пакета и отправляют полученный по меньшей мере один сетевой пакет в по меньшей мере одно буферизирующее логическое устройство выходной очереди;

по меньшей мере одно буферизирующее логическое устройство выходной очереди передает полученный сетевой пакет на MAC-интерфейсы.

2. Способ по п.1, отличающийся тем, что время нахождения по меньшей мере одного сетевого пакета в буферизирующем логическом устройстве входной очереди зависит от размера сетевого пакета и от состояния вычислительного конвейера.

3. Способ по п.1, отличающийся тем, что время нахождения по меньшей мере одного сетевого пакета в буферизирующем логическом устройстве выходной очереди зависит от размера сетевого пакета.

4. Способ по п.1, отличающий тем, что в случае несоответствия контрольной суммы буферизирующее логическое устройство сбрасывает сетевой пакет.

5. Способ по п.1, отличающийся тем, что метаданные содержат, по меньшей мере: размер сетевого пакета, размер заголовка сетевого пакета, отметку времени, идентификатор входного порта сетевого пакета, идентификаторы выходных портов, резерв.

6. Способ по п.1, отличающийся тем, что вычислительный конвейер состоит из по меньшей мере одного вычислительного блока, имеющего тактово-детерминистическую модель работы с памятью и со стадиями вычислительного конвейера.

7. Способ по п.1, отличающийся тем, что на выходе из конвейера сетевой пакет сбрасывают, если метаданные обрабатываемого заголовка сетевого пакета не содержат информацию об идентификаторах выходных портов в соответствующем поле.

8. Способ по п.1, дополнительно содержащий этап, на котором заголовок по меньшей мере одного сетевого пакета после обработки вычислительным конвейером отправляют на повторную обработку.

9. Способ по п.1, дополнительно содержащий этап, на котором отправляют заголовок по меньшей мере одного сетевого пакета после обработки вычислительным конвейером к внешним системам управления.

10. Сетевое процессорное устройство, осуществляющее способ по пп.1-9, содержащее:

по меньшей мере одно буферизирующее устройство входной очереди;

разделитель памяти;

вычислительный конвейер;

интерфейс записи в основную память;

основную память;

буфер исходящей очереди;

планировщик отправки;

управляющий порт;

по меньшей мере одно буферизирующее устройство выходной очереди.

| US 7826469 B1, 02.11.2010 | |||

| US 7715449 B1, 11.05.2010 | |||

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| СЕТЕВОЕ УСТРОЙСТВО, ТЕРМИНАЛЬНОЕ УСТРОЙСТВО И СВЯЗАННЫЕ С НИМИ СПОСОБЫ | 2018 |

|

RU2731769C1 |

Авторы

Даты

2021-09-23—Публикация

2020-10-08—Подача