Изобретение относится к микроэлектронике и предназначено для использования в схемных решениях и топологиях интегральных микросхем контроллеров запоминающих устройств, предназначенных для управления операциями чтения и записи многоканальных микросхем флеш памяти, предназначенных для долговременного энергонезависимого хранения данных (NAND).

Твердотельные накопители (ТНИ или SSD) привлекают внимание разработчиков как системы памяти, оснащенные флэш-памятью (flash EEPROM), в качестве внешних накопителей используемых вычислительными системами.

Флэш-память имеет такие преимущества, как высокая скорость обмена данными, а также пониженный вес, по сравнению с магнитным диском.

Типовой SSD включает в себя несколько микросхем флэш-памяти, контроллер, который управляет чтением и записью соответствующих микросхем флэш-памяти в ответ на запрос от главного устройства, например, стационарного компьютера, буферную память для обслуживания процесса передачи данных между соответствующими микросхемами флэш-памяти и главным устройством, цепи управления питанием и интерфейс подключения к главному устройству (хосту).

При проектировании твердотельного накопителя, в том числе и накопителей, в которых может быть использовано предложенное изобретение, как правило, используется многослойная реализация, в которой, для увеличения удельной емкости памяти, используется несколько кристаллов микросхем памяти, например, в виде многослойной сборки, в то время как площадь площадок для выводов контроллера и для монтажных площадок ограничена.

При использовании синхронного контроллера данные, считываемые из памяти, могут фиксироваться и выводиться в состоянии низкой нагрузки (при небольшом количестве буферов данных); однако в состоянии высокой нагрузки (при большом количестве буферов, заполненных считанными данными) данные, считанные из памяти, могут не фиксироваться и не выводиться из-за задержки данных, вызванной задержкой, обусловленной затратами времени на арбитраж доступа к кристаллам в сборках и отдельным микросхемам (корпусам) на шинах ONFI (TOGGLE).

Для декодирования информации, поступающей из каналов, используются аппаратные декодеры. В современных ТНИ используются LDPC-Декодеры. Отличительными особенностями LDPC-Декодеров являются:

- высокая пропускная способность;

- малая площадь / малое энергопотребление.

В указанном выше многослойном продукте для каждого модуля отдельно могут использоваться выделенные шины данных, адресов и управления, а также шины питания, которые располагаются внутри кристалла. Нагрузка соответствующих шин повышается с увеличением количества кристаллов памяти, например, в многослойной сборке, а при увеличении нагрузки соответствующих сигнальных линий увеличивается задержка сигналов ввода-вывода из-за задержек, вызванных повышением емкости и активного сопротивления самих линий передачи данных. Кроме того, современных ТНИ пропускная способность физического интерфейса Хост-ТНИ (например, PCIe 3.0) значительно превосходит пропускную способность отдельной микросхемы NAND-флеш памяти. В связи с этим в ТНИ используются одновременно несколько микросхем NAND-флеш памяти, объединенных в так называемые каналы. Процедуры Записи и Чтения, при этом, выполняются параллельно по нескольким каналам. Отдельный канал обычно содержит от 1 до 8 микросхем NAND-флеш памяти. Использование одного канала передачи данных практически нецелесообразною так как для скорость передачи данных существенно ограничивается.

Недостатком известных декодеров, используемых в ТНИ, является отсутствие оптимизации производительности обработки информации, в связи с невозможностью равномерного распределения загруженности нескольких, не привязанных к микросхемам памяти LDPC декодеров, при работе с несколькими микросхемами NAND-флеш памяти.

Например, патент США US2018175885 описывает аппаратный декодер, использующий общую энергозависимую память для промежуточных преобразований содержимого ячеек, а также общую схему декодирования данных для нескольких ячеек памяти.

Существенным недостатком указанного решения является необходимость использования общего адресного пространства для хранения содержимого ячеек, а также использование одного канала и одного декодера для передачи данных к хосту. Такая конфигурация может повысить скорость обработки данных только при использовании нескольких контроллеров параллельно.

Использование выделенных для групп ячеек каналов для обработки данных повышает скорость работы, однако может понизить стабильность при одновременном использовании всех каналов, за счет повышения энергопотребление и увеличения емкостных и резистивных задержек. Повышенное электропотребление может привести к преждевременному выходу из строя накопителей информации.

Таким образом, в уровне техники существует необходимость в оптимизации распределения загруженности каналов при выполнении операций записи-считывания с учетом возможности возникновения ошибок, а также необходимости стирания данных в ячейках перед выполнением операций записи, при выполнения указанных операций на физических устройствах. При этом несколько параллельно функционирующих каналов NAND-флеш памяти должны быть оптимизированы таким образом, чтобы обеспечивалась максимальная возможная скорость чтения и записи информации.

Дополнительно, одна микросхема контроллера ТНИ в различных вариантах исполнения ТНИ должна обеспечивать универсальное взаимодействие Хоста с различными наборами микросхем NAND-флеш памяти. Устранение недостатков уровня техники является задачей настоящего изобретения.

Техническим результатом, достигаемым при реализации изобретения является решение указанных выше задач, устранение недостатков уровня техники и повышение эффективности работы ТНИ за счет равномерного распределения загруженности входящих в него NAND-флеш памяти при операциях чтения и записи, возможности параллельного выполнения указанных ниже служебных операций, в том числе сборки мусора и валидации ячеек, повышение надежности ТНИ, в котором используется предложенное изобретение.

Заявленный результат обеспечивается за счет того, что при выполнении аппаратного декодирования содержимого твердотельного накопителя информации, содержащего n>1 независимых блоков памяти, выделяют n аппаратных каналов записи-считывания данных и m < n, независимых аппаратных декодеров, реализующих один и тот же процесс декодирования блоков данных, где значение данных от каждого из блоков передается через один из каналов записи-считывания к одному из независимых выделенных блоков памяти, с формированием, до завершения передачи, сигнала занятости канала, участвующего в процессе записи или считывания данных,

при поступлении запроса от внешней системы на считывание данных логического сектора данных, определяют адрес блока, соответствующего логическому сектору, и, после выделения адреса внешней памяти, предназначенной для записи значения логического сектора, инициализируют процесс считывания данных по запросу, для чего определяют физический блок, хранящий данные запрошенного логического сектора данных, выделяют независимый физический блок непосредственно адресуемой памяти для записи значения блока, при наличии свободного канала, выбирают и занимают свободный канал, выделяют свободный аппаратный декодер, формируют запрос на передачу данных из определенного физического блока к выделенной памяти с использованием свободного канала из определенного физического блока, где данные содержат данные, считанные из блока и проверочную сумму, и

А. определяют правильность контрольной суммы с использованием выбранного аппаратного декодера, имеющего непосредственный доступ к выделенной памяти, содержащей значение данных и контрольной суммы,

B. по результатам завершения вычисления и проверки контрольной суммы, возвращают результат считывания внешней системе и освобождают выделенный канал.

При несовпадении контрольной суммы с вычисленной контрольной суммой, перед выполнение операции В, в частном случае реализации способа изменяют физические параметры считывания данных из блока и повторно считывают из блока с использованием канала, после чего повторно выполняют операцию А, при этом .в частном случае задают заранее заданное количество физических параметров считывания данных, и при несовпадении контрольных сумм после перебора всех заданных физических параметров считывания данных, возвращают код ошибки и помечают бок как не валидный.

В частном случае, используют аппаратное вычисление строки контрольной суммы с использованием выделенного декодера и последующее аппаратное сравнение вычисленной строки контрольной суммы со значением контрольной суммы с использованием логики выделенного декодера.

При этом аппаратный способ вычисления контрольной суммы может быть задан в матричном виде с использованием независимой перезаписываемой энергонезависимой памяти. В частном случае способ реализуется аппаратным контроллеров, в котором m равняется ближайшему целому от n, умноженного на 0,6 – 0,8.

В другом частном случае, при наличии свободного канала и отсутствии запросов, осуществляется сбор мусора, а контроллер может быть выполнен инициирующим и осуществляющим сбор мусора при отсутствии запроса на считывание.

Кроме того, 11 в качестве физических параметров считывания данных могут быть использованы мягкие значения, при этом используется блок формирования мягких значений, содержащий, по меньшей мере, два независимых модуля формирования мягких значений, каждый из которых служит для изменения мягких значений и их записи в блоки внешней памяти, выделенные соответствующим блокам памяти, с обеспечением возможности использования сформированных мягких значений соответствующим декодером при декодировании данных соответствующего блока памяти.

Наличие нескольких модулей в блоке памятей для хранения секторов, в контроллере декодеров и LDPC-декодеров позволяют управляющему блоку декодера контроллера ТНИ обеспечивать равномерное распределения загруженности входящих в него NAND-флеш памяти при операции чтения.

Все модули контроллеров каналов и модули памяти могут быть выполнен ы независимыми, в связи с чем одновременно все n каналов могут осуществлять передачу данных в любом выбранном направлении.

В одном из вариантов декодер контроллера твердотельного накопителя информации, дополнительно содержащий блок формирования мягких значений, имеющий, по меньшей мере два, независимых модулей формирования мягких значений, каждый из которых служит для запоминания, в каких трех модулях памяти блока памятей для хранения секторов сохранены данные его сектора, может быть соединен двухсторонней связью для управляющих команд с управляющим блоком и контроллером декодеров.

В немеханических запоминающих устройствах на основе микросхем NAND-флеш памяти (далее, твердотельный накопитель информации - ТНИ) используется несколько отдельных микросхем NAND-флеш памяти. Они предназначены для хранения пользовательских данных.

Современные ТНИ взаимодействуют с хостом через специализированные логические и физические интерфейсы. В современных ТНИ используется физический интерфейс PCIe 3.0 и логический интерфейс – NVMe. При этом микросхемы NAND-флеш памяти используют иные физические и логические интерфейсы, зачастую отличающиеся у различных производителей.

Контроллер ТНИ, в частности, обеспечивает выполнение следующих операций:

- Операция записи. При данной операции пользовательские данные перемещаются от Хоста через контроллер ТНИ в набор микросхем NAND-флеш памяти. При этом, в процессе обработки данных контроллером ТНИ, данные подвергаются процедуре помехоустойчивого кодирования. Процедура помехоустойчивого кодирования выполняется с помощью аппаратных блоков – кодеров. В состав контроллера ТНИ может входить несколько кодеров.

- Операция чтения. При этой операции данные извлекаются из элементов набора микросхем NAND-флеш памяти, далее обрабатываются контроллером ТНИ и передаются к хосту. При обработке контроллером ТНИ, данные декодируются с помощью аппаратных блоков - декодеров. В состав контроллера ТНИ может входить несколько Декодеров. При декодировании в данных исправляются возможные ошибки, возникшие в процессе записи, хранения, чтения и передачи информации внутри ТНИ.

Стандартными логическими интерфейсами взаимодействия с микросхемами NAND-флеш памяти являются интерфейсы ONFI и Toggle. Чтобы Контроллер ТНИ мог поддерживать работу с микросхемами NAND-флеш памяти от различных производителей в состав Контроллера ТНИ входят специализированные аппаратные блоки - NAND-Каналы, которые преобразуют различные интерфейсы микросхем NAND-флеш памяти к единому логическому интерфейсу Канала.

Обычно Контроллеры ТНИ проектируются так, чтобы на их основе можно было изготовить различные варианты ТНИ, отличающиеся по объему и быстродействию. Зачастую это достигается путем включения/отключения некоторых из Каналов.

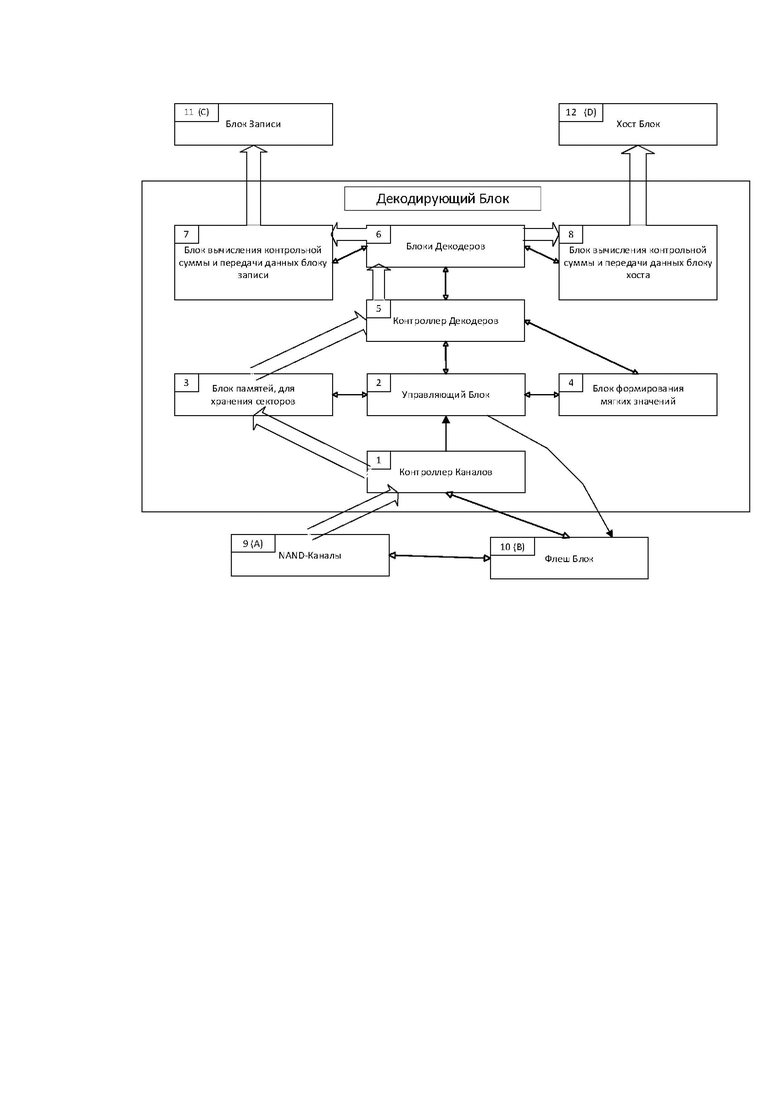

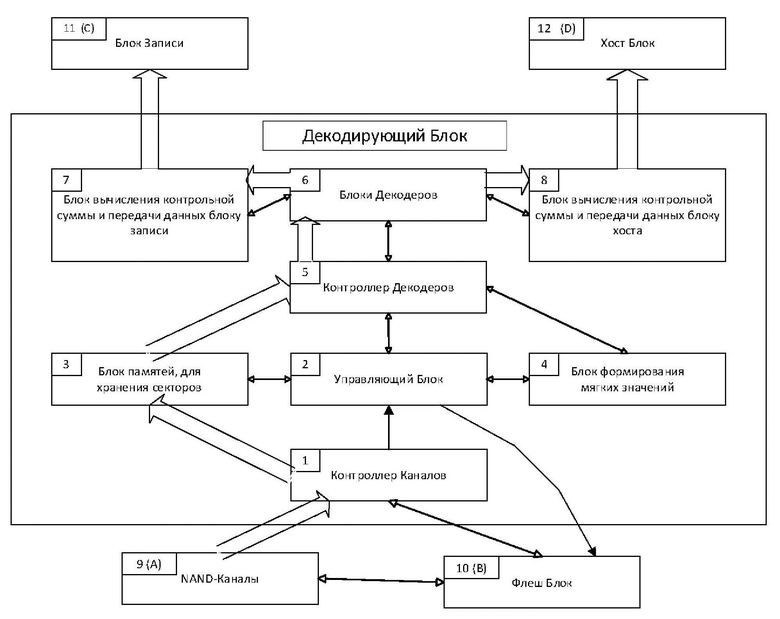

На фигуре представлена блок-схема декодирующего блока, где цифрами показаны: 1 – контроллер каналов, 2 – управляющий блок, 3 – блок памятей или внешняя память для промежуточного хранения данных секторов, а также служебных сведений, относящихся к секторам, например, мягкие значения, используемые для декодирования. Позицией 4 обозначен блок формирования мягких значений, 5 – контроллер декодеров или центральное управляющее устройство, предназначенное для согласования работы отдельных блоков, включая блок записи, а также для управления интерфейсами обмена данными с хостом. Позицией 6 обозначен блок декодеров, 7 – блок вычисления контрольной суммы при записи и передаче данных блоку записи, 8 – блок вычисления контродьной суммы считанных данных и передачи контрольной суммы блоку хоста, 9 – блок А или NAND каналы, 10 – блок В или флеш блок, 10 – блок С или блок записи и 11 – блок D или блок считывания.

На фигуре узкими стрелками обозначаются управляющие команды, а широкими стрелками – каналы или процессы передачи данных.

Далее будет подробно описано предлагаемое изобретение с примером его реализации. Выполненные курсивом в латинице условные обозначения относятся к аппаратным интерфейсам обмена данными и интерпретируют логические параметры, значения которых определяются параметрами сигналов, формирующихся в соответствующих электрических цепях аппаратных блоков. Выполненные прописными латинскими буквами обозначения характеризуют блоки данных, обрабатываемые и формируемые в процессе взаимодействия блоков устрйства, реализующего предложенный способ.

Работа декодера контроллера ТНИ может быть охарактеризована, как следующая задача: дано n – NAND-Каналов, которые поставляют данные для декодирования, и m – Декодеров, которые декодируют эти данные, где n > m. Производительность n Каналов приблизительно равна производительности m Декодеров. Необходимо обеспечить бесперебойную работу Декодеров так, чтобы при этом все Каналы обслуживались равномерно.

Блок A представляет собой NAND-Контроллеры. Из него данные поступают в декодирующий блок (блок контроллера ТНИ).

Блок B управляет всеми n Каналами и передает Декодирующему Блоку информацию о наличии на Каналах данных для декодирования. Помимо этого Блок B формирует все необходимые команды для NAND-Контроллеров.

Допустим n=8. Порция данных, предназначенная для декодирования, равна длине кодового слова и называется сектором. Имеется 2 режима декодирования: жесткий и мягкий. При жестком декодировании сектор считывается с NAND-Контроллера один раз, при мягком декодировании сектор считывается 3 раза с разными порогами чтения, и за счет этого формируются мягкие значения LLR. Для каждого из Каналов блок B передает Декодирующему Блоку информацию о секторе, состоящую из следующих полей: флаг ready_to_decode, говорящий, что на Канале есть сектор, который надо декодировать; psa – физический адрес сектора, который надо декодировать; from_gc – флаг, означающий, что сектор поступает от сборщика мусора; cur_bit_num – число говорящее, который раз считывается сектор, может принимать значения 0, 1, или 2 в зависимости от того первый, второй или третий раз считывается данный сектор; last_bit_num – будет равен 2, если это мягкое декодирование, и равен 0 – если жесткое декодирование.

Блок С осуществляет обратную запись на диск секторов от сборщика мусора.

Блок D передает Хосту прочитанные сектора.

В режиме жесткого декодирования используется блок 3, состоящий состоит из k независимых модулей памяти, каждый из которых может сохранить в себе 1 сектор. В нашем случае k=18. Каждый модуль памяти может быть свободным и занятым. Каждый модуль памяти имеет флаг mem_free, говорящий, что модуль памяти свободный, и выставляет его управляющему блоку 2.

Блок 1 состоит из n модулей, каждый из которых обслуживает свой канал. Каждый из этих модулей передает информацию о своем канале управляющему блоку 2. Если управляющий блок 2 обнаруживает флаги ready_to_decode (готов к декодированию), т.е. если имеются каналы, которые хотят обратиться к декодеру, и если имеются свободные модули памяти, то управляющий блок выбирает по кругу один канал и один модуль памяти и связывает их друг с другом. В модуле памяти запоминается и хранится информация о секторе с выделенного ему канала. После этого выбранный модуль канала начинает перекачку данных с NAND в выделенный модуль памяти. Поскольку ширина элемента памяти шире, чем ширина поступающих от NAND данных, то модуль Канала сначала накапливает данные до нужной ширины, и уже потом записывает в память. Все модули каналов 2 и модули памяти независимые, поэтому одновременно все n Каналов могут осуществлять перекачку данных. Когда перекачка сектора в память завершена, модуль канала освобождается, и информация о завершении перекачки передается в блок B, одновременно модуль памяти поднимает флаг ready (готов), показывающий, что в этом модуле памяти хранится готовый к декодированию сектор.

Блок 5 содержит m модулей декодера, каждый из которых обслуживает свой декодер. В блоке 6 содержатся m независимых декодеров, например, LDPC-декодеров (декодеров с low-density parity-check или с кодом с малой плотностью проверок на чётность). В нашем случае m =2. Декодер может быть свободным и занятым. Модуль декодера передает состояние своего Декодера управляющему блоку через флаг dec_free (свободный декодер). Если управляющий блок 2 обнаруживает готовый к декодированию сектор в памяти и свободный декодер, то он выбирает в цикле готовый модуль памяти и свободный модуль декодера и связывает их друг с другом. Модуль декодера запоминает информацию сектора с выделенного ему модуля памяти. Выбранный модуль декодера запускает процесс декодирования на своем декодере. В процессе декодирования Декодер запрашивает у модуля декодера начальные значения LLR (тест отношения правдоподобия или likelihood ratio test) в удобном для него порядке. Модуль декодера извлекает информацию из выделенного ему модуля памяти, формирует LLR и передает их декодеру. После загрузки всех начальных значений LLR декодер сообщает об этом своему модулю декодера, а модуль декодера передает эту информацию выделенному ему модулю памяти, после чего декодирование продолжается, а соответствующий модуль памяти освобождается с выставлением соответствующего флага.

Ответом каждого декодера является декодированный сектор, т.е. сектор с исправленными ошибками, и этот ответ формируется в специальном буфере ответа. У каждого декодера может иметься два таких буфера. Если декодирование завершилось неуспешно, то информация о неуспешном декодировании передается от модуля декодера через управляющий блок соответствующему каналу, с которого поступил сектор. Если декодирование завершилось успешно, и в первом буфере ответа сформировался декодированный сектор, декодер переключается на второй буфер ответа и начинает декодировать новый сектор, формируя ответ во втором секторе. При этом выставляется флаг, указывающий на то, что в буфере ответа есть готовый декодированный сектор и его нужно обработать. Если имеется декодированный сектор от сборщика мусора, то этот флаг выставляется блоку 7, в противном случае он выставляется блоку 8.

Блок 7, обнаружив декодированный сектор, при наличии свободной памяти, закачивает этот сектор в память. Одновременно с закачкой, модуль 7 вычисляет контрольную сумму. После закачки информационной части кодового слова, формируется контрольная сумма. Полученная контрольная сумма сравнивается с контрольной суммой, находящейся в метаданных данного сектора (некоторое количество первых бит кодового слова). Если эти контрольные суммы совпадают, то считается что слово декодировано правильно, и загруженный в память блока 7 сектор, передается блоку записи C. Информация о успешном декодировании перелается от модуля декодера через управляющий блок соответствующему каналу, с которого пришел этот сектор. После выгрузки сектора в память блока 7 соответствующий буфер ответа декодера становится свободным. Если контрольные суммы не совпали, то декодирование считается неуспешным и информация о неуспешном декодировании перелается от модуля декодера через управляющий блок соответствующему Каналу, с которого пришел этот сектор.

Блок 8, обнаружив декодированный сектор, обращается к блоку хоста D и просит выделить память под закачку сектора. После того как блок хоста D выделяет эту память, блок 8 начинает закачивать этот сектор из буфера ответа в выделенную память. При этом выкачивается только информационная часть кодового слова. Одновременно с закачкой модуль 8 вычисляет контрольную сумму. После закачки информационной части кодового слова контрольная сумма оказывается сформирована. Полученная контрольная сумма сравнивается с контрольной суммой, находящейся в метаданных данного сектора. Если эти контрольные суммы совпадают, то считается что слово декодировано правильно. Информация о успешном декодировании передается от модуля декодера через управляющий блок соответствующему Каналу, с которого пришел этот сектор. После выгрузки сектора в выделенную память блока хоста D соответствующий буфер ответа Декодера становится свободным. Если контрольные суммы не совпали, то декодирование считается неуспешным и информация о неуспешном декодировании перелается от модуля декодера через управляющий блок соответствующему Каналу, с которого пришел этот сектор.

Если Декодер завершил декодирование, но видит, что второй буфер ответа еще не освободился, то он переходит в состояние простоя, и выходит из этого состояния только тогда, когда этот буфер ответа освободится. Декодер, находящийся в состоянии простоя считается занятым. Таким образом Декодер считается свободным, если он не находится в процессе декодирования и у него есть свободный буфер ответа.

В режиме мягкого декодирования используется блок 4. Этот блок состоит из q независимых модулей формирования мягких значений, каждый из которых служит для запоминания, в каких трех модулях памяти были сохранены данные его сектора. В нашем случае q=2. Каждый из этих модулей может быть свободным или занятым и сообщает о своем состоянии управляющему блоку 2 с помощью флага soft_free.

Если управляющий блок 2 видит, что есть Каналы, у которых last_bit_num=2 (т.е. этот Канал хочет выполнить мягкое декодирование), есть свободный модуль формирования мягких значений и свободный модуль памяти, то управляющий блок выбирает по кругу один из модулей Канала, которые хотят выполнить мягкое декодирование, выбирает один из свободных модулей формирования мягких значений и один из свободных модулей памяти, и связывает выбранный модуль формирования мягких значений с выбранным Кана лом. Модуль формирования мягких значений запоминает информацию о секторе выбранного Канала и номер выбранного модуля памяти. После этого начинается процесс перекачки данных с Канала в модуль памяти. По завершении перекачки Канал обращается к NAND за следующим чтением этого сектора с новыми пороговыми значениями, и после завершения этого чтения опять поднимает флаг готовности сектора ready_to_decode, но при этом уже будет cur_bit_num=1. Управляющий блок в приоритетном порядке выделяет этому Каналу модуль памяти, который запоминается в выделенном модуле формирования мягких значений. После этого опять закачивается сектор с Канала в память. И по завершении скачивания запрашивается следующее значением сектора и по его готовности поднимается флаг ready_to_decode с cur_bit_num=2. Управляющий блок опять в приоритетном порядке выделяет этому Каналу модуль памяти, который запоминается в выделенном модуле формирования мягких значений. После этого опять закачивается сектор с Канала в память. И по завершении третьего скачивания модуль Канала считается свободным, а выбранный модуль формирования мягких значений поднимает флаг ready, который передает управляющему блоку 2.

Управляющий блок, видя флаг ready от модуля формирования мягких значений, дожидается, когда освободиться Декодер и связывает освободившийся модуль декодера с готовым модулем формирования мягких значений.

Модуль декодера запоминает информацию сектора с выделенного ему модуля формирования мягких значений. Выбранный модуль декодера запускает процесс декодирования на своем Декодере. В процессе декодирования Декодер запрашивает у модуля декодера начальные значения LLR в удобном для него порядке. Для формирования начальных значений LLR модуль декодера извлекает информацию сразу из трех модулей памяти, соответствующих выбранному модулю формирования мягких значений. После загрузки всех начальных значений LLR Декодер сообщает об этом своему модулю декодера, а модуль декодера передает эту информацию выделенному ему модулю формирования мягких значений, после чего этот модуль формирования мягких значений памяти становится свободным и становятся свободными все три модуля памяти, соответствующих данному модулю формирования мягких значений.

Дальнейший процесс декодирования полностью аналогичен режиму жесткого декодирования.

В качестве Хоста, упомянутого в описании, подразумевается вышестоящее по иерархии управляющее звено. Им может быть микропроцессор, сервер и т.п. устройство.

Далее описан порядок выполнения основных операций, реализуемых Декодирующим блоком.

Операции, реализуемые Декодирующим Блоком

Включение

При включении устройства Декодирующий Блок получает сигнал INIT, который переводит модуль в начальное состояние. Кроме того, после включения устройства на модуль приходят сигналы

1) WORD_LEN - количество порций данных сектора, поступающих от канала, минус 1;

2) COL_NUM - равен количеству столбцов в LDPC матрице минус 1;

3) SHORTENNING_SHIFT - равен количеству дополняющих бит (уверенных нулей) в первом стобце матрицы;

4) PUNCTURING_SHIFT - равен количеству невыколотых бит в первом выколотом столбце матрицы;

5) BEG_ADR - адрес в памяти команд LDPC декодера, где начинается программа обработки, текущей LDPC матрицы; в случае если в память команд загружена только одна матрица, то этот сигнал равен 0;

6) BEG2_ADR - адрес в памяти команд LDPC декодера, где начинается программа обработки второй и более итераций; дело в том, что при второй и более итерациях несколько первых команд не используются; как правило число неиспользуемых команд равно 7, и соответственно BEG2_ADR = BEG_ADR + 7;

7) LAST_ADR - адрес последней команды в памяти команд.

8) COL_INFO_BEG_ADR - адрес начала блока, относящегося у текущей LDPC матрице и содержащего информацию о непустых ячейках каждого их столбцов; в случае, если декодер ослуживает только одну матрицу, COL_INFO_BEG_ADR = 0;

9) LAST_ROW_NUM - число строк в текущей LDPC матрице минус 1;

10) LAST_EDGE_NUM - число непустых ячеек в текущей LDPC матрице минус 1;

11) SECOND_V2C_MEM_COL_BEG - количество столбцов в первой половине, текущей LDPC матрицы; Поскольку в LDPC декодере используется однопортовая память 1RW, в которую нельзя одновременно писать и читать, то чтобы обеспечить бесперебойную работу, матрица делится на две части и каждая часть обслуживается свои вычислителем;

12) LAST_ITER_NUM - максимальное число итераций минус 1.

Все перечисленные выше параметры автоматически вычисляются по LDPC матрице с помощью специальной инициализирующей программы. В частности, составляется расписание вычислений в процессе декодирования и это расписание сохраняется в памяти команд. Поэтому если память команд не является ROM, то расписание должно быть загружено в память команд каждого из декодеров до подачи сигнала INIT.

Выключение

При выключении устройства приходит сигнал SWITCH_OFF_MODE. Этот сигнал удерживается все время, пока устройство выключается. В процессе выключения устройства выполняются следующие действия:

1) Прекращается декодирование секторов для хоста.

2) Освобождаются блоки памяти, занятые секторами для хоста.

3) Освобождаются модули формирования софт значений, если они формируют софт значение для сектора для хоста.

4) После того как все декодеры и все модули памяти сообщают, что они свободны, и если при этом сигнал EVERYTHING_IS_READ поднят (это означает, что в флэш блоке нет страниц, которые еще надо декодировать), то модуль поднимает сигнал NO_MORE_SECTORS_FROM_GC (который означает, что больше секторов от сборщика мусора не поступит) и передает его блоку записи.

Взаимодействие с флеш блоком

Взаимодействие с каналами (а точнее с Флеш Блок) происходит следующим образом:

1) Декодирующий Блок отправляет флеш блоку сигналы READY_TO_GET_HARD и READY_TO_GET_SOFT, сообщая, что может принять сектор для декодирования с помощью хард значений и софт значений соответственно. Первый сигнал фактически говорит, что у Декодирующего Блока есть место в памяти для загрузки одного сектора, а второй сигнал, сообщает, что кроме того у Декодирующего Блока есть свободный модуль для формирования софт значений.

2) С помощью сигнала SECTOR_READY канал сообщает, что у него есть сектор для декодирования. На каждый канал свой сигнал SECTOR_READY. Вместе с этим сигналом приходят сигналы

а) HARD - индикатор, что ожидается хард декодирование. Фактически HARD = (BIT_NUM == 0) && (BIT_NUM_TO_DECODE == 0).

б) BIT_NUM - номер софт бита. Если 0, то - это хард бит, 1 - первый софт бит и т.д.

в) BIT_NUM_TO_DECODE - сколько софт бит планируется загрузить минус 1. Если BIT_NUM < BIT_NUM_TO_DECODE, то мы просто загружаем страницу в память модуля и декодировать будем позже. Если BIT_NUM = BIT_NUM_TO_DECODE, то после загрузки сектора декодируем сектор с учетом всех ранее загруженных бит.

г) FROM_GC - индикатор того, что сектор от сборщика мусора.

д) PPA - физический адрес страницы. Используется только если сектор от сборщика мусора.

е) SECTOR_NUM - номер сектора на странице. Используется только если сектор от сборщика мусора.

ж) TEMPERATURE - температура сектора. Используется только если сектор от сборщика мусора.

з) FROM_REPAIR_TO_DECODE - канал говорит, что читаемая страница от восстановителя супер-блоков.

и) REPAIR_PARITY_TO_DECODE - канал говорит, что читаемая страница от восстановителя супер-блоков принадлежит проверочному вею.

3) После получения от каналов сигналов SECTOR_READY Декодирующий Блок выбирает по кругу один из каналов и разрешает ему перекачку данных с помощью сигнала READY_TO_RECEIVE_DATA. При поступлении сигнала READY_TO_RECEIVE_DATA одному из каналов сигнал SECTOR_READY у данного канала опускается. Сигнал READY_TO_RECEIVE_DATA удерживается, пока от NAND контроллера не поступит первая порция данных.

4) Индикатором поступления данных от NAND контроллеров являются сигналы DATA_IN_PUSH. Сами данные поступают через входы DATA_IN.

5) После получения от NAND контроллера всего сектора Декодирующий Блок посылает флэш блоку сигнал DATA_TO_DECODE_FINISHED, который нужен чтобы освободить канал для других операций.

6) В момент первого поступления сигнала READY_TO_RECEIVE_DATA флэш блок может отменить передачу данных декодеру с помощью сигнала CANCEL_READ. Просто опустить сигнал SECTOR_READY недостаточно, поскольку реакция модуля Декодирующего Блока на сигнал запаздывает на 1 такт, и сигнал CANCEL_READ позволяет снять противоречия, которые могут возникнуть из-за этого запаздывания. Сигнал CANCEL_READ может появиться в двух случаях:

а) при выключении устройства, если передаваемые данные не являются повторным чтением сборщика мусора;

б) если для разрешения патовых ситуаций надо срочно пропустить на данный канал операцию записи, отменив при этом операцию чтения.

7) По завершении декодирования и проверки CRC Декодирующий Блок посылает флэш блоку, а точнее соответствующим каналам информацию об успешности декодирования с помощью сигналов DECODE_SUCCESS (декодирование завершилось успешно) и DECODE_FAIL (декодирование завершилось не успешно). Вместе с этими сигналами поступают сигналы:

а) PPA_TO_CHANNEL - физический адрес страницы;

б) SECTOR_NUM_TO_CHANNEL - номер декодированного или недекодированного сектора на странице.

в) FROM_GC_TO_CHANNEL - индикатор того, что декодированный или недекодированный сектор был от сборщика мусора.

г) FROM_REPAIR_TO_CHANNEL - говорит, что декодированный или недекодированный сектор от восстановителя. При неуспешном декодировании эта информация используется для формирования повторного чтения, а при успешном декодировании уменьшает счетчик обрабатываемых секторов блока-жертвы.

8) Если какой-то декодер простаивает, поскольку не может сбросить сектор от сборщика мусора в блок записи, то Декодирующий Блок посылает флэш блоку сигнал DECODER_IDLE, который информирует о возникновении патовой ситуации, и необходимости форсировать запись вордлайнов на NAND контроллеры.

Взаимодействие с блоком записи

Взаимодействие с блоком записи осуществляется следующим образом:

1) После того как декодеры декодировали сектор, он передается на блок вычисления контрольной суммы (CRC).

2) В момент, когда подсчитана контрольная сумма и если сектор не с проверочного вея, то поднимается флаг FIND_FOR_GC, который просит у блока записи узнать, есть ли в его памяти сектор с адресом LSA_FOR_GC.

3) На следующий такт приходит ответ от блока записи в виде сигнала NO_GC_SECTOR_NEEDED.

4) Если NO_GC_SECTOR_NEEDED = 1, то это означает, что в памяти блока записи уже имеется сектор с адресом LSA_FOR_GC, и, значит, он более актуальный, и, следовательно, данный декодированный сектор не нужен. Этот же сигнал NO_GC_SECTOR_NEEDED передается декодеру, и декодер освобождает память с данными данного сектора. При этом модуль CRC_CALC_FOR_GC_SECTOR прекращает обработку данного сектора.

5) Если NO_GC_SECTOR_NEEDED = 0 на следующий такт после сигнала FIND_FOR_GC, или если сигнал FIND_FOR_GC не посылался (сектор был с проверочного вея), то это означает, что в памяти блока записи нет сектора с адресом LSA_FOR_GC.

а) Тогда если контрольная сумма не сошлась, то декодирование считается неуспешным, о чем сообщается соответствующему каналу с помощью сигнала DECODE_FAIL, который мы описывали ранее.

б) Если контрольная сумма сошлась, то декодирование считается успешным, о чем сообщается соответствующему каналу с помощью сигнала DECODE_SUCCESS, который мы описывали ранее. В результате выгрузка проверочных бит сектора продолжается.

6) В случае 5 б) модуль CRC_CALC_FOR_GC_SECTOR просит у блока записи место для записи сектора с помощью сигнала GET_SECTOR_FOR_GC. При это он еще передает сигнал TEMPERATURE_FOR_GC, сообщая какой температуры нужен вордлайн. Если параметр синтеза superblock_repair включен, то кроме того выставляются сигналы:

а) WB_REPAIR_SECTOR - совзаимодействие блоку записи, что поступает сектор от восстановителя супер-блоков;

б) WB_REPAIR_PARITY - совзаимодействие блоку записи, что поступающий сектор с проверочного вея;

в) WB_REPAIR_SEC_NUM - номер сектора в вордлайне поступающего сектора.

7) В ответ блок записи выдает сигнал SET_SECTOR_FOR_GC. В результате сигнал GET_SECTOR_FOR_GC опускается, и можно начать запись сектора из внутренней памяти модуля Декодирующий Блок в память блока записи.

8) С этого момента начинается процесс выгрузки данных из внутренней памяти модуля Декодирующий Блок в память блока записи. Эта запись происходит с помощью сигналов BEFORE_WRITE_FROM_GC, WRITE_ADR_FROM_GC и WRITE_DATA_ FROM_GC. Причем сигналы BEFORE_WRITE_FROM_GC и WRITE_ADR_FROM_GC приходят одновременно, а сигнал WRITE_DATA_FROM_GC появляется на такт позже. Сигналы BEFORE_WRITE_FROM_GC должны приходить в строго определенные такты, которые случаются один раз в 4 такта. Т.е. WRITE_DATA_FROM_GC должны случаться в такты TIME_TO_WRITE_DATA_TO_WRITE_BLOCK.

9) Сразу после начала записи в блок записи поднимается флаг PUSH_INFO_FROM_GC, который загружает на регистры блока записи информацию о секторе, передаваемую через сигналы LSA_FROM_GC_OUT, GEN_PPA_OUT, CRC_FROM_GC_OUT, SYNC_PACKAGE_FROM_GC_OUT.

10) По окончании выгрузки сектора вместе с последним сигналом BEFORE_WRITE_FROM_GC приходит сигнал BEFORE_LAST_WRITE_FROM_GC, который информирует блок записи, что загрузка сектора завершена.

Взаимодействие с Хост Блоком

Взаимодействие с хост блоком осуществляется следующим образом:

1) Хост блок передает модулю Декодирующий Блок сигнал TIME_TO_WRITE_DATA_ TO_WRITE_BLOCK_3, с помощью которого Декодирующий Блок формирует сигналы BEFORE_WRITE_FROM_GC.

2) После декодирования сектора для хоста Декодирующий Блок посылает сигнал GET_SECTOR_FOR_HOST, который означает просьбу выделить память внутри хост блока под выгрузку декодированного сектора для хоста.

3) В ответ хост блок посылает сигнал SET_SECTOR_FOR_HOST, который означает, что память выделена, и сектор можно выгружать в хост блок.

4) С этого момента начинается процесс выгрузки данных из внутренней памяти модуля Декодирующего Блока в память хост блока. Эта запись происходит с помощью сигналов WRITE_FOR_HOST, WRITE_ADR_FOR_HOST и WRITE_DATA_FOR_HOST, которые приходят одновременно.

5) Одновременно с выгрузкой сектора идет вычисление CRC, и в момент, когда информационная часть загружена, появляется сигнал HOST_DATA_LOADED, и одновременно с этим сигналом может появиться сигнал HOST_CRC_ERROR, который означает, что контрольная сумма не сошлась. В этом случае соответствующему каналу флэш блока посылается сигнал DECODE_FAIL, а хост блок исключает из своей памяти загруженный сектор. Если же вместе с сигналом HOST_DATA_LOADED не пришел сигнал HOST_CRC_ERROR, то декодирование успешное и соответствующему каналу флэш блока посылается сигнал DECODE_SUCCESS, а хост блок принимает загруженный сектор и в дальнейшем этот сектор будет передан хосту.

6) Вместе сигналом HOST_DATA_LOADED хост блоку передаются сигналы LSA_FOR_HOST_OUT (используется для передачи хосту и SYNC_PACKAGE_ FOR_HOST_OUT (используется для расшифровки сектора.

Изобретение относится к компьютерной технике и предназначено для осуществления процесса декодирования цифровой информации, поступающей от нескольких независимых микросхем NAND-флеш памяти, в аппаратуре контроллера немеханических запоминающих устройств на основе микросхем NAND-флеш памяти. Техническим результатом является повышение эффективности работы ТНИ за счет равномерного распределения загруженности входящих в него NAND-флеш памяти при операции чтения. Декодер контроллера твердотельного накопителя информации для декодирования данных от n NAND-Каналов, содержащий управляющий блок, осуществляющий контроль работы входящих в декодер блоков, контроллер каналов, состоящий из n модулей, каждый из которых связан с определенным NAND-Каналом, блок памяти для хранения секторов, содержащий независимые модули памяти, контроллер декодеров, содержащий m модулей декодеров, где n>m, блок декодеров, содержащий m LDPC-декодеров, блок вычисления контрольной суммы и передачи данных блоку записи и блок вычисления контрольной суммы и передачи данных блоку хоста. 8 з.п. ф-лы, 1 ил.

1. Способ аппаратного ускорения декодирования содержимого твердотельного накопителя информации, заключающийся в том, что для твердотельного накопителя информации, содержащего n>1 независимых блоков памяти, выделяют n аппаратных каналов записи-считывания данных и m < n независимых аппаратных декодеров, реализующих один и тот же процесс декодирования блоков данных, где значение данных от каждого из блоков передается через один из каналов записи-считывания к одному из независимых выделенных блоков памяти, с формированием, до завершения передачи, сигнала занятости канала, участвующего в процессе записи или считывания данных,

при поступлении запроса от внешней системы на считывание данных логического сектора данных определяют адрес блока, соответствующего логическому сектору, и после выделения адреса внешней памяти, предназначенной для записи значения логического сектора, инициализируют процесс считывания данных по запросу, для чего определяют физический блок, хранящий данные запрошенного логического сектора данных, выделяют независимый физический блок непосредственно адресуемой памяти для записи значения блока, при наличии свободного канала выбирают и занимают свободный канал, выделяют свободный аппаратный декодер, формируют запрос на передачу данных из определенного физического блока к выделенной памяти с использованием свободного канала из определенного физического блока, где данные содержат данные, считанные из блока, и проверочную сумму, и

А. определяют правильность контрольной суммы с использованием выбранного аппаратного декодера, имеющего непосредственный доступ к выделенной памяти, содержащей значение данных и контрольной суммы,

B. по результатам завершения вычисления и проверки контрольной суммы возвращают результат считывания внешней системе и освобождают выделенный канал.

2. Способ по п. 1, отличающийся тем, что при несовпадении контрольной суммы с вычисленной контрольной суммой, перед выполнением операции В, изменяют физические параметры считывания данных из блока и повторно считывают из блока с использованием канала, после чего повторно выполняют операцию А.

3. Способ по п. 2, отличающийся тем, что задают заранее заданное количество физических параметров считывания данных, и при несовпадении контрольных сумм после перебора всех заданных физических параметров считывания данных возвращают код ошибки и помечают бок как невалидный.

4. Способ по п. 1, отличающийся тем, что используют аппаратное вычисление строки контрольной суммы с использованием выделенного декодера и последующее аппаратное сравнение вычисленной строки контрольной суммы со значением контрольной суммы с использованием логики выделенного декодера.

5. Способ по п. 1, отличающийся тем, что аппаратный способ вычисления контрольной суммы задается в матричном виде с использованием независимой перезаписываемой энергонезависимой памяти.

6. Способ по п. 1, отличающийся тем, что при наличии свободного канала и отсутствии запросов осуществляется сбор мусора.

7. Способ по п. 1, отличающийся тем, что выполняют контроллер инициирующим и осуществляющим сбор мусора при отсутствии запроса на считывание.

8. Способ по п. 1, отличающийся тем, что осуществляют динамическую привязку аппаратных каналов записи-считывания данных к блокам памяти.

9. Способ по п. 2, отличающийся тем, что в качестве физических параметров считывания данных используют мягкие значения, при этом используют блок формирования мягких значений, содержащий по меньшей мере два независимых модуля формирования мягких значений, каждый из которых служит для изменения мягких значений и их записи в блоки внешней памяти, выделенные соответствующим блокам памяти, с обеспечением возможности использования сформированных мягких значений соответствующим декодером при декодировании данных соответствующего блока памяти.

| Способ получения цианистых соединений | 1924 |

|

SU2018A1 |

| US 9135181 B2, 15.09.2015 | |||

| US 10387317 B2, 20.08.2019 | |||

| US 9235526 B2, 12.01.2016 | |||

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| ИСПОЛЬЗОВАНИЕ ВНЕШНИХ УСТРОЙСТВ ПАМЯТИ ДЛЯ УЛУЧШЕНИЯ ПРОИЗВОДИТЕЛЬНОСТИ СИСТЕМЫ | 2005 |

|

RU2395115C2 |

Авторы

Даты

2022-04-04—Публикация

2021-04-19—Подача