Изобретение относится к декодированию с низкой плотностью проверки четности, технике моделирования и может быть использовано при цифровом моделировании характеристик помехоустойчивых низкоплотностных декодеров с использованием архитектуры перекрывающегося декодирования.

Известна архитектура декодера, описанная в патенте Китая «QC-LDPC decoder, method for performing layered decodinгенg and storage device», US 10581460 B2, МПК H03M 13/11, опубл. 03.03.2020. Способ декодирования включает в себя: деление проверочной матрицы закодированного сообщения QC-LDPC на M уровней, где M является положительным целым числом.

Недостатком способа является то, что для реализации декодера тактовая частота для синхронизации строительных блоков применена ко всему декодеру, что увеличивает энергопотребление декодера и может вызывать конфликт доступа к памяти.

Наиболее близким по своей технической сущности к заявленному способу является способ, описанный в патенте США «Low-latency segmented quasi-cyclic low-density parity-check (QC-LDPC) decoder», US 11,575,390 B2, МПК H03M 13/11, МПК H03M 13/00, опубл. 07.02.2023. Способ декодирования включает в себя: сегментирование матрицы QC-LDPC с использованием реконфигурируемых сдвиговых регистров для обработки данных с низкой задержкой. Сегментированный QC-LDPC декодер с низкой задержкой использует конфигурацию объединения ребер между переменными узлами (VN) и контрольными узлами (CN) одного или нескольких блоков контрольных узлов декодера QC-LDPC.

Недостатком способа является то, что для реализации циклических сдвигов в декодере требует увеличения аппаратных ресурсов с увеличением длины кодового слова и может вызывать конфликт доступа к памяти, из-за чего также увеличивается и время задержки.

Техническим результатом является уменьшение аппаратных ресурсов и уменьшение задержки чтения/записи при организации памяти и оптимизации энергопотребления. Перекрывающееся декодирование в структурных блоках декодера позволяет увеличить пропускную способность без ухудшения других параметров декодера, в частности его производительности исправления ошибок.

Сущность изобретения.

Решаемой технической задачей изобретения является уменьшение задержки передачи данных и уменьшение аппаратных ресурсов декодера при неизменном энергопотреблении.

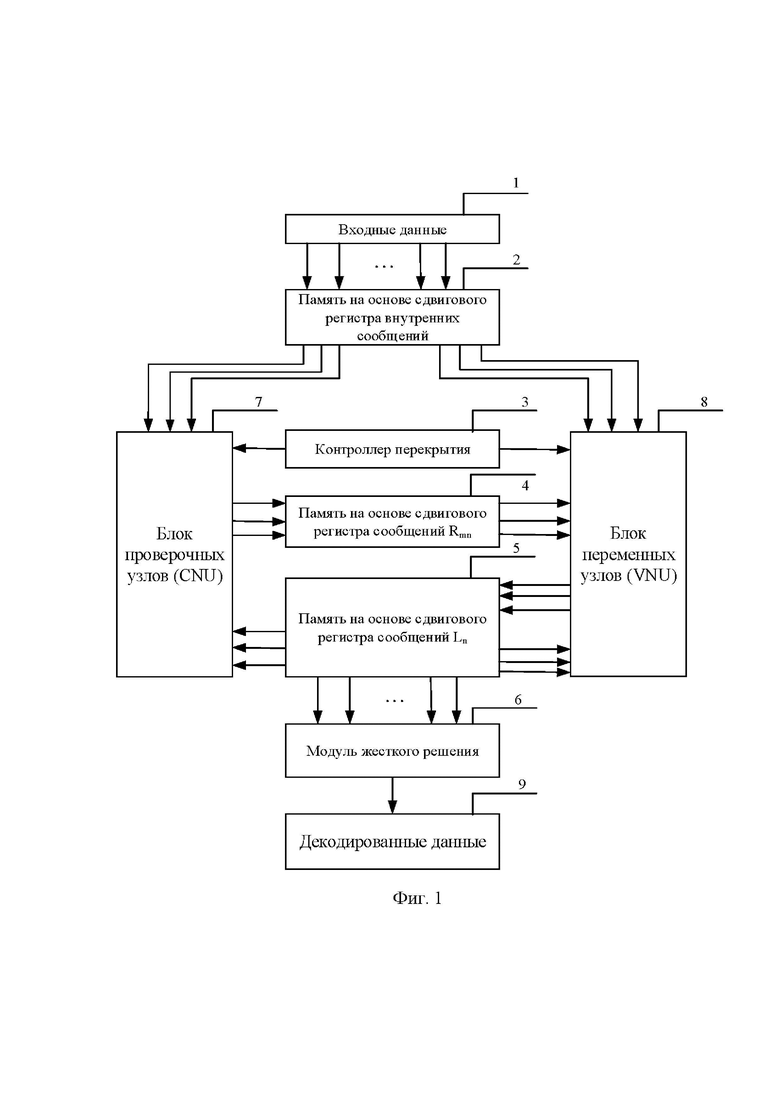

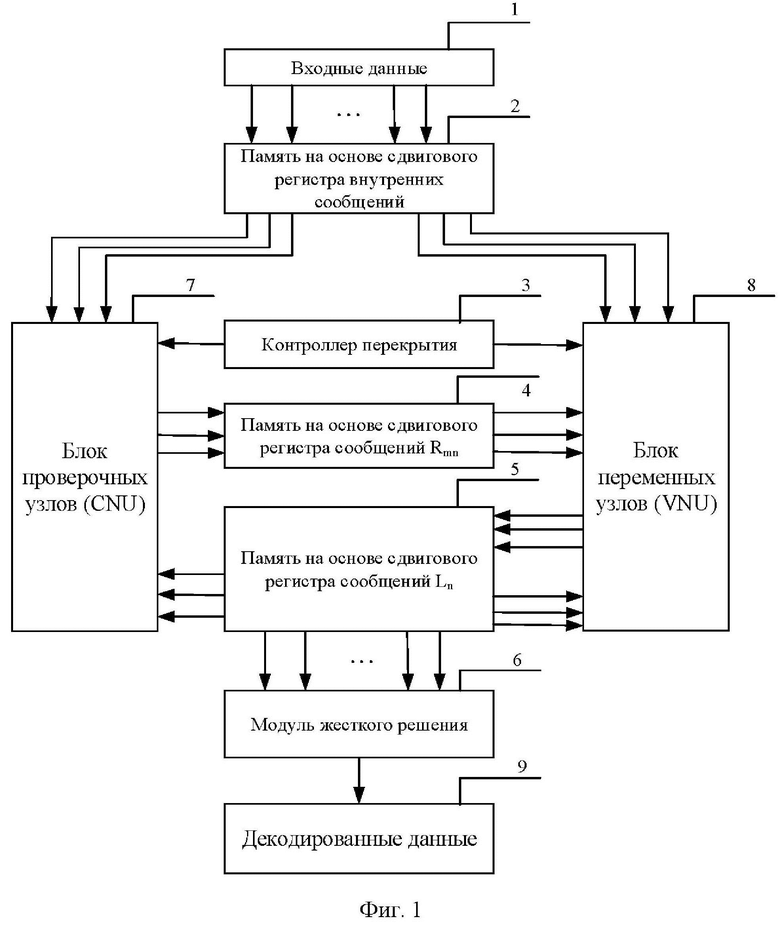

Сущность изобретения поясняется приведенными далее фигурами. На фиг. 1 представлена предлагаемая архитектура системы декодирования. Такая архитектура QC-LDPC декодера соответствует 2-битному квантованию, сохраняя при этом хорошую производительность декодирования, но значительно упрощая вычисления и хранение. Для оптимизации структуры памяти блока проверочных узлов (CNU) для хранения каждого сообщения c_v используется только три бита, представляющих собой произведение знаковых битов min1 и min2, вместо хранения всех сообщений Rmn , переданных от m-го контрольного узла к n-му переменному узлу. Значения min1 и min2, которые вычисляются в CNU, могут быть использованы для восстановления точного Rmn в блоке переменных узлов (VNU) перед использованием. Используется булева операционная система в блоках CNU и VNU для облегчения вычисления сообщений c_v/v_c по логическим схемам, тем самым снижая тем самым снижая нагрузки на использование аппаратных ресурсов.

Структура декодера состоит из: 1 - входные данные, 2 - память на основе сдвигового регистра внутренних сообщений, 3 - контроллер перекрытия, 4 - память на основе сдвигового регистра сообщений Rmn, 5 - память на основе сдвигового регистра сообщений Ln, 6 - модуль жесткого решения, 7 - блок проверочных узлов (CNU), 8 - блок переменных узлов (VNU), 9 - декодированные данные.

Блок входных данных 1 передает данные, подлежащие декодированию, Полученное мягкое сообщение квантифицируется и усекается до двух бит, а затем сохраняется в памяти, построенной с использованием памяти на основе сдвигового регистра 2. Полученные данные также передаются в блок проверочных узлов 7 декодера, который генерирует информацию c_v, состоящую из трех бит. После того, как достаточно строк было итерировано, контроллер перекрытия 3 посылает сигнал синхронизации в блок переменных узлов 8, и результат v_c выводится после преобразования и сложения. Блок памяти на основе сдвигового регистра сообщений Rmn 4 сохраняет промежуточные значения от m-го контрольного узла к n-му переменному узлу. Модуль жесткого решения 6 начинает свою работу тогда, когда число итераций достигает заданного значения. Используя предлагаемую матрицу QC-LDPC, оптимизированную для перекрытия, контроллер перекрытия 3 позволяет блоку переменных узлов VNU 8 работать, когда обновлены три группы блока проверочных узлов CNU 7, что ускоряет декодирование и увеличивая пропускную способность в три раза.

Предлагаемый способ увеличения пропускной способности декодера заключается в следующем.

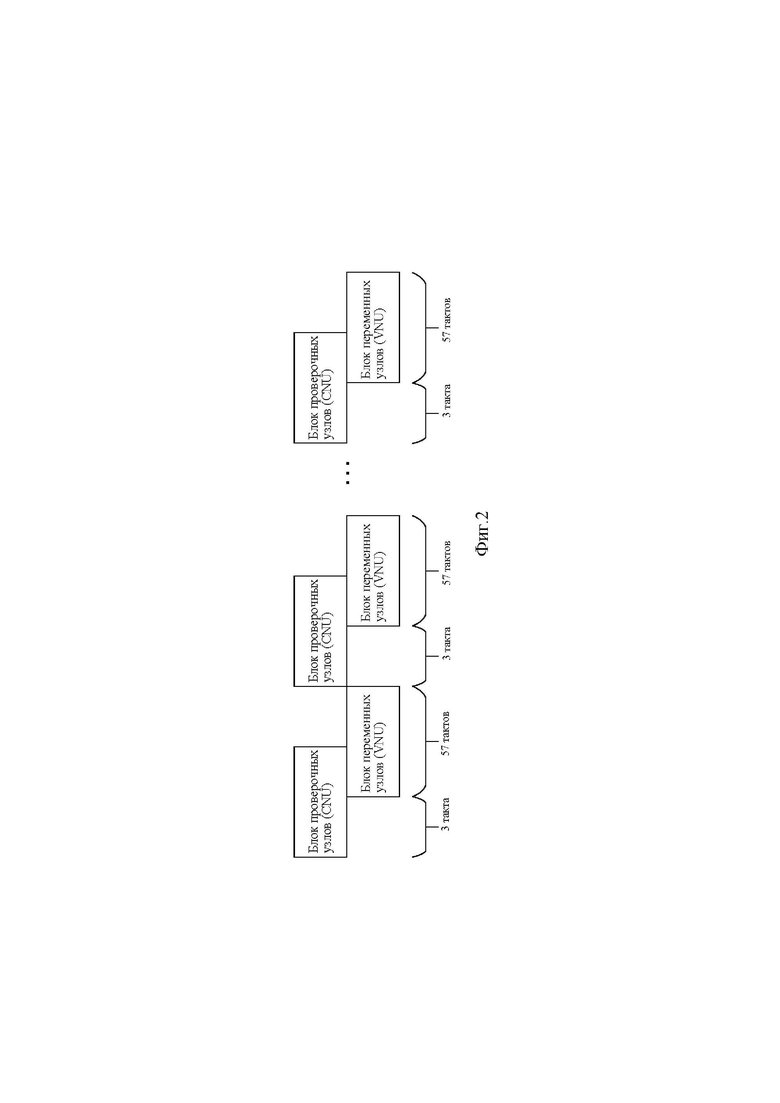

Предлагаемый декодер использует частично-параллельную архитектуру, что позволяет начинать обработку столбцов после трех вычислений обработки строк, а не ждать завершения обработки всех строк, что приводит к сокращению времени декодирования на одну треть. На фиг. 2 показана структурная схема соотношения времени перекрытия обработки блоков контрольных узлов и блоков переменных узлов при декодировании.

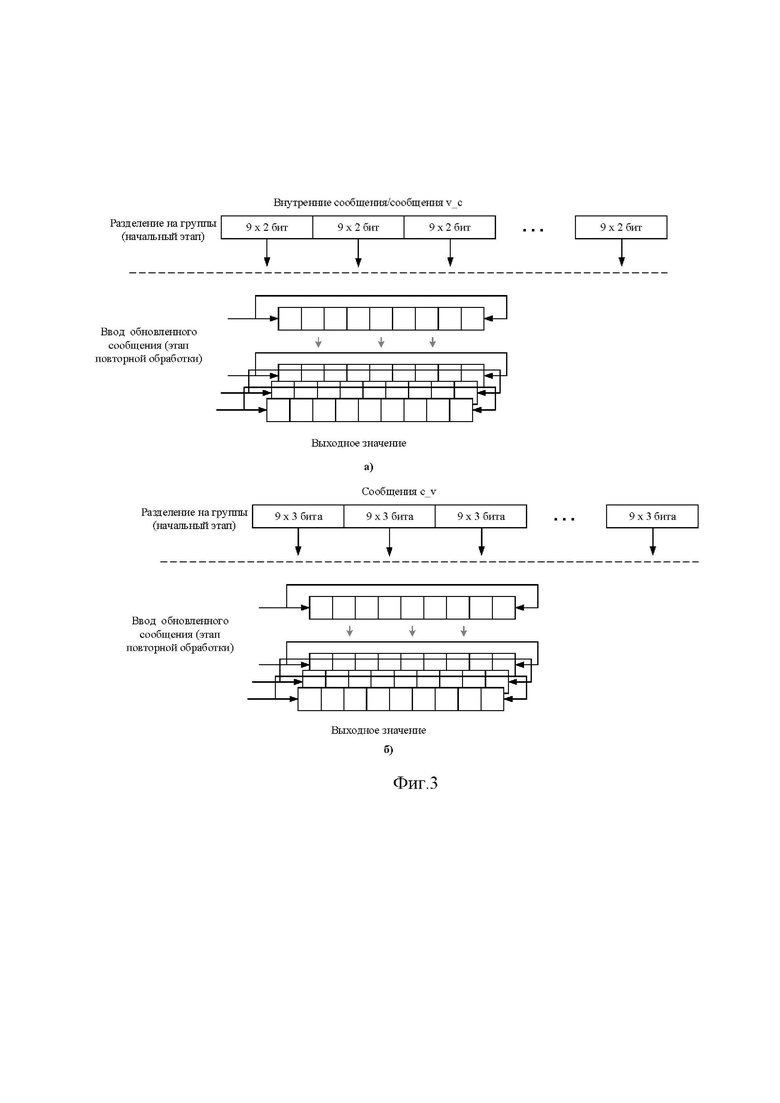

Для уменьшения задержки чтения/записи была использована структура организации блоков памяти, построенная на сдвиговых регистрах. На фиг. 3 структура организации блоков памяти на основе сдвиговых регистров а) для внутренних сообщений и сообщений v_c, б) для сообщений с_v. Блок памяти на основе регистров сдвига циклически сдвигает два или три бита и обновляет первые несколько битов в соответствии с последними результатами расчетов. В подматрицах контроля четности каждая строка (или столбец) смещается на предыдущую строку (или столбец). Это означает, что биты слева от битов, обработанных за один такт, являются битами, необходимыми для следующих тактов.

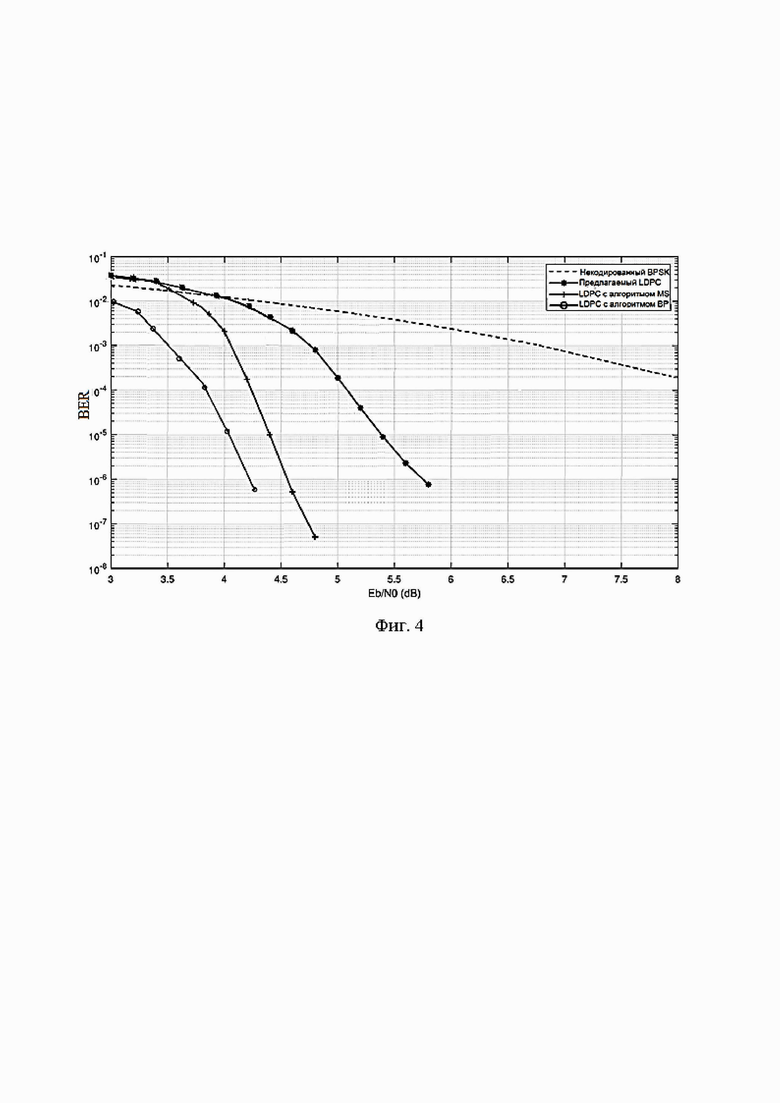

Достигаемое улучшение производительности в канале с аддитивным белым гауссовым шумом с двоичной фазовой модуляцией (BPSK) для трех различных алгоритмов декодирования, каждый из которых выполнялся в течение восьми итераций, подтверждается программно полученными данными вычислений, представленными на фиг. 4. Фиг. 4 Производительность частоты битовых ошибок (BER) по сравнению с отношением сигнал/шум (Eb/N0) для LDPC декодера.

Таким образом, коэффициент усиления кодирования 5 дБ достигается при отношении сигнал/шум 10−6 и достигает пропускной способности 6,56 Гбит/с при рабочей частоте 144,25 МГц, что демонстрирует существенное усиление кодирования по сравнению с незакодированным BPSK и на 1 дБ лучше, чем декодер, выполненный с использованием стандартного алгоритма min-sum (MS), на 1,4 дБ лучше в сравнении с декодером, построенным но алгоритму belief propagation (BP).

Технический результат достигается за счет того, что декодер использует частично параллельную архитектуру с полным перекрытием блоков проверочных и переменных узлов, что позволяет им работать независимо друг от друга, и организация блоков памяти на основе регистров сдвига обеспечивает разбиение данных на векторы и обеспечивает их хранение их в виде массива в соответствии с размером подматрицы в порядке строк (столбцов) без конфликтов адресов, благодаря чему обеспечивается высокая пропускная способность при декодировании и уменьшается время задержки передачи данных без ухудшения других параметров декодера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ декодирования данных на основе LDPC кода | 2023 |

|

RU2811085C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ КОДОВ С НИЗКОЙ ПЛОТНОСТЬЮ ПРОВЕРОК НА ЧЕТНОСТЬ | 2017 |

|

RU2739465C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2014 |

|

RU2656830C2 |

| Способ декодирования данных на основе LDPC кода | 2020 |

|

RU2747050C1 |

| СПОСОБЫ И УСТРОЙСТВО LDPC-ДЕКОДИРОВАНИЯ | 2005 |

|

RU2392737C2 |

| ЭФФЕКТИВНЫЕ ПО ИСПОЛЬЗОВАНИЮ ПАМЯТИ СПОСОБЫ ДЕКОДИРОВАНИЯ КОДОВ С НИЗКОЙ ПЛОТНОСТЬЮ КОНТРОЛЯ ПО ЧЕТНОСТИ (LDPC) И УСТРОЙСТВА ДЛЯ ОСУЩЕСТВЛЕНИЯ ЭТИХ СПОСОБОВ | 2005 |

|

RU2382493C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2012 |

|

RU2595579C2 |

| УЛУЧШЕННОЕ ВЫКАЛЫВАНИЕ И СТРУКТУРА КОДА С МАЛОЙ ПЛОТНОСТЬЮ ПРОВЕРОК НА ЧЕТНОСТЬ (LDPC) | 2017 |

|

RU2718171C1 |

| СПОСОБЫ И СИСТЕМЫ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ LDPC КОДОВ | 2016 |

|

RU2716044C1 |

| ВЫСОКОСКОРОСТНЫЕ ДЛИННЫЕ LDPC КОДЫ | 2017 |

|

RU2733826C1 |

Изобретение относится к декодированию с низкой плотностью проверки четности. Техническим результатом является уменьшение аппаратных ресурсов и уменьшение задержки чтения/записи при организации памяти и оптимизация энергопотребления. Технический результат достигается за счет того, что декодер использует частично параллельную архитектуру с полным перекрытием блоков проверочных и переменных узлов, что позволяет им работать независимо друг от друга, и организация блоков памяти на основе регистров сдвига обеспечивает разбиение данных на векторы и обеспечивает их хранение в виде массива в соответствии с размером подматрицы в порядке строк (столбцов) без конфликтов адресов, благодаря чему обеспечивается высокая пропускная способность при декодировании и уменьшается время задержки передачи данных без ухудшения других параметров декодера. 4 ил.

Способ декодирования с низкой плотностью проверок на четность, заключающийся в использовании реконфигурируемых сдвиговых регистров для обработки данных с низкой задержкой, отличающийся тем, что блок входных данных передает данные, подлежащие декодированию, при этом полученное мягкое сообщение квантифицируется и усекается до двух бит, а затем сохраняется в памяти, построенной с использованием памяти на основе сдвигового регистра, полученные данные также передаются в блок проверочных узлов декодера, который генерирует информацию c_v, состоящую из трех бит, представляющих собой произведение знаковых битов min1 и min2, после того как достаточно строк было итерировано, контроллер перекрытия посылает сигнал синхронизации в блок переменных узлов, и результат v_c выводится после преобразования и сложения, при этом блок памяти на основе сдвигового регистра сообщений Rmn сохраняет промежуточные значения от m-го контрольного узла к n-му переменному узлу, модуль жесткого решения начинает свою работу тогда, когда число итераций достигает заданного значения, используя предлагаемую матрицу QC-LDPC, оптимизированную для перекрытия, контроллер перекрытия позволяет блоку переменных узлов VNU работать, когда обновлены три группы блока проверочных узлов CNU.

| US 11575390 B2, 07.02.2023 | |||

| Способ декодирования данных на основе LDPC кода | 2023 |

|

RU2811085C1 |

| US 10581460 B2, 03.03.2020 | |||

| Устройство для декодирования кодов с минимальной избыточностью | 1988 |

|

SU1536511A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ | 2005 |

|

RU2370886C2 |

Авторы

Даты

2025-05-21—Публикация

2024-10-29—Подача