Настоящее изобретение относится к программируемой логической схеме для управления электрической установкой, в частности, ядерной установкой, причем программируемая логическая схема содержит операционный блок, содержащий:

- множество типов функциональных блоков, причем два различных типа функциональных блоков пригодны для выполнения по меньшей мере одной отдельной функции,

- по меньшей мере один модуль обработки, подходящий для приема по меньшей мере одной последовательности функциональных блоков, подлежащих выполнению, и

- по меньшей мере одну внутреннюю память, выполненную с возможностью хранить по меньшей мере упомянутую последовательность.

Кроме того, настоящее изобретение также относится к устройству управления для управления электрической установкой, в частности, ядерной установкой, причем устройство управления содержит по меньшей мере одну такую программируемую логическую схему.

Дополнительно, настоящее изобретение также относится к способу управления электрической установкой, реализуемой, по меньшей мере частично, вышеупомянутым устройством управления для управления электрической установкой.

Из документа EP 2988420 A1 известна система управления электрической установкой, основанной на электронной плате, содержащей две программируемые логические матрицы FPGA (Field Programmable Gate Array).

Первая FPGA служит в качестве ведущей и содержит набор функциональных блоков, содержащий столько же функциональных блоков одного типа, например, типа «AND», сколько число экземпляров блока этого типа для заданного приложения команды управления ядерной установкой. Вторая FPGA подключена «точка-точка» к входам и выходам первой FPGA и служит в качестве матрицы физического соединения функциональных блоков первой FPGA.

После каждой модификации рассматриваемого приложения команды управления или в случае изменения приложения команды управления требуется перепрограммирование на VHDL (языке описания аппаратных средств (HDL) сверхбыстродействующей интегрированной схемы (VHIC)) или Verilog и переквалификация второй FPGA, соединяющей функциональные блоки друг с другом.

Действительно, в контексте команды управления ядерной установкой каждая структура FPGA должна быть тщательным образом квалифицирована с использованием сложных процессов разработки и верификации.

Такой этап перепрограммирования на языке описания аппаратных средств, например, VHDL или Verilog, требует знания оператором такого языка, и переквалификация требует времени и усилий для проверки.

Для устранения упомянутых недостатков, в документе EP 3,107,212 A1 было описано решение, основанное на реализации FPGA, также содержащей набор функциональных блоков, выполняемых параллельно в соответствии с несколькими последовательными циклами, для получения результата заданного приложения команды управления ядерной установкой. Согласно этому решению FPGA схема содержит, по меньшей мере, столько же функциональных блоков одного и того же типа, что и количество экземпляров блока этого типа. Кроме того, в этом документе конвейер данных позволяет передавать двоичные и аналоговые значения между функциональными блоками, каждый из которых имеет определенную архитектуру, позволяя им извлекать свои входные и выходные данные из конвейера и отправлять их на конвейер, соответственно.

Однако для этого решения требуется большое количество функциональных блоков одного и того же типа, определенных эмпирически на основании опыта, полученного при проектировании системы команд управления ядерными установками. Кроме того, выполнение параллельно функциональных блоков в течение нескольких последовательных циклов, которые необходимы для получения результата, ассоциированного с приложением, требует осуществления синхронизации, в частности, с использованием временной задержки (задержек), чтобы гарантировать детерминизм передачи данных между каждым функциональным блоком и между каждым циклом.

Следовательно, задачей изобретения является предоставление альтернативного решения для команды управления ядерной установкой, основанной на реализации программируемой логической схемы, для которой, в случае изменения приложения команды управления не требуется перепрограммирование на VHDL или повторная квалификация модуля обработки при одновременном сокращении количества реализованных логических ресурсов и при более простом удовлетворении детерминированных требований безопасности, требуемых для устройства безопасности, такого как устройство управления ядерной установкой.

С этой целью изобретение относится к программируемой логической схеме вышеупомянутого типа, в котором программируемая логическая схема содержит один функциональный блок каждого типа, причем данный функциональный блок подходит для вызова несколько раз, и исполнительный модуль, выполненный с возможностью выполнять вызываемый функциональный блок (блоки) последовательно в соответствии с указанной последовательностью.

Затем программируемая логическая схема в соответствии с изобретением позволяет значительно уменьшить количество логических ресурсов и, следовательно, размер и энергопотребление программируемой логической схемы, гарантируя при этом детерминизм приложения команд управления благодаря последовательному выполнению вызываемых функциональных блоков в соответствии с их последовательностью (то есть, порядком) выполнения в течение одного цикла (цикла, соответствующего времени, в течение которого входные данные программируемой логической схемы фиксируют в памяти и будут переоценены только в течение следующего цикла). Другими словами, согласно настоящему изобретению для получения результата применения данной команды управления требуется один цикл, соответствующий выполнению последовательности функциональных блоков, перечисленных в последовательности.

Согласно другим преимущественным аспектам изобретения программируемая логическая схема содержит один или несколько из следующих признаков, рассматриваемых отдельно или в соответствии со всеми технически возможными комбинациями:

- программируемая логическая схема представляет собой тип FPGA;

- исполнительный модуль является конечным автоматом;

- операционный блок дополнительно содержит множество распараллеливаемых блоков с плавающей запятой;

- по меньшей мере, один модуль обработки подходит для приема прикладной программы, соответствующей группе файлов конфигурации компьютера, содержащей упомянутую последовательность, и, по меньшей мере, один другой компьютерный файл, принадлежащий группе, содержащей:

- файл конфигурации памяти, соответствующий таблице, ассоциированной, по меньшей мере, с одним входным/выходным сигналом программируемой логической схемы, адрес в ее памяти,

- файл со значением (значениями) параметра (параметров) функционального блока (блоков), пригодный для выполнения, по меньшей мере, одной функции с использованием параметра,

- список файлов для каждого функционального блока, адрес или адреса памяти, выделенной одному или нескольким входам этого функционального блока,

- список файлов для каждого функционального блока, адрес или адреса памяти, выделенной для одного или нескольких выходам этого функционального блока;

- значения параметров упорядочены в их файле как функция упомянутой последовательности функционального блока (блоков), который должен быть выполнен;

- память содержит, по меньшей мере, две области хранения данных, соответственно выделенные для двоичных данных и аналоговых данных;

- каждая область хранения содержит, по меньшей мере, три выделенные подобласти;

- по меньшей мере, одна подобласть, выделенная для входных данных программируемой логической схемы,

- по меньшей мере, одна подобласть, выделенная для выходных данных программируемой логической схемы,

- по меньшей мере, одна подобласть, выделенная для временных данных, полученных во время выполнения упомянутой последовательности;

- подобласти, выделенные для входных данных, или подобласти, выделенные для выходных данных, являются синхронными триггерными регистрами.

Изобретение также относится к устройству управления, как определено выше.

Согласно другим преимущественным аспектам изобретения устройство управления содержит одну или несколько из следующих признаков, рассматриваемых отдельно или в соответствии со всеми технически возможными комбинациями:

- устройство управления содержит множество программируемых логических схем вышеупомянутого типа;

- устройство управления дополнительно содержит:

- по меньшей мере, один модуль электропитания;

- вспомогательные модули среди одного или нескольких модулей, предназначенных для получения отдельных входных данных, один или несколько модулей, предназначенных для публикации различных выходных данных и один или несколько модулей диагностики технического обслуживания, и

- коммуникационную шину, выполненную с возможностью соединять программируемую логическую схему (схемы) со вспомогательными модулями;

- коммуникационная шина содержит четыре многоточечных дифференциальных сигнальных линии низкого напряжения (M-LVDS), соответственно выделенных для входных данных и выходных данных каждой программируемой логической схемы в каждом направлении передачи;

- устройство управления содержит волоконно-оптическую сеть связи, выполненную с возможностью соединять множество программируемых логических схем;

- устройство управления, в котором каждая ведущая программируемая логическая схема из множества программируемых логических схем пригодна для подключения к тактовому генератору и выполнена с возможностью синхронизировать другие программируемые логические схемы из множества программируемых логических схем посредством волоконно-оптической сети связи;

- устройство управления, в котором ведущая программируемая логическая схема также выполнена с возможностью синхронизировать работу вспомогательных модулей посредством коммуникационной шины;

- устройство управления, в котором множество программируемых логических схем размещено в одной стойке;

- устройство управления, в котором программируемые логические схемы из множества программируемых логических схем разделены, по меньшей мере, на две отдельные стойки.

Изобретение также относится к способу управления электрической установкой, реализуемому, по меньшей мере частично, устройством управления электрической установкой, содержащим программируемую логическую схему, содержащую операционный блок, содержащий:

- множество типов функциональных блоков, причем два различных типа функциональных блоков подходят для выполнения, по меньшей мере, одной отдельной функции,

- по меньшей мере, один модуль обработки, подходящий для приема, по меньшей мере, одной последовательности функциональных блоков, которые должны быть выполнены,

- по меньшей мере, одну внутреннюю память, выполненную с возможностью хранить, по меньшей мере, упомянутую последовательность,

программируемая логическая схема, содержащая один функциональный блок каждого типа, причем один функциональный блок подходит для вызова несколько раз и содержащая исполнительный модуль, выполненный с возможностью последовательного выполнения вызываемого функционального блока (блоков) в соответствии с упомянутой последовательностью,

способ, содержащий, по меньшей мере:

- прием, по меньшей мере, одной последовательности функциональных блоков, которые должны быть выполнены,

- выполнение последовательно вызываемого функционального блока (блоков) в соответствии с упомянутой последовательностью.

В соответствии с другими преимущественными аспектами изобретения способ управления содержит один или несколько из следующих признаков, рассматриваемых отдельно или в соответствии со всеми технически возможными комбинациями:

- реализация способа распределена по нескольким отдельным объектам, а именно, генератору прикладной программы плана обслуживания и устройству управления вышеупомянутого типа, содержащему, по меньшей мере, один модуль диагностики технического обслуживания и, по меньшей мере, одну программируемую логическую схему вышеупомянутого типа;

- способ, дополнительно содержащий:

- программирование функциональных блоков программируемой логической схемы (схем),

- разработку файла библиотеки, описывающего характеристики функций, которые могут быть реализованы каждым функциональным блоком, как запрограммировано, и сохранение упомянутого файла библиотеки в памяти генератора прикладных программ;

- разработка функциональных схем, показывающих применение команд управления электрической установкой с использованием графического издателя, подключенного к генератору прикладных программ,

- преобразование данных функциональных схем через генератор прикладных программ, по меньшей мере, в одну последовательность функциональных блоков, которые должны быть выполнены, причем каждый функциональный блок последовательности реализует функции в соответствии с функциями, предварительно запрограммированными и проиндексированными в файле библиотеки,

- подключение генератора прикладной программы к устройству управления электрической установкой через модуль диагностики технического обслуживания,

- загрузка, по меньшей мере, последовательности функциональных блоков, которые должны быть выполнены, в устройство управления;

- файл библиотеки содержит для каждого запрограммированного функционального блока:

- его тип,

- описание, по меньшей мере, одной функции, которая пригодна для реализации,

- его идентификатор, соответствующий заранее определенному коду языка описания аппаратного обеспечения,

- его номер и/или тип входов,

- его номер и/или тип выхода,

- его номер и/или тип параметра (параметров), который подходит для использования.

Эти признаки и преимущества изобретения будут очевидны после прочтения нижеследующего описания, предоставленного исключительно в качестве неограничивающего примера и выполненного со ссылкой на прилагаемые чертежи, на которых:

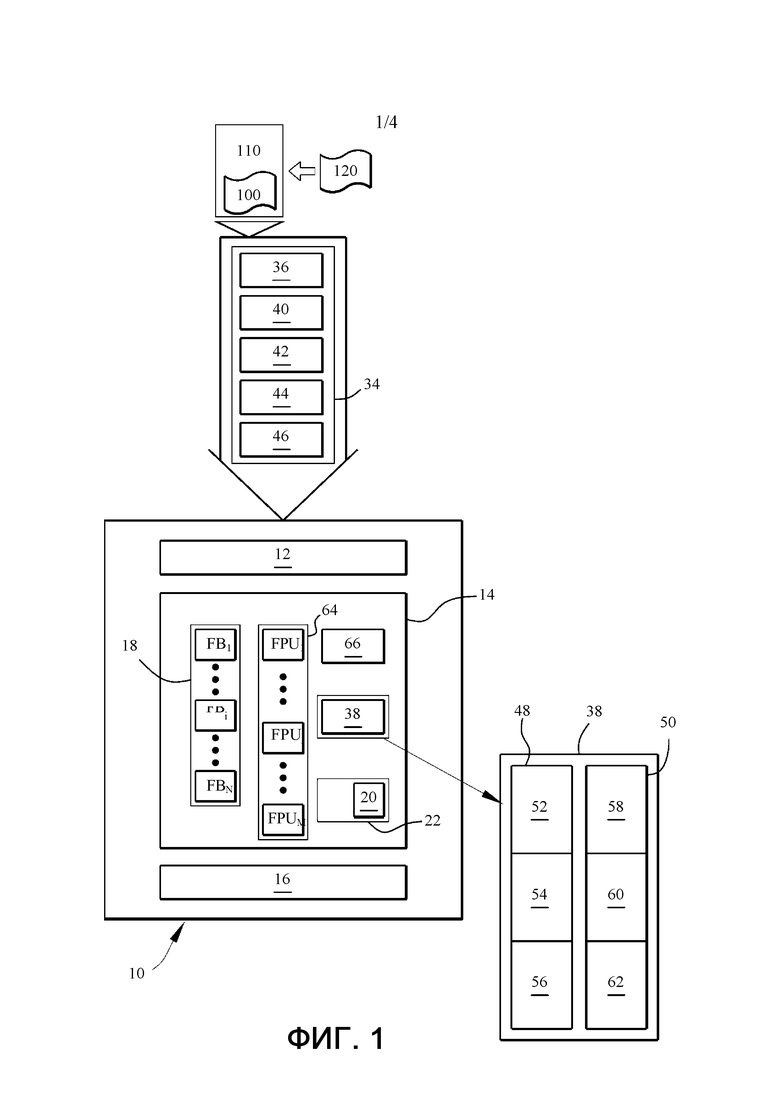

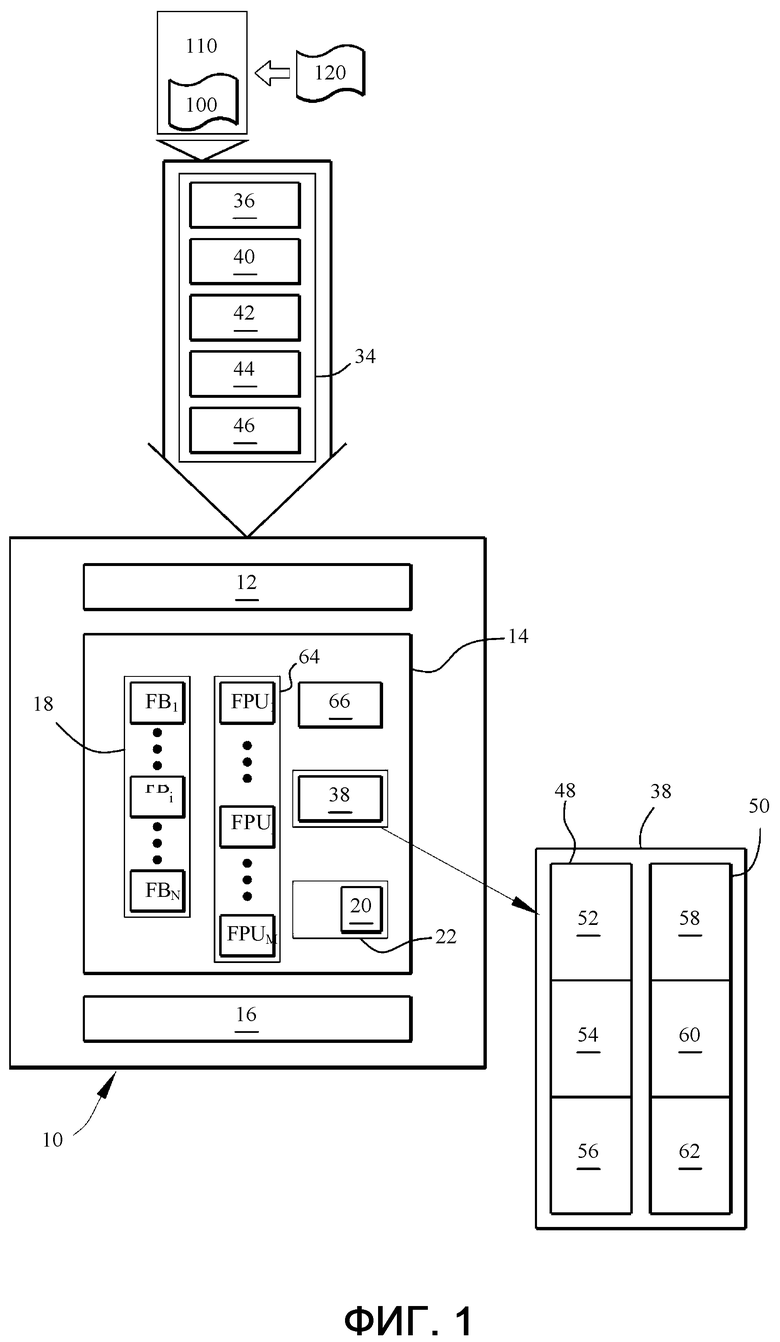

- фиг.1 представляет собой схематическую иллюстрацию программируемой логической схемы согласно изобретению;

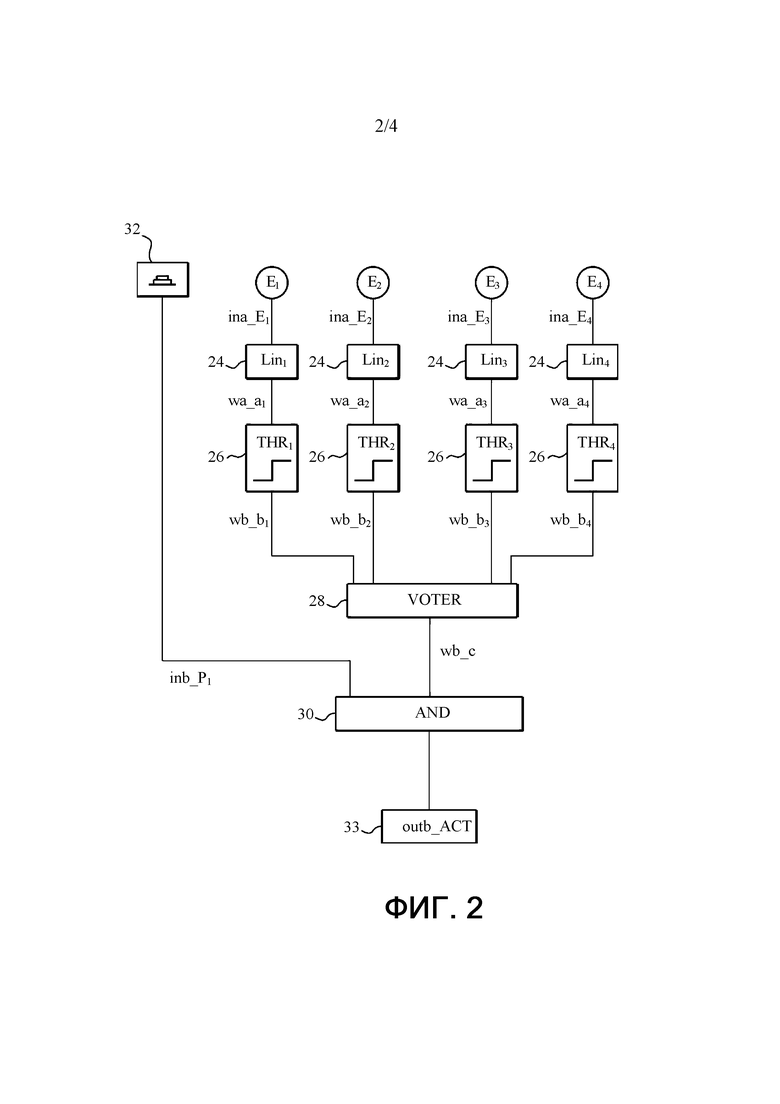

- фиг.2 является иллюстрацией, показывающей примерное приложение команды управления, которое должно быть выполнено;

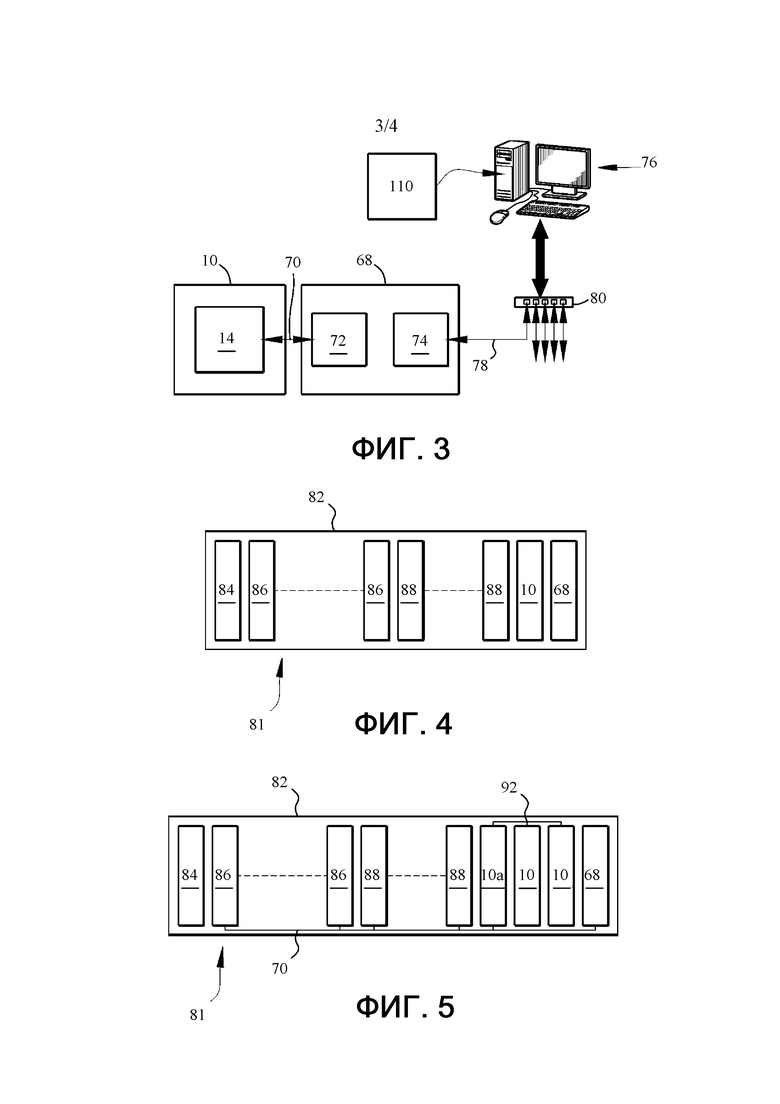

- фиг.3 является схематическим изображением соединения программируемой логической схемы в соответствии с изобретением с модулем диагностики технического обслуживания;

- фиг.4 является схематическим изображением устройства управления согласно изобретению, содержащего, согласно одному варианту осуществления, программируемую логическую схему по фиг.1;

- фиг.5 и фиг.6 соответственно показывают два варианта устройства управления, содержащих множество программируемых логических схем, показанных на фиг.1.

На фиг.1 программируемая логическая схема 10 представляет собой модуль обработки (PM). Более конкретно, программируемая логическая схема 10 выполнена в виде электронной структуры, такой как программируемая логическая матрица (FPGA).

Такая FPGA 10 содержит модуль 12 для управления входными сигналами, операционный блок 14 (OPU) и модуль 16 для управления выходными сигналами.

Операционный блок 14 содержит множество 18 N типов различных функциональных блоков FB1,… FBi,…, FBN, где N является целым числом и I-индексами типа функционального блока между единицей и N.

Два различных типа функциональных блоков являются подходящими для выполнения по меньшей мере одной отдельной функции. «Функция» относится к функции, подходящей для реализации посредством FPGA.

Согласно настоящему изобретению операционный блок содержит один функциональный блок каждого типа.

Каждый функциональный блок также квалифицируется один раз и в течение проектирования программируемой логической схемы и, в соответствии с настоящим изобретением, впоследствии вызывается только для выполнения во время применения команды управления без необходимости какой-либо переквалификации в случае изменения/модификации приложения команды управления.

Каждый экземпляр блока может дополнительно иметь, если необходимо, выделенный объем 20 внутренней памяти исполнительного модуля 22 операционного блока 14, что позволяет сохранять значения, которые являются постоянными от одного цикла выполнения к следующему.

Поэтому набор функций, пригодных для реализации посредством FPGA в соответствии с настоящим изобретением, реализуется (то есть, программируется в соответствии с предварительным этапом) раз и навсегда в VHDL. Их характеристики, например, перечислены и сохранены в файле 100 библиотеки, который хранится в памяти (не показана) автоматического генератора 110 данных конфигурации блока 76 обслуживания (показан на фиг.3), удаленного и отличного от программируемой логической схемы 10 по настоящему изобретению.

Другими словами, файл 100 библиотеки описывает характеристики функций, которые могут быть реализованы каждым функциональным блоком, как запрограммировано.

Такой файл 100 библиотеки, например, содержит для каждого функционального блока:

- его тип,

- описание по меньшей мере одной функции, пригодной для реализации,

- его идентификатор, соответствующий заранее определенному произвольному коду,

- его номер и/или тип входов,

- его номер и/или тип выходов,

- его номер и/или тип параметров, подходящих для использования.

Такой файл 100 библиотеки разрабатывается заранее и используется автоматическим генератором данных конфигурации блока 76 обслуживания, что позволяет автоматически преобразовывать набор функциональных диаграмм 120 в прикладную программу 34.

Фиг.2 иллюстрирует функциональную схему 120 примерного приложения команд управления, которое должно быть выполнено. Такое приложение соответствует выявлению предельной температуры в четырех различных точках ядерного реактора.

Такое приложение генерируется оператором из графического издателя, подключенного к автоматическому генератору 110 прикладной программы 34, не требуя специальных знаний на языке описания VHDL или Verilog.

Автоматический генератор 110 прикладной программы 34 подходит для преобразования данных из такой функциональной схемы 120 генератором 110 прикладной программы 34 по меньшей мере в одну последовательность 46 функциональных блоков, которые должны быть выполнены, причем каждый функциональный блок последовательности реализует функции, соответствующие ранее запрограммированным функциям и проиндексированным в файле 100 библиотеки.

Для реализации такого приложения команд управления необходимы четыре типа 24, 26, 28, 30 различных функциональных блоков, а именно, четыре типа LIN, THR, VOTER и AND, которые графически соединены направленными линиями, показывающими причинно-следственные связи между функциональными блоками.

Более конкретно, оператор графически определяет количество входов и сигналов приложения команды управления, а именно, E1, E2, E3 и E4, которые соответствуют, например, различным точкам измерения параметров ядерного реактора.

В соответствии с этим приложением команды управления электрические сигналы точек Ei (i = 1-4) затем могут быть преобразованы с использованием функционального блока типа LIN в физические данные, в данном случае значение температуры.

Затем значение температуры, полученное на выходе функционального блока 24 типа LIN, сравнивают с пороговым значением температуры с использованием функционального блока 26 типа THR, имеющего в качестве параметра это пороговое значение температуры, а именно, например, 100°C.

Затем целевое приложение команд управления содержит функцию голосования, реализованную функциональным блоком 28 VOTER, который применяют к четырем сигналам, ассоциированным с каждой входной точкой. Функция голосования, например, представляет собой функцию голосования 2/4, способную подтвердить или аннулировать (то есть двоичный результат) сравнение с пороговым значением температуры по меньшей мере два из четырех сравнений имеют одинаковый результат.

Наконец, целевое приложение команд управления может учитывать, используя функциональный блок 30 AND, активацию кнопки 32 (которая может быть приведена в действие вручную оператором), которая блокирует результат. Другими словами, функциональный результат 30 AND принимает два двоичных входа, соответственно соответствующих выходным сигналам кнопки 32 и функционального блока 28 VOTER, и выдает в качестве вывода двоичный результат 33 функционального блока VOTER, если кнопка 32 не была приведена в действие, и, в противном случае, противоположный двоичный результат 33.

Таким образом, для этого примера приложения команды управления файл 100 библиотеки, используемый автоматическим генератором 110, имеет, например, вид следующей таблицы:

Со ссылкой на фиг.1, функциональный блок FB1, например, относится к типу LIN, и ему назначается код 0x01 на FPGA плате, функциональный блок FBi = 5 относится к типу THR, и ему назначается код 0x02, функциональный блок FBi = 12 имеет тип VOTER и ему присвоен код 0x03, и функциональный блок FBi = 18 имеет тип AND и ему присвоен код 0x04.

Из схемы, показанной на фиг.2, и файла 100 библиотеки, описанного выше, автоматически генерируют набор файлов конфигурации компьютера, образующих прикладную программу 34.

Такая прикладная программа 34, в частности, содержит:

- файл 36 конфигурации памяти 38 операционного блока 14, соответствующий таблице, ассоциированный, по меньшей мере, с одним входным/выходным сигналом программируемой логической схемы 10, адрес в его памяти,

- файл 40 значения (значений) параметров функционального блока (блоков), подходящий для выполнения, по меньшей мере, одной функции с использованием параметра,

- файл 42, в котором перечислены для каждого функционального блока адрес или адреса памяти, выделенной для одного или нескольких входов этого функционального блока,

- файл 44, в котором перечислены для каждого функционального блока адрес или адреса памяти, выделенной для одного или нескольких выходных сигналов этого функционального блока,

- последовательность 46 функциональных блоков, которые должны быть выполнены.

Память 38 операционного блока 14 содержит по меньшей мере два пространства 48 и 50 для хранения данных, соответственно выделенных для двоичных данных (логическое значение, закодированное в двух разных битах) и аналоговых данных (плавающие числа, содержащиеся, например, в тридцати двух битах). В варианте, который не показан, память 38 операционного блока 14 дополнительно содержит область хранения данных, выделенную для значений параметров файла 40.

Пространство 48 хранения двоичных данных, в свою очередь, имеет приоритет по меньшей мере в трех подпространствах, а именно: первое подпространство 52, выделенное для двоичных входных данных программируемой логической схемы 10, второе подпространство 54, выделенное для временных двоичных данных, полученных во время выполнения последовательности 46, третье подпространство 56, предназначенное для двоичных выходных данных программируемой логической схемы.

Аналогично, пространство 50 хранения аналоговых данных, в свою очередь, имеет приоритет по меньшей мере в трех подпространствах, а именно: первое подпространство 58, выделенное для данных аналогового ввода программируемой логической схемы 10, второе подпространство 60, выделенное для временных аналоговых данных, полученных во время выполнения последовательности 46, третье подпространство 58, предназначенное для данных аналогового выхода программируемой логической схемы.

Файл 36 конфигурации памяти 38 выполнен с возможностью считывать исполнительным модулем 22 операционного блока 14 в течение одного цикла выполнения приложения команды управления (например, соответствующего тому, что показано на фиг.2).

Во время выполнения последовательности 46 исполнительный модуль 22 считывает в файле 36 конфигурации, где хранят значения, в памяти 38 значения входов и выходов приложения в целом.

Другими словами, файл 36 конфигурации является таблицей распределения в различных подпространствах памяти (то есть регистрах) адресов памяти на входах и выходах программируемой логической схемы 10.

Пять входных значений, в соответствии с примером приложения команды управления, показанным на фиг.2, с четырьмя аналоговыми значениями ina_E1, ina_E2, ina_E3 и ina_E4, соответствующими электрическим сигналам, представляющим измерения температуры соответственно точек E1-E4 и двоичное значение inb_P1, представляющее активацию/деактивацию кнопки 32.

Выходное значение outb_ACT поставляют после выполнения функциональных блоков в соответствии с последовательностью 46 функциональных блоков.

Таким образом, для этого примерного приложения команд управления, показанного на фиг.2, файл 36 конфигурации имеет, например, форму следующей таблицы:

0x0004

В соответствии с настоящим изобретением последовательность 46 функционального блока (блоков), подлежащего исполнению, является списком компьютерных файлов из причинно-следственных связей схемы, порядка формирования экземпляров функциональных блоков, которые должны последовательно выполняться исполнительным модулем 22 операционного блока 14, чтобы выполнить требуемое приложение команды управления.

Последовательность 46 представляет собой компьютерный файл, например, показанный в виде следующей упорядоченной таблицы:

Другими словами, согласно настоящему изобретению один функциональный блок FB (код которого указан в ранее описанном файле библиотеки) выполняется одновременно в соответствии с последовательными экземплярами последовательности функциональных блоков, указанных ранее в файле компьютера последовательности 46.

Такое последовательное выполнение гарантирует детерминизм выполнения приложения команды управления, поскольку сохраняют и/или повторно вводят выходные данные каждого функционального блока на входе следующего функционального блока согласно экземпляру.

Согласно предшествующему уровню техники для выполнения приложения команды управления, показанного на фиг.2, необходимо, чтобы FPGA содержала четыре функциональных блока типа LIN, четыре функциональных блока типа THR, один функциональный блок типа VOTER и один функциональный блок типа AND, или всего около десяти различных функциональных блоков.

Напротив, в соответствии с настоящим изобретением необходим один функциональный блок каждого типа, который «вызывают» столько раз, сколько требуется в соответствии с приложением команды управления, которое должно быть выполнено. Таким образом, в связи с примерным приложением по фиг.2, количество функциональных блоков, необходимых для выполнения такого приложения, уменьшено с десяти до четырех, что позволяет уменьшить размер FPGA (т.е. оптимизировать компактность) и/или возможность интеграции в нее функциональных блоков, которые можно вызывать для других приложений команд управления.

Другими словами, аппаратный импринт (например, VHDL импринт) программируемой логической схемы согласно изобретению, является уникальным и постоянным, причем квалифицированный функциональный блок пригоден для повторного использования из одного приложения команды управления в другое. Согласно изобретению, только одна прикладная программа 34 отличается от одного приложения команды управления от другого, причем вызывают один и тот же функциональный блок, например, в первом случае для первого приложения команды управления и в последнем случае для второго приложения команды управления, отличного от первого.

Компьютерный файл 40 значения (значений) параметра функциональных блоков, в свою очередь, содержит значения параметров, необходимых во время выполнения последовательности 46, причем эти значения параметров упорядочены с учетом последовательности 46 выполнения функциональных блоков.

Компьютерный файл 40 значений параметров показан, например, в виде следующей упорядоченной таблицы:

Другими словами, для примерного приложения команды управления, показанного на фиг.2, формируют один и тот же функциональный блок FBi = 5 типа THR четыре раза с одним и тем же значением параметра, а именно, температуры 100°C.

Согласно другим примерным приложениям команд управления разные значения параметров подходят для ассоциации с разными экземплярами функционального блока FBi = 5 типа THR. Таким образом, без изменения аппаратного импринта (например, VHDL импринта) и, как результат, без переквалификации программируемой схемы, настоящее изобретение позволяет изменять параметры одного и того же функционального блока в течение срока службы системы команд управления или одного из приложения к другому. Таким образом, упрощают функционирование программируемой схемы.

Кроме того, как указывалось ранее, прикладная программа 34 также содержит два компьютерных файла 42 и 44, перечисляющих, соответственно, для каждого функционального блока, с одной стороны, адрес или адреса памяти 38, выделенной для одного или нескольких входных операндов этого функционального блока и, с другой стороны, адрес или адреса памяти, выделенной одному или нескольким выходным операндам этого функционального блока.

В связи с приложением, показанным на фиг.2, эти два компьютерных файла 42 и 44 имеют, например, соответственно следующий вид:

5

Затем исполнительный модуль 22 работает как конечный автомат и автоматически распределяет и/или сохраняет на каждом экземпляре функционального блока входные и выходные значения по адресам памяти, указанным в файлах 42 и 44 прикладной программы 34.

Указатель позволяет исполнительному модулю 22 определять для каждого экземпляра функционального блока начальное местоположение адресов входных и выходных значений, которые должны быть считаны в файлах 42 и 44. В конце выполнения каждого экземпляра функционального блока, последний обновляет указатель как функцию от числа прочитанных входных значений и количества сгенерированных выходных значений, позволяя исполнительному модулю 22 определять адреса, которые будут считаны в файлах 42 и 44 для следующего экземпляра блока.

Другими словами, компьютерные файлы прикладной программы 34 имеют синергетический эффект, так что исполнительный модуль 22 выполнен с возможностью выполнять параллельный учет всех из них для реализации последовательного выполнения без установления физической связи между различными функциональными блоками.

Таким образом, в связи с примерным приложением команды управления, показанным на фиг.2, исполнительный модуль 22 выполнен с возможностью считывать последовательность 46 и определять, какой первый функциональный блок должен быть выполнен.

Этот первый блок является функциональным блоком FB1 типа LIN, и исполнительный модуль 22 затем конфигурируют для распределения ему в качестве входных данных, в соответствии с компьютерным файлом 42, ассоциированным с входными данными каждого функционального блока, аналогового значения ina_E1, которое хранят по адресу 0x0001 подпространства 58, выделенного для ввода аналоговых данных памяти 38.

Затем выполняют функциональный блок FB1 типа LIN и аналоговое значение wa_a1, доставляемое в качестве вывода, сохраняют по адресу 0x0800 в подпространства 60 памяти, выделенной для временных аналоговых данных, в соответствии с компьютерным файлом 44, ассоциированным с выходными данными каждого функционального блока.

Затем исполнительный модуль 22 выполнен с возможностью считывать последовательность 46 и определять, какой второй функциональный блок должен быть выполнен. Этот второй блок является функциональным блоком FBi = 5 типа THR, и ему назначен код 0x02 на FPGA плате. Затем исполнительный модуль 22 выполнен с возможностью распределять ему в качестве входных данных значение wa_a1, которое хранят по адресу 0x0800, а также значение параметра 100.0, которое является следующим значением в наборе значений аналоговых параметров.

Затем выполняют функциональный блок FB5 типа THR, и двоичное значение wb_b1, доставляемое в качестве выходных данных, записывают и сохраняют исполнительным модулем 22 по адресу 0x0804 в подпространстве 54, выделенном для временных двоичных данных.

Затем, согласно последовательности 46, третий функциональный блок, который должен быть выполнен, снова является функциональным блоком FB1 типа LIN. Во время этого второго экземпляра этого же функционального блока FB1 типа LIN исполнительный модуль 22 затем конфигурируют для распределения ему в качестве ввода аналогового значения ina_E2, которое хранят по адресу 0x0005 в подпространстве 58, выделенном для входных аналоговых данных памяти 38.

Затем выполняют функциональный блок FB1 типа LIN второй раз, и аналоговое значение wa_a2, доставляемое в качестве вывода, сохраняют по адресу 0x0805 в подпространстве 60 памяти, выделенном для временных аналоговых данных, и так далее, пока вся последовательность 46 не будет полностью выполнена (т.е. до тех пор, пока код 0x00 остановки не будет считан исполнительным модулем 22).

Таким образом, согласно настоящему изобретению, выполняют один функциональный блок в данный момент один раз.

В соответствии с примером, показанным на фиг.1, операционный блок 14 дополнительно содержит множество из 64 М параллелизуемых блоков с плавающей запятой (FPU), где М является целым числом.

Такие блоки, например, пригодны для реализации вычислений квадратного корня или логарифма и распараллелены для выполнения сложных вычислений, требуемых во время выполнения функционального блока, таких как определение соотношения между тепловым потоком для возникновения кризиса кипения и фактический тепловой поток в активной зоне реактора, называемый отношением критического теплового потока/коэффициент DNBR (запас до кризиса пузырькового кипения). Такой пул блоков с плавающей точкой является общим для всех функциональных блоков операционного блока 14 и позволяет увеличить вычислительную мощность функционального блока, когда последний выполнен с возможностью реализации сложных аналоговых вычислений. Масштабируемость программируемой логической схемы 10 соответственно увеличивается.

Операционный блок 14 также содержит интерфейс 66 ввода-вывода, подходящий для приема и повторной передачи соответственно входных данных ina_E1, ina_E2, ina_E3, ina_E4 и выходных данных inb_P1 и outb_ACT, проиндексированных в файле конфигурации 36 и ассоциированных с приложением команды управления в целом.

Интерфейс 66 выполнен с возможностью принимать прикладную программу 34 через шину внутренней конфигурации (ICB), подключенную к модулю 12 управления входных сигналов, и отправлять через эту же шину данные управления и диагностические данные в модуль 16 управления выходных сигналов.

Модуль 12 управления входными сигналами и модуль 16 управления выходными сигналами находятся вне операционного блока 14 и выполнен с возможностью устанавливать связь с устройствами и/или схемами вне программируемой логической схемы 10.

Данный модуль 12 управления входного сигнала и этот модуль 16 управления выходным сигналом, в свою очередь, представляют собой конечный автомат, содержащий одну или несколько областей памяти, соответственно, выделенных для аналоговых и двоичных данных, не показаны.

Среди этих выделенных областей памяти некоторые предназначены для управления входными и выходными данными, которыми обмениваются с сетью связи, и пригодны для приема/передачи данных, отправляемых/передаваемых асинхронно в рабочем цикле программируемой логической схемы 10. С этой целью эти области памяти, выделенные специально для сетевых данных, представляют собой синхронные регистры триггеров для хранения сетевых данных, принятых/переданных в течение текущего цикла, в то время как сетевые данные, принятые/переданные в течение предшествующего цикла, используют операционным блоком 14 в течение текущего цикла. Таким образом, программируемая логическая схема 10 имеет определенное количество волоконно-оптических разъемов, позволяющих отправлять/принимать эти данные по сетям связи.

Модули 12 и 16, в частности, выполнены с возможностью обеспечивать связь с модулем 68 диагностики технического обслуживания (SMD), показанным на фиг.3.

Такой модуль 68 диагностики технического обслуживания, в частности, позволяет загружать в программируемую логическую схему 10 прикладную программу 34, ассоциированную с исполняемым приложением, или изменять параметры функционального блока (например, изменение порогового значения температуры от 100°С до 120°C) для запуска периодических проверок технического обслуживания в программируемой логической схеме 10 или для передачи программируемой логической схемы 10 в соответствии с изобретением в модуль 68 диагностики технического обслуживания при обслуживании данных. Эти обмены данными между программируемой логической схемой 10 и модулем 68 диагностики технического обслуживания обеспечиваются с использованием линии связи, такой как шина 70, соединенная с шиной объединительной платы корпусов, соответственно содержащей программируемую логическую схему 10 и модуль 68 диагностики технического обслуживания.

Модуль 68 диагностики технического обслуживания также содержит программируемую логическую схему 72, например, FPGA, и микропроцессор 74 и выполнен с возможностью устанавливать связь в соответствии с процедурой безопасности с блоком 76 обслуживания, например, содержащим автоматический генератор 110, с использованием линии 78 связи типа Ethernet и коммутатора 80, подходящего для связи с другими устройствами управления электрооборудованием, причем устройство управления содержит, по меньшей мере, одну программируемую логическую схему 10 согласно изобретению, как описано ранее.

Блок 76 технического обслуживания, например, удален от ядерной электрической установки, в которой реализована программируемая логическая схема 10. В этом блоке 76 технического обслуживания оператор технического обслуживания использует графический издатель (не требующее предварительного знания VHDL или Verilog) для выполнения приложений команды управления, которые должны быть реализованы в ядерной электрической установке, в форме функциональных схем 120, как показано, например, на фиг.2. Как указано ранее, функциональные схемы 120 затем преобразуются в прикладную программу 34 автоматическим генератором 110, который использует файл 100 библиотека, чтобы гарантировать, что прикладная программа 34 будет выполнена без влияния на квалифицированную конфигурацию программируемой логической схемы 10. Прикладная программа 34 затем загружается через модуль 68 диагностики технического обслуживания в программируемую логическую схему 10.

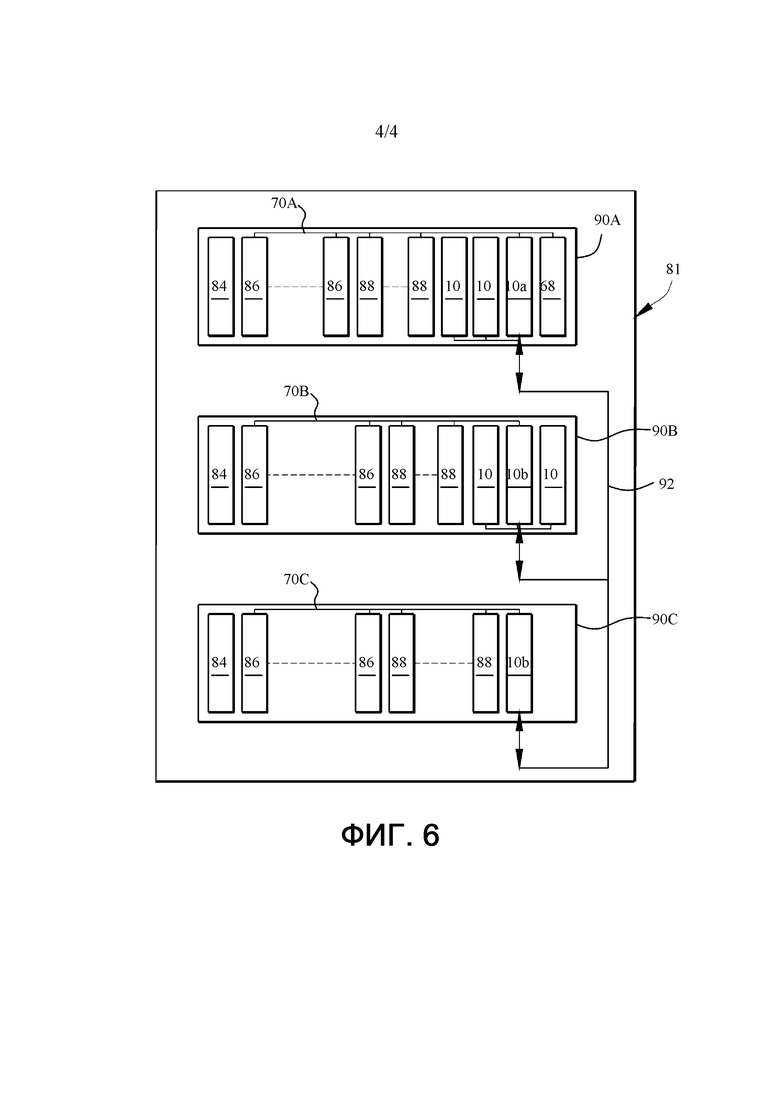

На фиг.4-6 соответственно показаны три варианта архитектуры такого устройства 81 управления.

На фиг.4 устройство 81 управления представляет собой «моно-» программируемую логическую схему 10. Другими словами, устройство 81 управления содержит стойку 82, образующую корпус, например, размером 6U (U является единицей измерения высоты стойки), в которой интегрирована одна программируемая логическая схема 10. Стойка 82 выполнена с возможностью дополнительно содержать модуль 84 электропитания и вспомогательные модули, а именно, один или несколько модулей 86, предназначенных для сбора различных входных данных, и один или несколько модулей 88, предназначенных для публикации различных выходных данных, и один или несколько модулей 68 диагностики технического обслуживания, как описано ранее. Кроме того, программируемая логическая схема 10 содержит разъемы (например, семь разъемов, которые не показаны), позволяющие, например, с использованием волоконной оптики, подключаться к сети связи.

Соединение прикладной программы 34 автоматического генератора 110 с устройством 81 управления может быть установлено через модуль (модули) 68 диагностики технического обслуживания, который, в частности, выполнен с возможностью загружать последовательность 46 функциональных блоков, которые должны быть выполнены, в устройство 81 управления, когда такое соединение установлено.

В пределах стойки 82 программируемая логическая схема 10 является ведущей и управляет связью со вспомогательными модулями 86, 88 и 68 через шину 70 с использованием, в качестве неограничивающего примера, многоточечной дифференциальной сигнализации низкого напряжения (M-LVDS) работающей, например, на частоте 50 МГц и, соответственно, выделенной для двоичных и аналоговых входных данных и для двоичных и аналоговых выходных данных программируемой логической схемы 10. Преимущественно, каждый тип данных (вход или выход) имеет независимую линию передачи для двоичных данных и аналоговых данных. В этом сценарии, следовательно, могут быть использованы четыре низковольтных дифференциальных линий передачи.

Поэтому многие варианты осуществления, которые не показаны, могут быть реализованы без выхода за пределы объема изобретения. Например, модули 86, предназначенные для сбора входных данных, и модули 88, предназначенные для публикации выходных данных, могут быть размещены на одной электронной плате уже известного типа «GPIO» (универсальный ввод-вывод).

Модуль 84 электропитания подает стабилизированную мощность для других модулей стойки 82 и также выполнен с возможностью выполнять преобразование напряжения, например, от 24 В постоянного тока до 5 В для питания каждого модуля корпуса 82.

На фиг.5 и фиг.6 показаны два варианта устройств 81 управления, содержащих множество программируемых логических схем 10, показанных на фиг.1.

Такая архитектура «мульти» программируемых логических схем 10 позволяет увеличить количество сетевых интерфейсов на устройство управления, дублировать операции команд управления, по меньшей мере, в двух программируемых логических схемах 10 для целей управления безопасностью, накладывающих правила избыточности, или оптимизировать межмодульную маршрутизацию внутри корпуса 82.

В такой архитектуре 10 «мульти» программируемых логических схем, множество программируемых логических схем 10 синхронизировано; эта синхронизация осуществляется посредством ведущей логической схемы 10а из числа программируемых логических схем 10, подключенных к тактовому генератору.

Ведущая программируемая логическая схема 10а, в частности, выполнена с возможностью поставлять через модуль 12 управления сигналы, показанные на фиг.1, импульса синхронизации в начале и/или конце цикла (например, цикл, имеющий длительность 2 мс) и запрос статуса другим модулям 86, предназначенным для отдельных входных данных, модулям 88, предназначенным для различных выходных данных, или другим программируемым логическим схемам 10 для синхронизации и обновления при каждом цикле входных/выходных данных следующего цикла (новая итерация того же приложения команды управления). В результате, в отличие от обменов через сети связи, эти обмены данными в одном и том же множестве программируемых логических схем выполняют синхронно.

Таким образом, все программируемые логические схемы 10 множества выполнены с возможностью работать одновременно в одном и том же цикле.

Два неограничивающих варианта такой «мульти» программируемой логической схемы архитектуры 10 показаны на фиг.5 и фиг.6 в качестве иллюстрации.

На фиг.5 три программируемые логические схемы, содержащие ведущую программируемую логическую схему 10а и две другие программируемые логические схемы 10, размещены в одной стойке 82, причем программируемые логические схемы 10 и 10а выполнены с возможностью устанавливать связь друг с другом и со вспомогательными модулями 86, 88, 68 стойки 82 синхронно. В варианте осуществления, показанном на фиг.5, программируемые логические схемы 10a и 10 осуществляют синхронную связь друг с другом посредством волоконной оптики 92, причем разъемы специально предназначены для этой коммуникации между программируемыми логическими схемами в рамках «многоконтурной архитектуры». Кроме того, ведущая программируемая логическая схема 10а взаимодействует синхронно со вспомогательными модулями 86, 88, 68 стойки 82 с использованием шины 70.

На фиг.6 показана «мульти» программируемая логическая схема 10а и 10 и «мульти» стойка 90А, 90В, 90C устройства 81 управления. В соответствии с этой многоконтурной и многостоечной архитектурой каждая стойка 90A, 90B, 90C соответствует компоновке, описанной на фиг.4 (одноконтурная схема) или на фиг.5 (многоконтурная схема).

Каждая стойка может дополнительно содержать вспомогательные модули 86, 88, 68.

Предпочтительно одна из стоек 90А является «ведущей» и содержит ведущую программируемую логическую схему 10а для всех программируемых логических схем 10 многоконтурного и многостоечного устройства 81 управления и обеспечивает синхронизацию вспомогательных модулей 86, 88, 68 его корпуса через шину 70А.

Программируемые логические схемы 10 устройства 81 управления выполнены с возможностью осуществлять синхронную связь от одной стойки к другой и внутри одной стойки с помощью волоконной оптики 92.

Каждая «ведомая» стойка 90B, 90C ведущей стойки 90A содержит среди своих программируемых логических схем 10 программируемую логическую схему 10b синхронизации для синхронизации вспомогательных модулей 86, 88, 68 ее стойки посредством шины 70B, 70C стойки.

В вариантах осуществления, показанных на фиг.5 и фиг.6, и без ограничения объема изобретения для каждого устройства 81 управления реализован единый модуль 68 диагностики технического обслуживания, независимо от количества программируемых логических схем 10 или количества стоек, которые содержит.

В вариантах осуществления, показанных на фиг.5 и фиг.6, и без ограничения объема изобретения только ведущая программируемая логическая схема 10a и программируемые логические схемы 10b синхронизации подключены к вспомогательным модулям 86, 88, 68 их соответствующих стоек 90A, 90B, 90C посредством их соответствующих шин 70A, 70B, 70C. Другие программируемые логические схемы 10 стойки подключаются к вспомогательным модулям 86, 88, 68 их стойки посредством, соответственно, ведущей программируемой логической схемы 10a или программируемой логической схемы 10b синхронизации и волоконно-оптической сети 92. В этой конфигурации шина 70А, 70В, 70С преимущественно содержит четыре линии связи многоточечной дифференциальной сигнализации низкого напряжения (M-LVDS), например, работающих на частоте 50 МГц, в каждом направлении передачи.

В другом варианте осуществления, который не показан, шины 70А, 70В, 70С могут быть рассчитаны таким образом, чтобы позволить каждой программируемой логической схеме 10 быть подключенной к вспомогательным модулям 86, 88, 68 ее стойки через шину 70А, 70В, 70С.

| название | год | авторы | номер документа |

|---|---|---|---|

| МЕТАПРОСТРАНСТВО: ПРОМЕЖУТОЧНОЕ КОММУНИКАЦИОННОЕ ПРОГРАММНОЕ ОБЕСПЕЧЕНИЕ ДЛЯ ЧАСТИЧНО СОЕДИНЕННЫХ ОДНОРАНГОВЫХ СЕТЕЙ МОБИЛЬНОЙ СВЯЗИ С ПРОИЗВОЛЬНОЙ СТРУКТУРОЙ | 2004 |

|

RU2366108C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ФАЙЛОВОЙ СИСТЕМЫ НА ПРОГРАММИРУЕМОМ ЛОГИЧЕСКОМ КОНТРОЛЛЕРЕ | 2011 |

|

RU2597514C2 |

| ИСПОЛЬЗОВАНИЕ АУТЕНТИФИЦИРОВАННЫХ МАНИФЕСТОВ ДЛЯ ОБЕСПЕЧЕНИЯ ВНЕШНЕЙ СЕРТИФИКАЦИИ МНОГОПРОЦЕССОРНЫХ ПЛАТФОРМ | 2014 |

|

RU2599340C2 |

| СПОСОБ И СИСТЕМА ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ УСТАНОВКИ В СЕТИ "МАШИНА-МАШИНА" НА ОСНОВЕ OPC-UA | 2015 |

|

RU2674758C1 |

| СИСТЕМА АДАПТИВНОГО УПРАВЛЕНИЯ ВСЕЙ УСТАНОВКОЙ И ЕЕ РЕГУЛИРОВАНИЕМ, А ТАКЖЕ СООТВЕТСТВУЮЩИЙ ЕЙ СПОСОБ | 2015 |

|

RU2674756C1 |

| АВТОМАТИЗИРОВАННОЕ ПРЕОБРАЗОВАНИЕ ОБЪЕКТА ИНТЕРФЕЙСА ПОЛЬЗОВАТЕЛЯ И ГЕНЕРАЦИЯ КОДА | 2012 |

|

RU2604431C2 |

| КОМАНДА И ЛОГИЧЕСКАЯ СХЕМА ДЛЯ СОРТИРОВКИ И ВЫГРУЗКИ КОМАНД СОХРАНЕНИЯ | 2014 |

|

RU2663362C1 |

| СИСТЕМА И СПОСОБ УПРАВЛЕНИЯ И ОРГАНИЗАЦИИ КЭША ВЕБ-БРАУЗЕРА | 2014 |

|

RU2629448C2 |

| ОДНОПРОЦЕССОРНАЯ ЭЛЕКТРОННАЯ СИСТЕМА БОРТОВОЙ ДОКУМЕНТАЦИИ 3-ГО КЛАССА | 2011 |

|

RU2568779C2 |

| СПОСОБ И СИСТЕМА УПРАВЛЕНИЯ ОБЪЕКТАМИ И ПРОЦЕССАМИ В ВЫЧИСЛИТЕЛЬНОЙ СРЕДЕ | 2023 |

|

RU2820753C1 |

Изобретение относится к программируемой логической схеме для управления электрической установкой, в частности ядерной установкой. Технический результат заключается в сокращении использования логических ресурсов. Программируемая логическая схема содержит операционный блок, содержащий функциональные блоки (FB1, FBi, FBN) нескольких типов, причем функциональные блоки двух различных типов являются подходящими для выполнения по меньшей мере одной различающейся функции. Более конкретно, схема содержит по одному функциональному блоку каждого типа, причем функциональные блоки являются подходящими для того, чтобы один и тот же блок вызывался несколько раз, а исполнительный модуль выполнен с возможностью выполнять вызываемый функциональный блок (блоки) последовательно, в соответствии с указанной последовательностью. 2 н. и 16 з.п. ф-лы, 6 ил.

1. Программируемая логическая схема (10) для управления электрической установкой, в частности ядерной установкой, содержащая операционный блок (14), содержащий

- функциональные блоки (FB1, FBi, FBN) нескольких типов, причем функциональные блоки двух различных типов являются подходящими для выполнения по меньшей мере одной различающейся функции,

- по меньшей мере один модуль обработки, подходящий для приема по меньшей мере одной последовательности (46) функционального блока или функциональных блоков, которые должны быть выполнены, и

- по меньшей мере одну внутреннюю память (38), выполненную с возможностью хранить по меньшей мере указанную последовательность (46),

отличающаяся тем, что содержит по одному функциональному блоку каждого типа, причем функциональные блоки являются подходящими для того, чтобы один и тот же блок вызывался несколько раз, и исполнительный модуль (22), выполненный с возможностью выполнять вызываемый функциональный блок (блоки) последовательно, в соответствии с указанной последовательностью (46).

2. Программируемая логическая схема (10) по п.1, которая является схемой FPGA типа.

3. Программируемая логическая схема (10) по п.1 или 2, в которой исполнительный модуль (22) представляет собой конечный автомат.

4. Программируемая логическая схема (10) по любому из пп.1-3, в которой операционный блок (14) дополнительно содержит несколько (64) распараллеливаемых блоков с плавающей запятой (FPU).

5. Программируемая логическая схема (PM) по любому из пп.1-4, в которой по меньшей мере один модуль обработки является подходящим для приема прикладной программы (34), соответствующей группе компьютерных файлов конфигурации, содержащей указанную последовательность, и по меньшей мере одному другому компьютерному файлу, принадлежащему группе, содержащей:

- файл (36) конфигурации памяти (38), соответствующий таблице, ассоциирующей по меньшей мере с одним входным/выходным сигналом программируемой логической схемы (PM) адрес в ее памяти (38),

- файл (40) со значением (значениями) параметра (параметров) функционального блока (блоков), подходящий для выполнения по меньшей мере одной функции с использованием параметра,

- файл (42), в котором для каждого функционального блока перечислены адрес или адреса памяти, выделенной для одного или нескольких входов этого функционального блока,

- файл (44), в котором для каждого функционального блока перечислены адрес или адреса памяти, выделенной для одного или нескольких выходов этого функционального блока.

6. Программируемая логическая схема (PM) по п.5, в которой порядок значений параметров в файле (40) установлен в соответствии с указанной последовательностью функционального блока (блоков), который должен быть выполнен.

7. Программируемая логическая схема (PM) по любому из пп.1-6, в которой память (38) содержит по меньшей мере две области (48, 50) хранения данных, предназначенные для двоичных данных и аналоговых данных соответственно.

8. Программируемая логическая схема (PM) по п.7, в которой каждая область (48, 50) хранения содержит по меньшей мере три выделенных подобластей:

- по меньшей мере одну подобласть (52, 58), выделенную для входных данных программируемой логической схемы (10),

- по меньшей мере одну подобласть (56, 62), выделенную для выходных данных программируемой логической схемы (10),

- по меньшей мере одну подобласть (54, 60), выделенную для временных данных, полученных во время выполнения указанной последовательности (46).

9. Программируемая логическая схема (PM) по п.8, в которой подобласти (52, 58), выделенные для входных данных, или подобласти (56, 62), выделенные для выходных данных, являются синхронными триггерными регистрами.

10. Устройство управления для управления электрической установкой, в частности ядерной установкой, содержащее по меньшей мере одну программируемую логическую схему (10) по любому из пп.1-9.

11. Устройство управления по п.10, которое содержит несколько программируемых логических схем (10) по любому из пп.1-9.

12. Устройство управления по п.10 или 11, дополнительно содержащее:

- по меньшей мере один модуль (84) электропитания;

- вспомогательные модули среди одного или нескольких модулей (86), выделенных для получения различных входных данных, одного или нескольких модулей (88), выделенных для публикации различных выходных данных, и одного или нескольких модулей (68) диагностики технического обслуживания, и

- коммуникационную шину (70), выполненную с возможностью соединять программируемую логическую схему (схемы) (10) со вспомогательными модулями (86, 88, 68).

13. Устройство управления по п.12, в котором коммуникационная шина (70) содержит четыре многоточечных линий сигнализации дифференциального низкого напряжения (M-LVDS), предназначенных соответственно для входных данных и выходных данных каждой программируемой логической схемы (10) в каждом направлении передачи.

14. Устройство управления по любому из пп.11-13, содержащее волоконно-оптическую сеть (92) связи, выполненную с возможностью соединять указанные несколько программируемых логических схем (10).

15. Устройство управления по любому из пп.11-14, в котором ведущая программируемая логическая схема (10а) из указанных нескольких программируемых логических схем (10) является подходящей для подключения к тактовому генератору и выполнена с возможностью синхронизировать другие программируемые логические схемы из указанных нескольких программируемых логических схем (10) посредством волоконно-оптической сети (92) связи.

16. Устройство управления по п.15, в котором ведущая программируемая логическая схема (10а) также выполнена с возможностью синхронизировать вспомогательные модули посредством коммуникационной шины (70).

17. Устройство управления по любому из пп.11-16, в котором указанные несколько программируемых логических схем (10, 10а, 10b) размещены в одной стойке (82).

18. Устройство управления по любому из пп.11-17, в котором программируемые логические схемы (10, 10а, 10b) из указанных нескольких программируемых логических схем разделены по меньшей мере на две отдельные стойки (90А, 90B, 90C).

| PHILLIP MCNELLES, Dynamic safety assessment of FPGA-based safety critical systems with applications in nuclear power generation, University of Ontario Institute of Technology, 12.2016 | |||

| Zongwu | |||

| Xie и др., DSP/FPGA-based Highly Integrated Flexible Joint Robot, The 2009 IEEE/RSJ International Conference on Intelligent Robots and Systems, 2009 |

Авторы

Даты

2022-04-11—Публикация

2018-03-08—Подача