Область техники, к которой относится изобретение

Настоящее изобретение касается области логических схем обработки, микропроцессоров и связанной архитектуры набора команд, которые при исполнении процессором или другой логической схемой обработки осуществляют логические, математические или другие функциональные операции.

Уровень техники

Многопроцессорные системы становятся все более обычными системами. Приложения многопроцессорных систем включают в себя динамическое разбиение на области вплоть до настольных вычислений. Для того чтобы воспользоваться преимуществами многопроцессорных система исполняемый код может быть разделен на множество цепочек для исполнения различными обрабатывающими объектами. Каждая цепочка может быть исполнена параллельно другой. Более того, для увеличения использования обрабатывающего объекта может быть применен измененный порядок исполнения команд. При измененном порядке исполнения, команды могут быть исполнены тогда, когда станет доступен вход, нужный для таких команд. Таким образом, команда, которая появилась позже в последовательности кода может быть исполнена до команды, появившейся в последовательности кода раньше.

Краткое описание чертежей

Варианты осуществления изобретения показаны в качестве примера и не ограничены фиг. с приложенных чертежей:

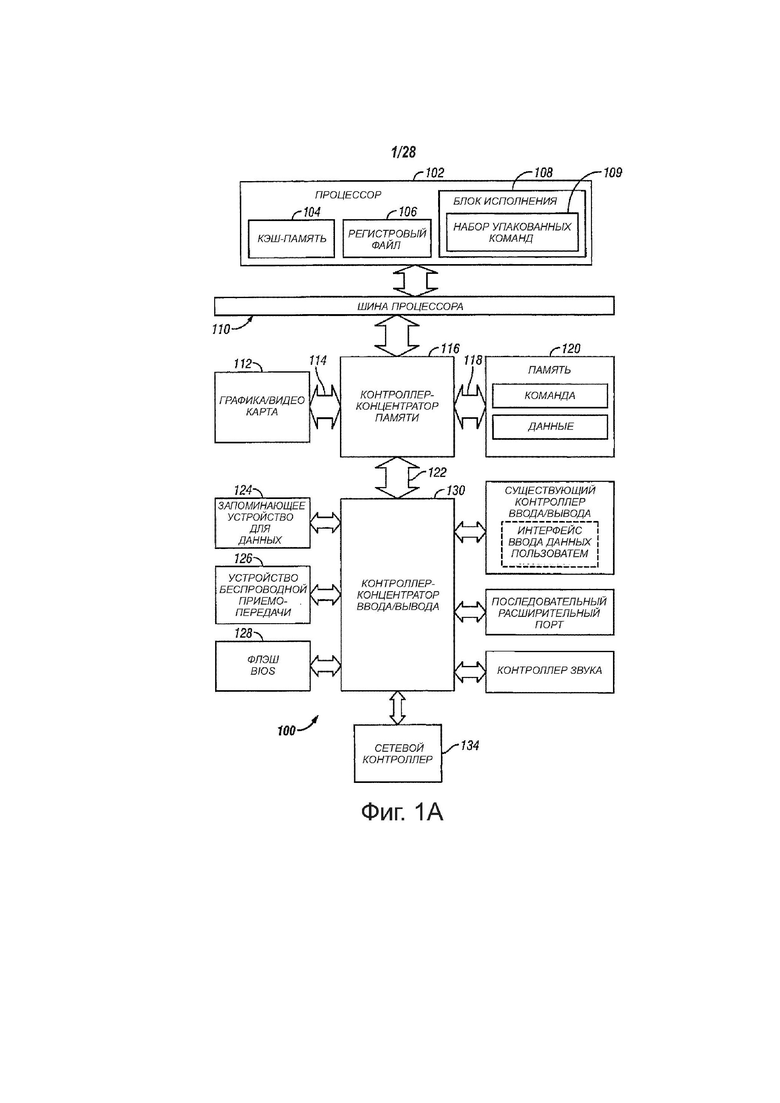

фиг. 1А - вид, показывающий структурную схему примера вычислительной системы, выполненной с процессором, который может содержать блоки исполнения для исполнения команды, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 1В - вид, показывающий систему обработки данных, в соответствии с вариантами осуществления настоящего изобретения;

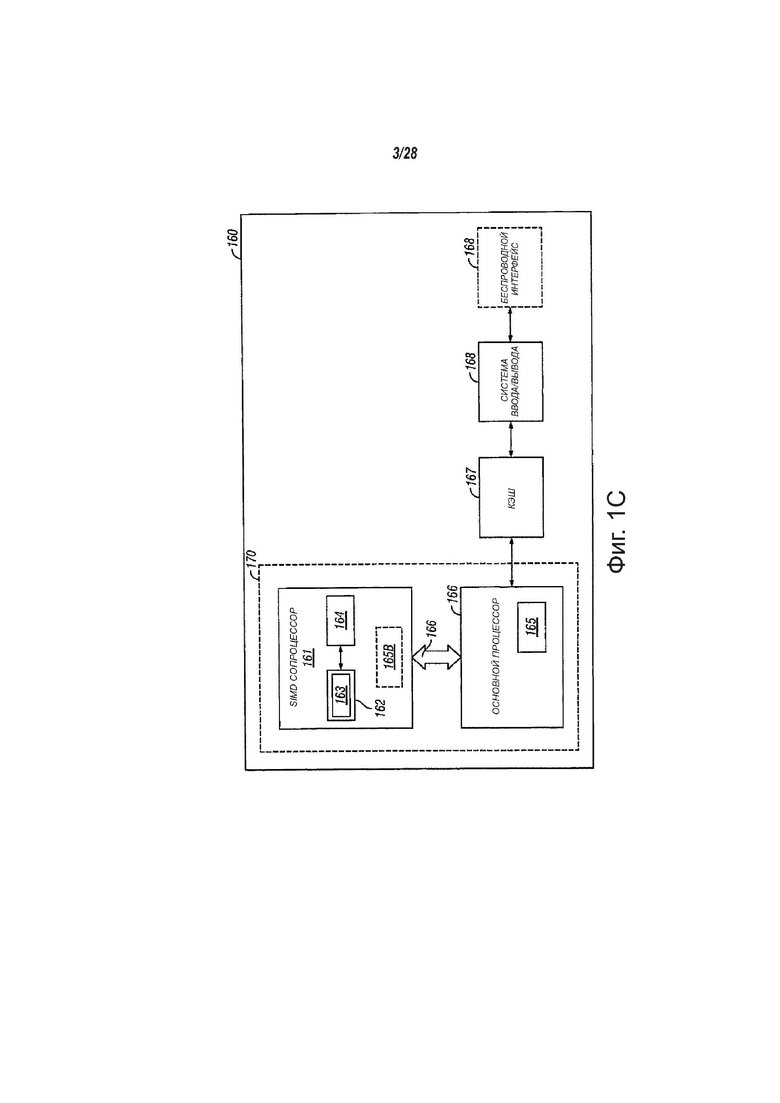

фиг. 1С - вид, показывающий другие варианты осуществления системы обработки данных для выполнения операций сравнения текстовых строк;

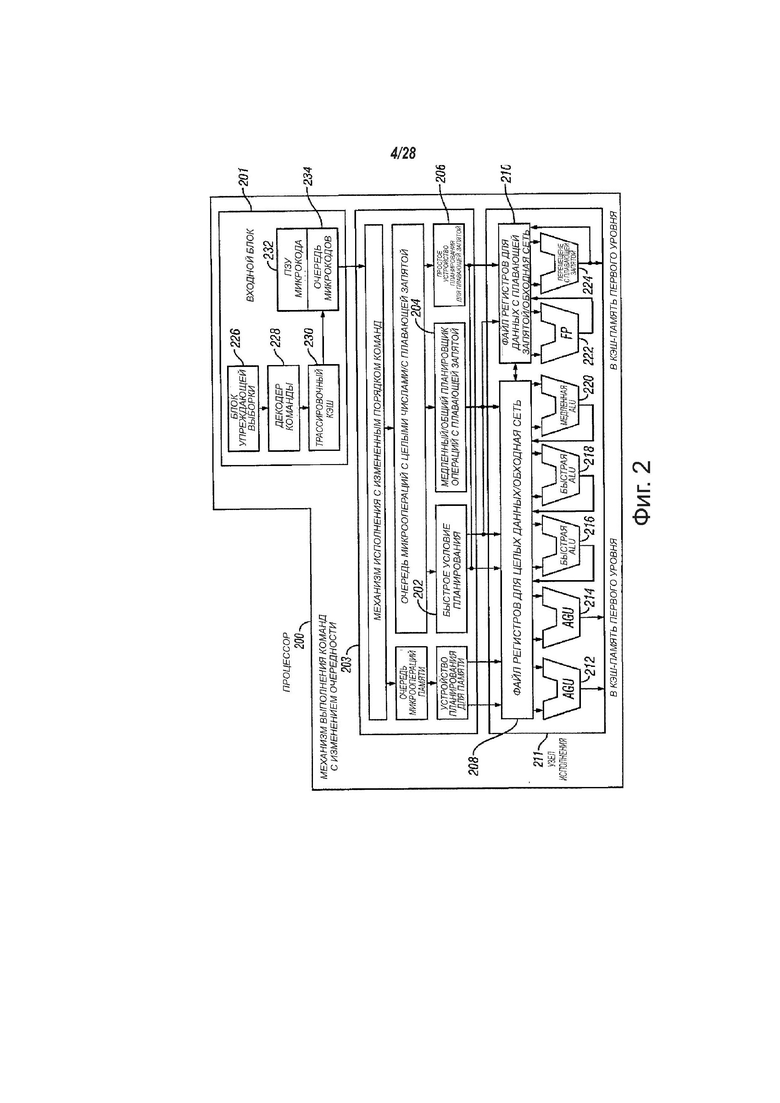

фиг. 2 - вид, показывающий структурную схему микроархитектуры для процессора, которая может содержать логические схемы для выполнения команд, в соответствии с вариантами осуществления настоящего изобретения;

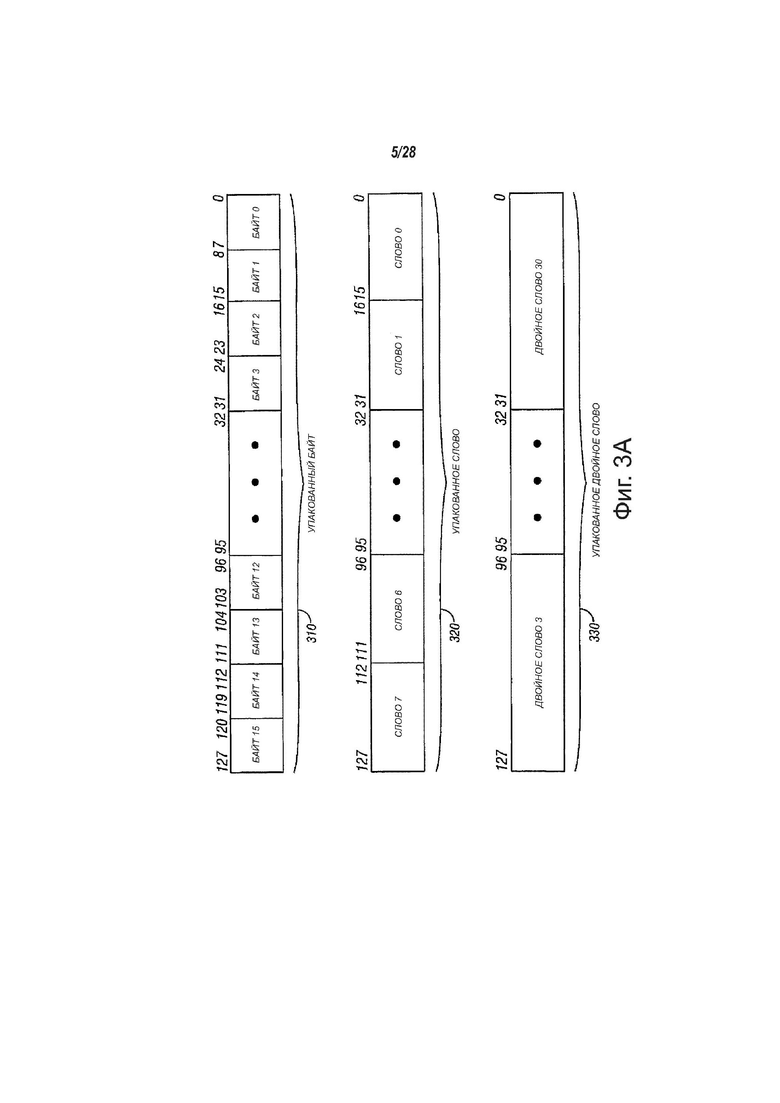

фиг. 3А - вид, показывающий различные представления типа данных «упакованные данные» в мультимедийных регистрах, в соответствии с вариантами осуществления настоящего изобретения;

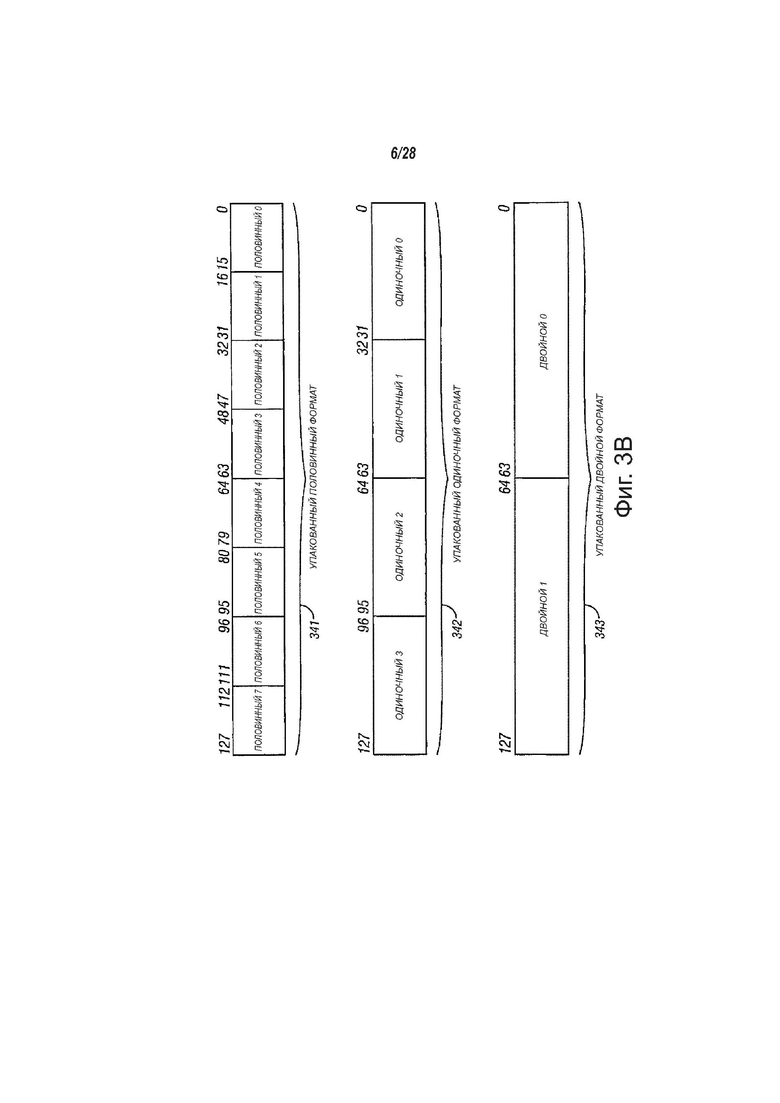

фиг. 3В - вид, показывающий возможные форматы хранения данных в регистре, в соответствии с вариантами осуществления настоящего изобретения;

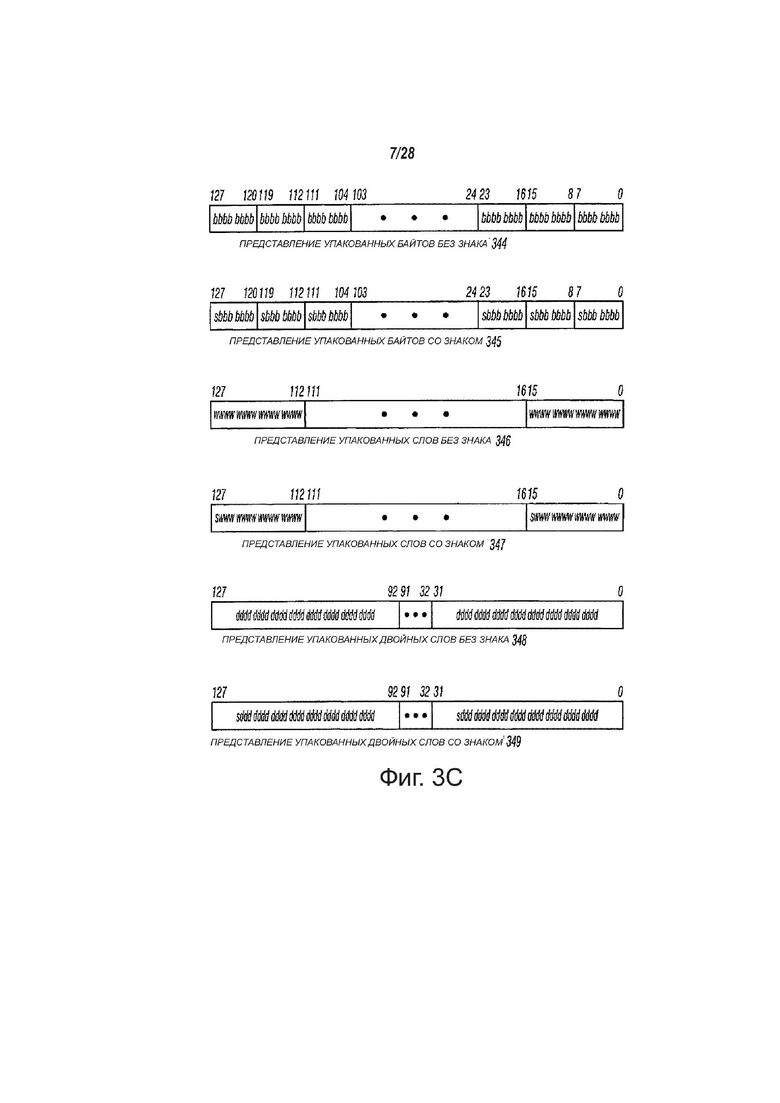

фиг. 3С - вид, показывающий различные представления типа данных «упакованные данные» со знаком и без знака в мультимедийных регистрах, в соответствии с вариантами осуществления настоящего изобретения;

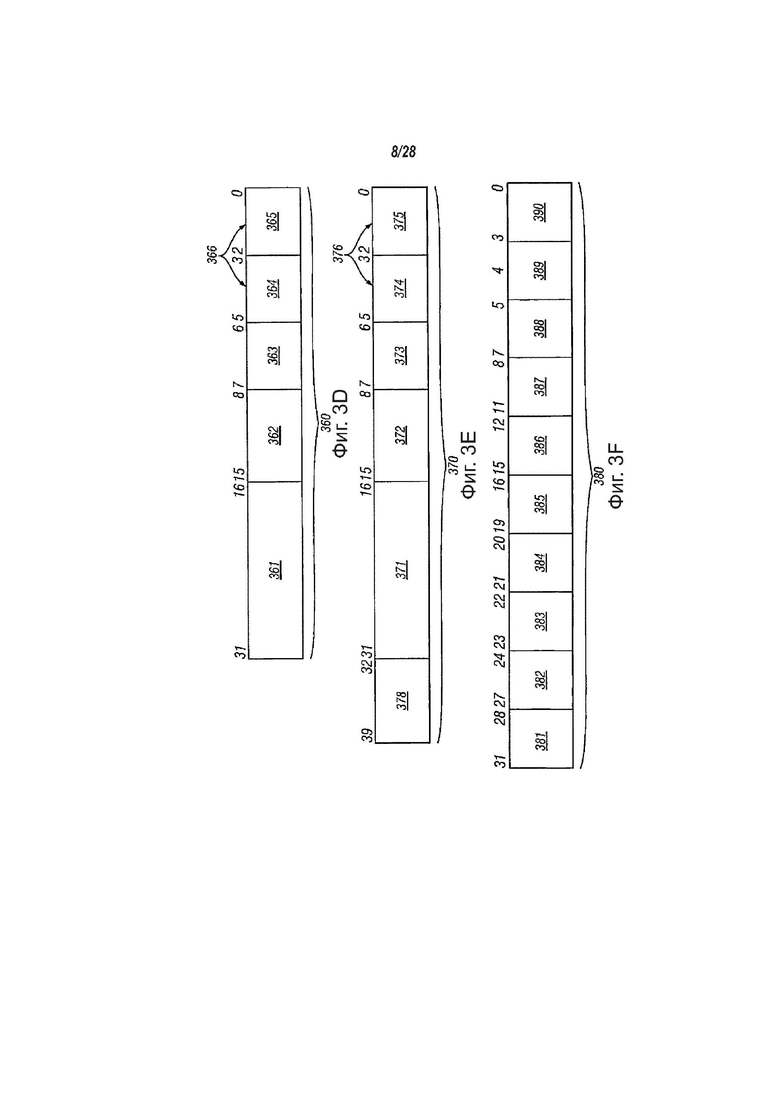

фиг. 3D - вид, показывающий один вариант осуществления формата кодирования операций;

фиг. 3E - вид, показывающий другой возможный формат кодирования операций, содержащий сорок и более битов, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 3F - вид, показывающий еще один возможный формат кодирования операций, в соответствии с вариантами осуществления настоящего изобретения;

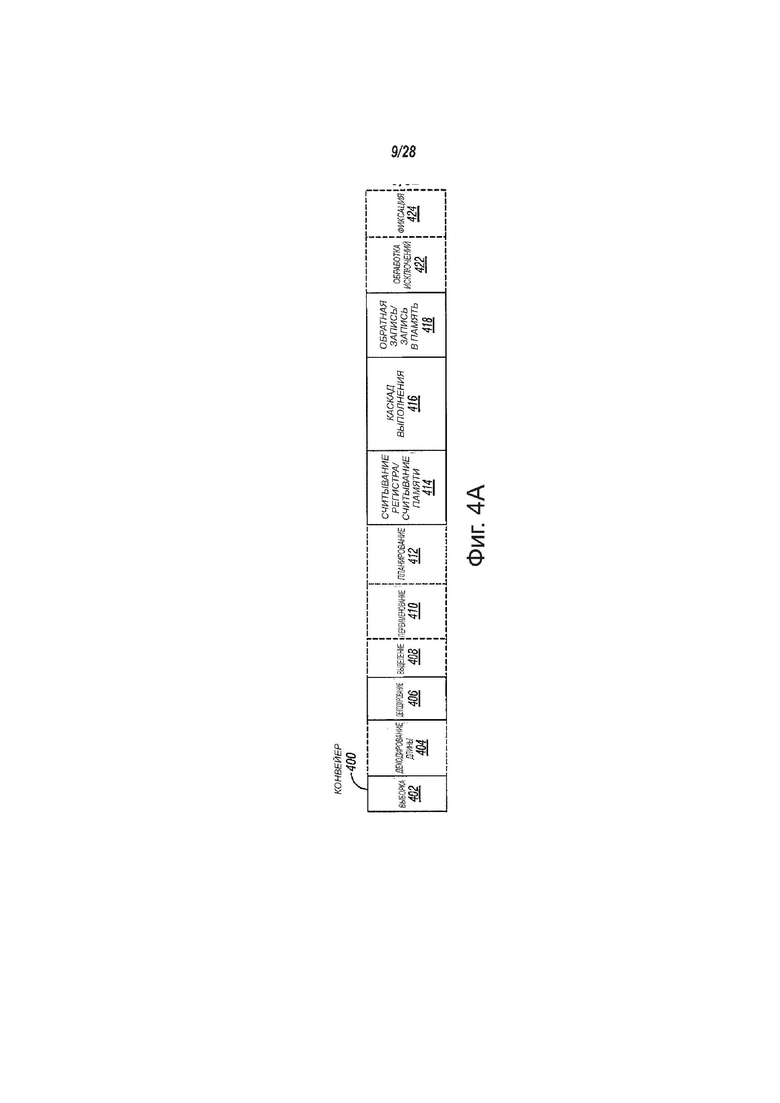

фиг. 4A - вид, показывающий структурную схему, иллюстрирующую конвейер с исполнением команд по очереди и конвейер с измененным порядком исполнения/выдачи команд, со ступенью переименования регистров, в соответствии с вариантами осуществления изобретения;

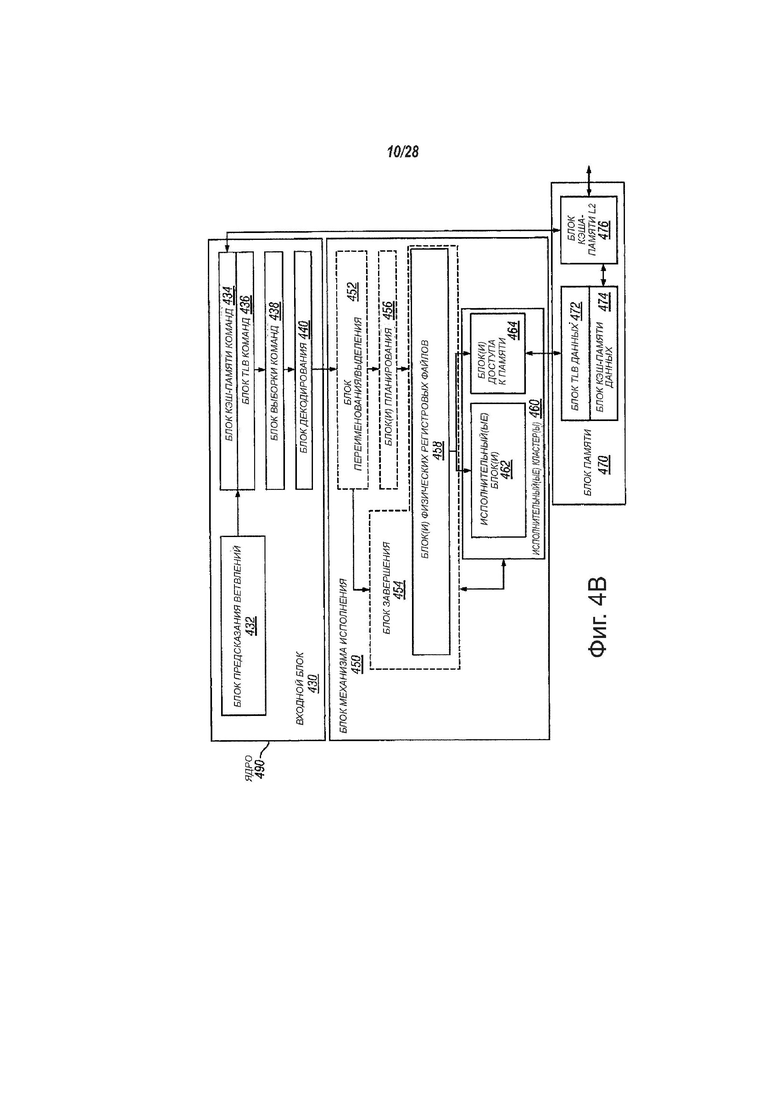

фиг. 4В - вид, показывающий структурную схему, иллюстрирующую архитектуру ядра с исполнением команд по очереди и подлежащую вхождению в процессор логическую схему с измененным порядком исполнения/выдачи команд и логическую схему переименования регистров, в соответствии с вариантами осуществления изобретения;

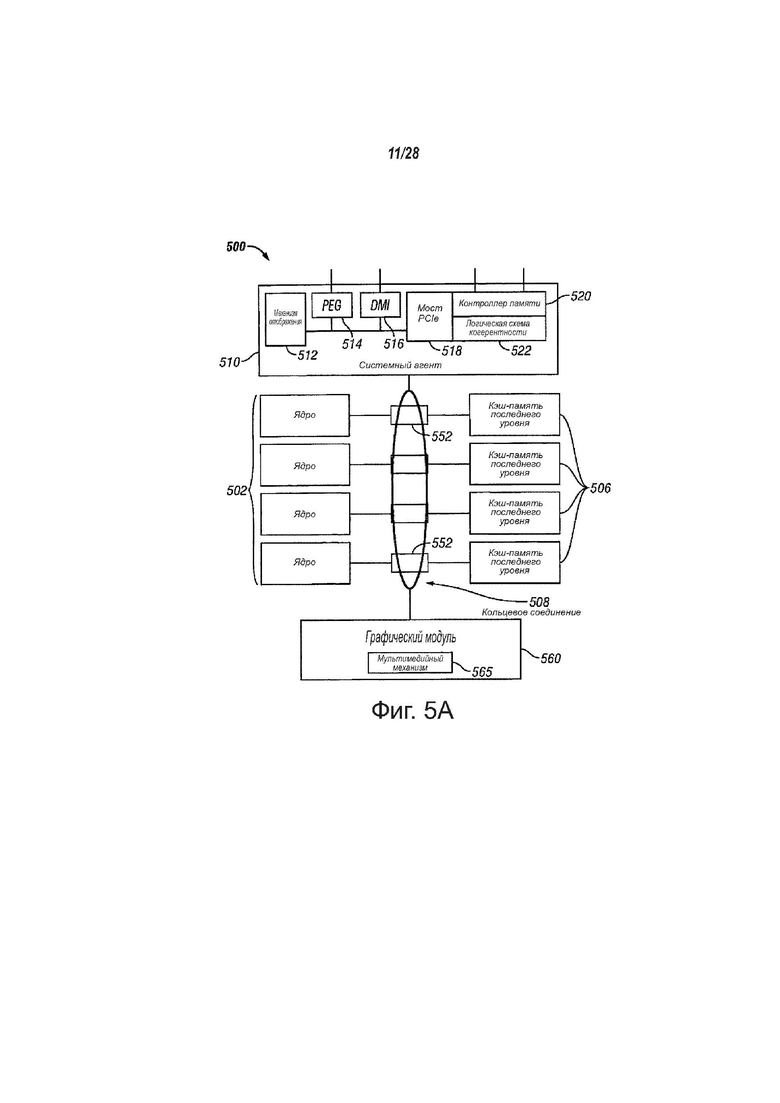

фиг. 5А - вид, показывающий структурную схему процессора, в соответствии с вариантами осуществления настоящего изобретения;

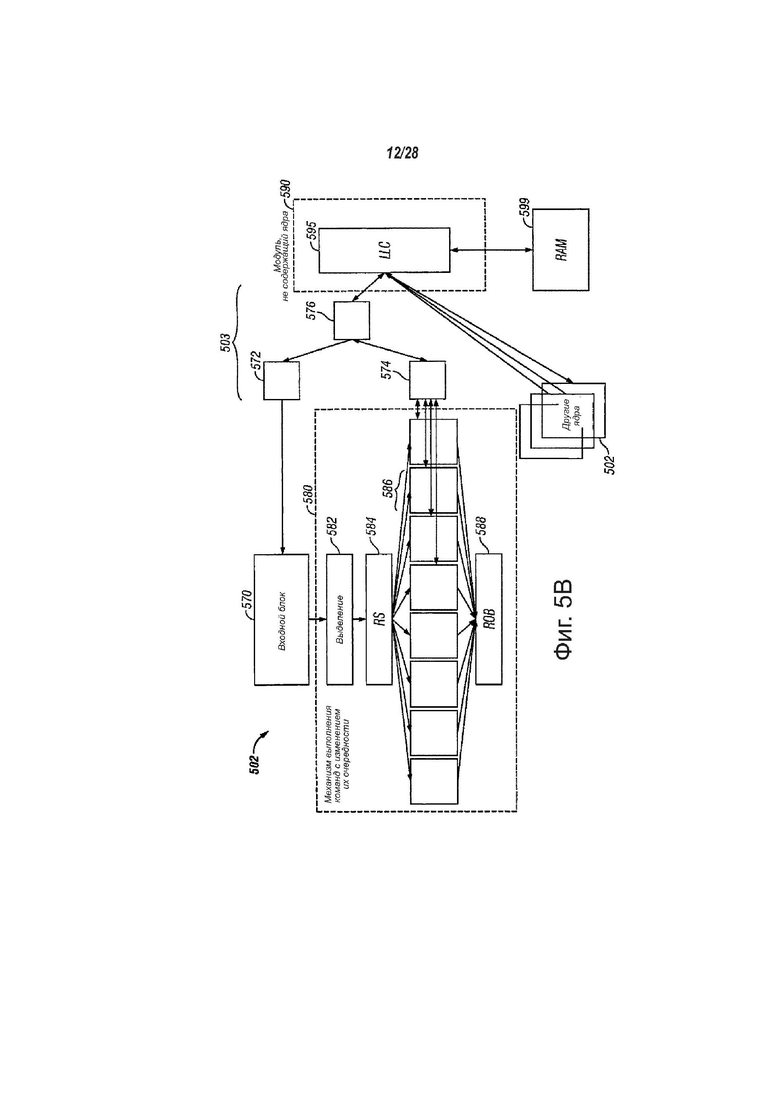

фиг. 5В - вид, показывающий структурную схему одного примера реализации ядра, в соответствии с вариантами осуществления настоящего изобретения;

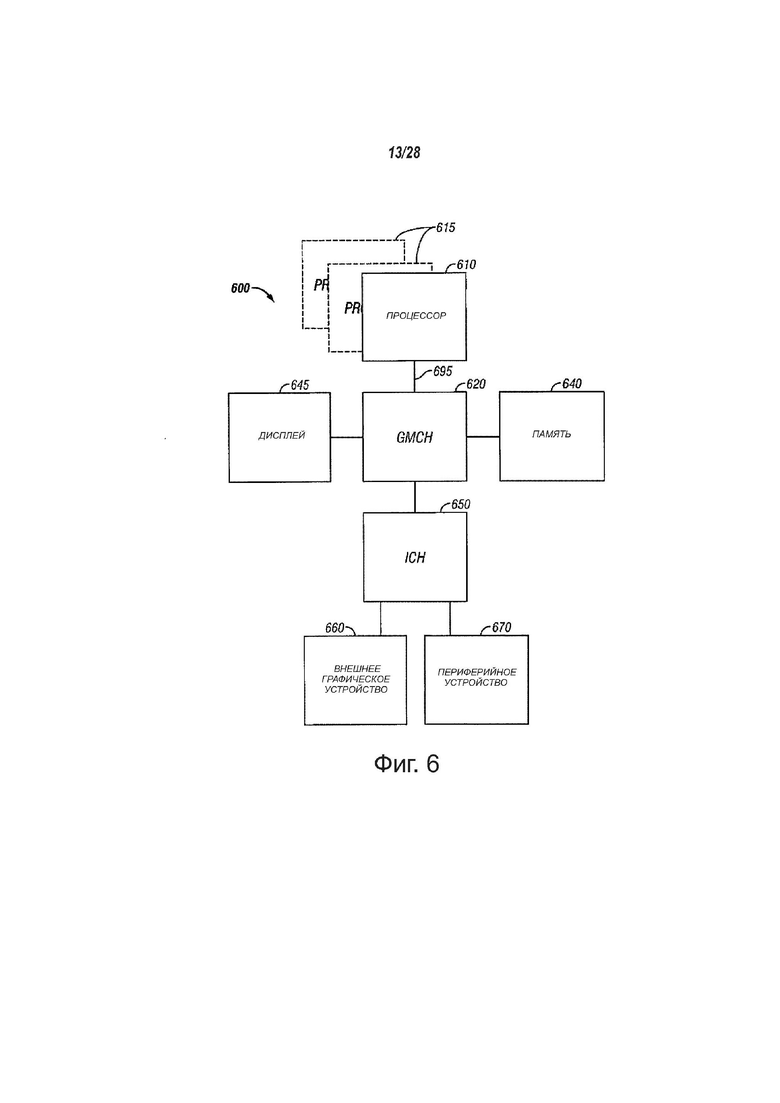

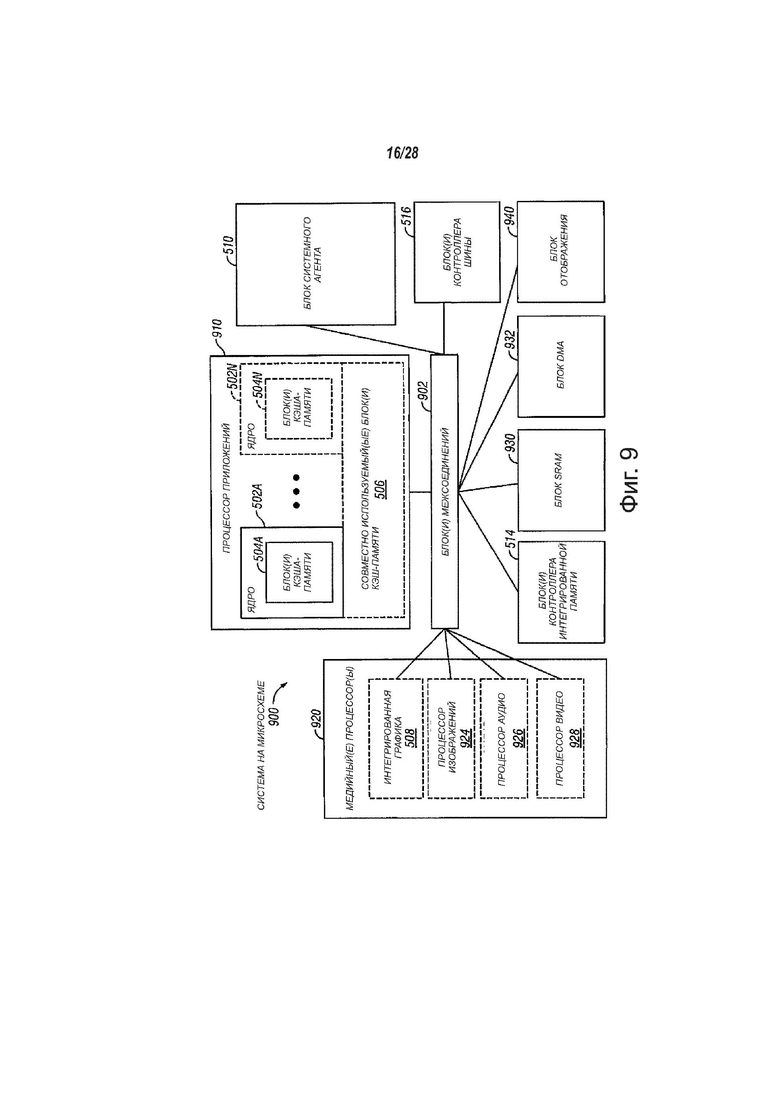

фиг. 6 - вид, показывающий структурную схему одной системы, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 7 - вид, показывающий структурную схему второй системы, в соответствии с вариантами осуществления настоящего изобретения;

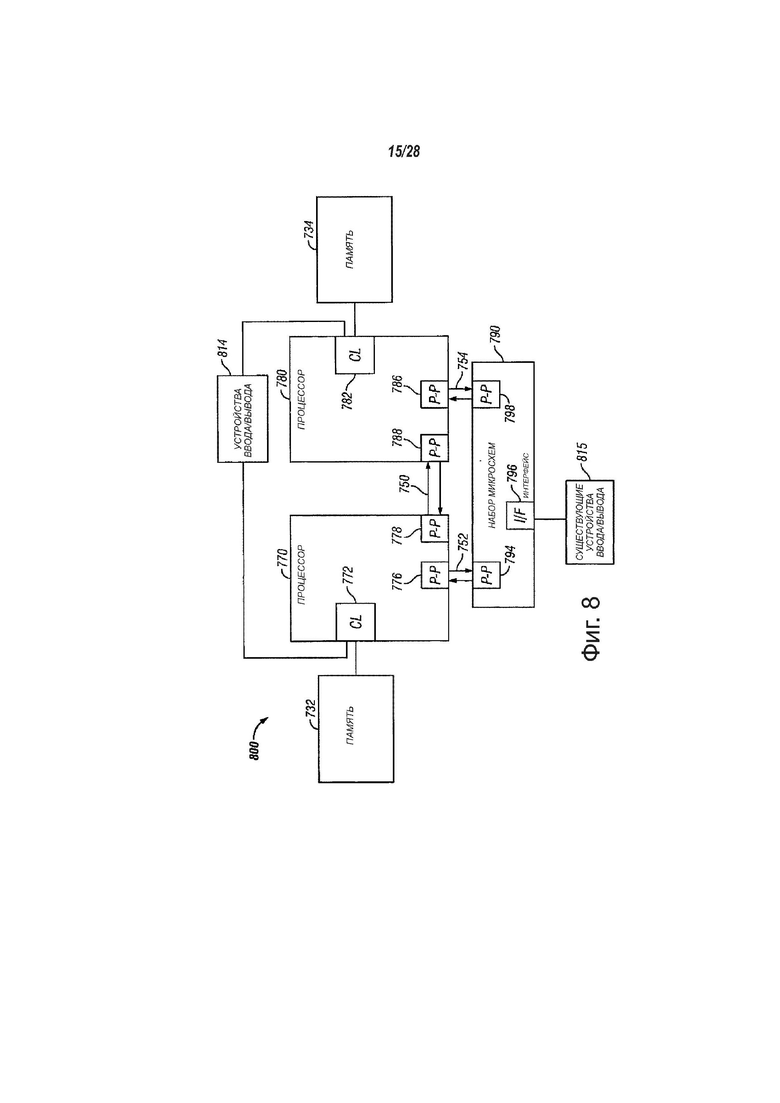

фиг. 8 - вид, показывающий структурную схему третьей системы, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 9 - вид, показывающий структурную схему системы-на-кристалле, в соответствии с вариантами осуществления настоящего изобретения;

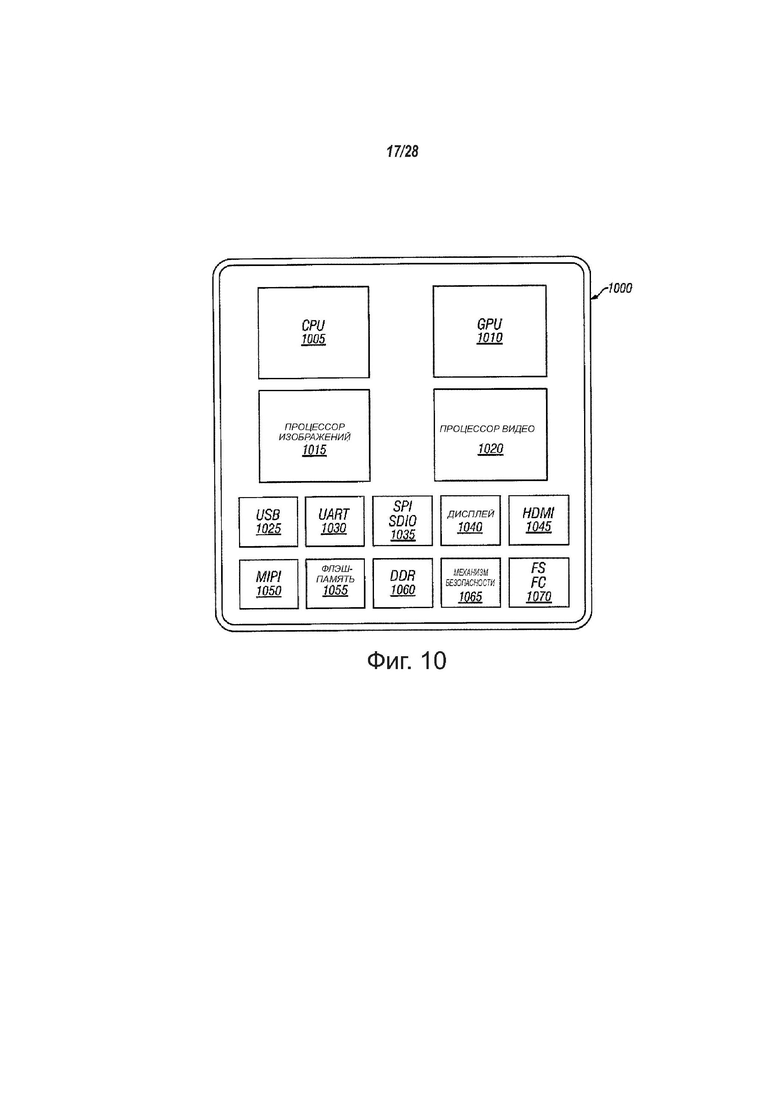

фиг. 10 - вид, показывающий процессор, содержащий центральный обрабатывающий блок и блок обработки графики, который может выполнить, по меньшей мере, одну команду, в соответствии с вариантами осуществления настоящего изобретения;

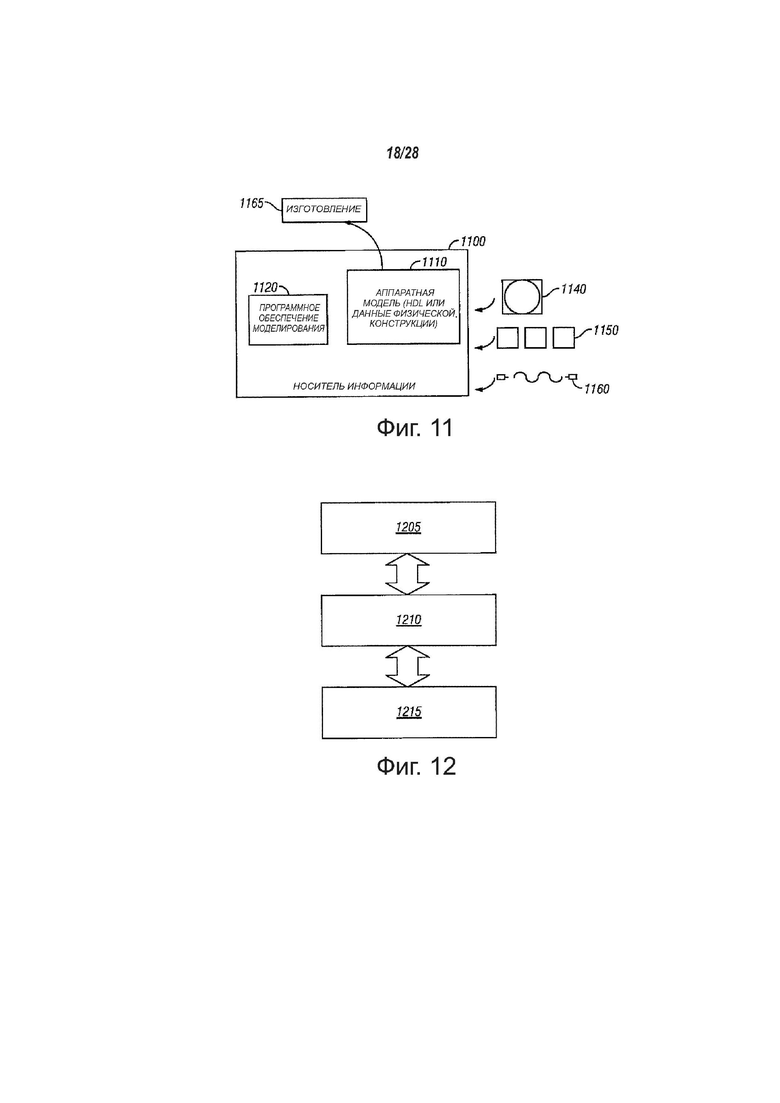

фиг. 11 - вид, показывающий структурную схему, иллюстрирующую развитие IP-ядер, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 12 - вид, показывающий, как команда первого типа может быть эмулирована процессором другого типа, в соответствии с вариантами осуществления настоящего изобретения;

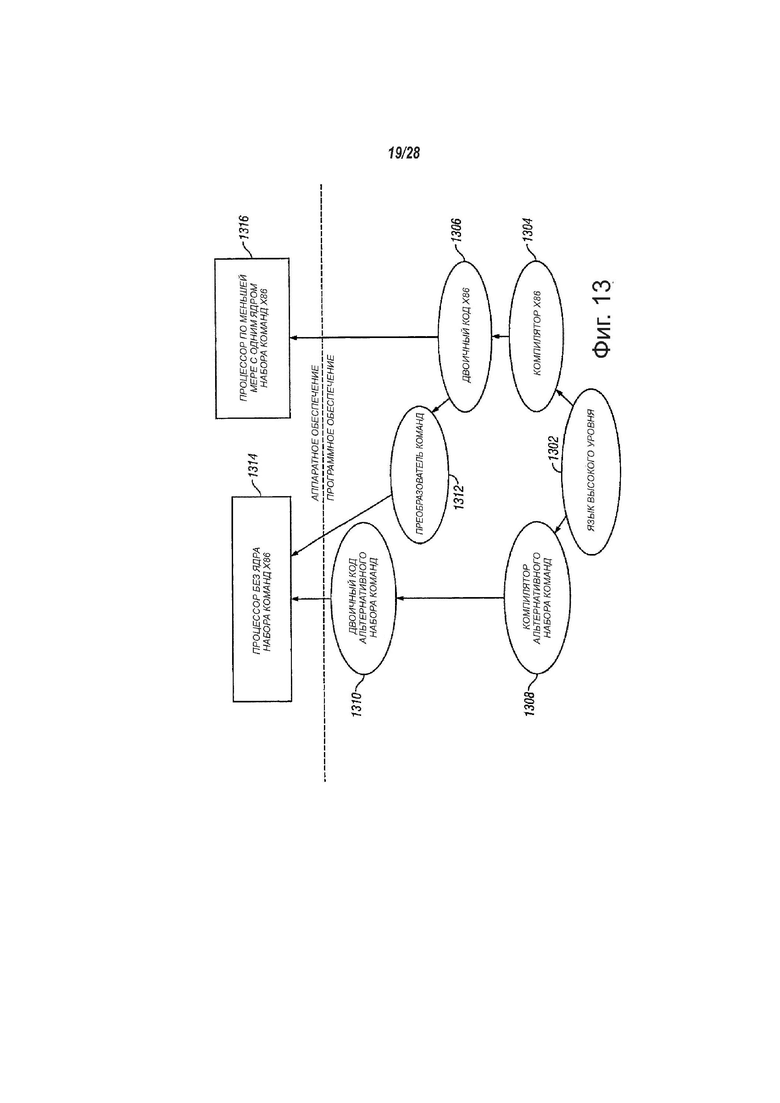

фиг. 13 - вид, показывающий структурную схему, иллюстрирующую использование программного устройства преобразования команд для преобразования двоичных команд исходного набора команд в двоичные команды целевого набора команд, в соответствии с вариантами осуществления изобретения;

фиг. 14 - вид, показывающий структурную схему одной архитектуры набора команд процессора, в соответствии с вариантами осуществления настоящего изобретения;

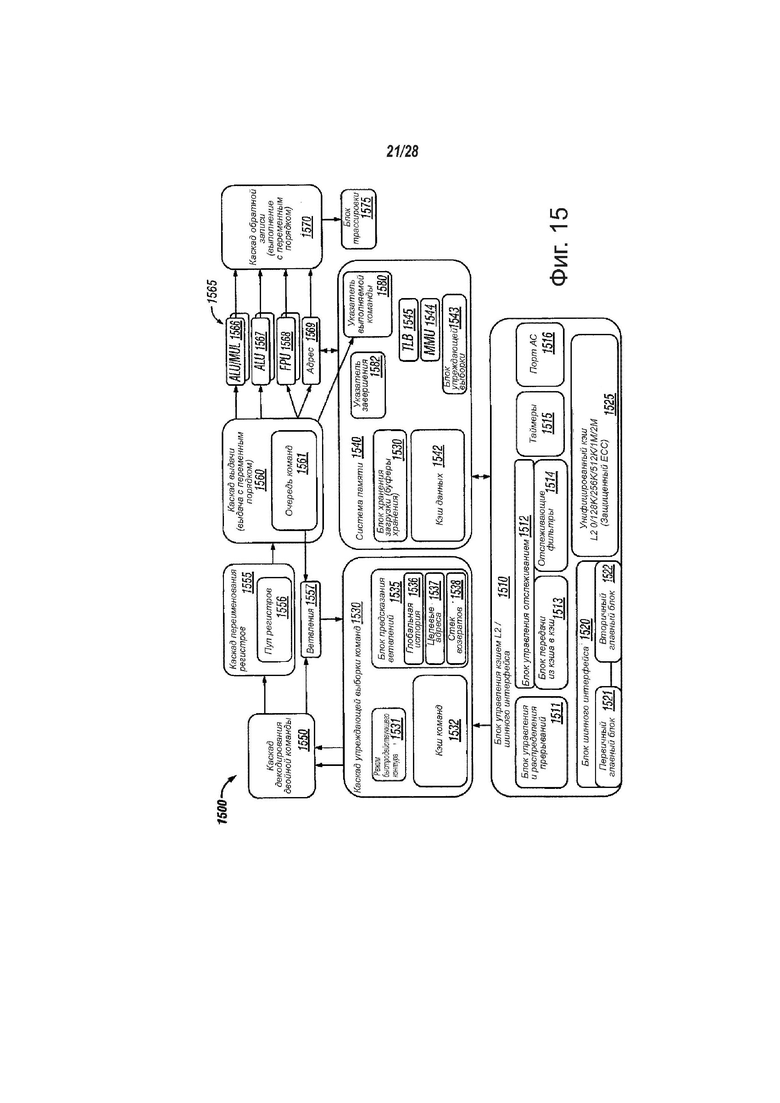

фиг. 15 - вид, более подробно показывающий структурную схему одной архитектуры набора команд процессора, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 16 - вид, показывающий структурную схему конвейера исполнения для процессора, в соответствии с вариантами осуществления настоящего изобретения;

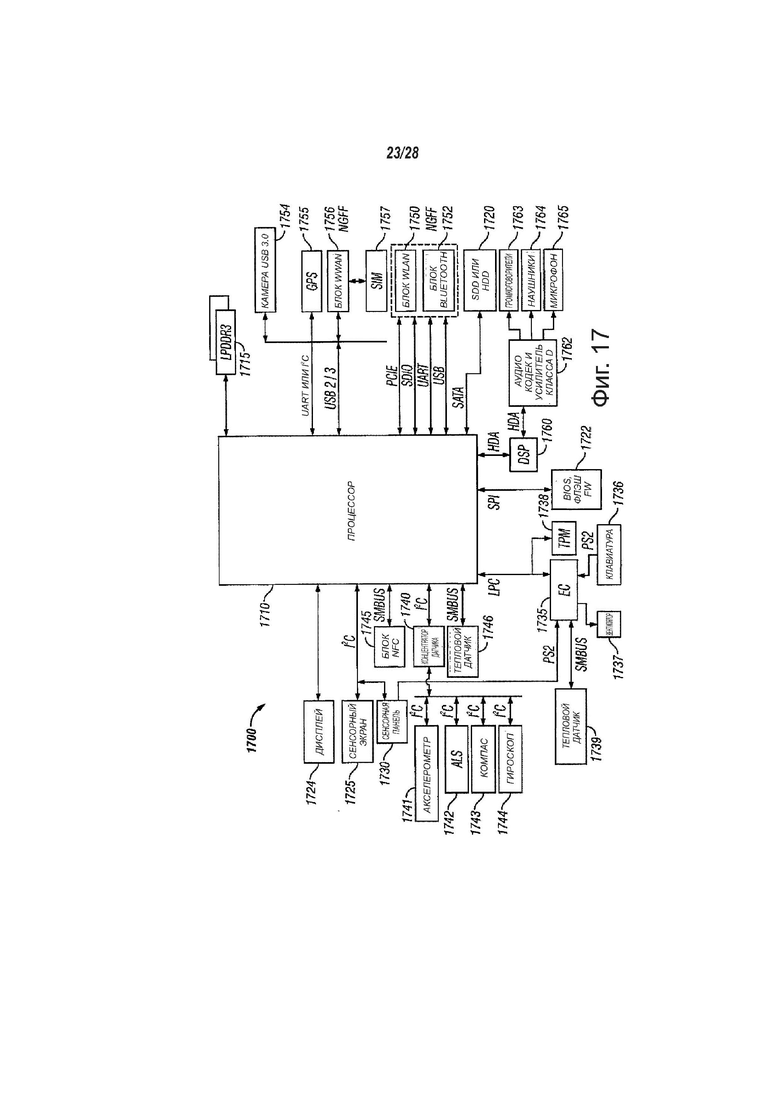

фиг. 17 - вид, показывающий структурную схему электронного устройства для использования процессора, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 18 - вид, показывающий пример системы для выгрузки и сортировки команд сохранения, в соответствии с вариантами осуществления настоящего изобретения;

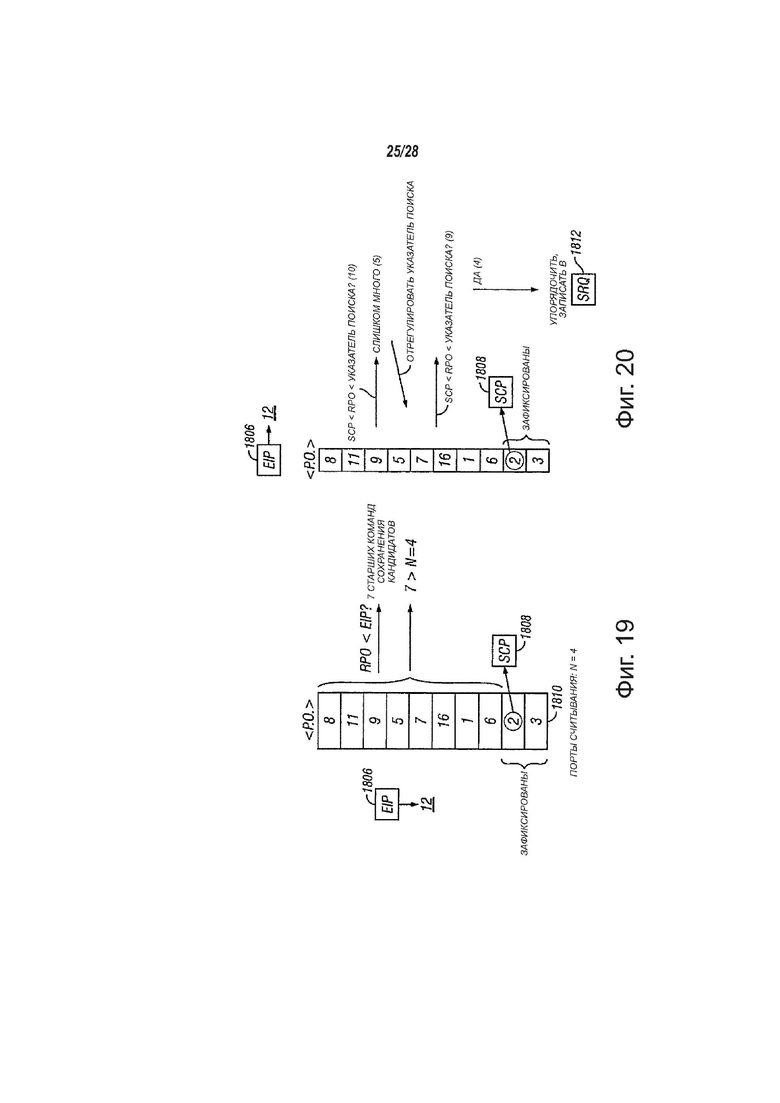

фиг. 19 - вид, показывающий ограничения, накладываемые на работу модуля поиска, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 20 - вид, показывающий пример работы модуля поиска с учетом ограничений, в соответствии с вариантами осуществления настоящего изобретения;

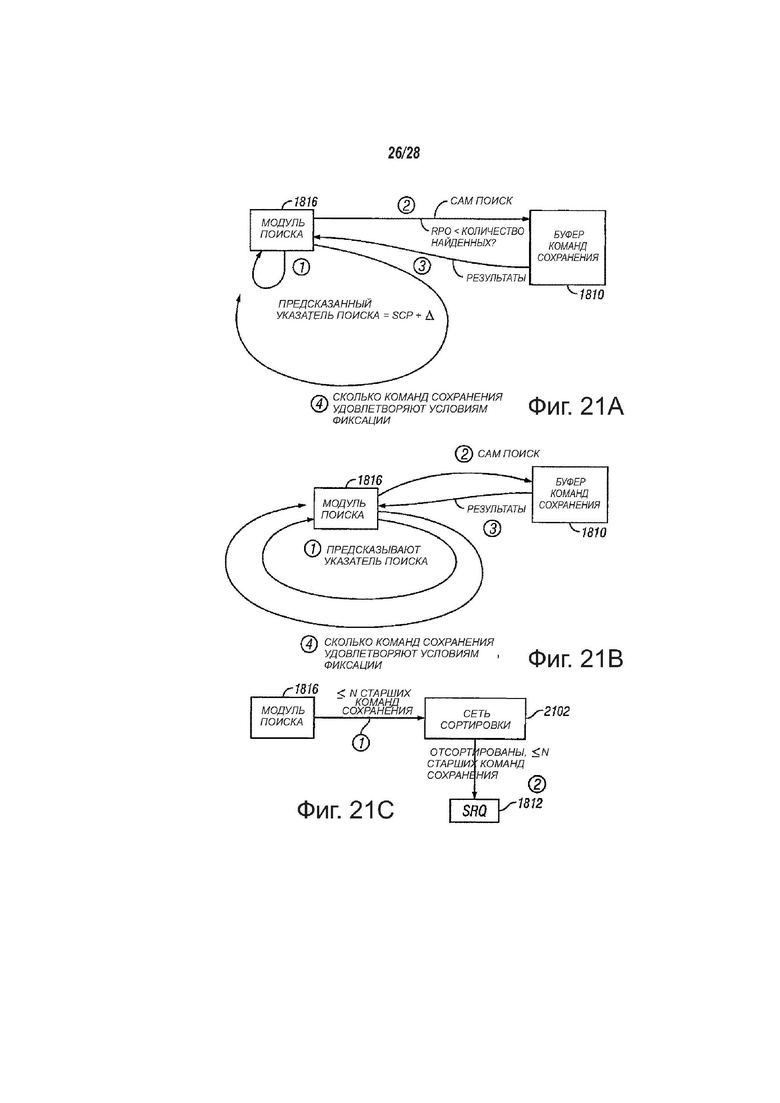

фиг. 21А, 21В и 21C - вид, показывающий пример работы модуля поиска, в соответствии с вариантами осуществления настоящего изобретения;

фиг. 22 - вид, показывающий пример работы модуля поиска по предсказанию или установке указателей поиска, в соответствии с вариантами осуществления настоящего изобретения;

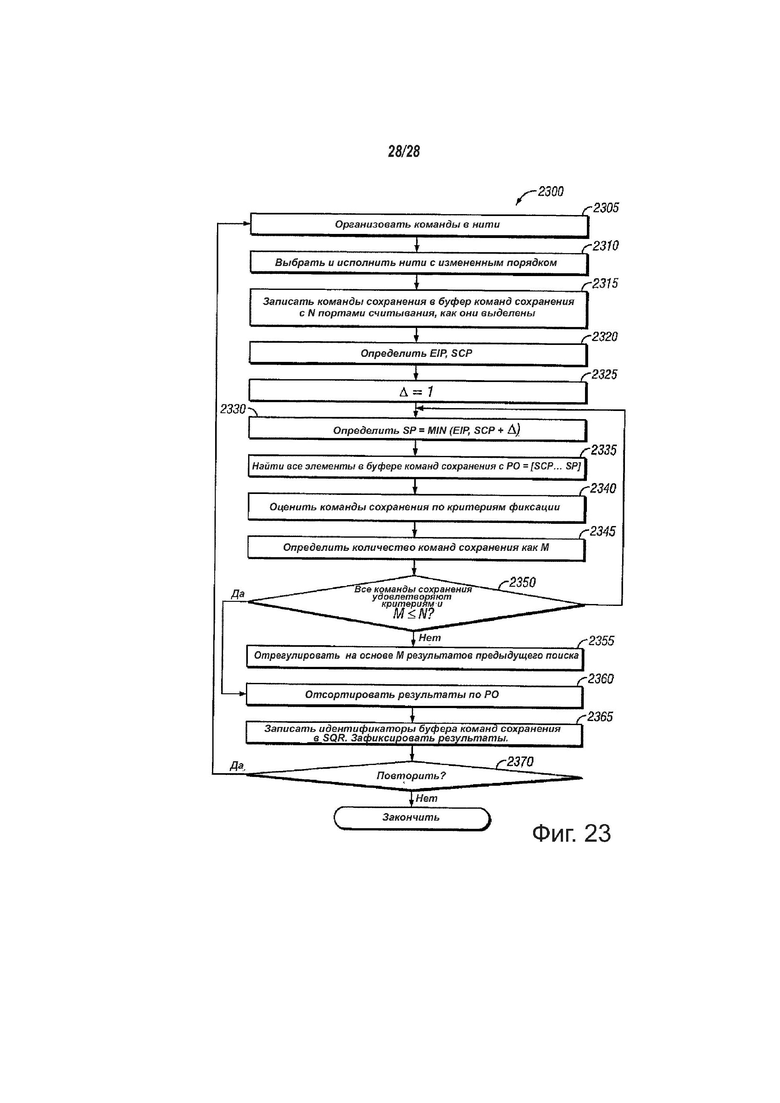

фиг. 23 - вид, показывающий пример варианта осуществления способа поиска и упорядочивания команд сохранения, в соответствии с вариантами осуществления настоящего изобретения.

Подробное описание изобретения

Далее описана команда и логическая схема обработки, для сортировки и выгрузки команд сохранения в процессоре или со связью с процессором, виртуальным процессором, пакетом, компьютерной системой или другим устройством обработки. Такое устройство обработки может содержать процессор с измененным порядком исполнения команд. Более того, такое устройство обработки может содержать многопоточный процессор с измененным порядком исполнением команд. Кроме того, сортировка и выгрузка команд сохранения может быть выполнена из неупорядоченного буфера, такого как буфер команд сохранения. В последующем описании, для обеспечения более глубокого понимания вариантов осуществления настоящего изобретения изложено большое количество конкретных деталей, таких как логическая схема обработки, типы процессоров, микроархитектурные условия, события, механизмы реализации и подобное. Тем не менее, специалистам в рассматриваемой области следует понимать, что варианты осуществления изобретения могут быть реализованы без подобных конкретных деталей. Дополнительно, некоторые хорошо известные структуры, схемы и подобное не показаны подробно, чтобы не создавать ненужные помехи пониманию вариантов осуществления настоящего изобретения.

Хотя приведенные ниже варианты осуществления изобретения описаны со ссылкой на один процессор, другие варианты осуществления изобретения применимы к другим типам интегральных схем и логических устройств. Аналогичные технологии и идеи вариантов осуществления настоящего изобретения могут быть применены в других типах схем или полупроводниковых устройств, которые могут получить пользу от более высокой пропускной способности конвейера и улучшенной производительности. Идеи вариантов осуществления настоящего изобретения применимы в любом процессоре или машине, которые осуществляют манипуляции с данными. Тем не менее, варианты осуществления изобретения не ограничены процессорами или машинами, которые выполняют операции с 512-битовыми, 256-битовыми, 128-битовыми, 64-битовыми, 32-битовыми или 16-битовыми данными, и могут быть применены в любом процессоре и машине, в которых могут быть выполнены манипуляции с данными или управление данными. Кроме того, в последующем описании приведены примеры и с иллюстративными целями на приложенных чертежах показаны различные примеры. Тем не менее, эти примеры не должны рассматриваться как ограничения, так как они приведены как примеры вариантов осуществления настоящего изобретения, а не для предоставления исчерпывающего списка всех возможных реализаций вариантов осуществления настоящего изобретения.

Хотя в приведенных ниже примерах описана обработка команд и их распределение в случае блоков исполнения и логических схем, другие варианты осуществления настоящего изобретения могут быть реализованы с помощью данных или команд, которые сохранены на считываемом машиной, материальном носителе и которые, при их выполнении машиной, побуждают машину выполнять функции, согласующиеся, по меньшей мере, с одним вариантом осуществления изобретения. В одном варианте осуществления изобретения функции, связанные с вариантами осуществления настоящего изобретения, реализованы в исполнимых машиной командах. Команды могут быть использованы для того, чтобы побудить процессор общего назначения или процессор специального назначения, который может быть запрограммирован этими командами, выполнить этапы настоящего изобретения. Варианты осуществления настоящего изобретения могут быть предоставлены как компьютерный программный продукт или программное обеспечение, которое может содержать считываемой машиной или компьютером носитель, на котором сохранены команды, которые можно использовать для программирования компьютера (или другого электронного устройства) с целью выполнения одной или нескольких операций, соответствующих вариантам осуществления настоящего изобретения. Более того, этапы вариантов осуществления настоящего изобретения могут быть выполнены с помощью специальных аппаратных компонентов, которые содержат логическую схему фиксированного назначения для выполнения этих этапов, или с помощью любой комбинации программируемых компонентов компьютера и аппаратных компонентов фиксированного назначения.

Команды, используемые для программирования логической схемы для выполнения вариантов осуществления настоящего изобретения, могут храниться в памяти системы, такой как DRAM, кэш-память, флеш-память или другое запоминающее устройство. Более того, команды могут быть распределены по сети или распределены с помощью других считываемых компьютером носителей. Таким образом, считываемый машиной носитель может являться любым механизмом для хранения или передачи информации в форме, считываемой машиной (например, компьютером), такой как, помимо прочего, гибкие диски, оптические диски, компакт-диски (CD-ROM) постоянного запоминающего устройства и магнитооптические диски, постоянное запоминающее устройство (ROM), оперативное запоминающее устройство (RAM), стираемое программируемое постоянное запоминающее устройство (EPROM), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM), магнитные или оптические карты, флеш-память или материальное, считываемое машиной запоминающее устройство, используемое при передаче информации по сети Интернет с помощью электрических, оптических, акустических или других форм распространяющихся сигналов (например, несущих волн, инфракрасных сигналов, цифровых сигналов и так далее). Соответственно, считываемый машиной носитель информации может содержать любой тип материального, считываемого компьютером носителя, подходящего для хранения или передачи электронных команд или информации в форме, считываемой машиной (например, компьютером).

Конструкция может проходить различные ступени от создания до моделирования и изготовления. Данные, представляющие конструкцию, могут представлять конструкцию различными способами. Во-первых, что может быть полезно при моделировании, аппаратное обеспечение может быть представлено с использованием языка описания аппаратного обеспечения или другого языка функционального описания. Кроме того, на некоторых ступенях процесса конструирования может быть изготовлена модель уровня схемы с логическими элементами и/или элементами-транзисторами. Более того, конструкции, на некоторой ступени, могут достичь уровня данных, представляющих физическое размещение различных устройств в модели аппаратного обеспечения. В случаях, когда используют некоторые технологии изготовления полупроводников, данные, представляющие модель аппаратного обеспечения, могут быть данными, определяющими наличие или отсутствие различных признаков на различных уровнях маски для масок, используемых для изготовления интегральной схемы. В любом представлении конструкции, данные могут быть сохранены в любой форме на считываемом машиной носителе. Память или магнитный или оптический накопитель, такой как диск, может быть считываемым машиной носителем для хранения информации, переданной с помощью оптической или электрической волны, модулированной или другим образом выработанной для передачи такой информации. Когда передают электрическую несущую волну, указывающую или несущую код или конструкцию, таким образом, что выполняют копирование, буферизацию или ретрансляцию электрического сигнала, может быть сделана новая копия. Таким образом, поставщик связи или поставщик доступа к сети может сохранять на материальном, считываемом машиной носителе, по меньшей мере, временно, изделие, такое как информация, закодированная в несущей волне и реализующая технологии вариантов осуществления настоящего изобретения.

В современных процессорах, для обработки и исполнения разного рода кода и команд может быть использовано большое количество разных блоков исполнения. Некоторые команды могут завершаться быстрее, а другие могут требовать для завершения некоторого количества тактовых циклов. Чем больше пропускная способность для команд, тем больше общая производительность процессора. Таким образом, предпочтительно, чтобы как можно большее количество команд исполнялось как можно быстрее. Тем не менее, могут присутствовать определенные команды, обладающие большей сложностью и требующие большего с точки зрения времени исполнения и ресурсов процессора, такие как команды с плавающей запятой, операции загрузки/сохранения, перемещения данных и так далее.

По мере использования большего количества компьютерных систем в интернет-приложениях, текстовых и мультимедийных приложениях, со временем была введена поддержка в виде дополнительного процессора. В одном варианте осуществления изобретения набор команд может быть связан с одной или несколькими архитектурами компьютера, содержащими типы данных, команды, архитектуру регистров, режимы адресации, архитектуру памяти, обработку прерываний и исключений и внешний ввод и вывод.

В одном варианте осуществления изобретения архитектура (ISA) набора команд может быть реализована одной или несколькими микроархитектурами, которые могут содержать логическую схему процессора и схемы, используемые для реализации одного или нескольких наборов команд. Соответственно, процессоры с различными микроархитектурами могут совместно использовать, по меньшей мере, часть общего набора команд. Например, процессоры Intel® Pentium 4, процессоры Intel® Core™ и процессоры компании Advanced Micro Devices, Inc., Саннивейл (Sunnyvale), Калифорния, реализуют практически идентичные версии набора х86 команд (с некоторыми расширениями, которые были добавлены в более новые версии), но обладают различными внутренними конструкциями. Аналогично, процессоры, разработанные другими компаниями-разработчиками процессоров, такими как ARM Holdings, Ltd., MIPS, или их лицензиаты или соразработчики, могут совместно использовать, по меньшей мере, часть общего набора команд, но могут обладать другими конструкциями. Например, одна и та же архитектура регистров из ISA может быть реализована различными путями в разных микроархитектурах, с использованием новых или хорошо известных технологий, в том числе специальных физических регистров, одного или нескольких динамических выделяемых физических регистров с использованием механизма переименования регистров (то есть, с использованием Таблицы (RAT) псевдонимов регистров, буфера (ROB) переупорядочивания и файла регистров выгрузки). В одном варианте осуществления изобретения регистры могут содержать один или несколько регистров, архитектур регистров, файлов регистров или других наборов регистров, которые могут как адресоваться, так и не адресоваться программистом.

Команда может подразумевать один или несколько форматов команд. В одном варианте осуществления изобретения формат команды может указывать различные поля (количество битов, расположение битов и так далее) для определения, помимо прочего, подлежащей выполнению операции и операндов, над которыми выполняют эту операцию. В еще одном варианте осуществления изобретения некоторые форматы команд могут быть дополнительно определены шаблонами команд (или подформатами). Например, шаблоны команды заданного формата команды могут быть определены так, что содержат разные подмножества полей формата команды и/или определены так, чтобы содержать заданное поле, интерпретируемое по-другому. В одном варианте осуществления изобретения команда может быть выражена с использованием некоторого формата команды (и, если определено, в одном из шаблонов команды для этого формата команды) и определяет или указывает операцию и операнды, над которыми будут выполнять эту операцию.

Научные, финансовые, автоматической векторизации общего назначения, RMS (распознавание, извлечение информации из данных и синтез) и визуальные и мультимедийные приложения (например, 2D/3D графика, обработка изображений, сжатие/распаковка видео, алгоритмы распознавания голоса и манипуляции звуком) могут требовать выполнения той же операции для большого количества элементов данных. В одном варианте осуществления изобретения тип команд (SIMD) с одним потоком команд и несколькими потоками данных представляет собой тип команд, который побуждает процессор выполнять операцию с множеством элементов данных. Технология SIMD может быть использована в процессорах, которые могут логически делить биты в регистре на некоторое количество элементов данных фиксированного размера или элементов данных переменного размера, каждый из которых представляет отдельное значение. Например, в одном варианте осуществления изобретения биты в 64-битовом регистре могут быть организованы как операнд-источник, содержащий четыре отдельных 16-битовых элемента данных, каждый из которых представляет отдельное 16-битовое значение. Этот тип данных может быть назван типом «упакованные» данные или типом «векторные» данные, и операнды этого типа данных могут называться операндами упакованных данных или векторными операндами. В одном варианте осуществления изобретения элемент упакованных данных или вектор может быть последовательностью элементов упакованных данных, сохраненной в одном регистре, и операнд упакованных данных или векторный операнд может быть операндом-источником или операндом-назначением SIMD команды (или «команды упакованных данных» или «векторной команды»). В одном варианте осуществления изобретения SIMD команда определяет одну векторную операцию, подлежащую выполнению для двух векторных операндов-источников с целью выработки векторного операнда-назначения (также называемого результирующим векторным операндом) такого же или другого размера, с таким же или другим количеством элементов данных и с таким же или другим порядком элементов данных.

Технология SIMD, такая, как использованная в процессорах Intel® Core™ с набором команд, содержащим команды x86, MMX™, потоковые SIMD расширения (SSE), SSE2, SSE3, SSE4.1 и SSE4.2, процессорах ARM, таких как семейство процессоров ARM Cortex®, набор команд которых содержит векторные команды (VFP) с плавающей запятой и/или команды NEON, и процессорах MIPS, таких как семейство процессоров Loongson, разработанные Институтом вычислительной технологии (ICT) китайской Академии наук, позволила значительно улучшить производительность приложений (Core™ и MMX™ являются зарегистрированными торговыми марками или торговыми марками компании Intel Corporation, Санта-Клара (Santa Clara), Калифорния).

В одном варианте осуществления изобретения регистры/данные назначения и источника могут быть общими терминами, представляющими источник и назначение соответствующих данных или операции. В некоторых вариантах осуществления изобретения они могут быть реализованы с помощью регистров, памяти или других областей хранения, обладающих названиями или функциями, отличающимися от упомянутых. Например, в одном варианте осуществления изобретения «DEST1» может быть регистром временного хранения или другой областью хранения, а «SRC1» и «SRC2» могут быть первым и вторым регистром-источником для хранения или другой областью хранения и так далее. В других вариантах осуществления изобретения две или несколько SRC и DEST областей хранения могут соответствовать разным элементам хранения данных в одной области хранения (например, SIMD регистр). В одном варианте осуществления изобретения один из регистров-источников также может выступать как регистр-назначение, например, благодаря обратной записи результата операции, выполненной с первыми и вторыми исходными данными, в один из двух регистров-источников, служащих в качестве регистров-назначений.

На фиг. 1А показана структурная схема примера вычислительной системы, выполненной с процессором, который может содержать блоки исполнения для исполнения команды, в соответствии с вариантами осуществления настоящего изобретения. Система 100 может содержать компонент, такой как процессор 102, для применения блоков исполнения, содержащих логическую схему для выполнения алгоритмов по обработке данных, в соответствии с настоящим изобретением, например, в соответствии с описанным в настоящем документе вариантом осуществления изобретения. Система 100 может быть представителем систем обработки, основанных на микропроцессорах PENTIUM® III, PENTIUM® 4, Xeon™, Itanium®, XScale™ и/или StrongARM™ компании Intel Corporation, Санта-Клара, Калифорния, хотя также могут быть использованы другие системы (в том числе PC с другими микропроцессорами, инженерные рабочие станции, телевизионные приставки и подобное). В одном варианте осуществления изобретения пример системы 100 может исполнять версию операционной системы WINDOWS™ компании Microsoft Corporation, Редмонд (Redmond), Вашингтон, хотя также могут быть использованы другие операционные системы (например, UNIX и Linux), встроенное программное обеспечение и/или графические интерфейсы пользователя. Таким образом, варианты осуществления настоящего изобретения не ограничены какой-либо конкретной комбинацией аппаратной схемы и программного обеспечения.

Варианты осуществления изобретения не ограничены компьютерными системами. Варианты осуществления настоящего изобретения могут быть использованы в других устройствах, таких как карманные устройства и встроенные приложения. Некоторыми примерами карманных устройств являются сотовые телефоны, устройства интернет-протокола, цифровые фотокамеры, персональные цифровые помощники (PDA) и карманные PC. Встроенными приложениями могут являться микроконтроллер, цифровой сигнальный процессор (DSP), система на микросхеме, сетевые компьютеры (NetPC), телевизионные приставки, сетевые концентраторы, коммутаторы глобальной вычислительной сети (WAN) или любая другая система, которая может выполнить одну или несколько команд в соответствии, по меньшей мере, в одним вариантом осуществления изобретения.

Компьютерная система 100 может содержать процессор 102, который может содержать один или несколько блоков 108 исполнения для выполнения алгоритма с целью исполнения, по меньшей мере, одной команды в соответствии с одним вариантом осуществления настоящего изобретения. Один вариант осуществления изобретения может быть описан в контексте однопроцессорной настольной или серверной системы, но другие варианты осуществления изобретения могут содержать многопроцессорную систему. Система 100 может быть примером «блочной» архитектуры системы. Система 100 может содержать процессор 102 для обработки сигналов данных. Процессор 102 может содержать микропроцессор (CISC) со сложным набором команд, микропроцессор (RISC) с сокращенным набором команд, микропроцессор (VLIW) с очень длинным командным словом, процессор, реализующий комбинации наборов команд, или любое другое процессорное устройство, такое как, например, цифровой сигнальный процессор. В одном варианте осуществления изобретения процессор 102 может быть связан с шиной 110 процессора, которая может передавать сигналы данных между процессором 102 и другими компонентами в системе 100. Элементы системы 100 могут выполнять обычные функции, хорошо известные специалистам в рассматриваемой области.

В одном варианте осуществления изобретения процессор 102 может содержать внутреннюю кэш-память 104 уровня 1 (L1). В зависимости от архитектуры, процессор 102 может содержать одну внутреннюю кэш-память или несколько уровней внутренней кэш-памяти. В другом варианте осуществления изобретения кэш-память может быть внешней по отношению к процессору 102. Другие варианты осуществления изобретения могут также содержать комбинацию как внутренних, так и внешних кэш-памятей, в зависимости от конкретной реализации и потребностей. Файл 106 регистров может хранить данные различных типов в различных регистрах, в том числе регистрах целых чисел, регистрах чисел с плавающей запятой, регистрах состояния и регистре указателей команд.

Блок 108 исполнения, содержащий логическую схему для выполнения операций с целыми числами и числами с плавающей запятой, также расположен в процессоре 102. Процессор 102 также может содержать ROM микрокода (ucode), в котором хранят микрокод для определенных макрокоманд. В одном варианте осуществления изобретения блок 108 исполнения может содержать логическую схему для обработки набора 109 команд для упакованных данных. Благодаря содержанию набора 109 команд для упакованных данных в наборе команд процессора 102 общего назначения, вместе с связанной схемой по исполнению команд, могут быть выполнены операции, используемые многими мультимедийными приложениями, с использованием упакованных данных в процессоре 102 общего назначения. Таким образом, многие мультимедийные приложения могут быть ускорены и исполнены более эффективно путем использования полной ширины шины данных процессора для выполнения операций с упакованными данными. Это может исключить потребность в переносе более мелких блоков данных по шине данных процессора с целью выполнения одной или нескольких операций с одним элементом данных за один раз.

Варианты осуществления блока 108 исполнения также могут быть использованы в микроконтроллерах, встроенных процессорах, графических устройствах, DSP и других типах логических схем. Система 100 может содержать память 120. Память 120 может быть реализована как динамическое оперативное запоминающее устройство (DRAM), статическое оперативное запоминающее устройство (SRAM), устройство флеш-памяти или другое устройство памяти. Память 120 может хранить команды и/или данные, представленные сигналами данных, которые могут быть исполнены процессором 102.

Микросхема 116 системной логики может быть связана с шиной 110 процессора и памятью 120. Микросхема 116 системной логики может содержать контроллер-концентратор (MCH) памяти. Процессор 102 может взаимодействовать с MCH 116 с помощью шины 110 процессора. MCH 116 может обеспечивать широкополосный путь 118 памяти к памяти 120 для хранения команд и данных и для хранения графических команд, данных и структур. MCH 116 может направлять сигналы данных между процессором 102, памятью 120 и другими компонентами в системе 100 и передавать сигналы данных между шиной 110 процессора, памятью 120 и вводом/выводом 122 системы. В некоторых вариантах осуществления изобретения микросхема 116 системной логики может предоставлять графический порт для связи с графическим контроллером 112. MCH 116 может быть соединен с памятью 120 с помощью интерфейса 118 памяти. Графическая карта 112 может быть связана с MCH 116 с помощью соединения 114 ускоренного графического порта (AGP).

Система 100 может использовать запатентованную шину 122 интерфейса концентратора для связи MCH 116 c контроллером-концентратором 130 (ICH) ввода-вывода. В одном варианте осуществления изобретения ICH 130 может обеспечивать прямые соединения с некоторыми устройствами ввода/вывода с помощью локальной шины ввода/вывода. Локальная шина ввода/вывода может содержать высокоскоростную шину ввода/вывода для соединения периферийных устройств с памятью 120, набором микросхем и процессором 102. Примерами могут являться контроллер звука, аппаратно реализованный программный концентратор 128 (флеш BIOS), устройство 126 беспроводной приемо-передачи, запоминающее устройство 124 для данных, существующий контроллер ввода/вывода, содержащий интерфейсы ввода данных пользователем и клавиатуры, последовательный порт расширения, такой как универсальная последовательная шина (USB) и сетевой контроллер 134. Запоминающее устройство 124 для данных может содержать накопитель на жестких дисках, накопитель на гибких дисках, устройство CD-ROM, устройство флеш-памяти или другое запоминающее устройство большой емкости.

В другом варианте осуществления системы, команда, соответствующая одному варианту осуществления изобретения, может быть использована с системой на микросхеме. Один вариант осуществления системы на микросхеме содержит процессор и память. Память для одной такой системы может содержать флеш-память. Флеш-память может быть расположена на том же кристалле, что и процессор и другие компоненты системы. Кроме того, в системе на микросхеме также могут быть расположены другие логические блоки, такие как контроллер памяти или графический контроллер.

На фиг. 1В показана система 140 обработки данных, в которой реализованы принципы вариантов осуществления настоящего изобретения. Специалисту в рассматриваемой области ясно, что описанные в настоящем документе варианты осуществления изобретения могут работать с альтернативными системами обработки, без выхода за границы объема патентования вариантов осуществления изобретения.

Компьютерная система 140 содержит обрабатывающее ядро 159 для выполнения, по меньшей мере, одной команды, в соответствии с одним вариантом осуществления изобретения. В одном варианте осуществления изобретения обрабатывающее ядро 159 представляет собой обрабатывающий блок с архитектурой любого типа, в том числе, помимо прочего, архитектурой типа CISC, RISC или VLIW. Обрабатывающее ядро 159 также может быть изготовлено с помощью одной или нескольких технологий обработки и может быть представлено на считываемом машиной носителе с достаточностью степенью детальности, может подходить для облегчения указанного изготовления.

Обрабатывающее ядро 159 содержит блок 142 исполнения, набор 145 файлов регистров и декодер 144. Обрабатывающее ядро 159 также может содержать дополнительную схему (не показана), которая может быть необязательной для понимания вариантов осуществления настоящего изобретения. Блок 142 исполнения может исполнять команды, принятые обрабатывающим ядром 159. Помимо выполнения типовых команд процессора, блок 142 исполнения может выполнять команды набора 143 команд для упакованных данных с целью выполнения операций над данными, представленными в форматах упакованных данных. Набор 143 команд для упакованных данных может содержать команды для выполнения вариантов осуществления изобретения и другие упакованные команды. Блок 142 исполнения может быть связан с файлом 145 регистров с помощью внутренней шины. Файл 145 регистров может представлять собой область хранения в обрабатывающем ядре 159 для хранения информации, в том числе данных. Как упомянуто выше, ясно, что область хранения может хранить упакованные данные, которые могут не быть критическими. Блок 142 исполнения может быть связан с декодером 144. Декодер 144 может декодировать команды, принятые обрабатывающим ядром 159, в сигналы управления и/или точки входа микрокода. В ответ на эти сигналы управления и/или точки входа микрокода, блок 142 исполнения выполняет соответствующие операции. В одном варианте осуществления изобретения декодер может интерпретировать код операции команды, который будет указывать, какую выполнять операцию с соответствующими данными, указанными в команде.

Обрабатывающее ядро 159 может быть связано с шиной 141 для обмена информацией с различными другими устройствами системы, которые могут содержать, помимо прочего, например, контроллер 146 синхронного динамического оперативного запоминающего устройства (SDRAM), контроллер 147 статичного оперативного запоминающего устройства (SRAM), интерфейс 148 пакетной флеш-памяти, контроллер 149 карты Международной ассоциации производителей карт памяти для персональных компьютеров (PCMCIA)/Сompact flash (CF), контроллер 150 жидкокристаллического дисплея (LCD), контроллер 151 прямого доступа (DMA) к памяти и интерфейс 152 альтернативного ведущего устройства шины. В одном варианте осуществления изобретения система 140 обработки данных также может содержать мост 154 ввода/вывода для связи с различными устройствами ввода/вывода с помощью шины 153 ввода/вывода. Такие устройства ввода/вывода могут содержать, помимо прочего, например, универсальное асинхронное устройство 155 (UART) приема/передачи, универсальную последовательную шину 156 (USB), UART 157 беспроводной технологии Bluetooth и интерфейс 158 расширения ввода/вывода.

Один вариант осуществления системы 140 обработки данных обеспечивает мобильную, сетевую и/или беспроводную связь и обрабатывающее ядро 159, которое может выполнять SIMD операции, в том числе операцию сравнения текстовых строк. Обрабатывающее ядро 159 может быть запрограммировано с помощью различных звуковых алгоритмов, видео алгоритмов, алгоритмов обработки изображений и алгоритмов связи, содержащих дискретные преобразования, такие как преобразование Уолша-Адамара, быстрое преобразование (FFT) Фурье, дискретное косинусное преобразование (DCT) и их соответствующие обратные преобразования; технологий сжатия/распаковки, такие как преобразование цветового пространства, оценка движения при кодировании видео или компенсация движения при декодировании видео; и функций (MODEM) модуляции/демодуляции, таких как импульсно-кодовая модуляция (PCT).

На фиг. 1С показаны другие варианты осуществления системы обработки данных, которая выполняет SIMD операции сравнения текстовых строк. В одном варианте осуществления изобретения система 160 обработки данных может содержать основной процессор 166, SIMD сопроцессор 161, кэш-память 167 и систему 168 ввода/вывода. Система 168 ввода/вывода может, при желании, быть связана с беспроводным интерфейсом 169. SIMD сопроцессор 161 может выполнять операции, содержащие команды, в соответствии с одним вариантом осуществления изобретения. В одном варианте осуществления изобретения обрабатывающее ядро 170 может быть изготовлено с помощью одной или нескольких технологий обработки и может быть представлено на считываемом машиной носителе с достаточностью степенью детальности, может подходить для облегчения изготовления всей или части системы 160 обработки данных, содержащей обрабатывающее ядро 170.

В одном варианте осуществления изобретения, SIMD сопроцессор 161 содержит блок 162 исполнения и набор файлов 164 регистров. Один вариант осуществления основного процессора 165 содержит декодер 165 для распознавания команд набора 163 команд, содержащего команды в соответствии с одним вариантом осуществления изобретения для исполнения блоком 162 исполнения. В других вариантах осуществления изобретения SIMD сопроцессор 161 также содержит, по меньшей мере, часть декодера 165 для декодирования команд набора 163 команд. Обрабатывающее ядро 170 также может содержать дополнительную схему (не показана), которая может быть необязательной для понимания вариантов осуществления настоящего изобретения.

При работе основной процессор 166 исполняет поток команд обработки данных, которые управляют операциями обработки данных общего типа, в том числе взаимодействиями с кэш-памятью 167 и системой 168 ввода/вывода. В поток команд обработки данных могут быть встроены команды SIMD сопроцессора. Декодер 165 основного процессора 166 распознает эти команды SIMD сопроцессора как команды такого типа, которые должны быть исполнены прикрепленным SIMD сопроцессором 161. Соответственно, основной процессор 166 направляет эти команды SIMD сопроцессора (или сигналы управления, представляющие команды SIMD сопроцессора) по шине 166 сопроцессора. Из шины 166 сопроцессора эти команды могут быть приняты любым прикрепленным SIMD сопроцессором. В этом случае SIMD сопроцессор 161 может принять и исполнить любую полученную и предназначенную для него команду SIMD сопроцессора.

Данные могут быть приняты с помощью беспроводного интерфейса 169 для обработки командами SIMD сопроцессора. В качестве одного примера, голосовая связь может быть принята в форме цифрового сигнала, который может быть обработан SIMD сопроцессором с помощью команд SIMD сопроцессора с целью восстановления образцов цифрового звука, представляющих голосовую связь. В качестве другого примера, сжатый звук и/или видео могут быть приняты в форме цифрового потока битов, который может быть обработан с помощью команд SIMD сопроцессора с целью восстановления образцов цифрового звука и/или видео кадров. В одном варианте осуществления обрабатывающего ядра 170 основной процессор 166 и SIMD сопроцессор 161 могут быть объединены в одно обрабатывающее ядро 170, содержащее блок 162 исполнения, набор файлов 164 регистров и декодер 165 для распознавания команд из набора 163 команд, содержащего команды в соответствии с одним вариантом осуществления изобретения.

На фиг. 2 показана структурная схема микроархитектуры процессора 200, который может содержать логические схемы для для исполнения команд, в соответствии с вариантами осуществления настоящего изобретения. В некоторых вариантах осуществления изобретения команда в соответствии с одним вариантом осуществления изобретения может быть реализована для работы с элементами данных, размер которых равен байту, слову, двойному слову, учетверенному слову и так далее, а также с такими типами данных, как целые одинарной и двойной точности и данные с плавающей запятой. В одном варианте осуществления изобретения входной блок 201 с исполнением команд по очереди может реализовывать часть процессора 200, которая может выбирать команды для исполнения и подготавливать команды для дальнейшего использования в конвейере процессора. Входной блок 201 может содержать несколько блоков. В одном варианте осуществления изобретения устройство 226 упреждающей выборки команд выбирает команды из памяти и подает команды на декодер 228 команд, который, в свою очередь, декодирует или интерпретирует команды. Например, в одном варианте осуществления изобретения декодер декодирует принятую команду в одну или несколько операций, называемых «микрокомандами» или «микрооперациями» (также называемые uop), которые может исполнять машина. В других вариантах осуществления изобретения декодер разбирает команду на код операции и соответствующие данные и поля управления, которые могут быть использованы микроархитектурой для выполнения операций в соответствии с одним вариантом осуществления изобретения. В одном варианте осуществления изобретения кэш-память 230 трассировки может собирать декодированные микрооперации в упорядоченные программой последовательности или трассы в очереди 234 микроопераций для исполнения. Когда кэш-память 230 трассировки сталкивается со сложной командой, ROM 232 микрокода предоставляет микрооперации, нужные для завершения операции.

Некоторые команды могут быть преобразованы в одну микрооперацию, тогда как другим нужно несколько микроопераций для завершения полной операции. В одном варианте осуществления изобретения, если нужно более четырех микроопераций для завершения команды, декодер 228 может обратиться к ROM 232 микрокода для выполнения команды. В одном варианте осуществления изобретения команда может быть декодирована в малое количество микроопераций для обработки в декодере 228 команд. В другом варианте осуществления изобретения команда может быть сохранена в ROM 232 микрокода, если для завершения операции нужно некоторое количество микроопераций. Кэш-память 230 трассировки обращается к точке входа программируемой логической матрицы (PLA) для определения корректного указателя микрокоманды с целью считывания из ROM 232 микрокода последовательности микрокода для завершения одной или нескольких команд в соответствии с одним вариантом осуществления изобретения. После того как ROM 232 микрокода завершает установку последовательности микроопераций для команды, входной блок 201 машины может возобновить выборку микроопераций из кэш-памяти 230 трассировки.

Механизм 203 исполнения с измененной очередью команд может подготовить команды для исполнения. Логическая схема исполнения с измененной очередью команд содержит некоторое количество буферов для сглаживания и переупорядочивания потока команд с целью оптимизации производительности, когда команды спускаются по конвейеру и при их планировании для исполнения. Логическая схема выделения выделяет буферы и ресурсы машины, которые нужны каждой микрооперации для исполнения. Логическая схема переименования регистров переименовывает логические регистры в записи в файле регистров. Устройство выделения также выделяет запись для каждой микрооперации в одной из двух очередях микроопераций, одна для операций с памятью и одна для операций без памяти, перед устройствами планирования команд: устройство планирования для памяти, быстрое устройство 202 планирования, медленное/общее устройство 204 планирования для плавающей запятой и простое устройство 206 планирования для плавающей запятой. Устройства 202, 204, 206 планирования для микроопераций определяют, когда микрооперация готова для исполнения на основе готовности зависимых входных операндов-источников и доступности ресурсов исполнения, которые нужны микрооперациям для завершения их операции. Быстрое устройство 202 планирования одного варианта осуществления изобретения может планировать в каждую половину основного такта цикла, а другие устройства планирования могут планировать только по тактам цикла основного процессора. Устройства планирования решают для портов отправления по планированию микроопераций для исполнения.

Файлы 208, 210 регистров могут быть расположены между устройствами 202, 204, 206 планирования и блоками 212, 214, 216, 218, 220, 222, 224 исполнения в узле 211 исполнения. Каждый из файлов 208, 210 регистров выполняет, соответственно, операции с целыми данными и с данными с плавающей запятой. Каждый из файлов 208, 210 регистров может содержать обходную сеть, по которой только завершенные результаты, которые еще не были записаны в файл регистров, могут обойти или быть направлены на новые зависимые микрооперации. Файл 208 регистров для целых данных и файл 210 регистров для данных с плавающей запятой могут обмениваться данными друг с другом. В одном варианте осуществления изобретения файл 208 регистров для целых данных может быть разделен на два отдельных файла регистров один файл регистров для младших тридцати двух битов данных, а второй файл регистров для старших тридцати двух битов данных. Файл 210 регистров для данных с плавающей запятой может содержать 128-битовые записи, так как команды с плавающей запятой обычно обладают операндами размером от 64 до 128 битов.

Узел 211 исполнения может содержать блоки 212, 214, 216, 218, 220, 222, 224 исполнения. Блоки 212, 214, 216, 218, 220, 222, 224 исполнения могут исполнять команды. Узел 211 исполнения может содержать файлы 208, 210 регистров, в которых хранятся значения операндов целых данных и данных с плавающей запятой, которые нужно исполнить микрокомандам. В одном варианте осуществления изобретения процессор 200 может содержать некоторое количество блоков исполнения: блок 212 (AGU) выработки адреса, AGU 214, быстрое ALU 216, быстрое ALU 218, медленное ALU 220, ALU 222 для данных с плавающей запятой, блок 224 перемещения для данных с плавающей запятой. В другом варианте осуществления изобретения блоки 222, 224 исполнения для данных с плавающей запятой В еще одном варианте осуществления изобретения ALU 222 для данных с плавающей запятой может содержать устройство деления 64-бита-на-64-бита для исполнения микроопераций деления, вычисления квадратного корня и остатка. В различных вариантах осуществления изобретения команды, подразумевающие значение с плавающей запятой, могут быть обработаны аппаратным обеспечением для данных с плавающей запятой. В одном варианте осуществления изобретения операции ALU могут быть переданы на высокоскоростные блоки 216, 218 исполнения ALU. Высокоскоростные ALU 216, 218 могут исполнять быстрые операции с эффективной задержкой в половину тактового цикла. В одном варианте осуществления изобретения наиболее сложные операции с целыми данными направляют в медленное ALU 220, так как медленное ALU 220 может содержать аппаратное обеспечение исполнения для целых данных для операций с длинной задержкой, таких как умножение, сдвиги, логические операции с флагами и обработка ветвлений. Операции загрузки/сохранения в памяти могут быть исполнены в AGU 212, 214. В одном варианте осуществления изобретения ALU 216, 218 для целых данных могут выполнять операции с целыми данными для 64-битовых операндов данных. В других вариантах осуществления изобретения ALU 216, 218, 220 могут быть реализованы для поддержки целого ряда битовых размеров данных, в том числе шестнадцати битовых, тридцати двух битовых, 128-битовых, 256-битовых и так далее. Аналогично, блоки 222, 224 для данных с плавающей запятой могут быть реализованы для поддержки ряда операндов с разными битовыми размерами. В одном варианте осуществления изобретения блоки 222, 224 для данных с плавающей запятой могут работать с 128-битовыми операндами упакованных данных в сочетании с SIMD и мультимедийными командами.

В одном варианте осуществления изобретения устройства 202, 204, 206 планирования микроопераций отправляют зависимые операции до завершения исполнения родительской загрузки. Так как микрооперации теоретически могут быть запланированы и исполнены в процессоре 200, то процессор 200 также может содержать логическую схему для обращения с промахами для памяти. Если загрузка данных не содержит данных в кэш-памяти, то могут присутствовать зависимые операции, обрабатываемые в конвейере, которые оставили устройство планирования с временно некорректными данными. Механизм повторного воспроизведения отслеживает и повторно исполняет команды, которые используют некорректные данные. Только для зависимых операций может понадобиться повторное воспроизведение, а независимым операциям могут позволить завершиться. Устройства планирования и механизм повторного воспроизведения одного варианта осуществления процессора также могут быть спроектированы для захвата последовательностей команд для операций сравнения текстовых строк.

Термином «регистры» могут называться встроенные в процессор ячейки хранения, которые могут быть использованы как часть команд для идентификации операндов. Другими словами, регистрами могут быть ячейки, которые можно использовать снаружи процессора (с точки зрения программиста). Тем не менее, в некоторых вариантах осуществления изобретения регистры могут быть не ограничены конкретным типом схемы. Предпочтительно, что регистр может сохранять данные, предоставлять данные и выполнять описанные в настоящем документе функции. Описанные в настоящем документе регистры могут быть реализованы схемой в процессоре, с использованием любого количества разных технологий, таких как специальные физические регистры, динамически выделяемые физические регистры с использованием переименования регистров, комбинации специальных и динамически выделяемых физических регистров и так далее. В одном варианте осуществления изобретения регистры целых данных хранят 32-битовые целые данные. Файл регистров одного варианта осуществления изобретения также содержит восемь мультимедийных SIMD регистров для упакованных данных. Для приведенного ниже описания, регистры можно понимать как регистры данных, спроектированные для содержания упакованных данных, такие как 64-битовые MMX™ регистры (также называемые в некоторых примерах «mm» регистрами) в микропроцессорах, поддерживающих технологию MMX компании Intel Corporation, Санта-Клара, Калифорния. Эти MMX регистры, доступные как в форме для целых данных, так и в форме для данных с плавающей запятой, могут работать с элементами упакованных данных, которые сопровождают SIMD и SSE команды. Аналогично, 128-битовые XMM регистр, относящиеся к технологии SSE2, SSE3, SSE4 и далее (в общем, называемые «SSEx»), могут содержать такие операнды с упакованными данными. В одном варианте осуществления изобретения, при сохранении упакованных данных и целых данных, регистрам не нужно различать эти два типа данных. В одном варианте осуществления изобретения целое значение и значение с плавающей запятой могут содержаться в одном файле регистров или в различных файлах регистров. Более того, в одном варианте осуществления изобретения данные с плавающей запятой и целые данные могут храниться в разных регистрах или в одинаковых регистрах.

В примерах, показанных на следующих фиг., может быть описано некоторое количество операндов данных. На фиг. 3А показаны различные представления типа данных «упакованные данные» в мультимедийных регистрах, в соответствии с вариантами осуществления настоящего изобретения. На фиг. 3А показаны типы данных для упакованного байта 310, упакованного слова 320 и упакованного двойного слова 330 для 128-битовых операндов. Формат 310 упакованного байта из этого примера может обладать длиной, равной 128 битам, и содержать шестнадцать байтовых элементов упакованных данных. Байт может быть определен, например, как восемь битов данных. Информация для каждого байтового элемента данных может быть сохранена в бите 7 - бите 0 для байта 0, в бите 15 - бите 8 для байта 1, в бите 23 - бите 16 для байта 2, … и, наконец, в бите 127 - бите 120 для байта 15. Таким образом, в регистре могут быть использованы все доступные биты. Эта компоновка хранения увеличивает эффективность хранения в процессоре. Также, с доступом к шестнадцати элементам данных, одна операция теперь может быть выполнена параллельно для шестнадцати элементов данных.

В общем, элемент данных может содержать отдельную часть данных, которая хранится в одном регистре или ячейке памяти с другими элементами данных той же длины. В последовательностях упакованных данных, относящихся к SSEx технологии, количество элементов данных, хранящихся в XMM регистре, может быть равно 128 битам, деленным на длину в битах отдельного элемента данных. Аналогично, в последовательностях упакованных данных, относящихся к MMX и SSE технологиям, количество элементов данных, хранящихся в MMX регистре, может быть равно 64 битам, деленным на длину в битах отдельного элемента данных. Хотя типы данных, показанные на фиг. 3А, могут обладать длиной 128 битов, варианты осуществления настоящего изобретения также могут работать с 64-битовыми операндами или операндами других размеров. Формат 320 упакованного слова из этого примера может обладать длиной, равной 128 битам, и содержать восемь элементов упакованных данных, размера равного слову. Каждое упакованное слово содержит шестнадцать битов информации. Формат 330 упакованного двойного слова из этого примера может обладать длиной, равной 128 битам, и содержать четыре элемента упакованных данных, размера равного двойному слову. Каждый элемент упакованных данных, размера равного двойному слову, содержит тридцать два бита информации. Упакованное четверное слово может обладать длиной, равной 128 битам, и содержать два элемента упакованных данных, размера равного четверному слову.

На фиг. 3В показаны возможные форматы хранения данных в регистре, в соответствии с вариантами осуществления настоящего изобретения. Каждые упакованные данные могут содержать более одного независимого элемента данных. Показано три формата упакованных данных; упакованные данные341 половинной точности, упакованные данные 342 одинарной точности, и упакованные данные 343 двойной точности. Один вариант осуществления упакованных данных 341 половинной точности, упакованных данных 342 одинарной точности и упакованных данных 343 двойной точности содержит элементы данных с фиксированной запятой. В другом варианте осуществления один или несколько из упакованных данных 341 половинной точности, упакованных данных 342 одинарной точности и упакованных данных 343 двойной точности могут содержать элементы данных с плавающей запятой. Один вариант осуществления упакованных данных 341 половинной точности может обладать длиной в 128 битов и содержать восемь 16-битовых элементов данных. Один вариант осуществления упакованных данных 342 одинарной точности может обладать длиной в 128 битов и содержать четыре 32-битовых элемента данных. Один вариант осуществления упакованных данных 343 двойной точности может обладать длиной в 128 битов и содержать два 64-битовых элемента данных. Ясно, что такие форматы данных могут быть дополнительно расширены на другие длины регистров, например, до 96 битов, 160 битов, 192 битов, 224 битов, 256 битов и более.

На фиг. 3С показаны различные представления типа данных «упакованные данные» со знаком и без знака в мультимедийных регистрах, в соответствии с вариантами осуществления настоящего изобретения. Упакованное байтовое представление 344 без знака показывает хранение упакованного байта без знака в SIMD регистре. Информация для каждого байтового элемента данных может быть сохранена в бите 7 - бите 0 для байта 0, в бите 15 - бите 8 для байта 1, в бите 23 - бите 16 для байта 2, … и, наконец, в бите 127 - бите 120 для байта 15. Таким образом, в регистре могут быть использованы все доступные биты. Эта компоновка хранения может увеличить эффективность хранения в процессоре. Также, с доступом к шестнадцати элементам данных, одна операция теперь может быть выполнена параллельным образом для шестнадцати элементов данных. Упакованное байтовое представление 345 со знаком показывает хранение упакованного байта со знаком. Заметим, что каждый восьмой бит каждого байтового элемента данных может быть указателем знака.

Упакованное представление 346 слов без знака показывает, как можно хранить слово семь - слово ноль в SIMD регистре. Упакованное представление 347 слов со знаком может быть аналогично упакованному представлению 346 слов без знака в регистре. Заметим, что каждый шестнадцатый бит каждого элемента данных слова может быть указателем знака. Упакованное представление 348 двойных слов без знака показывают, как хранят элементы данных из двойных слов. Упакованное представление 349 двойных слов со знаком может быть аналогично упакованному представлению 348 двойных слов без знака в регистре. Заметим, что обязательный бит знака может быть тридцать вторым битом каждого элемента данных из двойного слова.

На фиг. 3D показан один вариант осуществления кодирования операции (код операции). Более того, формат 360 может содержать операнд регистра/памяти, отсылающий к режимам, соответствующим типу формата кода операции, описанного в «Руководство для разработчиков программного обеспечения по IA-32 архитектуре Intel, том 2: Справка по набору команд», компания Intel Corporation, Санта-Клара, Калифорния, указанное руководство доступно на сайте intel.com/design/litcentr (www). В одном варианте осуществления изобретения любая команда может быть закодирована одним или несколькими полями из полей 361 и 362. Может быть идентифицировано до двух мест операндов на команду, в том числе до двух идентификаторов 364 и 365 операндов-источников. В одном варианте осуществления изобретения идентификатор 366 операнда-назначения может быть тем же, что и идентификатор 364 операнда-источника, при это в других вариантах осуществления изобретения они могут быть разными. В другом варианте осуществления изобретения идентификатор 366 операнда-назначения может быть тем же, что и идентификатор 365 операнда-источника, при это в других вариантах осуществления изобретения они могут быть разными. В одном варианте осуществления изобретения один из операндов-источников, идентифицированный идентификатором 364 и 365 операнда-источника, может быть переписан результатами операций сравнения текстовых строк, при этом в других вариантах осуществления изобретения идентификатор 364 соответствует элементу регистра источника, а идентификатор 365 соответствует элементу регистра назначения. В одном варианте осуществления изобретения идентификаторы 364 и 365 операнда могут идентифицировать 32-битовые или 64-битовые операнды-источники и операнды-назначения.

На фиг. 3E показан другой возможный формат 370 кодирования (код операции) операций, содержащий сорок или более битов, в соответствии с вариантами осуществления настоящего изобретения. Формат 370 кода операции соответствует формату 360 кода операции и содержит необязательный байт 378 префикса. Команда, соответствующая одному варианту осуществления изобретения, может быть закодирована одним или несколькими полями 378, 371 и 372. Идентификаторами 374 и 375 операндов-источников и байтом 378 префикса может быть идентифицировано до двух мест операндов на команду. В одном варианте осуществления изобретения байт 378 префикса может быть использован для идентификации 32-битовых или 64-битовых операндов-источников и операндов-назначений. В одном варианте осуществления изобретения идентификатор 376 операнда-назначения может быть тем же, что и идентификатор 374 операнда-источника, при это в других вариантах осуществления изобретения они могут быть разными. В другом варианте осуществления изобретения идентификатор 376 операнда-назначения может быть тем же, что и идентификатор 375 операнда-источника, при это в других вариантах осуществления изобретения они могут быть разными. В одном варианте осуществления изобретения команда работает с одним или несколькими операндами, идентифицированными идентификаторами 374 и 375 операндов, и один или несколько операндов, идентифицированных идентификаторами 374 и 375 операндов, могут быть переписаны результатами команды, при этом в других вариантах осуществления изобретения операнды, идентифицированные идентификаторами 374 и 375 операндов, могут быть записаны в другой элемент данных в другом регистре. Форматы 360 и 370 кода операции позволяют осуществлять адресацию регистр в регистр, память в регистр, регистр в память, регистр с помощью регистра, регистр с помощью непосредственного значения, регистр в память, которая определена в части полей 363 и 373 MOD и необязательными байтами масштабирование-индекс-основание и смещение.

На фиг. 3F показан еще один возможный формат кодирования (код операции) операций, в соответствии с вариантами осуществления настоящего изобретения. 64-битовые арифметические операции (SIMD) с одним потоком команд и несколькими потоками данных могут быть выполнены с помощью команды обработки (CDP) данных сопроцессором. Формат 380 кодирования операции (код операции) показывает одну такую CDP команду с полями 382 и 389 кода CDP операции. Тип CDP команды, для другого варианта осуществления изобретения, может быть закодирован с помощью одного или нескольких полей 383, 384, 387 и 388. Может быть идентифицировано до трех мест операндов на команду, в том числе до двух идентификаторов 385 и 390 операндов-источников и одного идентификатора 386 операнда-назначения. Один вариант осуществления сопроцессора может работать с восьми-битовыми, шестнадцати-битовыми, тридцати двух-битовыми и 64-битовыми значениями. В одном варианте осуществления изобретения команда может быть выполнена над целыми элементами данных. В некоторых вариантах осуществления изобретения команда может быть выполнена с условием, с использованием поля 381 условия. Для некоторых вариантов осуществления изобретения размеры исходных данных могут быть закодированы в поле 383. В некоторых вариантах осуществления изобретения, в SIMD полях может быть сделано определение нуля (Z), отрицательного (N), перемещения (C) и переполнения (V). Для некоторых команд, тип насыщения может быть закодирован в поле 384.

На фиг. 4A показана структурная схема, иллюстрирующая конвейер с исполнением команд по очереди и конвейер с измененным порядком исполнения/выдачи команд, со ступенью переименования регистров, в соответствии с вариантами осуществления изобретения. На фиг. 4В показана структурная схема, иллюстрирующая архитектуру ядра с исполнением команд по очереди и подлежащую вхождению в процессор логическую схему с измененным порядком исполнения/выдачи команд, логическую схему переименования регистров, в соответствии с вариантами осуществления изобретения. Прямоугольники, изображенные сплошными линиями на фиг. 4A, показывают конвейер с исполнением команд по очереди, а прямоугольники, изображенные пунктирными линиями, показывают конвейер с измененным порядком исполнения/выдачи команд и переименованием регистров. Аналогично, прямоугольники, изображенные сплошными линиями на фиг. 4В, показывают логическую схему архитектуры с исполнением команд по очереди, а прямоугольники, изображенные пунктирными линиями, показывает логическую схему переименования регистров и логическую схему с измененным порядком исполнения/выдачи команд.

На фиг. 4A конвейер 400 процессора может содержать ступень 402 выборки, ступень 404 декодирования длины, ступень 406 декодирования, ступень 408 выделения, ступень 410 переименования, ступень 412 планирования (также известна как отправление или выдача), ступень 414 чтения регистра/памяти, ступень 416 исполнения, ступень 418 повторной записи/записи в память, ступень 422 обработки исключений и ступень 424 фиксации.

На фиг. 4В стрелки показывают связи между двумя или несколькими блоками, а направление стрелок указывает направление потока данных между этими блоками. На фиг. 4B показано ядро 490 процессора, содержащее входной блок 430, связанный с блоком 450 механизма исполнения, при этом входной блок 1730 и блок 1750 механизма исполнения могут быть связаны с блоком 470 памяти.

Ядро 490 может быть вычислительным ядром (RISC) с сокращенным набором команд, вычислительным ядром (СISC) со сложным набором команд, ядром (VLIW) с очень длинным командным словом или ядром гибридного или альтернативного типа. В качестве еще одного варианта, ядро 490 может быть ядром специального назначения, таким как, например, сетевое ядро или ядро связи, ядро устройства сжатия, графическое ядро или подобное.

Входной блок 430 может содержать блок 432 предсказания ветвления, связанный с блоком 434 кэш-памяти команд. Блок 434 кэш-памяти команд может быть связан с буфером 436 ассоциативной трансляции (TLB) команд. TLB 436 может быть связан с блоком 438 выборки команд, который связан с блоком 440 декодирования. Блок 440 декодирования может декодировать команды и вырабатывать в качестве выхода одну или несколько микроопераций, точек входа микрокода, микрокоманд, других команд или других сигналов управления, которые могут быть декодированы, или другим образом могут отражать или могут быть получены из исходных команд. Декодер может быть реализован с использованием различных механизмов. Примерами подходящих механизмов являются, помимо прочего, таблицы соответствия, аппаратные реализации, программируемые логические матрицы (PLA), постоянные запоминающие устройства (ROM) с микрокодом и так далее. В одном варианте осуществления изобретения блок 434 кэш-памяти команд может быть дополнительно связан с блоком 476 кэш-памяти уровня 2 (L2) в блоке 470 памяти. Блок 440 декодирования может быть связан с блоком 452 переименования/выделения из блока 450 механизма исполнения.

Блок 450 механизма исполнения может содержать блок 452 переименования/выделения, связанный с блоком 454 выгрузки и набором из одного или нескольких блоков 456 планирования. Блоки 456 планирования представляют собой любое количество разных устройств планирования, в том числе резервирующие станции, центральное окно команд и так далее. Блоки 456 планирования могут быть связаны с блоками 458 файлов физических регистров. Каждый из блоков 458 файлов физических регистров представляет один или несколько файлов физических регистров, при этом различные файлы хранят данные одного или нескольких типов данных, таких как скалярные целые, скалярные с плавающей запятой, упакованные целые, упакованные с плавающей запятой, векторные целые, векторные с плавающей запятой и так далее, состояния (например, указатель команды, который является адресом следующей команды, подлежащей исполнению) и так далее. Блоки 458 файлов физических регистров могут быть перекрыты блоком 154 выгрузки для показа различных путей, которыми могут быть реализованы переименование регистров и измененный порядок исполнения команд (например, с использованием одного или нескольких буферов переупорядочивания и одного или нескольких файлов выгрузки регистров; с использованием одного или нескольких файлов будущего, одного или нескольких буферов истории и одного или нескольких файлов регистров выгрузки; с использованием карт регистров и пула регистров; и так далее.). В общем, архитектурные регистры могут быть видимы снаружи процессора или видимы с точки зрения программиста. Регистры могут быть не ограничены любым известным конкретным типом схемы. Различные типы регистров могут подходить, при условии, что они сохраняют и предоставляют данные, как описано в настоящем документе. Примеры подходящих регистров содержат, помимо прочего, специальные физические регистры, динамически выделяемые физические регистры с использованием переименования регистров и комбинации специальных и динамически выделяемых физических регистров и так далее. Блок 454 выгрузки и блоки 458 файлов физических регистров могут быть связаны с кластерами 460 исполнения. Кластеры 460 исполнения могут содержать набор из одного или нескольких блоков 462 исполнения и набор из одного или нескольких блоков 464 доступа к памяти. Блоки 462 исполнения могут осуществлять различные операции (например, сдвиги, сложение, вычитание, умножение) для различных типов данных (например, скалярных с плавающей запятой, упакованных целых, упакованных с плавающей запятой, векторных целых, векторных с плавающей запятой). Хотя некоторые варианты осуществления изобретения могут содержать некоторое количество блоков исполнения, выделенных для конкретных функций или наборов функций, другие варианты осуществления изобретения могут содержать только один блок исполнения или множество блоков исполнения, которые все выполняют все функции. Блоки 456 планирования, блоки 458 файла физических регистров и кластеры 460 исполнения показаны с возможностью наличия нескольких блоков, так как определенные варианты осуществления изобретения создают отдельные конвейеры для определенных типов данных/операций (например, конвейер скалярных целых, конвейер скалярных с плавающей запятой/упакованных целых/упакованных с плавающей запятой/векторных целых/векторных с плавающей запятой и/или конвейер доступа к памяти, каждый из которых обладает собственных блоком планирования, блоком файла физических регистров и/или кластером исполнения - и в случае отдельного конвейера доступа к памяти, могут быть реализованы определенные варианты осуществления изобретения, в которых только кластер исполнения этого конвейера содержит блоки 464 доступа к памяти). Также следует понимать, что, когда используют отдельные конвейеры, один или несколько этих конвейеров могут быть с измененным порядком исполнения/выдачи команд, а другие - с исполнением команд по очереди.

Набор блоков 464 доступа к памяти может быть связан с блоком 470 памяти, который может содержать блок 472 TLB данных, связанный с блоком 474 кэш-памяти данных, связанным с блоком 476 кэш-памяти уровня 2 (L2). В одном примере варианта осуществления изобретения блоки 464 доступа к памяти могут содержать блок загрузки, блок адреса хранения и блок хранения данных, каждый из которых может быть связан с блоком 472 TLB данных в блоке 470 памяти. Блок 476 кэш-памяти L2 может быть связан с одним или несколькими другими уровнями кэш-памяти и, в конечном счете, с основной памятью.

В качестве примера, архитектура ядра с измененным порядком исполнения/выдачи команд, с переименованием регистров, может реализовывать конвейер 400 следующим образом: 1) блок 438 выборки команд может выполнять ступени 402 и 404 выборки и декодирования длины; 2) блок 440 декодирования может выполнять ступень 406 декодирования; 3) блок 452 переименования/выделения может выполнять ступень 408 выделения и ступень 410 переименования; 4) блоки 456 планирования может выполнять ступень 412 планирования; 5) блоки 458 файлов физических регистров и блок 470 памяти могут выполнять ступень 414 считывания регистра/памяти; кластер 460 исполнения может выполнять ступень 416 исполнения; 6) блок 470 памяти и блоки 458 файлов физических регистров могут выполнять ступень 418 обратной записи/записи в память; 7) различные блоки могут участвовать в осуществлении ступени 422 обработки исключений; и 8) блок 454 выгрузки и блоки 458 файлов физических регистров могут выполнять ступень 424 фиксации.

Ядро 490 может поддерживать один или несколько наборов команд (например, набор х86 команд (с некоторыми расширениями, добавленными в более новых версиях); набор команд MIPS компании IPS Technologies, город Саннивейл (Sunnyvale), Калифорния; набор команд ARM (с необязательными дополнительными расширениями, такими как NEON) компании ARM Holdings, Саннивейл, Калифорния).

Ясно, что ядро может поддерживать многопоточность (исполнение двух или нескольких параллельных наборов операций или цепочек) разными способами. Поддержка многопоточности может быть выполнена, например, благодаря наличию многопоточности с квантованием времени, одновременной многопоточности (когда единственное физическое ядро предоставляет для каждой цепочки логическое ядро, которые физическое ядро выполняет одновременно) или их комбинаций. Такая комбинация может содержать, например, выборку с квантованием времени и декодирование и дальнейшую одновременную многопоточность, например, как в технологии Intel® Hyperthreading.

Хотя переименование регистров может быть описано в случае изменения порядка исполнения команд, следует понимать, что переименование регистров может быть использовано в архитектуре с исполнением команд по очереди. Хотя показанный вариант осуществления процессора также может содержать отдельные блоки 434/474 кэш-памяти команд и данных и совместно используемый блок 476 кэш-памяти L2, другие варианты осуществления изобретения могут содержать единственную внутреннюю кэш-память как для команд, так и для данных, такую как, например, внутренняя кэш-память уровня 1 (L1), или несколько уровней внутренней кэш-памяти. В некоторых вариантах осуществления изобретения система может содержать комбинацию внутренней кэш-памяти и внешней кэш-памяти, которая может являться внешней по отношению к ядру и/или процессору. В других вариантах осуществления изобретения, все кэш-памяти могут быть внешними для ядра и/или процессора.

На фиг. 5А показана структурная схема процессора 500, в соответствии с вариантами осуществления настоящего изобретения. В одном варианте осуществления изобретения процессор 500 может содержать многоядерный процессор. Процессор 500 может содержать системный агент 510, с возможностью обмена информацией, связанный с одним или несколькими ядрами 502. Более того, ядра 502 и системный агент 510 могут быть, с возможностью обмена информацией, связаны с одной или несколькими кэш-памятями 506. Ядра 502, системный агент 510 и кэш-памяти 506 могут быть связаны, с возможностью обмена информацией, с помощью одного или нескольких блоков 552 управления памятью. Более того, ядра 502, системный агент 510 и кэш-памяти 506 могут быть, с возможностью обмена информацией, связаны с графическим модулем 560 с помощью блоков 552 управления памятью.

Процессор 500 может содержать любой подходящий механизм для соединения ядер 502, системного агента 510 и кэш-памятей 506 и графического модуля 560. В одном варианте осуществления изобретения процессор 500 может содержать кольцеобразный блок 508 соединения, выполненный для соединения ядер 502, системного агента 510 и кэш-памятей 506 и графического модуля 560. В других вариантах осуществления изобретения процессор 500 может содержать любое количество хорошо известных технологий для соединения таких блоков. Кольцеобразный блок 508 соединения может использовать блоки 552 управления памятью для облегчения соединения.

Процессор 500 может содержать иерархию памяти, включающую в себя один или несколько уровней кэш-памяти в ядрах, один или несколько совместно используемых блоков кэш-памяти, таких как кэш-памяти 506, или внешнюю память (не показана), связанную с набором блоков 552 контроллеров интегрированной памяти. Кэш-памяти 506 могут содержать любую подходящую кэш-память. В одном варианте осуществления изобретения кэш-памяти 506 могут содержать одну или несколько кэш-памятей среднего уровня, такого как уровень 2 (L2), уровень 3 (L3), уровень 4 (L4), или другие уровни кэш-памяти, кэш-память (LLC) последнего уровня и/или их комбинации.

В различных вариантах осуществления изобретения одно или несколько ядер 502 способны поддерживать многопоточность. Системный агент 510 может содержать компоненты для координации и управления ядрами 502. Блок 510 системного агента может содержать, например, блок (PCU) управления питанием. PCU может являться или содержать логическую схему или компоненты, нужные для регулирования состояния электропитания ядер 502. Системный агент 510 может содержать механизм 512 отображения для приведения в действие одного или нескольких внешне подключенных дисплеев или графических модулей 560. Системный агент 510 содержать интерфейс 514 для шин связи для графики. В одном варианте осуществления изобретения интерфейс 514 может быть реализован с помощью PCI Express (PCIe). В другом варианте осуществления изобретения интерфейс 514 может быть реализован с помощью PCI Express Graphics (PEG). Системный агент 510 может содержать прямой мультимедийный интерфейс 516 (DMI). DMI 516 может обеспечивать каналы между различными мостами на материнской плате или другого участка компьютерной системы. Системный агент 510 может содержать PCIe мост 518 для обеспечения PCIe каналов к другим элементам вычислительной системы. PCIe мост 518 может быть реализован с использованием контроллера 520 памяти и логической схемы 522 когерентности.

Ядра 502 могут быть реализованы любым подходящим образом. Ядра 502 могут быть однородными или разнородными с точки зрения архитектуры и/или набора команд. В одном варианте осуществления изобретения некоторые ядра 502 могут быть ядрами с исполнением команд по очереди, а другие ядра могут быть ядрами с измененным порядком исполнения команд. В другом варианте осуществления изобретения два или несколько ядер 502 могут исполнять один и тот же набор команд, а другие могут исполнять только подмножество этого набора команд или другого набора команд.

Процессор 500 может содержать процессор общего назначения, такой как процессор Core™ i3, i5, i7, 2 Duo и Quad, Xeon™, Itanium™, XScale™ или StrongARM™, компания Intel Corporation, Санта-Клара, Калифорния. Процессор 500 может быть поставлен другой компанией, такой как ARM Holdings Ltd, MIPS, и так далее. Процессор 500 может быть процессором специального назначения, таким как, например, сетевой процессор или процессор связи, устройством сжатия, графический процессор, сопроцессор, встроенный процессор или подобный. Процессор 500 может быть реализован на одной или нескольких микросхемах. Процессор 500 может быть частью и/или может быть реализован на одной или нескольких подложках с использованием некоторого количества технологий обработки, таких как, например, BiCMOS, CMOS или NMOS.

В одном варианте осуществления изобретения одна заданная кэш-память 506 может быть совместно используемой многими ядрами из ядер 502. В другом варианте осуществления изобретения одна заданная кэш-память 506 может быть выделена для одного из ядер 502. Назначение кэш-памятей 506 ядрам 502 может быть выполнено контроллером кэш-памятей или другим подходящим механизмом. Одна заданная кэш-память 506 может быть использована совместно двумя или несколькими ядрами 502 путем реализации квантования времени для заданной кэш-памяти 506.

Графический модуль 560 может реализовывать подсистему обработки интегрированной графики. В одном варианте осуществления изобретения графический модуль 560 может содержать графический процессор. Более того, графический модуль 560 может содержать мультимедийный механизм 565. Мультимедийный механизм 565 может обеспечить мультимедийное кодирование и декодирование видео.

На фиг. 5В показана структурная схема одного примера реализации ядра 502, в соответствии с вариантами осуществления настоящего изобретения. Ядро 502 может содержать входной блок 570, с возможностью обмена информацией, связанный с механизмом 580 исполнения с измененным порядком команд. Ядро 502 может быть, с возможностью обмена информацией, связанным с другими участками процессора 500 с помощью иерархии 503 кэш-памяти.

Входной блок 570 может быть реализован любым подходящим способом, таким как полностью или частично с помощью входного блока 201, описанного выше. В одном варианте осуществления изобретения входной блок 570 может обмениваться информацией с другими участками процессора 500 с помощью иерархии 503 кэш-памяти. В еще одном варианте осуществления изобретения входной блок 570 может осуществлять выборку команд из участков процессора 500 и подготавливать команды для дальнейшего использования в конвейере процессора, при их прохождении к механизму 580 исполнения с измененным порядком команд.