Изобретение относится к области силовой электроники, в частности, к устройствам сопряжения между цифровыми устройствами и силовыми МОП или IGBT (БТИЗ-биполярными транзисторами с изолированными затворами) транзисторами.

Драйвер предназначен для управления силовыми транзисторами в электронной аппаратуре с высокими уровнями электромагнитных помех или высокими требованиями к надежности работы, а также при значительной длине линий связи, по которым на драйвер поступают сигналы управления.

Известен драйвер для IGBT - транзистора [патент РФ №94084, МПК Н02М 1/00, Н02М 3/155, опубл. 10.05.2010], содержащий блок гальванической развязки, блок формирования сигналов, блок сопряжения (промежуточного усиления) сигналов, а также, блок усиления мощности (выходной формирователь токов затвора).

Известное устройство - драйвер IGBT - транзистора, дополнительно, включает в состав блок контроля силового напряжения. Управление известным устройством осуществляется с помощью одного управляющего сигнала, поступающего от внешнего цифрового устройства.

Известный драйвер не обладает достаточной помехоустойчивостью, так как не обеспечивает эффективную защиту от наведенного паразитного сигнала на линию связи, по которой приходит управляющий сигнал, вызванного воздействием электромагнитных помех, и имеет более узкую область применения.

Известен драйвер IGBT [патент РФ №107419, МПК Н02М 1/08, опубл. 10.08.2011], который выбран в качестве прототипа. Драйвер содержит гальванически развязанную цепь управления, промежуточный усилитель и выходной формирователь токов затвора.

Известное устройство - драйвер IGBT обеспечивает гальваническую развязку источника управляющего сигнала - цифрового устройства от цепей силовой электроники, прием, усиление управляющего сигнала, формирование выходного сигнала на включение и выключение силового транзистора IGBT, однако оно не обладает достаточной помехоустойчивостью и надежностью, так как не обеспечивает эффективную защиту от наведенного паразитного сигнала на линию связи, по которой приходит управляющий сигнал, вызванного воздействием электромагнитных помех, и имеет более узкую область применения.

Применение известного устройства ограничено его недостаточной помехоустойчивостью и приводит к необходимости минимизации допустимой длины линии связи между ним и цифровым устройством, формирующим сигналы управления (к необходимости размещения в непосредственной близости известного устройства - драйвера IGBT от цифрового устройства управления), а также ограничено более высокими требованиями к защите линии связи от воздействия электромагнитных помех, чем существенно сужается область применения драйвера IGBT.

При увеличении длины линии связи сверх критической, для данного технического решения, или недостаточных мерах, принятых по защите линии связи от воздействия электромагнитных помех, возможно формирование кратковременных ложных выходных сигналов, вызванных, наведенными электромагнитными помехами в линии связи, паразитными электрическими сигналами, что снижает надежность и безопасность применения известного устройства в приборах силовой электроники.

Указанные условия практически исключают применение известного устройства в электронной аппаратуре с высокими требованиями к помехоустойчивости, безопасности и надежности функционирования, в частности, к обеспечению невыдачи ложного выходного сигнала, при отсутствии управляющего входного сигнала, на открывание силового транзистора в условиях воздействия интенсивных электромагнитных помех.

Технической задачей заявляемого изобретения является создание драйвера управления силовыми транзисторами с высокой помехоустойчивостью, безопасностью применения и повышенной надежностью.

Техническим результатом, получаемым при использовании заявляемого изобретения, является высокая помехоустойчивость, безопасность и надежность, при расширении области применения, получаемые при осуществлении управления его работой с помощью двух независимых парафазных сигналов, поступающих по отдельным линиям связи и выработки выходного сигнала на включение и выключение внешнего силового транзистора на основе логического анализа состояния управляющих сигналов, имеющих разный уровень приоритета.

Указанный технический результат достигается тем, что драйвер управления силовыми транзисторами с повышенной помехоустойчивостью, содержащий гальванически развязанную цепь управления, промежуточные усилители и выходной формирователь токов затвора, согласно изобретению, он включает две линии связи управления с отдельными каналами приема сигналов на включение и выключение внешнего силового транзистора, первый и второй канал, соответственно, дополнительно он содержит первый и второй симметричные фильтры нижних частот, устройство блокировки верхнего плеча выходного формирователя токов затвора, формирователь постоянного падения напряжения и балластный резистор, а гальванически развязанная цепь управления состоит из первого и второго входных устройств, промежуточный усилитель состоит из первого и второго усилителей, выходной формирователь токов затвора состоит из двух транзисторов, n-p-n типа верхнего плеча и n-p-n типа нижнего плеча, соответственно, при этом, входы первого и второго фильтров нижних частот служат для электрического подключения внешних управляющих сигналов, на включение и выключение внешнего силового транзистора, соответственно, выходы первого и второго фильтров нижних частот электрически подключены к входам первого и второго входных устройств, соответственно, выход первого входного устройства электрически подключен к входу первого усилителя, выход второго входного устройства электрически подключен к входам второго усилителя и устройства блокировки верхнего плеча, выход первого усилителя электрически соединен с базой транзистора верхнего плеча и вторым выходом устройства блокировки верхнего плеча, выход второго усилителя электрически соединен с базой транзистора нижнего плеча, коллекторы транзисторов верхнего и нижнего плеча электрически соединены между собой и подключены к первому выводу балластного резистора, а также к выходу управления внешним силовым транзистором, эмиттер транзистора верхнего плеча электрически подключен ко второму выводу формирователя постоянного падения напряжения, первый вывод формирователя постоянного падения напряжения подключен к шине положительного напряжения питания постоянного тока и первому выходу устройства блокировки верхнего плеча, эмиттер транзистора нижнего плеча электрически подключен ко второму выводу балластного резистора и к шине отрицательного напряжения питания постоянного тока, таким образом, первый канал приема сигнала на включение внешнего силового транзистора образован из последовательно включенных первого фильтра нижних частот, первого входного устройства, первого промежуточного усилителя, устройства блокировки верхнего плеча, формирователя постоянного падения напряжения и транзистора верхнего плеча, а второй канал приема сигнала на выключение внешнего силового транзистора состоит из второго фильтра нижних частот, второго входного устройства, второго промежуточного усилителя и транзистора нижнего плеча.

Наличие в драйвере устройства блокировки верхнего плеча, управляемого сигналом с выхода второго входного устройства и формирователя постоянного падения напряжения обеспечивает, при поступлении входного сигнала на выключение внешнего силового транзистора во второй канал приема, задействование устройства блокировки верхнего плеча, что приводит к прикладыванию к переходу эмиттер-база транзистора верхнего плеча отрицательного напряжения и вызванное им принудительное закрывание транзистора верхнего плеча, даже при одновременном поступлении входного сигнала на включение внешнего силового транзистора в первый канал приема.

Таким образом, в процессе функционирования устройства, появление вызванного воздействием электромагнитных помех, случайного сигнала в цепях линий связи, направленного на включение внешнего силового транзистора и приводящего к кратковременному формированию сигнала на включение внешнего силового транзистора в первом канале приема, не приводит к открыванию внешнего силового транзистора, так как любое прохождение сигнала в первом канале приема блокируется штатным сигналом на закрывание внешнего силового транзистора во втором канале приема. При этом, аналогичный случайный сигнал в цепях линий связи, вызванный воздействием электромагнитных помех, противоположный по полярности присутствующему на линии связи штатному сигналу на выключение внешнего силового транзистора, обладающий достаточной интенсивностью, чтобы, накладываясь на штатный сигнал, приводить к его кратковременному пропаданию во втором канале приема, также, не приведет к открыванию внешнего силового транзистора, так как его закрытое состояние в таком режиме поддерживается с помощью балластного резистора, подключенного между затвором внешнего силового транзистора и отрицательной шиной питания постоянного тока.

При обрыве линий связи, между драйвером и цифровым устройством, закрытое состояние внешнего силового транзистора, также, обеспечивается с помощью балластного резистора.

Гипотетически, ложное включение внешнего силового транзистора под воздействием электромагнитных помех в цепях линий связи может быть реализовано в устройстве только при одновременном поступлении двух случайных входных сигналов различной полярности и высокой интенсивности: первого сигнала на включение внешнего силового транзистора в первом канале приема; второго сигнала, противоположного по полярности, как первому случайному сигналу, так и штатному сигналу, на выключение внешнего силового транзистора и вызывающего снятие штатного сигнала во втором канале приема. Высокая помехоустойчивость к воздействию данной комбинации случайных сигналов обеспечивается двумя симметричными фильтрами низких частот, не пропускающими на вход устройства случайные сигналы малой длительности, а также, конструктивным выполнением линий связи источника управляющих сигналов (цифрового устройства) и драйвера с помощью единого кабеля, в составе которого линии связи на включение и выключение, соответственно, выполнены отдельными близко расположенными витыми парами проводов, что минимизирует возможность одновременного формирования на обоих линиях связи разнополярных сигналов, вызванных электромагнитными помехами.

Следовательно, воздействие электромагнитных помех на линии связи драйвера или обрыв линий связи не приводит к его ложному срабатыванию и, соответственно, ложному включению внешнего силового транзистора, что обеспечивает повышенную помехоустойчивость и надежность функционирования данного устройства в условиях повышенной протяженности линий связи, между цифровым устройством и устройством силовой электроники, в состав которого входит внешний силовой транзистор, а также высокой интенсивности электромагнитных помех.

В заявляемом техническом решении, относительно прототипа, улучшены такие основные технические характеристики как помехоустойчивость к воздействию электромагнитных помех на линии связи с цифровым устройством - источником управляющих сигналов и надежность функционирования, в том числе при повышенной длине линий связи. Кроме того, повышена безопасность применения по такому критерию, как невыдача ложного выходного сигнала на включение внешнего силового транзистора, при воздействии электромагнитных помех высокой интенсивности на линии связи или при обрыве линий связи. Совокупность дополнительных качественных характеристик допускает его применение в аппаратуре с повышенными требованиями к длине линий связи и воздействию электромагнитных помех, в том числе, с критическими требованиями по невыдаче ложных выходных сигналов в процессе эксплуатации, например - в цепях задействования пиротехнических и взрывных устройств, что расширяет область его применения.

Таким образом, совокупность всех изложенных выше признаков создает условия обеспечения высокой помехостойкости, надежности и безопасности драйвера, а также расширения области его применения.

Наличие в заявляемом изобретении признаков, отличающих его от прототипа, позволяет считать его соответствующим условию «новизна».

Новые признаки, которые содержит отличительная часть формулы изобретения, не выявлены в технических решениях аналогичного назначения и в других областях техники. На этом основании можно сделать вывод о соответствии заявляемого изобретения условию патентоспособности «изобретательский уровень».

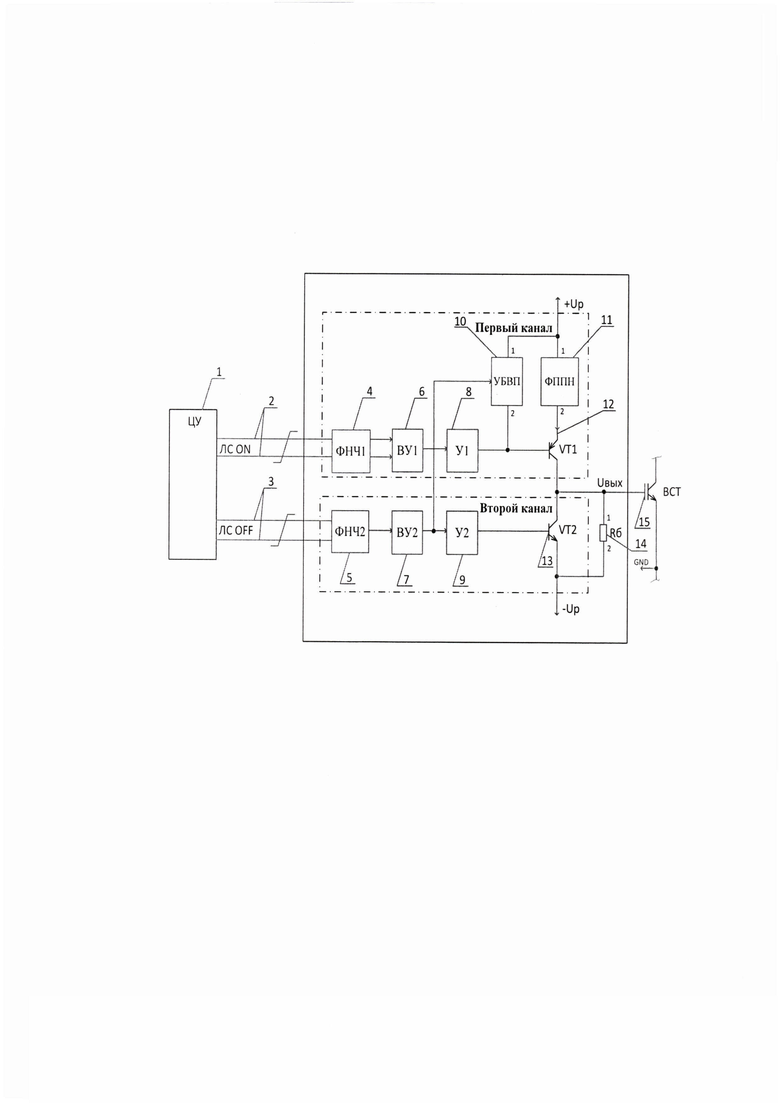

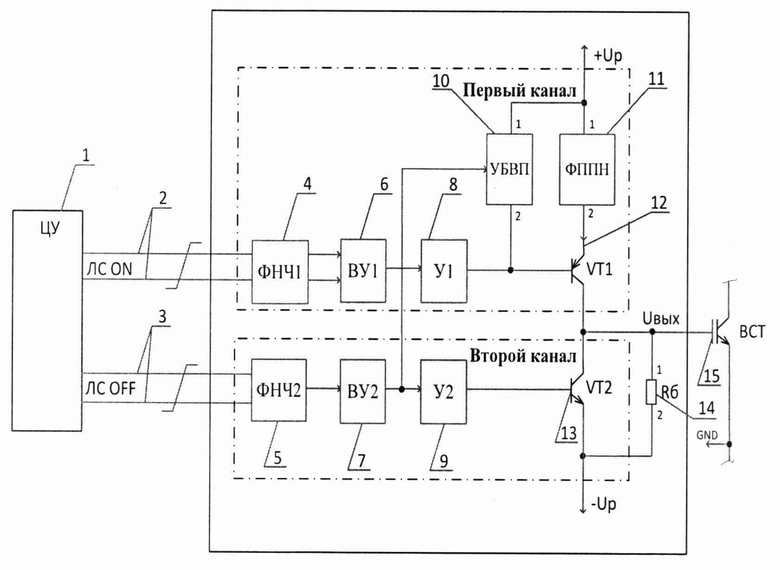

Изобретение иллюстрируется чертежами:

на фигуре представлена функциональная схема драйвера и внешних устройств.

Внешние устройства включают:

- цифровое устройство (ЦУ) 1;

- внешний силовой транзистор (ВСТ) 15.

- линии связи (ЛС ON) 2 и (ЛС OFF) 3 управления первым и вторым каналами приема сигналов на включение и выключение, соответственно, ВСТ 15, поступающие от ЦУ 1;

Драйвер содержит:

- симметричные фильтры нижних частот (ФНЧ1) 4 и (ФНЧ2) 5, предназначенные для подавления кратковременных электрических паразитных сигналов, возникающих на ЛС ON 2 и ЛС OFF 3, под действием электромагнитных помех (ЭМП);

- входные устройства (ВУ1) 6 и (ВУ2) 7, предназначенные для приема парафазных управляющих сигналов, поступающих по ЛС ON 2 и ЛС OFF 3, а также обеспечения гальванической развязки электрических цепей драйвера и ЦУ 1;

- усилители (У1) 8 и (У2) 9 обеспечивающие усиление сигналов, поступающих с выходов ВУ1 6 и ВУ2 7, по току;

- выходной формирователь токов затвора, представляющего собой полумостовую схему управления ВСТ 15, состоящую из транзистора верхнего плеча VT1 12 p-n-р типа, обеспечивающего формирование выходного сигнала на внешнем выходе драйвера Uвых на включение ВСТ 15 и транзистора нижнего плеча VT2 13 n-p-n типа, обеспечивающего формирование выходного сигнала на внешнем выходе драйвера Uвых на выключение ВСТ 15.

- устройство блокировки верхнего плеча (УБВП) 10, обеспечивающее запирание VT1 12 при поступлении на ВУ2 7 управляющего сигнала по ЛС OFF 3 на выключение ВСТ 15, в том числе, при одновременном поступлении на ВУ1 6 по ЛС ON 2 управляющего сигнала на отпирание VT1 12 и включения ВСТ 15;

- формирователь постоянного падения напряжения (ФППН) 11, обеспечивающий постоянное падение напряжения между его выводами в диапазоне значений (0.7 - 1,5) В, предназначенный для более надежного и быстрого запирания VT1 12 при срабатывании УБВП 10;

- балластный резистор Rб 14, шунтирующий переход коллектор-эмиттер VT2 13, предназначенный для запирания ВСТ 15 при невыдаче обоих управляющих сигналов ЦУ 1 на ЛС ON 2 и ЛС OFF 3 или обрыве ЛС ON 2 и ЛС OFF 3.

ФНЧ1 4, ВУ1 6, У1 8, УБВП 10, ФППН 11 и VT1 12 образуют первый канал приема сигнала, поступающего по ЛС ON 2, на включение ВСТ 15, а ФНЧ2 5, ВУ2 7, У2 9 и VT2 13 - второй канал приема сигнала, поступающего по ЛС OFF 3, на запирание ВСТ 15.

Входы ФНЧ1 4 и ФНЧ2 5 служат для электрического подключения к ЛС ON 2 и ЛС OFF 3, соответственно, выходы ФНЧ1 4 и ФНЧ2 5 электрически подключены к входам ВУ1 6 и ВУ2 7, соответственно, выход ВУ1 6 электрически подключен к входу У1 8, выход ВУ2 7 электрически подключен к входам второго усилителя У2 9 и УБВП 10, выход У1 8 электрически соединен с базой VT1 12 и вторым выходом УБВП 10, выход У2 9 электрически соединен с базой VT2 13, коллекторы VT1 12 и VT2 13 электрически соединены между собой и подключены к первому выводу Rб 14, а также к внешнему выходу драйвера Uвых, соединенному с затвором ВСТ 15, эмиттер VT1 12 электрически подключен ко второму выводу ФППН 11, первый вывод которого подключен к шине положительного напряжения питания постоянного тока (+Up) и первому выходу УБВП 10, эмиттер VT2 13 электрически подключен ко второму выводу Rб 14 и к шине отрицательного напряжения питания постоянного тока (-Up), эмиттер ВСТ 15 подключен к средней по потенциалу точке между +Up и -Up - (GND).

Таким образом, первый канал приема сигнала на включение ВСТ 15 образован из последовательно включенных ФНЧ1 4, ВУ1 6, У1 8 и VT1 12 и ФППН 11, подключенного вторым выводом к эмиттеру VT1 12, а первым выводом к +Up, а также УБВП 10, подключенного вторым выводом к базе VT1 12, а первым выводом к +Up, тогда как второй канал приема сигнала на выключение ВСТ 15 состоит из последовательно включенных ФНЧ2 5, ВУ2 7, У2 9, VT2 13, при этом выход ВУ2 7 соединен с управляющим входом УБВП 10 из состава первого канала. За счет такого соединения обеспечивается, при поступлении управляющего сигнала от ЦУ 1 по ЛС OFF 3 во второй канал приема, не только включение VT2 13, вырабатывающего сигнал на внешнем выходе драйвера Uвых выключения ВСТ 15, но и срабатывание УБВП 10, что приводит к прикладыванию к переходу эмиттер-база VT1 12 отрицательного потенциала, практически равного падению напряжения на ФППН 11, и, вызванное им, принудительное закрывание VT1 12, даже при одновременном поступлении управляющего сигнала по ЛС ON 2 в первый канал приема на включение ВСТ 15.

Поэтому, появление паразитного сигнала в цепи ЛС ON 2, приводящего к кратковременному формированию в первом канале сигнала на открывание ВСТ 15, не приводит к его открыванию, так как любое прохождение сигнала в первом канале блокируется, сформированным по цепи ЛС OFF 3, штатным сигналом на закрывание ВСТ 15 во втором канале.

Паразитный сигнал в цепях ЛС OFF 3, противоположный по полярности штатному сигналу на выключение ВСТ 15, обладающий достаточной интенсивностью, чтобы, накладываясь на штатный сигнал, приводить к его кратковременному пропаданию во втором канале, также, не приведет к открыванию ВСТ 15, так как его закрытое состояние в таком режиме поддерживается с помощью Rб 14.

При обрыве ЛС ON 2 и ЛС OFF 3 закрытое состояние ВСТ 15, также, обеспечивается с помощью Rб 14.

Следовательно, появление паразитных электрических сигналов на ЛС ON 2 и ЛС OFF 3 или их обрыв не приводит к ложному включению ВСТ 15, что обеспечивает повышенную помехоустойчивость и надежность функционирования драйвера в условиях наличия ЛС ON 2 и ЛС OFF 3 повышенной протяженности, а также воздействия на них интенсивных электромагнитных помех.

Совокупность качественных характеристик драйвера: высокой помехоустойчивости, надежности и безопасности, допускает его применение в аппаратуре с повышенными требованиями к длине ЛС ON 2 и ЛС OFF 3 и воздействию электромагнитных помех, в том числе, с критическими требованиями по невыдаче ложных выходных сигналов на включение ВСТ 15 в процессе эксплуатации, например - в цепях задействования пиротехнических и взрывных устройств, что расширяет область его применения.

Работа драйвера осуществляется следующим образом. При поступлении по ЛС ON 2 управляющего сигнала на вход первого канала, производится фильтрация данного сигнала от высокочастотных неинформативных составляющих на ФНЧ1 4, его прием и гальваническая развязка от ЛС ON 2 на ВУ1 6, с последующим усилением сигнала на У1 8. При условии отсутствия управляющего сигнала, поступающего по ЛС OFF 3 на вход второго канала, отфильтрованный и усиленный сигнал поступает на базу VT1 12, создавая ток через его переход эмиттер - база. VT1 12 открывается, при этом, положительное, относительно потенциала GND, напряжение +Up, через ФППН 11 и переход эмиттер - коллектор VT1 15, прикладывается к выходу драйвера Uвых, формируя сигнал на включение ВСТ 15. При поступлении по ЛС OFF 3 управляющего сигнала, во втором канале производится, аналогично первому каналу, выделение и обработка сигнала, приводящая к открыванию VT2 13 и подаче на выход драйвера Uвых, через переход коллектор - эмиттер VT2 13, отрицательного, относительно потенциала GND, напряжения -Up, формируя сигнал на выключение ВСТ 15. Дополнительно, выходной сигнал с ВУ2 7 поступает на вход УБВП 10, которое включается и блокирует поступление выходного сигнала с У1 8 на базу транзистора VT1 12, устанавливая потенциал базы VT1 12 близким к напряжению +Up.Это приводит к формированию на переходе эмиттер - база VT1 12 отрицательного потенциала, ориентировочно равного падению напряжения на ФППН 11, и принудительному закрыванию VT1 12, даже при наличии управляющего сигнала в первом канале. Такой режим поочередного функционирования VT1 12 и VT2 13, дополнительно, обеспечивает защиту от сквозных токов через данные транзисторы, вызванных их одновременно открытым состоянием.

Данный алгоритм работы драйвера обеспечивает:

- высокую помехоустойчивость драйвера к паразитным электрическим сигналам, поступающим по ЛС ON 2 и ЛС OFF 3, вызванным воздействием электромагнитных помех, а, следовательно, повышенную надежность защиты от ложного включения исполнительных устройств, управляемых драйвером и, в целом, повышение общей безопасности эксплуатации устройств, в состав которых входит драйвер;

- защиту от сквозных токов через VT1 12 и VT2 13, вызванных одновременно открытым состоянием VT1 12 и VT2 13.

Помехоустойчивость драйвера к паразитным электрическим сигналам, вызванных воздействием электромагнитных помех на ЛС OFF 3, направленных на кратковременное выключение исполнительных устройств обеспечивается их подавлением ФНЧ1 4.

Таким образом, заявляемое техническое решение позволит создать драйвер управления силовыми транзисторами с высокой помехостойкостью и безопасностью, а также повышенной надежностью и широкой областью применения, в том числе, в устройствах с критическими требованиями в части невыдачи ложных срабатываний в процессе эксплуатации.

Заявляемый драйвер в составе различных устройств может обеспечивать их надежное функционирование и защиту от ложных включений, при длине линий связи от устройства управления до драйвера более 10 м, при высокой интенсивности электромагнитных помех.

Представленные выше сведения свидетельствуют о выполнении при использовании заявляемого изобретения следующей совокупности условий:

- заявляемый драйвер управления силовыми транзисторами относится к области силовых электронных устройств различного назначения, в частности, к устройствам сопряжения между цифровыми устройствами и силовыми МОП или IGBT (БТИЗ) транзисторами;

- заявляемый драйвер при использовании способен обеспечить высокую помехоустойчивость и безопасность, а также повышенную надежность;

- для заявляемого драйвера в том виде, в котором он охарактеризован в формуле изобретения, подтверждена возможность его осуществления с помощью описанных в заявке и известных до даты приоритета средств и методов.

Следовательно, заявленный драйвер соответствует условию «промышленная применимость».

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СТАБИЛИЗАЦИИ УРОВНЯ ТОКА В ОБМОТКЕ ДВУХФАЗНОГО БИПОЛЯРНОГО ШАГОВОГО ДВИГАТЕЛЯ В ПОЛНОШАГОВОМ РЕЖИМЕ И ДРАЙВЕР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2019 |

|

RU2708073C1 |

| СПОСОБ И РЕВЕРСИВНОЕ УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ЭНЕРГИИ МАГНИТНОГО ПОЛЯ ФЕРРОМАГНИТНОГО СЕРДЕЧНИКА В ТЕПЛОВУЮ ИЛИ ЭЛЕКТРИЧЕСКУЮ ЭНЕРГИЮ | 2014 |

|

RU2586251C2 |

| ЩИТ УПРАВЛЕНИЯ ЭЛЕКТРОПИТАНИЕМ | 2008 |

|

RU2406201C2 |

| МНОГОКАНАЛЬНЫЙ ИМПУЛЬСНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ | 2024 |

|

RU2838912C1 |

| ИМПУЛЬСНЫЙ ИСТОЧНИК НАПРЯЖЕНИЯ | 2014 |

|

RU2551118C1 |

| ПОЛУМОСТОВОЙ АВТОГЕНЕРАТОРНЫЙ ИНВЕРТОР | 2014 |

|

RU2573647C1 |

| КОММУТАТОР ШИН ЭЛЕКТРОПИТАНИЯ | 2010 |

|

RU2444840C1 |

| МАЛОГАБАРИТНЫЙ ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР, УСТОЙЧИВЫЙ К ВОЗДЕЙСТВИЮ ИОНИЗИРУЮЩИМ ИЗЛУЧЕНИЕМ | 2013 |

|

RU2557479C2 |

| Способ оптимального поддержания скорости транспортного средства в режиме круиз-контроля | 2016 |

|

RU2629616C2 |

| СИСТЕМА ОСВЕЩЕНИЯ | 2021 |

|

RU2789082C1 |

Изобретение относится к области силовой электроники, в частности, к устройствам сопряжения между цифровыми устройствами с силовыми МОП (Металл - Оксид - Полупроводник) или IGBT (БТИЗ - биполярными транзисторами с изолированными затворами) транзисторами. Драйвер предназначен для управления силовыми транзисторами в электронной аппаратуре с высокими уровнями электромагнитных помех или высокими требованиями к надежности работы, а также при значительной длине линий связи, по которым на драйвер поступают сигналы управления. Техническим результатом, получаемым при использовании заявляемого изобретения, является высокая помехоустойчивость, безопасность и надежность, при расширении области применения. Отличительной особенностью драйвера является управление его работой с помощью двух внешних независимых парафазных сигналов, поступающих по отдельным линиям связи. Формирование выходного сигнала драйвера на включение или выключение внешнего силового транзистора производится на основе логического анализа состояния обоих входных управляющих сигналов, имеющих разный уровень приоритета. 1 ил.

Драйвер управления силовыми транзисторами с повышенной помехоустойчивостью, содержащий гальванически развязанную цепь управления, промежуточный усилитель и выходной формирователь токов затвора, отличающийся тем, что он включает две линии связи управления с отдельными каналами приема сигналов на включение и выключение внешнего силового транзистора, первый и второй канал, соответственно, дополнительно он содержит первый и второй симметричные фильтры нижних частот, устройство блокировки верхнего плеча выходного формирователя токов затвора, формирователь постоянного падения напряжения и балластный резистор, а гальванически развязанная цепь управления состоит из первого и второго входных устройств, промежуточный усилитель состоит из первого и второго усилителей, выходной формирователь токов затвора состоит из двух транзисторов, p-n-p-типа верхнего плеча и n-p-n-типа нижнего плеча, соответственно, при этом входы первого и второго фильтров нижних частот служат для электрического подключения внешних управляющих сигналов, на включение и выключение внешнего силового транзистора, соответственно, выходы первого и второго фильтров нижних частот электрически подключены к входам первого и второго входных устройств, соответственно, выход первого входного устройства электрически подключен к входу первого усилителя, выход второго входного устройства электрически подключен к входам второго усилителя и устройства блокировки верхнего плеча, выход первого усилителя электрически соединен с базой транзистора верхнего плеча и вторым выходом устройства блокировки верхнего плеча, выход второго усилителя электрически соединен с базой транзистора нижнего плеча, коллекторы транзисторов верхнего и нижнего плеча электрически соединены между собой и подключены к первому выводу балластного резистора, а также к выходу управления внешним силовым транзистором, эмиттер транзистора верхнего плеча электрически подключен ко второму выводу формирователя постоянного падения напряжения, первый вывод формирователя постоянного падения напряжения подключен к шине положительного напряжения питания постоянного тока и первому выходу устройства блокировки верхнего плеча, эмиттер транзистора нижнего плеча электрически подключен ко второму выводу балластного резистора и к шине отрицательного напряжения питания постоянного тока, таким образом, первый канал приема сигнала на включение внешнего силового транзистора образован из последовательно включенных первого фильтра нижних частот, первого входного устройства, первого промежуточного усилителя, устройства блокировки верхнего плеча, формирователя постоянного падения напряжения и транзистора верхнего плеча, а второй канал приема сигнала на выключение внешнего силового транзистора состоит из второго фильтра нижних частот, второго входного устройства, второго промежуточного усилителя и транзистора нижнего плеча.

| US 10715132 B2, 14.07.2020 | |||

| US 2021119627 A1, 22.04.2021 | |||

| Клей на основе жидкого стекла | 1949 |

|

SU107419A1 |

| Способ очистки ячеек сетки механизированных сит и устройство для осуществления этого способа | 1952 |

|

SU94084A1 |

| Устройство для защиты ртутных выпрямителей от коротких замыкании и обратных зажиганий | 1932 |

|

SU31071A1 |

| US 10944330 B1, 09.03.2021. | |||

Авторы

Даты

2022-05-13—Публикация

2021-10-07—Подача