Изобретение относится к вычислительной технике и может быть использовано в синтезаторах частот и делителях частоты с дробным коэффициентом деления, а также в устройствах цифровой обработки сигналов и в криптографических приложениях.

Известны накапливающие сумматоры [1], [2], [3], содержащие двоичные сумматоры и регистры.

Недостатком этих устройств является то, что они осуществляют суммирование чисел по модулю, равному натуральной степени числа два, тогда как во многих задачах требуется суммирование по модулю произвольных чисел.

Также из уровня техники известен накапливающий сумматор по модулю [4], содержащий n-разрядный и (n+1)-разрядный сумматоры, мультиплексор и регистр, позволяющий осуществлять суммирование по модулю произвольных чисел.

Недостатком этого устройства является низкое быстродействие, так как задержка распространения сигналов увеличивается на величину задержки в (n+1)-разрядном сумматоре и мультиплексоре.

Наиболее близким по технической сущности к заявленному изобретению является накапливающий сумматор для синтезаторов частот [5], содержащий два n-разрядных сумматора, мультиплексор, регистр, а также (n+1)-разрядный сумматор, позволяющий осуществлять суммирование по модулю произвольных чисел.

Недостатком этого устройства является большой объем оборудования и как следствие большое энергопотребление, что ограничивает его применение в автономных мобильных устройствах.

Техническим результатом является сокращение объема оборудования и как следствие уменьшение энергопотребления.

Указанный технический результат достигается тем, что в накапливающем сумматоре для синтезаторов частот, содержащем (n+1)-разрядный сумматор, n-разрядный мультиплексор и n-разрядный регистр, причем вход переноса устройства соединен со входом переноса (n+1)-разрядного сумматора, (1…n)-й разряды информационных выходов которого соединены со вторыми информационными входами n-разрядного мультиплексора, информационные выходы которого соединены с информационными входами n-разрядного регистра, информационные выходы которого соединены с информационными выходами устройства, тактовый вход соединен с тактовым входом устройства, вход установки в начальное состояние соединен со входом установки в начальное состояние устройства, первый информационный вход устройства был соединен с первым разрядом первых информационных входов (n+1)-разрядного сумматора и n-разрядного мультиплексора, вторые информационные входы устройства соединены с (1…n)-ми разрядами вторых информационных входов (n+1)-разрядного сумматора, выход переноса которого соединен с управляющим входом мультиплексора, (1…n)-й разряды информационных выходов n-разрядного регистра соединены со (2…(n+1))-м разрядами первых информационных входов (n+1)-разрядного сумматора соответственно, а (1…(n-1))-й разряды соединены с (2…n)-м разрядами первых информационных входов n-разрядного мультиплексора.

Сущность изобретения заключается в реализации следующего способа накопительного суммирования чисел Ai по произвольному модулю P. Накапливающее суммирование осуществляется в соответствии с выражением

Si = (2Si-1 + Ai) mod P, i = 1, 2, 3, … ,

где Si - значение суммы на выходе устройства на i-ом такте работы;

Ai - число, принимающее значение 0 или 1, поступающее на вход устройства на i-ом такте работы.

До первого такта работы устройство устанавливается в начальное состояние S0 в диапазоне чисел от 0 до P-1.

Если значение выражения Si = 2Si-1+Ai меньше P, то выполняется обычное суммирование Si = 2Si-1+Ai и эта сумма Si является результатом работы устройства на i-ом такте. Если же значение выражения (Si = 2Si-1+Ai) ≥ P, то результатом работы устройства на i-ом такте является значение (2Si-1+Ai) - P.

В результате реализации такого алгоритма накаливающего суммирования на выходе устройства образуется последовательность чисел, которая может быть использована в синтезаторах частот с малым энергопотреблением.

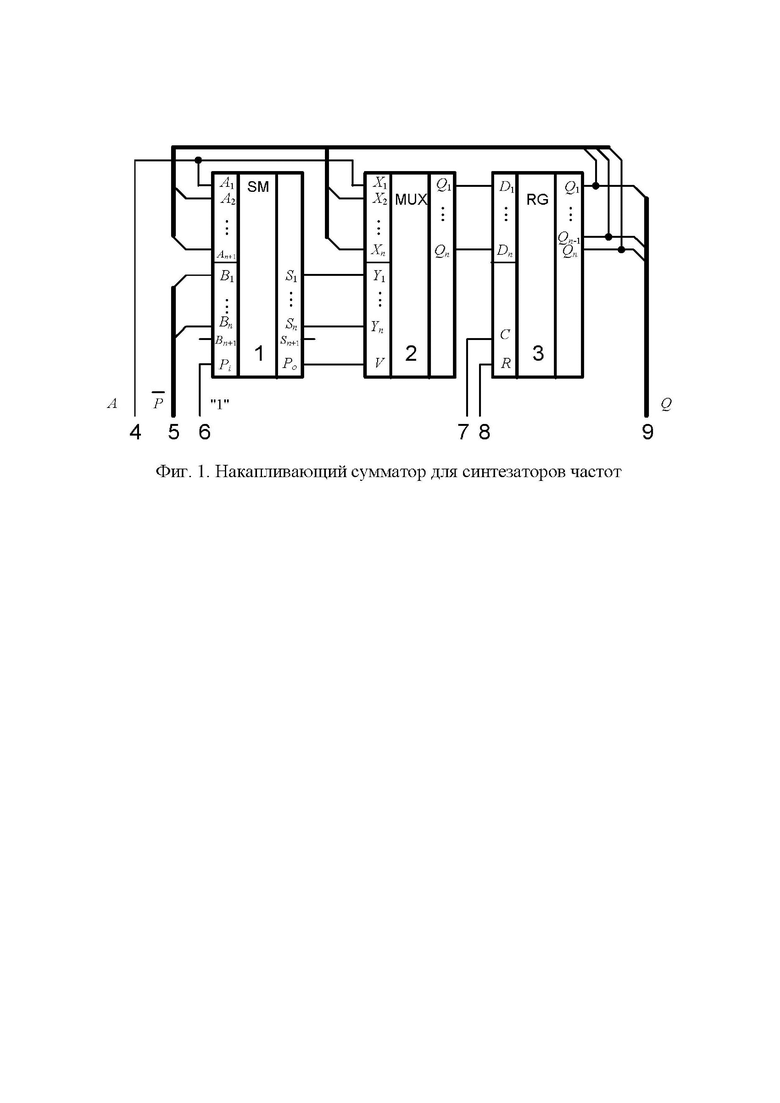

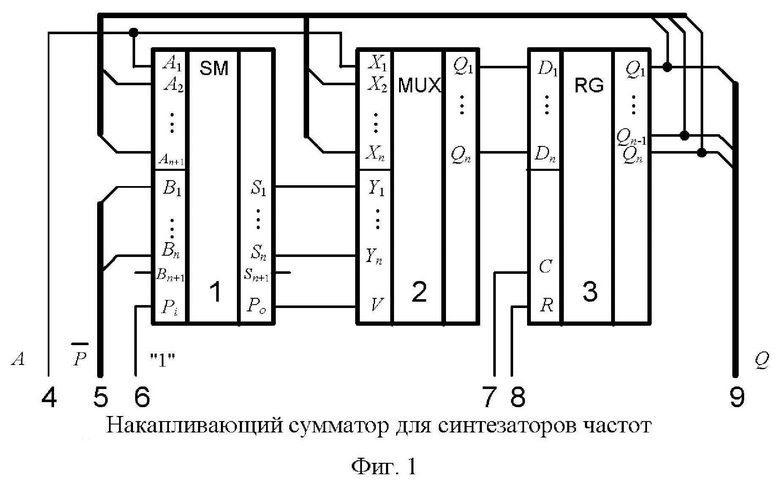

На фиг. 1 представлена схема накапливающего сумматора для синтезаторов частот.

Накапливающий сумматор для синтезаторов частот содержит (n+1)-разрядный сумматор 1, n-разрядный мультиплексор 2, n-разрядный регистр 3, первый информационный вход 4, вторые информационные входы 5, вход переноса 6, тактовый вход 7, вход установки в начальное состояние 8 и информационные выходы 9.

На первый информационный вход 4, последовательно, синхронно с тактовыми импульсами, подаваемыми на тактовый вход 7, подается последовательность чисел Ai, на вход переноса 6 подается сигнал логической единицы, на вторые информационные входы 5 подается код модуля в инверсном виде, вход установки в начальное состояние 8 служит для установки в начальное состояние устройства перед началом работы. Информационные выходы 9 являются выходами устройства.

Первый информационный вход 4 устройства соединен с первым разрядом первых информационных входов (n+1)-разрядного сумматора 1 и n-разрядного мультиплексора 2, второй информационный вход устройства соединен с (1…n)-ми разрядами вторых информационных входов (n+1)-разрядного сумматора 1. Вход переноса 6 устройства соединен со входом переноса (n+1)-разрядного сумматора 1, выход переноса которого соединен с управляющим входом мультиплексора 2, а (1…n)-й разряды информационных выходов соединены со вторыми информационными входами n-разрядного мультиплексора 2, информационные выходы которого соединены с информационными входами n-разрядного регистра 3, информационные выходы которого соединены с информационными выходами устройства, причем (1…n)-й разряды информационных выходов n-разрядного регистра 3 также соединены со (2…(n+1))-м разрядами первых информационных входов (n+1)-разрядного сумматора 1 соответственно, а (1…(n-1))-й разряды также соединены с (2…n)-м разрядами первых информационных входов n-разрядного мультиплексора 2. Тактовый вход n-разрядного регистра 3 соединен с тактовым входом 7 устройства, а вход установки в начальное состояние соединен со входом установки в начальное состояние 8 устройства.

Накапливающий сумматор для синтезаторов частот работает следующим образом (см. фиг. 1).

Перед началом работы на вход установки в начальное состояние 8 устройства подается импульс, который устанавливает устройство в начальное состояние S0, записывая в n-разрядный регистр 3 число из диапазона чисел от 0 до P-1. На тактовый вход 7 устройства поступают тактовые импульсы, которые синхронизируют работу устройства. С каждым тактовым импульсом i = 1, 2, 3, … на первый информационный вход 4 поступают коды чисел Ai, поступающие далее на первый разряд первых информационных входов (n+1)-разрядного сумматора 1 и на первый разряд n-разрядного мультиплексора 2. Входные числа Ai могут принимать значение 0 или 1. На (2…(n+1))-е разряды первых информационных входов (n+1)-разрядного сумматора 1 поступает код числа с (1…n)-го разрядов информационных выходов n-разрядного регистра 3. В результате на первых информационных входах (n+1)-разрядного сумматора 1 образуется сумма 2S0 + A1. Так как на вторые информационные входы (n+1)-разрядного сумматора 1 со вторых информационных входов 5 поступает инверсный код модуля P, а на его вход переноса со входа переноса 6 поступает сигнал логической единицы, то на информационных выходах (n+1)-разрядного сумматора 1 образуется значение (2S0 + A1) - P.

В случае, если ((2S0 + A1) - P) ≥ 0, то на выходе переноса (n+1)-разрядного сумматора 1 образуется логический ноль, который воздействуя на управляющий вход мультиплексора 2, обеспечит коммутацию на его информационные выходы его вторых информационных входов.

Если же ((2S0 + A1) - P) < 0, то на выходе переноса (n+1)-разрядного сумматора 1 образуется сигнал логической единицы, который воздействуя на управляющий вход мультиплексора 2, обеспечит коммутацию на его информационные выходы его первых информационных входов. При этом на первых информационных входах мультиплексора 2 присутствует код числа (2S0 + A1).

В результате на информационных выходах мультиплексора 2 образуется код числа S1 = ((2S0 + A1) mod P, который под воздействием тактового импульса с тактового входа 7 будет записан в n-разрядный регистр 3 и поступит на информационные выходы 9 устройства.

Устройство прототип содержит 3 сумматора, мультиплексор и регистр. Предложенное же устройство содержит один сумматор, мультиплексор и регистр. В результате объем оборудования сокращен на два n-разрядных сумматора. Учитывая, что сумматор потребляет примерно в 3-4 раза больше энергии, чем мультиплексор или регистр, предложенное устройство будет потреблять в 2-2,3 раза меньше энергии, чем устройство прототип.

Источники информации

1. Тарабрин Б.В. Справочник по интегральным микросхемам/Б.В. Тарабрин, С.В. Якубовский, Н.А. Барканов и др.; под ред. Б.В. Тарабрина - 2-е изд., перераб. и доп. - М.: Энергия, 1981, рис. 5-250, стр.741.

2. Наумкина Л.Г. Цифровая схемотехника. Конспект лекций по дисциплине «Схемотехника» - М.: «Горная книга», Издательство Московского государственного горного университета, 2008. рис. 6.9, стр.228

3. Патент RU 2544748 С1. Накапливающий сумматор. Опубликован 20.03.2015. Бюл. №8.

4. Патент RU 2500017 С1. Накапливающий сумматор по модулю. Опубликован 17.11.2013. Бюл. № 33.

5. Патент RU 2753594 С1. Накапливающий сумматор для синтезаторов частот. Опубликован 18.08.2021 Бюл. № 23.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2835073C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2829093C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ДЛЯ СИНТЕЗАТОРОВ ЧАСТОТ | 2020 |

|

RU2753594C1 |

| Накапливающий сумматор по модулю | 2022 |

|

RU2791441C1 |

| ДВУХКАНАЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ | 2024 |

|

RU2823898C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2020 |

|

RU2754122C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ГРУППОВОЙ СТРУКТУРЫ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ С ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ | 2024 |

|

RU2833212C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ | 2012 |

|

RU2500017C1 |

| Накапливающий сумматор | 2017 |

|

RU2642366C1 |

| УМНОЖИТЕЛЬ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2839987C1 |

Изобретение относится к вычислительной технике и может быть использовано в синтезаторах частот и делителях частоты с дробным коэффициентом деления, а также в устройствах цифровой обработки сигналов и в криптографических приложениях. Технический результат заключается в уменьшении энергопотребления синтезатора частот. Технический результат достигается за счет того, что первый информационный вход устройства соединен с первым разрядом первых информационных входов (n+1)-разрядного сумматора и n-разрядного мультиплексора, вторые информационные входы устройства соединены с (1…n)-ми разрядами вторых информационных входов (n+1)-разрядного сумматора, выход переноса которого соединён с управляющим входом мультиплексора, (1…n)-е разряды информационных выходов n-разрядного регистра соединены с (2…(n+1))-ми разрядами первых информационных входов (n+1)-разрядного сумматора соответственно, а (1…(n-1))-е разряды соединены с (2…n)-ми разрядами первых информационных входов n-разрядного мультиплексора. 1 ил.

Накапливающий сумматор для синтезаторов частот, содержащий (n+1)-разрядный сумматор, n-разрядный мультиплексор и n-разрядный регистр, причем вход переноса устройства соединен со входом переноса (n+1)-разрядного сумматора, (1…n)-е разряды информационных выходов которого соединены со вторыми информационными входами n-разрядного мультиплексора, информационные выходы которого соединены с информационными входами n-разрядного регистра, информационные выходы которого соединены с информационными выходами устройства, тактовый вход соединен с тактовым входом устройства, вход установки в начальное состояние соединен со входом установки в начальное состояние устройства, отличающийся тем, что первый информационный вход устройства соединен с первым разрядом первых информационных входов (n+1)-разрядного сумматора и n-разрядного мультиплексора, вторые информационные входы устройства соединены с (1…n)-ми разрядами вторых информационных входов (n+1)-разрядного сумматора, выход переноса которого соединён с управляющим входом мультиплексора, (1…n)-е разряды информационных выходов n-разрядного регистра соединены с (2…(n+1))-ми разрядами первых информационных входов (n+1)-разрядного сумматора соответственно, а (1…(n-1))-е разряды соединены с (2…n)-ми разрядами первых информационных входов n-разрядного мультиплексора.

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ | 2012 |

|

RU2500017C1 |

| US 6630849 B2, 07.10.2003 | |||

| Накапливающий сумматор | 2017 |

|

RU2642366C1 |

| Параллельный сумматор | 2016 |

|

RU2635247C1 |

| RU 2059286 C1, 27.04.1996. | |||

Авторы

Даты

2022-12-02—Публикация

2022-10-03—Подача