Изобретение относится к вычислительной технике и может быть использовано в арифметических сумматорах для выполнения операций суммирования над числами в двоичном коде.

Известен сумматор с последовательным переносом, содержащий объединенные в цепь N полные одноразрядные сумматоры (рис. 5.5, стр. 604. Дэвид М. Хэррис и Сара Л. Хэррис. Цифровая схемотехника и архитектура компьютера. Второе издание. Издательство Morgan Kaufman. English Edition, 2013). Сумматор позволяет выполнять параллельное суммирование двух n-разрядных чисел.

Недостатком данного сумматора является то, что скорость его суммирования падает при увеличении числа N.

Наиболее близким по технической сущности к заявляемому изобретению является сумматор с условным переносом (рис. 2.32, стр. 88-89. Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ - Петербург, 2004. - 528 с.), содержащий три параллельных n/2-разрядных сумматора, один n/2-разрядный двухвходовый мультиплексор и один одноразрядный двухвходовый мультиплексор. Сумматор позволяет выполнять параллельное суммирование двух n - разрядных чисел.

Недостатком данного сумматора является большой объем оборудования.

Техническим результатом данного изобретения является сокращение объема оборудования и, как следствие, уменьшение энергопотребления за счет исключения одного n/2-разрядного двухвходового мультиплексора, одного одноразрядного двухвходового мультиплексора, одного n/2-разрядного сумматора и введения одного (n/2+1)-разрядного полусумматора.

Для достижения технического результата в параллельный сумматор, содержащий два n/2-разрядных сумматора, причем первые информационные входы первого n/2-разрядного сумматора являются входами младших разрядов первого слагаемого, вторые информационные входы являются входами младших разрядов второго слагаемого, вход переноса является входом переноса параллельного сумматора, а информационные выходы являются выходами младших разрядов суммы параллельного сумматора, первые информационные входы второго n/2-разрядного сумматора являются входами старших разрядов первого слагаемого, вторые информационные входы являются входами старших разрядов второго слагаемого, а на вход переноса подается логический «0», введен (n/2+1)-разрядный полусумматор, второй информационный вход которого соединен с выходом переноса первого n/2-разрядного сумматора, младшие n/2 первые информационные входы соединены с информационными выходами второго n/2-разрядного сумматора, (n/2+1)-й первый информационный вход соединен с выходом переноса второго n/2-разрядного сумматора, младшие n/2 информационные выходы являются выходами старших разрядов суммы параллельного сумматора, а (n/2+1)-й информационный выход является выходом переноса параллельного сумматора.

Сущность изобретения заключается в реализации следующего способа суммирования n - разрядных чисел А и В.

Имея n-разрядный сумматор, делят его на 2 равные n/2-разрядные группы. На первом n/2-разрядном сумматоре суммируют младшие с 1 по n/2 разряды слагаемых Амл и Вмл, на втором n/2-разрядном сумматоре суммируют старшие поля операндов Аст и Bст при условии, что перенос на Cin2 на втором n/2-разрядном сумматоре равен «0». После получения результата в первом n/2-разрядном сумматоре становится известным фактическое значение переноса во второй n/2-разрядный сумматор. К этому моменту времени становится также известен результат во втором n/2-разрядном сумматоре. Используя (n/2+1)-разрядный полусумматор, суммируют значение переноса с результатом второго n/2-разрядного сумматора. В итоге получают окончательное значение старших разрядов суммы.

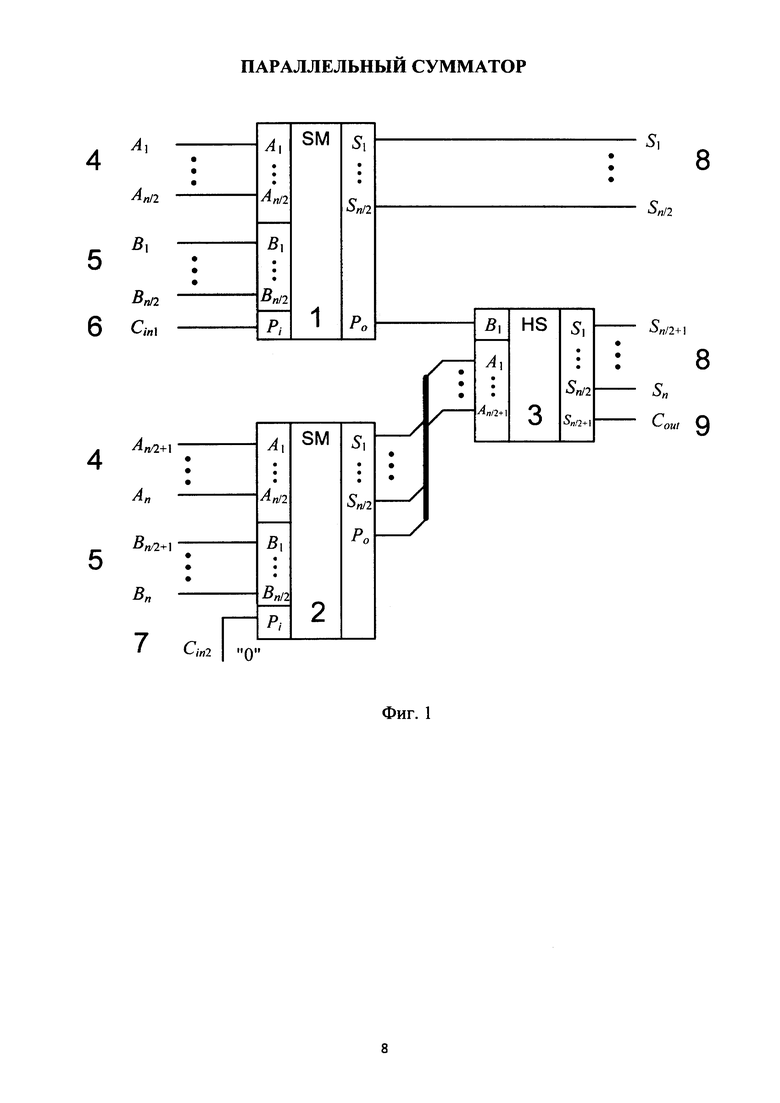

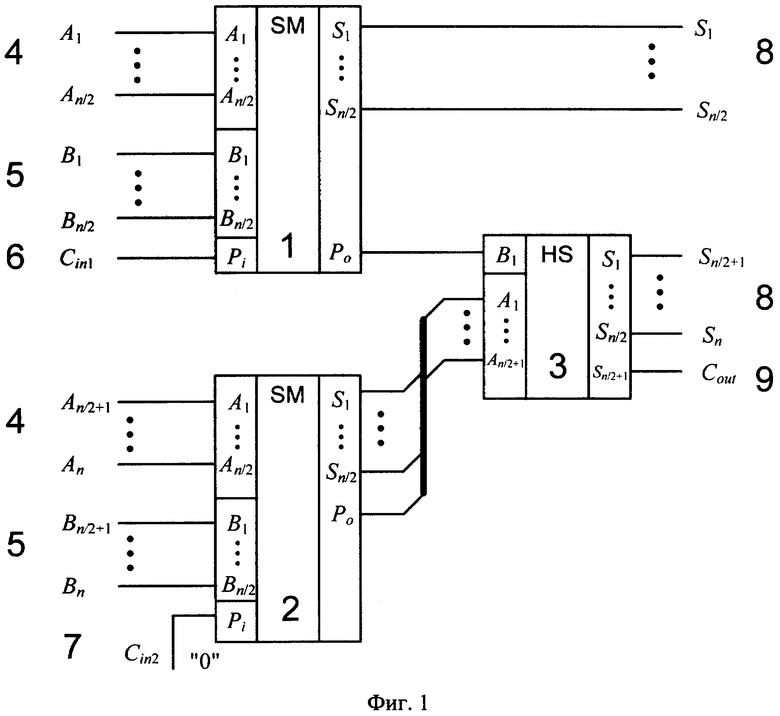

На фиг. 1 представлена схема параллельного сумматора.

Параллельный сумматор содержит два n/2-разрядных сумматора 1 и 2, (n/2+1)-разрядный полусумматор 3, информационные входы 4 первого слагаемого А, разделенные на младшие разряды Амл с А1 по Аn/2 и старшие разряды Aст с Аn/2+1 по Аn, информационные входы 5 второго слагаемого В, также разделенные на младшие разряды Вмл с В1 по Вn/2 и старшие разряды Вст с Вn/2+1 по Вn, первый вход 6 переноса Cin1, второй вход переноса 7 Cin2, выход 8 суммы S, выход 9 переноса Сout. Первые информационные входы первого n/2-разрядного сумматора 1 являются информационными входами 4 младших разрядов первого слагаемого Амл, вторые информационные входы являются информационными входами 5 младших разрядов второго слагаемого Вмл, вход переноса является первым входом 6 переноса Сin1 параллельного сумматора, а информационные выходы являются выходами 8 младших разрядов суммы Sмл параллельного сумматора, первые информационные входы второго n/2-разрядного сумматора 2 являются информационными входами 4 старших разрядов Аст первого слагаемого, вторые информационные входы являются информационными входами 5 старших разрядов Вст второго слагаемого, а на второй вход 7 переноса Cin2 подается логический «0», второй информационный вход (n/2+1)-разрядного полусумматора 3 соединен с выходом переноса первого n/2-разрядного сумматора 1, младшие n/2 первые информационные входы соединены с информационными выходами второго n/2-разрядного сумматора 2, (n/2+1)-й первый информационный вход соединен с выходом переноса второго n/2-разрядного сумматора 2, младшие n/2 информационные выходы являются выходами 8 старших разрядов суммы Sст параллельного сумматора, а (n/2+1)-й информационный выход является выходом 9 переноса Сout параллельного сумматора.

Параллельный сумматор работает следующим образом.

Первое А и второе В n-разрядные слагаемые разделяют на n/2 младшие (A1 … An/2) (В1 … Вn/2) и n/2 старшие (Аn/2+1 … Аn), (Вn/2+1 … Вn) разряды. Первое слагаемое поступает на информационный вход 4, а второе слагаемое поступает на информационный вход 5 параллельного сумматора. На первый вход 6 переноса Cin1 параллельного сумматора при увеличении разрядности суммируемых чисел может подаваться сигнал переноса. Младшие разряды первого (А1 … Аn/2) и второго (В1 … Вn/2) слагаемых суммируются в первом n/2-разрядном сумматоре 1. Одновременно старшие разряды первого (Аn/2+1 … Аn) и второго (Вn/2+1 … Вn) слагаемых суммируются во втором n/2-разрядном сумматоре 2, на второй вход 7 переноса которого подается сигнал логического «0». На выходах 8 суммы (S1 … Sn/2) первого n/2-разрядного сумматора 1 образуются младшие разряды суммы S. Сигнал переноса с выхода переноса Рo первого n/2-разрядного сумматора 1 суммируется с промежуточными результатами суммы старших разрядов, образующихся на выходе второго n/2-разрядного сумматора 2 в n/2+1-разрядном полусумматоре 3. В результате на (S1 … Sn/2) информационных выходах n/2+1-разрядного полусумматора 3 образуется окончательная сумма старших разрядов, которая поступает на (Sn/2+1 … Sn) выходы 8 суммы S параллельного сумматора, а на Sn/2+1 информационном выходе n/2+1-разрядного полусумматора 3 образуется сигнал переноса Cout, который поступает на выход 9 переноса устройства.

Рассмотрим работу параллельного сумматора на конкретном примере.

Пусть разрядность слагаемых А и В n составляет 4 бита, пусть А=1310=11012, В=710=01112. Тогда младшие разряды Амл=01, Bмл=11, а старшие разряды Аст=11, Bст=01. На информационных выходах первого n/2-разрядного сумматора 1 образуются младшие разряды суммы Sмл=00, а на выходе переноса Ро первого n/2-разрядного сумматора 1 образуется сигнал логической «1». На выходах второго n/2-разрядного сумматора 2 образуется сумма чисел Аст и Вст=11+01=00, а на его выходе переноса образуется сигнал логической «1». В результате в n/2+1-разрядном полусумматоре 3 осуществляется суммирование чисел 100+1=101. В итоге на выходе устройства образуется число S=101002=2010. Суммирование выполнено корректно, поскольку 13+7=20.

Оценим эффективность предлагаемого устройства по сравнению с прототипом.

Одноразрядный полусумматор содержит 4 элементарных логических элемента, одноразрядный полный сумматор состоит из двух полусумматоров и дополнительного логического элемента, т.е. содержит 9 элементарных логических элементов (рис. 3.52, с. 274 и рис. 3.53, с. 276, Безуглов Д.А. Цифровые устройства и микропроцессоры / Д.А. Безуглов, И.В. Калиенко. - Изд. 2-е. - Ростов н/Д: Феникс, 2008. - 468 с.). Один мультиплексор содержит 3 элементарных логических элемента на один разряд и один логический элемент на всю схему (рис. 3.8 б, с. 104, Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. - М.: Радио и связь. 1990. - 334 с.).

При построении сумматора n-разрядных чисел прототип будет содержать три n/2-разрядных сумматора по 9 элементарных логических элементов на разряд и два мультиплексора, один n/2-разрядный, а второй одноразрядный, соответственно, с 3n/2+1 и 4 элементарными логическими элементами на разряд. Итого прототип будет содержать 3⋅9n/2+3n/2+1+4=15n+5 элементарных логических элементов.

Предлагаемое техническое решение при построении сумматора n-разрядных чисел будет содержать два n/2-разрядных сумматора по 9 элементарных логических элементов на разряд и один (n/2+1)-разрядный полусумматор с 4 элементарными логическими элементами на разряд. Итого предлагаемое техническое решение будет содержать 2⋅9n/2+4(n/2+1)=9n+2n+4=11n+4 элементарных логических элементов.

Таким образом, предлагаемое техническое решение будет содержать на (15n+5)-(11n+4)=4n+1 элементарных логических элементов на один разряд меньше, чем прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий сумматор | 2017 |

|

RU2642366C1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| РЕКОНФИГУРИРУЕМЫЙ АСИНХРОННЫЙ СУММАТОР-УМНОЖИТЕЛЬ | 1999 |

|

RU2159464C1 |

| УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО МОДУЛЮ ТРИ | 1991 |

|

RU2011215C1 |

| ГЕНЕРАТОР С РАЗДЕЛЬНОЙ ЦИФРОВОЙ РЕГУЛИРОВКОЙ ЧАСТОТЫ И ФАЗЫ ИМПУЛЬСОВ | 2000 |

|

RU2168268C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ДЛЯ СИНТЕЗАТОРОВ ЧАСТОТ | 2020 |

|

RU2753594C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2021 |

|

RU2764876C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2021 |

|

RU2763988C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2020 |

|

RU2754122C1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических сумматорах для выполнения операций суммирования над числами в двоичном коде. Технический результат заключается в сокращении объема оборудования и, как следствие, уменьшении энергопотребления за счет исключения одного n/2-разрядного двухвходового мультиплексора, одного одноразрядного двухвходового мультиплексора, одного n/2-разрядного сумматора и введения одного (n/2+1)-разрядного полусумматора. Сущность изобретения заключается в реализации следующего способа суммирования n-разрядных чисел А и В. Имея n-разрядный сумматор, делят его на 2 равные n/2-разрядные группы. На одном n/2-разрядном сумматоре суммируют младшие поля операндов Амл и Вмл, на втором n/2-разрядном сумматоре суммируют старшие поля операндов Аст и Вст при условии, что перенос на Cin2 на втором n/2-разрядном сумматоре равен «0». 1 ил.

Параллельный сумматор, содержащий два n/2-разрядных сумматора, причем первые информационные входы первого n/2-разрядного сумматора являются входами младших разрядов первого слагаемого, вторые информационные входы являются входами младших разрядов второго слагаемого, вход переноса является входом переноса параллельного сумматора, а информационные выходы являются выходами младших разрядов суммы параллельного сумматора, первые информационные входы второго n/2-разрядного сумматора являются входами старших разрядов первого слагаемого, вторые информационные входы являются входами старших разрядов второго слагаемого, а на вход переноса подается логический «0», отличающийся тем, что в него введен (n/2+1)-разрядный полусумматор, второй информационный вход которого соединен с выходом переноса первого n/2-разрядного сумматора, младшие n/2 первые информационные входы соединены с информационными выходами второго n/2-разрядного сумматора, (n/2+1)-й первый информационный вход соединен с выходом переноса второго n/2-разрядного сумматора, младшие n/2 информационные выходы являются выходами старших разрядов суммы параллельного сумматора, а (n/2+1)-й информационный выход является выходом переноса параллельного сумматора.

| Параллельный двоичный сумматор | 1988 |

|

SU1571577A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| СУММАТОР С ПЕРЕМЕННЫМ МОДУЛЕМ СЛОЖЕНИЯ | 2000 |

|

RU2183347C2 |

| US 3987291, 19.10.1976. | |||

Авторы

Даты

2017-11-09—Публикация

2016-12-21—Подача