Область техники, к которой относится изобретение

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах цифровой обработки сигналов, в криптографических приложениях и в системах связи и управления.

Уровень техники

Известен накапливающий сумматор, содержащий три сумматора, регистр и мультиплексор с соответствующими связями, позволяющий выполнять накапливающее суммирование, поступающих на его вход чисел по модулю 2n [1].

Недостатком данного сумматора являются ограниченные функциональные возможности, а именно невозможность выполнения операции накапливающего суммирования по модулю, отличающегося от значения 2n.

Известен накапливающий сумматор, содержащий два сумматора, полусумматор и регистр с соответствующими связями, позволяющий выполнять накапливающее суммирование, поступающих на его вход чисел по модулю 2n [2].

Недостатком данного сумматора являются ограниченные функциональные возможности, а именно невозможность выполнения операции накапливающего суммирования по модулю, отличающегося от значения 2n.

Известен накапливающий сумматор, содержащий два сумматора, мультиплексор и регистр, позволяющий выполнять накапливающее суммирование, поступающих на его вход чисел по произвольному модулю P [3].

Недостатком данного сумматора является большой объем оборудования при работе с числами большой разрядности, что снижает надежность устройства.

Наиболее близким по технической сущности к заявляемому изобретению является накапливающий сумматор по модулю, содержащий n-разрядный сумматор, n одноразрядных сумматоров, (n+1)-разрядный сумматор, мультиплексор и параллельный регистр с соответствующими связями, позволяющий выполнять накапливающее суммирование поступающих на его вход чисел по произвольному модулю P [4].

Недостатком данного сумматора является большой объем оборудования при работе с числами большой разрядности, что снижает надежность устройства.

Техническим результатом изобретения является сокращение объема оборудования при суммировании чисел большой разрядности.

Раскрытие сущности изобретения

Для достижения технического результата в накапливающий сумматор групповой структуры по произвольному модулю с последовательным переносом, содержащий первый n-разрядный накапливающий сумматор по модулю, где n – его разрядность, первые информационные входы устройства, вторые информационные входы устройства, информационные выходы устройства, тактовый вход устройства, соединенный с тактовым входом первого n-разрядного накапливающего сумматора по модулю, при этом младшие n разрядов первых и вторых информационных входов устройства и информационных выходов соединены соответственно с первыми и вторыми информационными входами и информационными выходами первого n-разрядного накапливающего сумматора по модулю, причем первый n-разрядный накапливающий сумматор по модулю содержит n полных одноразрядных разрядных сумматоров, (n+1)-разрядный сумматор, n-разрядный сумматор, n-разрядный мультиплексор и n-разрядный регистр, вход синхронизации которого соединен с тактовым входом первого n-разрядного накапливающего сумматора по модулю, информационные выходы соединены с информационными выходами первого n-разрядного накапливающего сумматора по модулю, первыми информационными входами n-разрядного сумматора и поразрядно с первыми информационными входами n полных одноразрядных сумматоров, первые информационные входы первого n-разрядного накапливающего сумматора по модулю соединены поразрядно со вторыми информационными входами n полных одноразрядных сумматоров и со вторыми информационными входами n-разрядного сумматора, вторые информационные входы первого n-разрядного накапливающего сумматора по модулю соединены поразрядно с входами переноса n полных одноразрядных сумматоров, информационные выходы которых соединены соответственно с (1, …, n)-ми разрядами первых информационных входов (n+1)-разрядного сумматора, а выходы переноса соединены с (2, …, n+1)-ми разрядами вторых информационных входов (n+1)-разрядного сумматора, (1, …, n)-е разряды информационных выходов которого соединены со вторыми информационными входами n-разрядного мультиплексора, первые информационные входы которого соединены с информационными выходами n-разрядного сумматора, а выходы соединены с информационными входами n-разрядного регистра, дополнительно введены (k − 1) n-разрядных накапливающих сумматоров по модулю, где k⋅n = m – разрядность устройства, выход переноса устройства, который соединен с выходом переноса k-го n-разрядного накапливающего сумматора по модулю, при этом тактовый вход устройства соединен с таковыми входами n-разрядных накапливающих сумматоров по модулю, выход переноса модуля k-го n-разрядного накапливающего сумматора по модулю соединен с управляющими входами kn-разрядных накапливающих сумматоров по модулю, которые далее соединены с управляющими входами n-разрядных мультиплексоров, (n+1, …, m)-е разряды первых информационных входов устройства соединены группами по n-разрядов соответственно с первыми информационными входами (2, …, k)-го n-разрядных накапливающих сумматоров по модулю, (n+1, …, m)-е разряды вторых информационных входов устройства соединены группами по n-разрядов соответственно со вторыми информационными входами (2, …, k)-го n-разрядных накапливающих сумматоров по модулю, (n+1, …, m)-е разряды информационных выходов устройства соединены группами по n-разрядов соответственно с информационными выходами (2, …, k)-го n-разрядных накапливающих сумматоров по модулю, вход переноса устройства и вход переноса модуля устройства соединены соответственно с входом переноса и с входом переноса модуля первого n-разрядного накапливающего сумматора по модулю, выходы переноса и выходы переноса модуля (1, …, k−1)-го n-разрядных накапливающих сумматоров по модулю соединены соответственно с входами переноса и с входами переноса модуля (2, …, k)-го n-разрядных сумматоров по модулю, входы переноса и входы переноса модуля n-разрядных накапливающих сумматоров по модулю соединены со входами переноса соответственно n-разрядных и (n+1)-разрядных сумматоров, а выходы переноса и выходы переноса модуля соединены соответственно с выходами переноса n-разрядных сумматоров и с (n+1)-ми разрядами информационных выходов (n+1)-разрядных сумматоров, на первый разряд вторых информационных входов которых подается сигнал логической единицы.

Сущность изобретения заключается в реализации следующего способа накопительного суммирования неотрицательных целых чисел Aj по модулю неотрицательного целого числа P, P ≥ 2. Поступающие на вход накапливающего сумматора числа Аj, где j=1, 2, 3,… такты работы устройства, 0 ≤ Аj < Р, потактово суммируются с числами Sj−1, 0 ≤ Sj−1 < Р записанными в его памяти на предыдущем такте. Пусть Sj сумма чисел (Aj + Sj−1) по произвольному модулю P на j-м такте работы устройства:

Sj = (Aj + Sj−1) mod P. (1)

Все числа A, P и S представлены в позиционной двоичной системе счисления.

A = , (2)

, (2)

P=  , (3)

, (3)

S=  , (4)

, (4)

где ai,  – коэффициенты, принимающие значение 0 или 1 в зависимости от значения числа A;

– коэффициенты, принимающие значение 0 или 1 в зависимости от значения числа A;

pi,  – коэффициенты, принимающие значение 0 или 1 в зависимости от значения модуля P;

– коэффициенты, принимающие значение 0 или 1 в зависимости от значения модуля P;

si,  – коэффициенты, принимающие значение 0 или 1 в зависимости от значения суммы S;

– коэффициенты, принимающие значение 0 или 1 в зависимости от значения суммы S;

m – количество разрядов в представлении чисел.

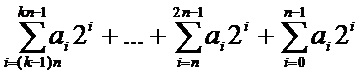

Разобьем число A в (2) на k групп по n разрядов:

A = , m = kn. (5)

, m = kn. (5)

Перепишем (5) в виде

A =Ak + … + A2 + A1. (6)

Аналогичным образом представим числа P и S:

P =Pk + … + P2 + P1. (7)

S =Sk + … + S2 + S1. (8)

Введем следующие обозначения:

S/j =Aj + Sj−1. (9)

S//j =Aj + Sj−1 − P. (10)

Тогда выражение (1) может быть переписано в следующем виде: Sj =  (11)

(11)

Операция вычитания в (10) может быть заменена операцией суммирования, если вместо прямого двоичного кода числа P использовать дополнительный двоичный код Pд:

S//j =Aj + Sj−1 − Pд. (12)

При этом разряд переноса, формируемый при выполнении (12), дополнительно может использоваться для определения условия в (11): если (Aj + Sj−1) < P, то сигнал на выходе переноса будет отсутствовать, появление сигнала на выходе переноса означает, что (Aj + Sj−1) ≥ P.

По аналогии с (6) представим числа S/j и S//j:

S/j = S/j k + … + S/j 2 + S/j 1. (13)

S//j = S//j k + … + S//j 2 + S//j 1. (14)

При этом с учетом (6) и (8) значение S/j в выражении (13) можно записать как:

S/j = Aj, i + Sj−1, i + Cinj, i−1, i=1, …,k, (15)

где Cinj, i−1 – сигнал переноса на j-ом такте из (i−1)-й группы суммирования.

Сигнал переноса, формируемый на j-ом такте в i-й группе суммирования, обозначим через Coutj, i.

С учетом (6), (7) и (8) значения S//j в выражении (14) можно записать как:

S//j = Aj, i + Sj−1, i + Pдi + CMinj, i−1, i=1, …, k, (16)

где CMinj, i−1 – сигнал переноса модуля на j-ом такте из (i−1)-й группы суммирования, Pд i – представление модуля в дополнительном коде аналогично (7).

Сигнал переноса модуля, формируемый на j-ом такте в i-й группе суммирования, обозначим через CMout j, i.

Таким образом на j-ом такте в каждой в i-й группе суммирования на основе Aj, i, Sj−1, i и Pд i с учетом Cinj, i−1 и CMinj, i−1 вычисляются значения S/j и S//j, а также формируются сигналы переноса Coutj, i и сигналы переноса модуля CMout j, i.

Соединяя группы суммирования последовательно, таким образом, что Cinj, i = Coutj, i−1 и CMinj, i = CMoutj, i −1, а также используя сигнал переноса модуля CMoutj, k в k-й группе для управления выбором S/j или S//j в соответствии с (11) получим структуру группового накапливающего суммирования по модулю с последовательным переносом. Внутри группы суммирование может выполняться по любой схеме, например, с параллельным переносом или префиксное суммирование, что позволит увеличить быстродействие устройства в целом по сравнению с прототипом. Все внутригрупповые сумматоры могут иметь одинаковую структуру, что делает предложенное решение универсальным и масштабируемым.

Краткое описание чертежей

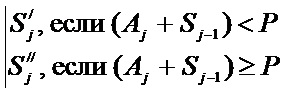

На фиг. 1 представлена схема накапливающего сумматора групповой структуры по произвольному модулю с последовательным переносом, содержащего kn-разрядных накапливающих сумматоров по модулю 1.1÷1.k, где n – разрядность i-го n-разрядного накапливающего сумматора по модулю 1.1÷1.k, i = 1, …, k, m = k·n – разрядность устройства, первые информационные входы 2 устройства, вторые информационные входы 3 устройства, выход переноса 4 устройства, тактовый вход устройства 5, вход переноса 6 устройства, вход переноса модуля 7 устройства, информационные выходы 8 устройства.

Первые информационные входы 2 устройства соединены соответствующими группами по n-разрядов с первыми информационными входами kn-разрядных накапливающих сумматоров по модулю 1.1÷1.k, вторые информационные входы 3 устройства соединены соответствующими группами по n-разрядов со вторыми информационными входами kn-разрядных накапливающих сумматоров по модулю 1.1÷1.k, информационные выходы kn-разрядных накапливающих сумматоров по модулю 1.1÷1.k соединены с соответствующими группами по n-разрядов информационных выходов 8 устройства, вход переноса 6 устройства соединен со входом переноса первого n-разрядного накапливающего сумматора по модулю 1.1, вход переноса модуля 7 устройства соединен со входом переноса модуля первого n-разрядного накапливающего сумматора по модулю 1.1, выход переноса k-го n-разрядного накапливающего сумматора по модулю 1.k соединен с выходом переноса 4 устройства, выход переноса модуля k-го n-разрядного накапливающего сумматора по модулю 1.k соединен с управляющими входами kn-разрядных накапливающих сумматоров по модулю 1.1÷1.k, выходы переноса (1, …, k−1)-го n-разрядных накапливающих сумматоров по модулю 1.1÷1.k−1 соединены со входами переноса (2, …, k)-го n-разрядных накапливающих сумматоров по модулю 1.2÷1.k, выходы переноса модуля (1, …, k−1)-го n-разрядных накапливающих сумматоров по модулю 1.1÷1.k−1 соединены со входами переноса модуля (2, …, k)-го n-разрядных накапливающих сумматоров по модулю 1.2÷1.k.

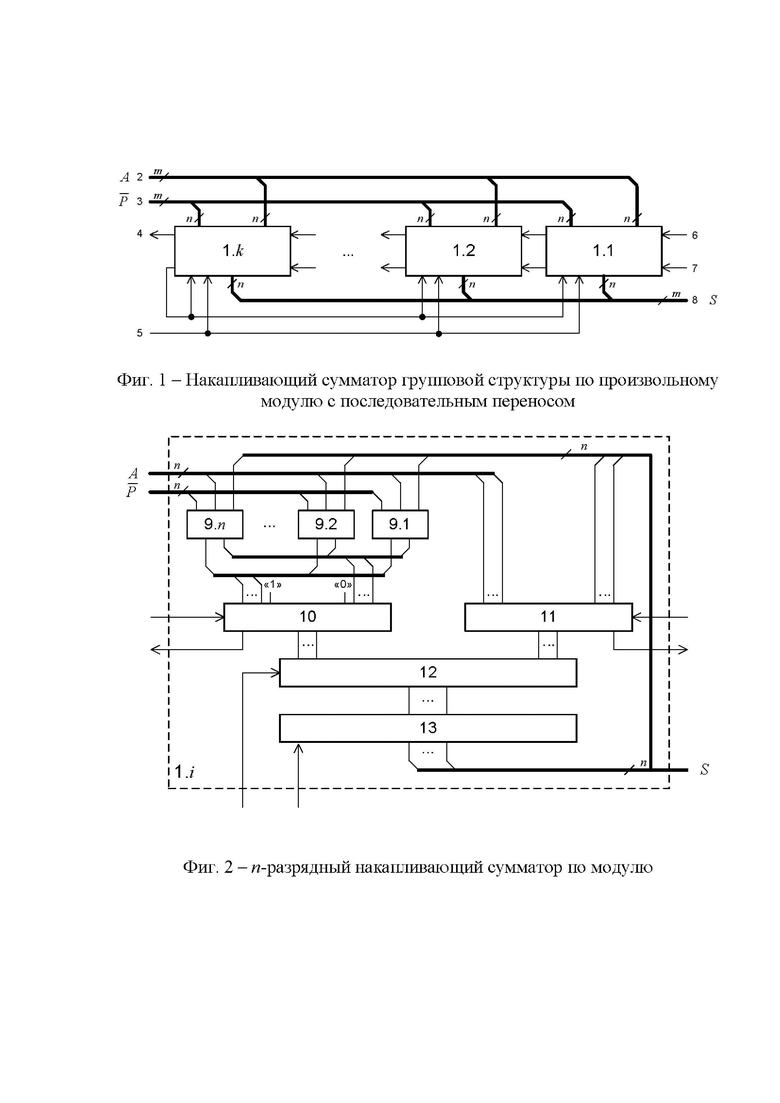

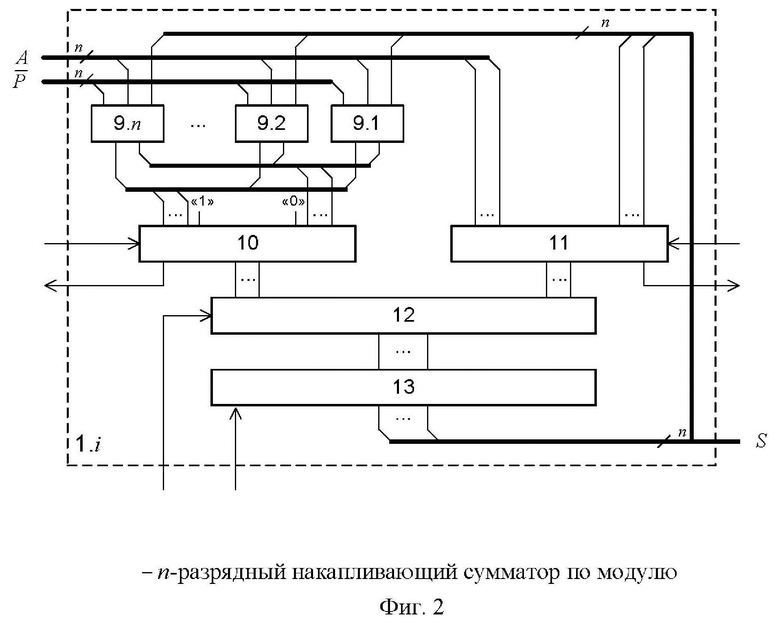

На фиг. 2 представлена схема одного из n-разрядных накапливающих сумматоров по модулю 1.1÷1.k, обозначенная как 1.i, и содержит n – полных одноразрядных сумматоров 9.1÷9.n, (n+1)-разрядный сумматор 10, n-разрядный сумматор 11, мультиплексор 12 и и n-разрядный регистр 13.

Информационные выходы n-разрядного регистра 13 соединены с информационными выходами n-разрядного накапливающего сумматора по модулю 1.i, первыми информационными входами n-разрядного сумматора 11 и поразрядно с первыми информационными входами n полных одноразрядных сумматоров 9.1÷9.n, вход синхронизации соединен с тактовым входом n-разрядного накапливающего сумматора по модулю 1.i, вход переноса n-разрядного сумматора 11 соединен со входом переноса n-разрядного накапливающего сумматора по модулю 1.i, а выход переноса соединен с выходом переноса n-разрядного накапливающего сумматора по модулю 1.i, вход переноса (n+1)-разрядного сумматора 10 соединен со входом переноса модуля n-разрядного накапливающего сумматора по модулю 1.i, (n+1)-й разряд информационных выходов (n+1)-разрядного сумматора 10 соединен с выходом переноса модуля n-разрядного накапливающего сумматора по модулю 1.i, а (1, …, n)-е разряды информационных выходов соединены со вторыми информационными входами мультиплексора 12, информационные выходы которого соединены с информационными входами n-разрядного регистра 13, с первыми информационными входами соединены информационные выходы n-разрядного сумматора 11, а управляющий вход соединен с управляющим входом n-разрядного накапливающего сумматора по модулю 1.i, первые информационные входы которого соединены со вторыми информационными входами n-разрядного сумматора 11 и поразрядно со вторыми информационными входами n полных одноразрядных сумматоров 9.1÷9.n, а вторые информационные входы соединены поразрядно со входами переноса n полных одноразрядных сумматоров 9.1÷9.n, информационные выходы которых соединены с (1, …, n)-ми разрядами первых информационных входов (n+1)-разрядного сумматора 10, а выходы переноса соединены с (2, …, n+1)-ми разрядами вторых информационных входов (n+1)-разрядного сумматора 10, на первый разряд которых подается сигнал логической единицы.

На первые информационные входы 2 накапливающего сумматора групповой структуры по произвольному модулю с последовательным переносом с каждым тактом поступают двоичные коды m-разрядных чисел Аj, где j=1, 2, 3,… такты работы устройства, на вторые информационные входы 3 поступают двоичные инверсные коды m-разрядных модулей Р. Двоичные коды m-разрядных чисел, являющихся искомой суммой Sj, снимаются с информационных выходов 8 устройства. Выход переноса 4 устройства, вход переноса 6 устройства, вход переноса модуля 7 устройства служат для наращивания групп устройства. Тактовые импульсы поступают на тактовый вход 5 устройства.

Осуществление изобретения

Накапливающий сумматор групповой структуры по произвольному модулю с последовательным переносом работает следующим образом (см. Фиг. 1).

Перед началом работы устройство находится в нулевом состоянии, все n-разрядные регистры 13 обнулены. С началом работы устройства на первые информационные входы 2 устройства подается первое m-разрядное слагаемое A, на вторые информационные входы 3 устройства подается m-разрядный инверсный код модуля P. С первых информационных входов 2 устройства m-разрядное число A подается группами по n разрядов, начиная с младших, на первые информационные входы n-разрядных накапливающих сумматоров по модулю 1.1÷1.k. Аналогичным образом модуль P подается соответственно на вторые информационные входы n-разрядных сумматоров по модулю 1.1÷1.k. На первые информационные входы полных одноразрядных сумматоров 9.1÷9.n (см. Фиг. 2) n-разрядных накапливающих сумматоров по модулю 1.1÷1.k поступают значения чисел с информационных выходов n-разрядного регистра 13, на первом такте эти значения равны нулю. На вторые информационные входы полных одноразрядных сумматоров 9.1÷9.n поступают соответствующие разряды кода числа A, а на входы переноса поступают соответствующие разряды инверсного кода модуля P. На выходах каждого из сумматоров n полных одноразрядных сумматоров 9.1÷9.n формируется сигнал частичной суммы и сигналы сквозного переноса трех чисел, поступающих на их входы. В результате на информационных выходах полных одноразрядных сумматоров 9.1÷9.n образуются поразрядные сигналы частичной суммы, а на выходах переноса образуются поразрядные сигналы сквозного переноса. Сигналы частичной суммы с информационных выходов полных одноразрядных сумматоров 9.1÷9.n поступают на (1, …, n)-й разряды первых информационных входов (n+1)-разрядного сумматора 10, на (n+1)-й разряд которого подается сигнал логического нуля. Сигналы с выходов переноса полных одноразрядных сумматоров 9.1÷9.n поступают на (2, …, (n+1))-й разряды вторых информационных входов (n+1)-разрядного сумматора 10, на первый разряд которого поступает сигнал логической единицы, преобразуя инверсный код модуля в дополнительный. На вход переноса (n+1)-разрядного сумматора 10 из предыдущей группы поступает сигнал переноса модуля с входа переноса модуля n-разрядного накапливающего сумматора по модулю 1.i. В результате на информационных выходах (n+1)-разрядного сумматора 10 образуется значение суммы в соответствии с (16) для данной группы накапливающего суммирования, причем значение, формируемое на (n+1)-м разряде информационных выходах (n+1)-разрядного сумматора 10, является сигналом переноса модуля и подается на выход переноса модуля соответствующего n-разрядного накапливающего сумматора по модулю 1,i, поступая далее в следующую группу суммирования в качестве входного сигнала переноса модуля. На вторые информационные входы мультиплексора 12 поступают значения с первых n разрядов информационных выходов (n+1)-разрядного сумматора 10. На вторые информационные входы n-разрядного сумматора 11 поступают соответствующие разряды числа A, на первые информационные входы поступают значения чисел с информационных выходов n-разрядного регистра 13, а на вход переноса из предыдущей группы суммирования поступает сигнал переноса со входа переноса n-разрядного накапливающего сумматора по модулю 1.i. На информационных выходах n-разрядного сумматора 11 образуется значение суммы в соответствии с (15) для данной группы накапливающего суммирования, а на выходе переноса образуется сигнал переноса, который подается на выход переноса соответствующего n-разрядного накапливающего сумматора по модулю 1.i, поступая далее в следующую группу суммирования в качестве входного сигнала переноса. Значение суммы с информационных выходов n-разрядного сумматора 11 поступает на первые информационные входы мультиплексора 12. Таким образом kn-разрядных накапливающих сумматоров по модулю 1.1÷1.k в каждой группе одновременно вычисляют значения слагаемых в (13) и в (14) с последовательным переносом сигналов переноса для (13) и сигналов переноса модуля для (14). В случае, если (A + B) ≥ P, то на выходе переноса модуля k-го n-разрядного накапливающего сумматора по модулю 1.k образуется сигнал логической единицы, который поступая на управляющие входы n-разрядных накапливающих сумматоров по модулю 1.1÷1.k и далее на управляющие входы мультиплексоров 12, скоммутирует с информационными выходами мультиплексоров 12 их вторые информационные входы. В результате на информационные входы n-разрядных регистров 13 поступит значение суммы в соответствии с (10), которое и будет являться искомой суммой. Под воздействием тактового импульса, поступающего с тактового входа 5 устройства на входы синхронизации n-разрядных регистров 13 данное значение запишется в этот регистр и поступит на информационные выходы 8 устройства. Если же (A + B) < P, то на выходе переноса модуля k-го n-разрядного накапливающего сумматора по модулю 1.k образуется сигнал логического нуля, под воздействием которого с информационными выходами мультиплексоров 12 окажутся скоммутированы их первые информационные входы, в результате на информационные выходы 8 устройства после воздействия тактового импульса поступит значение суммы в соответствии с (9), которая и будет являться искомой суммой в этом случае.

Оценим технический результат, достигаемый при использовании предлагаемого устройства по сравнению с устройством прототипом.

Объем оборудования прототипа Qпр можно оценить следующим выражением

Q пр =QS1+QS m+1+QSm+QMm+QRGm, (17)

где QS1 – объем оборудования полных одноразрядных сумматоров;

QS m +1 – объем оборудования (m+1)-разрядного сумматора;

QSm – объем оборудования m-разрядного сумматора;

QMm – объем оборудования m-разрядного мультиплексора;

QRGm – объем оборудования m-разрядного регистра.

Объем оборудования выразим количеством элементарных логических элементов, используемых при построении устройств. Для m-разрядного устройства прототипа

QS 1 = 5m; QMm= 3m; QRGm = 5m. (18)

Без потери общности примем QS m+1=QSm. Тогда (17) можно записать как

Q пр = 13m+2QSm. (19)

Объем оборудования предложенного решения Qиз можно оценить следующим выражением

Q из =k(QS1+QS n+1+QSn+QMn+QRGn) (20)

где QS1 – объем оборудования полных одноразрядных сумматоров;

QS n +1 – объем оборудования (n+1)-разрядного сумматора;

QSn – объем оборудования n-разрядного сумматора;

QMn – объем оборудования n-разрядного мультиплексора;

QRGn – объем оборудования n-разрядного регистра;

k – количество групп суммирования.

Для n-разрядных групп предложенного устройства

QS 1 = 5n; QMn= 3n; QRGn = 5n. (21)

Без потери общности примем QS n+1=QSn. Тогда (20) можно записать как

Q из =k(13n+2QSn), (22)

Определим выигрыш B в оборудовании как

B =Qпр / Qиз= (13m+2QSm) / k(13n+2QSn). (23)

Подставляя в (23) справочные данные, например из [5], по количеству логических элементов для многоразрядных сумматоров в префиксном исполнении для 256 разрядного устройства, выполненного в виде 32 групп по 8 разрядов, получим выигрыш в оборудовании около 1,5 раз:

B = (13⋅256+2⋅3843) / 32(13⋅8+2⋅63) = 1,496. (24)

Источники информации

1. Петренко В.И., Жук А.П., Кузьминов Ю.В. Накапливающий сумматор // Патент РФ №2544748. Опубл. 20.03.2015. Бюл. №8.

2. Петренко В.И., Бибарсов М. Р. Накапливающий сумматор // Патент РФ № 2642366. Опубл. 24.01.2018. Бюл. №3.

3. Петренко В.И., Кузьминов Ю.В. Накапливающий сумматор по модулю // Патент РФ № 2500017. Опубл. 27.11.2013.Бюл. № 33.

4. Петренко В.И., Пуйко Д. Д. Накапливающий сумматор по модулю // Патент РФ № 2791441. Опубл. 07.03.2023. Бюл. № 7.

5. Якунин А.Н., АунгМьо Сан. Сравнительный анализ характеристик двоичных многоразрядных параллельных сумматоров // Изв. вузов. Электроника. – 2018. – Т. 23. – № 3. – С. 293–303. DOI: 10.24151/1561-5405-2018-23-3-293-303.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНОГО СУММИРОВАНИЯ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2023 |

|

RU2805939C1 |

| СУММАТОР ГРУППОВОЙ СТРУКТУРЫ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ С ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ | 2024 |

|

RU2822292C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2835073C1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР ПО МОДУЛЮ | 2023 |

|

RU2804379C1 |

| Многоканальный накапливающий сумматор по произвольным модулям | 2024 |

|

RU2837596C1 |

| КОНВЕЙЕРНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР ПО ПРОИЗВОЛЬНЫМ МОДУЛЯМ | 2024 |

|

RU2823911C1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ БЫСТРОЙ СВЕРТКИ | 1991 |

|

RU2028666C1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах цифровой обработки сигналов, в криптографических приложениях и в системах связи и управления. Техническим результатом изобретения является сокращение объема оборудования при суммировании чисел большой разрядности. Для этого устройство содержит kn-разрядных накапливающих сумматоров по модулю, причем каждый из них содержит n – полных одноразрядных сумматоров, (n+1)-разрядный сумматор, n-разрядный сумматор, n-разрядный мультиплексор и n-разрядный регистр с соответствующими связями. 2 ил.

Накапливающий сумматор групповой структуры по произвольному модулю с последовательным переносом, содержащий первый n-разрядный накапливающий сумматор по модулю, где n – его разрядность, первые информационные входы устройства, вторые информационные входы устройства, информационные выходы устройства, тактовый вход устройства, соединенный с тактовым входом первого n-разрядного накапливающего сумматора по модулю, при этом младшие n разрядов первых и вторых информационных входов устройства и информационных выходов соединены соответственно с первыми и вторыми информационными входами и информационными выходами первого n-разрядного накапливающего сумматора по модулю, причем первый n-разрядный накапливающий сумматор по модулю содержит n полных одноразрядных разрядных сумматоров, (n+1)-разрядный сумматор, n-разрядный сумматор, n-разрядный мультиплексор и n-разрядный регистр, вход синхронизации которого соединен с тактовым входом первого n-разрядного накапливающего сумматора по модулю, информационные выходы соединены с информационными выходами первого n-разрядного накапливающего сумматора по модулю, первыми информационными входами n-разрядного сумматора и поразрядно с первыми информационными входами n полных одноразрядных сумматоров, первые информационные входы первого n-разрядного накапливающего сумматора по модулю соединены поразрядно со вторыми информационными входами n полных одноразрядных сумматоров и со вторыми информационными входами n-разрядного сумматора, вторые информационные входы первого n-разрядного накапливающего сумматора по модулю соединены поразрядно со входами переноса n полных одноразрядных сумматоров, информационные выходы которых соединены соответственно с (1, …, n)-ми разрядами первых информационных входов (n+1)-разрядного сумматора, на (n+1)-й разряд которых подается сигнал логического нуля, а выходы переноса n полных одноразрядных сумматоров соединены с (2, …, n+1)-ми разрядами вторых информационных входов (n+1)-разрядного сумматора, (1, …, n)-е разряды информационных выходов которого соединены со вторыми информационными входами n-разрядного мультиплексора, первые информационные входы которого соединены с информационными выходами n-разрядного сумматора, а выходы соединены с информационными входами n-разрядного регистра, отличающийся тем, что в него дополнительно введены (k-1) n-разрядных накапливающих сумматоров по модулю, где k⋅n = m – разрядность устройства, выход переноса устройства, который соединен с выходом переноса k-го n-разрядного накапливающего сумматора по модулю, при этом тактовый вход устройства соединен с таковыми входами n-разрядных накапливающих сумматоров по модулю, выход переноса модуля k-го n-разрядного накапливающего сумматора по модулю соединен с управляющими входами kn-разрядных накапливающих сумматоров по модулю, которые далее соединены с управляющими входами n-разрядных мультиплексоров, (n+1, …, m)-е разряды первых информационных входов устройства соединены группами по n-разрядов соответственно с первыми информационными входами (2, …, k)-го n-разрядных накапливающих сумматоров по модулю, (n+1, …, m)-е разряды вторых информационных входов устройства соединены группами по n-разрядов соответственно со вторыми информационными входами (2, …, k)-го n-разрядных накапливающих сумматоров по модулю, (n+1, …, m)-е разряды информационных выходов устройства соединены группами по n-разрядов соответственно с информационными выходами (2, …, k)-го n-разрядных накапливающих сумматоров по модулю, вход переноса устройства и вход переноса модуля устройства соединены соответственно с входом переноса и с входом переноса модуля первого n-разрядного накапливающего сумматора по модулю, выходы переноса и выходы переноса модуля (1, …, k−1)-го n-разрядных накапливающих сумматоров по модулю соединены соответственно со входами переноса и с входами переноса модуля (2, …, k)-го n-разрядных сумматоров по модулю, входы переноса и входы переноса модуля n-разрядных накапливающих сумматоров по модулю соединены с входами переноса соответственно n-разрядных и (n+1)-разрядных сумматоров, а выходы переноса и выходы переноса модуля соединены соответственно с выходами переноса n-разрядных сумматоров и с (n+1)-ми разрядами информационных выходов (n+1)-разрядных сумматоров, на первый разряд вторых информационных входов которых подается сигнал логической единицы.

| Накапливающий сумматор по модулю | 2022 |

|

RU2791441C1 |

| СУММАТОР ПО МОДУЛЮ P | 1992 |

|

RU2032934C1 |

| US 5418736 A1, 23.05.1995 | |||

| Накапливающий сумматор | 1988 |

|

SU1597880A1 |

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

Авторы

Даты

2025-01-14—Публикация

2024-05-17—Подача