ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники и может быть использовано в процессорах обработки сигналов и процессорах общего назначения, устройствах преобразования информации, кодирования и декодирования данных.

Известны устройства управляемого циклического сдвига (RU №2480905 С2, МПК Н03М 13/19, заявлено 08.10.2009, опубликовано 27.04.2013, Бюл. №12; Дж. Ф.Уэйкерли Проектирование цифровых устройств, том 2, М.: Постмаркет, с. 556, рис. 6.2), в которых описаны устройства для сдвига N разрядных входных данных в сторону старших разрядов на величину сдвига от 0 до N-1 задаваемую К разрядами, где К≤log2 N, содержит селекторы (мультиплексоры) с двумя входами, одним выходом и вводом управления, причем селекторы объединены в К последовательно расположенных ступеней и управляемых соответствующим разрядом кода величины сдвига, причем выходы предыдущей ступени являются входами следующей ступени.

Недостатком данных устройств являются большие аппаратные затраты для сохранения значений всех разрядов сдвигаемых операндов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятые за прототип, способ и устройство для параллельного объединения данных со сдвигом вправо (RU №2273044 С2, МПК G06F 9/315, заявлен 28.10.2002, опубликован 27.03.2006, Бюл. №9). В устройстве параллельно со сдвигом влево на (L-M) элементов данных первого операнда, имеющего первый набор из L элементов данных, сдвигают второй операнд, имеющий второй набор из L элементов данных, вправо на М элементов данных, и объединяют упомянутый сдвинутый первый набор с упомянутым сдвинутым вторым набором для получения результата, имеющего L элементов данных. В устройстве осуществляется объединение (присоединение) младших разрядов первого операнда и старших разрядов второго операнда.

Недостатком данного устройства является отсутствие средств для объединения старших разрядов первого и второго операндов с заданным количеством разрядов из операндов, а также большие аппаратные затраты на сдвиг как влево, так и вправо на полную разрядную сетку, и на формирование нулевых значений в освобождающихся при сдвиге разрядах.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задача, на решение которой направлено предлагаемое изобретение, заключается в создании устройства предназначенного для выполнения операции объединения (сцепления, соединения, присоединения) старших разрядов двух групп данных (операндов) с заданным количеством старших разрядов в каждой из групп.

Техническим результатом изобретения является обеспечение реализации объединения старших разрядов групп данных с заданным количеством разрядов из групп.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для объединения групп данных содержит первую А и вторую В внешние группы входных данных и выходную группу Q содержащие по N разрядов, третью группу из (k+1) разрядов v0, v1, …, vk внешней входной шины задания количества разрядов М из второй группы В входных данных (где М задается в диапазоне от 0 до N, k=]log2N[(большее целое)), k внутренних шин BS0, BS1, …, BS(k-1) и внутреннюю шину сдвига SB, содержащие по (N-1) разрядов и внутреннюю шину управления BU, содержащую N разрядов,

а также содержит k каскадов 10, 11, …, 1(k-1), из которых каждый i-й каскад, где i=0, 1, …, (k-1), содержит по (N-1-2i) первых групп мультиплексоров, вторую группу из (N-1) мультиплексоров 21, 22, …, 2(N-1), третью группу из N мультиплексоров 31, 32, …, 3N, дешифратор 4, элемент И с инверсным входом 5 и группу из (N-1) элементов ИЛИ 62, 63, …, 6N,

причем N разрядов первой А внешней группы входов соединены с первыми информационными входами одноименных элементов третьей группы из N мультиплексоров 31, 32, …, 3N,

k внутренних шин BS0, BS1, …, BS(k-1) являются входными шинами одноименных каскадов 10, 11, …, 1(k-1),

(N-1) разрядов второй В внешней группы входов, начиная со второго разряда до N-го разряда, являются соответствующими (N-1) разрядами нулевой внутренней шины BS0, начиная с первого разряда до (N-1)-го разряда, а также (N-1) разрядов второй В внешней группы входов, начиная со первого до (N-1)-го разряда, соединены с первыми информационными входами одноименных элементов второй группы из (N-1) мультиплексоров 21, 22, …, 2(N-1),

причем в каждом i-м каскаде из группы 10, 11, …, 1(k-1) первые информационные входы мультиплексоров соединены с одноименными разрядами соответствующей i-й внутренней шины BSi из группы BS0, BS1, …, BS(k-1), а нулевые информационные входы каждого j-го мультиплексора из первых групп мультиплексоров, где j=1, 2, …, (N-1-2i), соединены с соответствующим j+2i разрядом одноименной i-й внутренней шины BSi из группы BS0, BS1, …, BS(k-1),

кроме того в каждом i-м каскаде из группы 10, 11, …, 1(k-1) входы управления мультиплексорами соединены между собой в i-м каскаде и соединены с соответствующим одноименным i-м разрядом vi из группы v0, v1, …, v(k-1) внешней входной шины задания количества разрядов М,

причем в каждом i-м каскаде, из первых (k-1) каскадов 10, 11, …, 1(k-2), начиная с нулевого каскада до (k-2)-го каскада, выход каждого j-го мультиплексора из первых групп мультиплексоров является соответствующим одноименным j-м разрядом входной шины следующего каскада BS(i+1), в которой старшие 2i разрядов, начиная с (N-2i)-го разряда до (N-1)-го разряда, соединены с одноименными старшими 2i разрядами входной шины предыдущего i-го каскада BS(i),

кроме того выходы (N-1-2(k-1)) мультиплексоров старшего k-го каскада 1(k-1) являются соответствующими одноименными разрядами внутренней шины сдвига SB, у которой старшие 2(k-1) разрядов, начиная с 2(k-1) разряда до (N-1) разряда соединены с одноименными старшими 2i разрядами входной шины старшего каскада в BS(k-1),

причем все (N-1) разрядов внутренней шины сдвига SB соединены с нулевыми информационными входами одноименных элементов второй группы из (N-1) мультиплексоров 21, 22, …, 2(N-1), выходы которых соединены с нулевыми информационными входами одноименных элементов 31, 32, …, 3(N-1) из третьей группы мультиплексоров 31, 32, …, 3N, в которой нулевой информационный вход старшего мультиплексора 3N соединен с N-м разрядом второй группы В внешних входов,

старший vk-й разряд внешней входной шины задания количества разрядов М соединен с входами управления всех мультиплексоров второй группы 21, 22, …, 2(N-1), а также соединен с инверсным входом элемента И 5,

кроме того младшие к разрядов v0, v1, …, v(k-1) внешней входной шины задания количества разрядов М соединены с соответствующими одноименными входами дешифратора 4, у которого нулевой выход соединен с прямым входом элемента И с инверсным входом 5, выход которого является первым разрядом внутренней шины управления BU, а выходы дешифратора 4, начиная с первого выхода до (2k-1)-го выхода, соединены со вторыми входами соответствующих элементов ИЛИ из группы 62, 63, …, 6N, выходы которых являются соответствующими разрядами внутренней шины управления BU, начиная со второго разряда до N-го разряда,

при этом выходы первых (N-2) элементов ИЛИ, начиная с первого элемента 62 до (N-2)-го элемента 6(N-1), соединены с первыми входами последующих (N-2) элементов ИЛИ, начиная со второго элемента 63 до (N-1)-го элемента 6N, а первый вход первого элемента ИЛИ 62 соединен с выходом элемента И с инверсным входом 5,

причем все N разрядов шины управления BU соединены с входами управления одноименных мультиплексоров третьей группы 31, 32, …, 3N, выходы которых являются одноименными N разрядами выходной группы Q.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

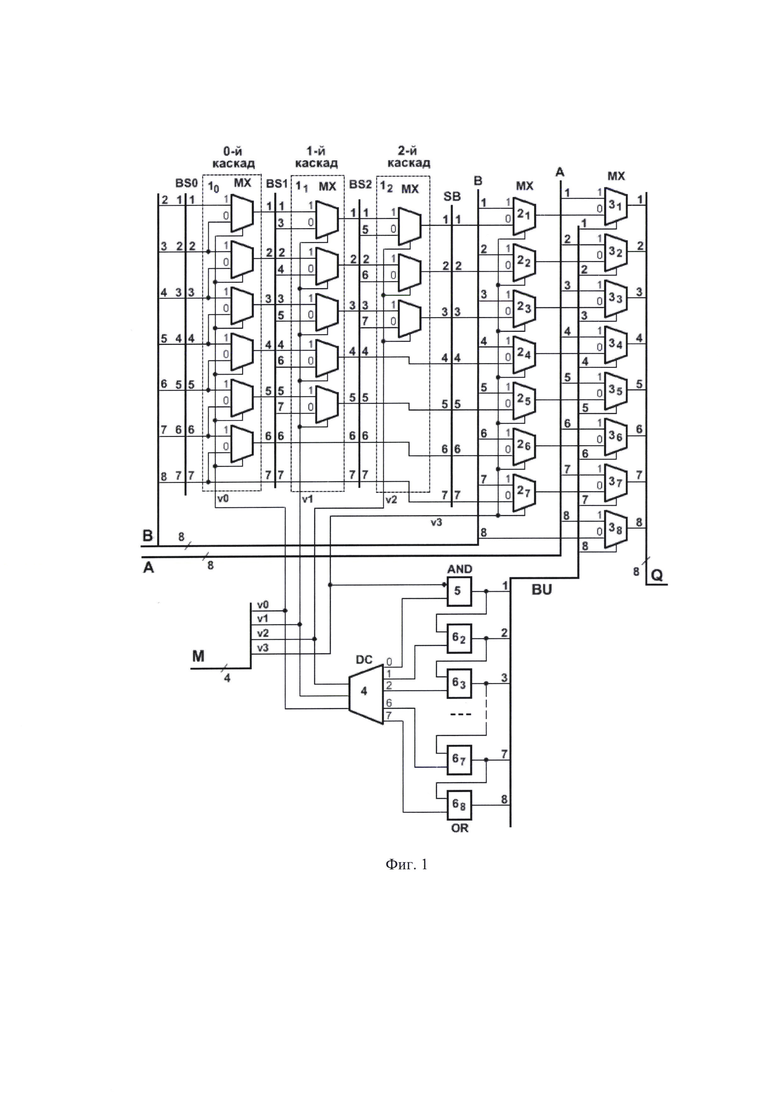

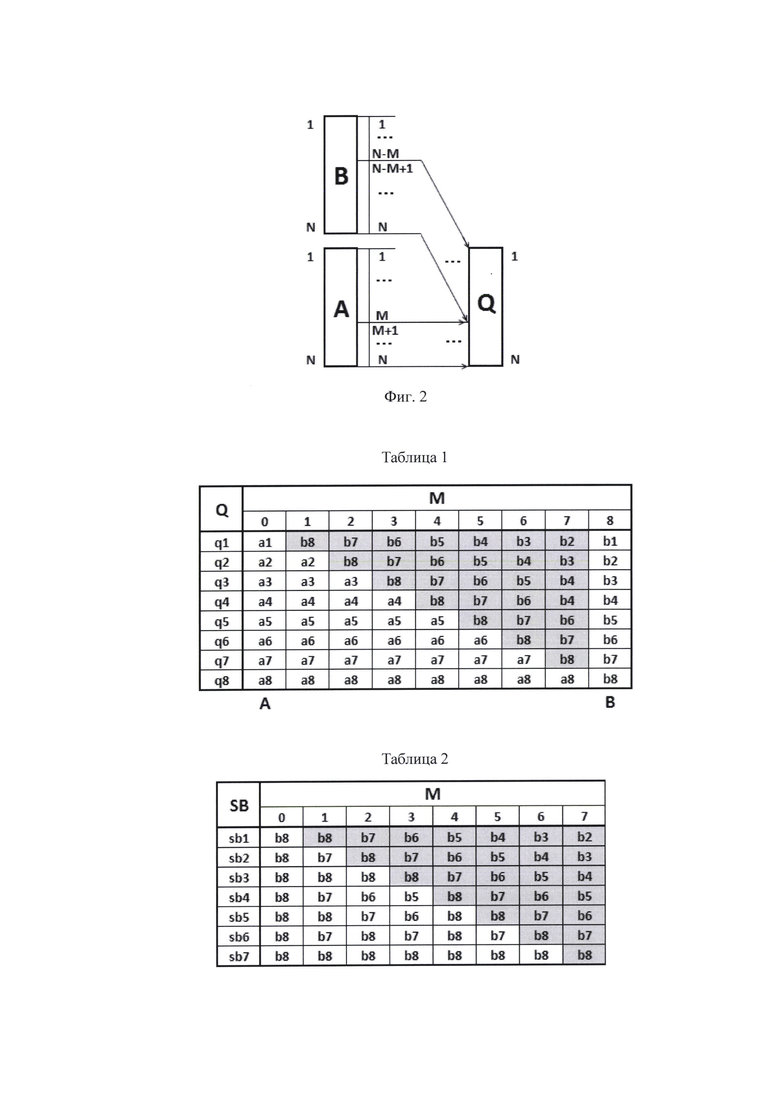

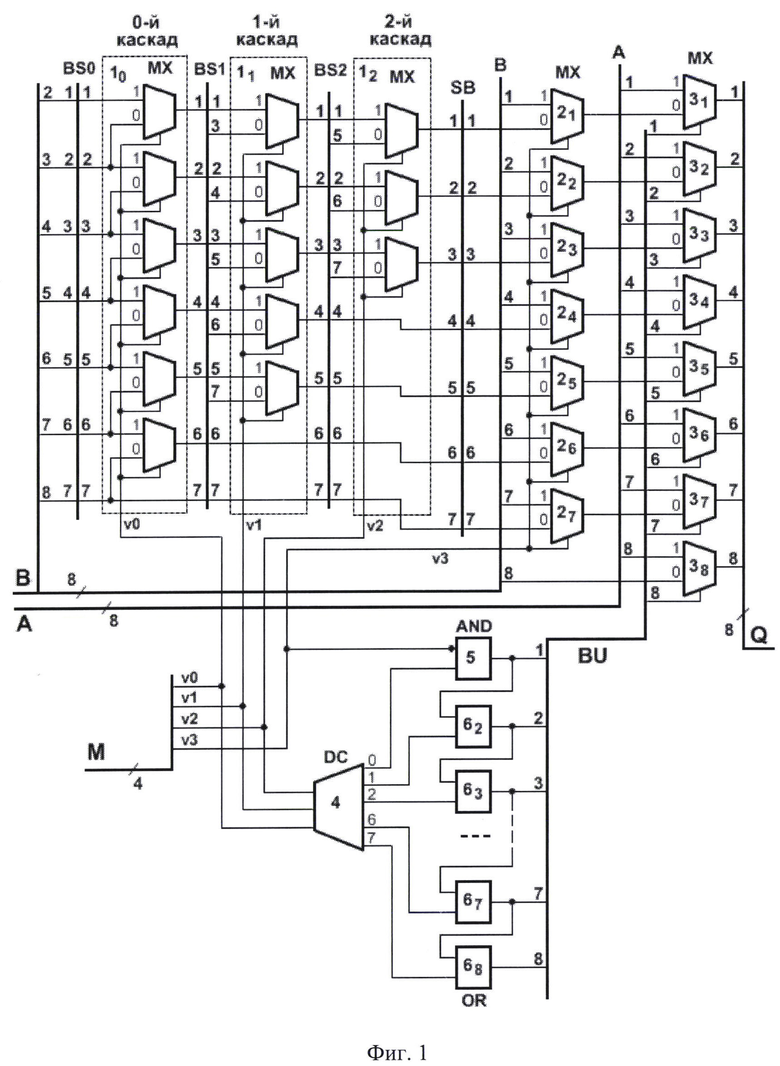

На фиг. 1 представлена схема предлагаемого устройство для объединения групп данных для входных и выходных данных разрядности N=8. На фиг. 2 приведена схема формирования N разрядов выходных данных Q.

На фиг. 1, фиг. 2 и в тексте введены следующие обозначения:

А - первая группа внешних входов, содержащая N разрядов,

В - вторая группа внешних входов, содержащая N разрядов,

Q - группа внешних выходов, содержащая N разрядов,

М - внешняя входная шина задания количества разрядов из второй группы В входных данных, где М задается в диапазоне от 0 до N,

v0, v1, …, vk - третья группа из (k+1) разрядов внешней входной шины М, где k=]log2N[(большее целое),

i - счетная переменная номера каскада, где i=0, 1, …, (k-1),

j - счетная переменная номера мультиплексора в i-м каскаде, где j=1, 2, …, (N-1-2i), BS0, BS1, …, BS(k-1) - группа из k внутренних шин BS0, BS1, …, BS(k-1), содержащих по (N-1) разрядов,

SB - внутренняя шина сдвига, содержащая (N-1) разрядов,

BU - внутренняя шина управления, содержащая N разрядов,

10, 11, …, 1(k-1) - к каскадов, содержащие первые группы мультиплексоров,

21, 22, …, 2(N-1) - вторая группа из (N-1) мультиплексоров,

31, 32, …, 3N - третья группа из N мультиплексоров,

4 - дешифратор,

5 - элемент И с инверсным входом,

62, 63, …, 6N - группа из (N-1) элементов ИЛИ.

Предлагаемое устройство для объединения групп данных содержит первую А и вторую В внешние группы входных данных и выходную группу Q содержащие по N разрядов, третью группу из (k+1) разрядов v0, v1, …, vk внешней входной шины задания количества разрядов М из второй группы В входных данных (где М задается в диапазоне от 0 до N, k=]log2N[(большее целое)), k внутренних шин BS0, BS1, …, BS(k-1) и внутреннюю шину сдвига SB, содержащие по (N-1) разрядов и внутреннюю шину управления BU, содержащую N разрядов.

Предлагаемое устройство для объединения групп данных также содержит k каскадов 10, 11, …, 1(k-1), из которых каждый i-й каскад, где i=0, 1, …, (k-1), содержит по (N-1-2i) первых групп мультиплексоров, вторую группу из (N-1) мультиплексоров 21, 22, …, 2(N-1), третью группу из N мультиплексоров 31, 32, …, 3N, дешифратор 4, элемент И с инверсным входом 5 и группу из (N-1) элементов ИЛИ 62, 63, …, 6N.

Причем N разрядов первой А внешней группы входов соединены с первыми информационными входами одноименных элементов третьей группы из N мультиплексоров 31, 32, …, 3N. При этом к внутренних шин BS0, BS1, …, BS(k-1) являются входными шинами одноименных каскадов 10, 11, …, 1(k-1).

(N-1) разрядов второй В внешней группы входов, начиная со второго разряда до N-го разряда, являются соответствующими (N-1) разрядами нулевой внутренней шины BS0, начиная с первого разряда до (N-1)-го разряда. Кроме того (N-1) разрядов второй В внешней группы входов, начиная со первого до (N-1)-го разряда, соединены с первыми информационными входами одноименных элементов второй группы из (N-1) мультиплексоров 21, 22, …, 2(N-1).

Причем в каждом i-м каскаде из группы 10, 11, …, 1(k-1) первые информационные входы мультиплексоров соединены с одноименными разрядами соответствующей i-й внутренней шины BSi из группы BS0, BS1, …, BS(k-1), а нулевые информационные входы каждого j-го мультиплексора из первых групп мультиплексоров, где j=1, 2, …, (N-1-2i), соединены с соответствующим j+2i разрядом одноименной i-й внутренней шины BSi из группы BS0, BS1, …, BS(k-1).

Кроме того в каждом i-м каскаде из группы 10, 11, …, 1(k-1) входы управления мультиплексорами соединены между собой в i-м каскаде и соединены с соответствующим одноименным i-м разрядом vi из группы v0, v1, …, v(k-1) внешней входной шины задания количества разрядов М.

Причем в каждом i-м каскаде, из первых (k-1) каскадов 10, 11, …, 1(k-2), начиная с нулевого каскада до (k-2)-го каскада, выход каждого j-го мультиплексора из первых групп мультиплексоров является соответствующим одноименным j-м разрядом входной шины следующего каскада BS(i+1), в которой старшие 2i разрядов, начиная с (N-2i)-го разряда до (N-1)-го разряда, соединены с одноименными старшими 2i разрядами входной шины предыдущего i-го каскада BS(i).

Кроме того выходы (N-1-2(k-1)) мультиплексоров старшего k-го каскада 1(k-1) являются соответствующими одноименными разрядами внутренней шины сдвига SB, у которой старшие 2(k-1) разрядов, начиная с 2(k-1) разряда до (N-1) разряда соединены с одноименными старшими 2i разрядами входной шины старшего каскада в BS(k-1).

Причем все (N-1) разрядов внутренней шины сдвига SB соединены с нулевыми информационными входами одноименных элементов второй группы из (N-1) мультиплексоров 21, 22, …, 2(N-1), выходы которых соединены с нулевыми информационными входами одноименных элементов 31, 32, …, 3(N-1) из третьей группы мультиплексоров 31, 32, …, 3N, в которой нулевой информационный вход старшего мультиплексора 3N соединен с N-м разрядом второй группы В внешних входов.

Старший vk-й разряд внешней входной шины задания количества разрядов М соединен с входами управления всех мультиплексоров второй группы 21, 22, …, 2(N-1), а также соединен с инверсным входом элемента И 5.

Кроме того младшие к разрядов v0, v1, …, v(k-1) внешней входной шины задания количества разрядов М соединены с соответствующими одноименными входами дешифратора 4, у которого нулевой выход соединен с прямым входом элемента И с инверсным входом 5, выход которого является первым разрядом внутренней шины управления BU, а выходы дешифратора 4, начиная с первого выхода до (2k-1)-го выхода, соединены со вторыми входами соответствующих элементов ИЛИ из группы 62, 63, …, 6N, выходы которых являются соответствующими разрядами внутренней шины управления BU, начиная со второго разряда до N-го разряда.

При этом выходы первых (N-2) элементов ИЛИ, начиная с первого элемента 62 до (N-2)-го элемента 6(N-1), соединены с первыми входами последующих (N-2) элементов ИЛИ, начиная со второго элемента 63 до (N-1)-го элемента 6N, а первый вход первого элемента ИЛИ 62 соединен с выходом элемента И с инверсным входом 5.

Причем все N разрядов шины управления BU соединены с входами управления одноименных мультиплексоров третьей группы 31, 32, …, 3N, выходы которых являются одноименными N разрядами выходной группы Q.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем. Устройство предназначено для объединения (соединения) старших разрядов первой А и второй В групп входных данных (операндов), содержащих по N разрядов. Количество старших разрядов передаваемых из второй группы В задается на внешней входной шине М. При этом из первой группы А передается (N-М) старших разрядов.

На фиг. 2 приведена схема формирования N разрядов выходных данных Q. При этом в (N-M) старшие разряды группы внешних выходов Q передаются старшие разряды первой группы внешних входов А, начиная с (М+1)-го разряда до N-го разряда, а в младшие М разрядов передаются старшие М разрядов второй группы внешних входов В, начиная с (N-M+1)-го разряда до N-го разряда.

В таблице 1 приведен пример формирования выходных данных при N=8 и задании числа разрядов М из второй группы B в диапазоне от 0 до N=8. Например, при М=3 на выходные пять старших разрядов q8-q4 выходной группы Q передаются пять старших разрядов а8-а4 первой группы А, а на три младшие разряды q3-q1 выходной группы Q передаются три старшие разряда b8-b6 второй группы В. При этом при М=0 на группу выходов Q передаются все разряды a8-a1 первой группы входов А, а при М=8 передаются все разряды b8-b1 второй группы входов В.

В каскадах 10, 11, …, 1(k-1) первых групп мультиплексоров осуществляется передача (сдвиг) М старших разрядов второй группы В, начиная со старшего разряда b8, в младшие разряды, начиная с первого разряда, внутренних шин BS0, BS1, …, BS(k-1), содержащие по (N-1) разрядов. При этом в каждом i-м каскаде, где i=0, 1, …, (k-1) - номер каскада, выполняется передача данных без сдвига (при vi=1) или со сдвигом на 2i разрядов (при vi=0) старших разрядов в младшие. На входы 0-го каскада 10 с внутренней шины BS0 поступают (N-1) разрядов второй группы внешних входов В, начиная со второго разряда b2 до N-го разряда.

Выходы старшего каскада 1(k-1) передаются на разряды внутренней шины сдвига SB, с которой далее поступают на нулевые информационные входы одноименных элементов второй группы из (N-1) мультиплексоров 21, 22, …, 2(N-1). В таблице 2 приведены связи между разрядами внутренней шины сдвига SB и разрядами второй группы внешних входов В для при N=8 и задании числа М в диапазоне от 0 до N=8.

Во второй группе из (N-1) мультиплексоров 21, 22, …, 2(N-1) на выходы передаются все разряды b8-b1 второй группы внешних входов В (при vk=1) или сдвинутые М старших разрядов второй группы внешних входов В (при vk=0) с внутренней шины сдвига SB, которые передаются в младшие разряды.

Одновременно на входы дешифратора 4 поступает k младших разрядов v0, v1, …, v(k-1) с шины М задания количества разрядов второй группы В входных данных. На выходах дешифратора 4 формируются унитарные коды «1 из N». Единичное значение, установленное на одном из выходов дешифратора 4, передается на соответствующий вход элемента И с инверсным входом 5 или группы из (N-1) элементов ИЛИ 62, 63, …, 6N и далее последовательно передается по цепочке элементов ИЛИ в сторону старших разрядов. При этом на внутренней шине управления BU, устанавливается упорядоченная последовательность единичных значений (унитарный позиционный ряд 11…100..0), начиная с М-го разряда до старшего N-го разряда. Далее значения N разрядов с внутренней шины управления BU поступают на входы управления одноименных мультиплексоров третьей группы 31, 32, …, 3N. При этом при нулевых значениях разрядов шины управления BU на выходы передаются значения сдвинутых М старших разрядов второй группы В входных данных, при единичном значении разрядов шины управления BU на выходы передаются значения (N-M) старших разрядов первой группы входных данных А.

Далее значения с выходов мультиплексоров третьей группы 31, 32, …, 3N. передается на группу внешних выходов Q. Таким образом, на выходах устройства осуществляется объединение (соединение) (N-M) старших разрядов первой группы входных данных А и М старших разрядов второй группы В входных данных (таблица 2).

Предлагаемое устройство работает следующим образом.

На внешние входы устройства подаются по N разрядов первой А и второй В групп входных данных (операндов). Одновременно на (k+1) разрядах v0, v1, …, vk внешней входной шины М задается двоичный код количества разрядов из второй выходной группы В.

Далее (N-1) разрядов второй В группы входных данных, начиная со второго разряда до N-го разряда, передаются на соответствующие разряды, начиная с первого разряда до (N-1)-го разряда, внутренней шины BS0 и далее на входы 0-го каскада 10 первых групп мультиплексоров. Например, для N=8 на внутреннюю шину BS0 передаются разряды b8-b2 второй В группы входных данных. Далее в 0-м каскаде может выполниться сдвиг на 1 разряд (20) в сторону младших разрядов (при v0=0) или передача без сдвига (при v0=1) с внутренней шины BS0 и результат с выходов мультиплексоров передается на внутреннюю шину BS1, которая является входной шиной для первого 11 каскада.

Далее в первом каскаде может выполниться сдвиг на два (21) разряда или передача без сдвига с внутренней шины BS1 в зависимости от значения разряда v1 и результат с выходов мультиплексоров передается на следующую внутреннюю шину для второго каскада BS2. Аналогично в следующих каскадах 1i возможно осуществление сдвига на 2i разрядов или передача без сдвига с внутренней шины BSi зависимости от значения разряда vi.

Результат сдвига разрядов второй В группы входных данных на заданные М разрядов передается на внутреннюю шину сдвига SB. В таблице 2 приведены результаты сдвига при N=8 и задании числа М в диапазоне от 0 до N=8. Например, при М=3 в младшие (sb3, sb2, sb1) разряды шины сдвига SB передаются три старшие разряда b8-b6 второй В группы входных данных, а также в старшие разряды (sb7-sb4) соответствующие значения разрядов (b8-b5) группы В. При М=0 на все разряды шины сдвига SB передается значение старшего разряда b8. В отличии от логического сдвига в разрядах с (М+1)-го до (N-1)-го не формируются нулевые значения или не передаются младшие разряды второй В группы как при циклическом сдвиге, так как разряды с (М+1)-го до (N-1)-го с шины сдвига SB не передаются на выходы устройства.

При нулевом значении старшего разряда vk=0 шины М значения разрядов с шины сдвига SB, а при единичном значении vk=1 значения разрядов b7-b1 второй группы В, передаются через вторую группу 21, 22, …, 2(N-1) из (N-1) мультиплексоров, на нулевые информационные входы (N-1) мультиплексоров из третьей группы 31, 32, …, 3(N-1), а также на нулевой информационный вход старшего мультиплексора 3N передается значение старшего N-го разряда второй группы В внешних входов.

Одновременно в зависимости от значений к младших разрядов v0, v1, …, v(k-1) с шины М задания количества разрядов второй группы В входных данных на выходах дешифратора 4 формируются унитарные коды «1 из N». При этом единичное значение формируется только на одном М-ом выходе дешифратора 4, которое далее передается на соответствующий вход элемента И с инверсным входом 5 или группы из (N-1) элементов ИЛИ 62, 63, …, 6N. Далее единичное значение последовательно передается по цепочке элементов ИЛИ в сторону старших разрядов и на внутренней шине управления BU устанавливается упорядоченная последовательность единичных значений (унитарный позиционный ряд 11…100..0), начиная с (М+1)-го разряда до старшего N-го разряда.

Далее значения N разрядов с внутренней шины управления BU поступают на входы управления одноименных мультиплексоров третьей группы 31, 32, …, 3N. При этом при нулевых значениях разрядов шины управления BU на выходы мультиплексоров передаются сдвинутые М старших разрядов bN, b(N-1), …, b(N-M+1) второй группы В входных данных, расположенные в соответствующих М младших разрядах М, (М-1), …, 1, а при единичном значении разрядов шины управления BU на выходы мультиплексоров N, (N-1), …, (М+1) передаются (N-M) старших разрядов aN, a(N-1), …, а(М+1) первой группы входных данных А.

При единичном значении старшего разряда vk=1 (v3=1 при N=8 и М=8) шины М значения разрядов с шины В второй группы входных данных через вторую группу 21, 22, …, 2(N-1) из (N-1) мультиплексоров на нулевые информационные входы мультиплексоров третьей группы 31, 32, …, 3N будут переданы значения всех N разрядов bN-b1. Одновременно при этом нулевое значение будет установлено на выходе элемента И с инверсным входом 5, а также нулевые значения на выходах с первого до (N-1)-го дешифратора 4. Поэтому нулевые значения будут установлены на всех разрядах шины управления BU и далее значение всех разрядов bN-b1 второй группы В входных данных передаются на выходы мультиплексоров третьей группы 31, 32, …, 3N, которые передаются на одноименные N разрядов выходной группы Q (в таблице 2 правый столбец при М=8).

При нулевых значениях всех разрядов (k+1) разрядов v0, v1, …, vk с шины М задания количества разрядов второй группы В входных данных единичное значение будет установлено на нулевом выходе дешифратора 4, по которому далее единичные значения формируются на выходах элемента И с инверсным входом 5 и группы из (N-1) элементов ИЛИ 62, 63, …, 6N и далее единичное значение будет установлено на всех разрядах шины управления BU, по которым с единичных информационных входов мультиплексоров третьей группы 31, 32, …, 3N все N разрядов aN-a1 первой группы А входных данных передаются на выходы мультиплексоров третьей группы 31, 32, …, 3N, которые передаются на одноименные N разрядов выходной группы Q (в таблице 2 левый столбец при М=0).

Таким образом, в предлагаемом устройстве на N разрядов выходной группы Q в старшие разряды передаются (N-M) старших разрядов aN-a(M+1) первой группы А входных данных, которые объединяются (соединяются) с М старшими разрядами bN-b(N-M+1) второй группы В входных данных, которые передаются в соответствующие М младшие разряды выходной группы Q.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство для объединения групп данных обладает регулярностью узлов и связей и соответствует заявляемому техническому результату - возможность объединения старших разрядов первой А и второй В групп данных с заданным количеством разрядов из групп.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СДВИГА ГРУПП ДАННЫХ | 2018 |

|

RU2674934C1 |

| КРУГОВОЙ АРБИТР ДИСПЕТЧЕРА ЗАДАЧ | 2022 |

|

RU2785771C1 |

| УСТРОЙСТВО ДЛЯ КОМПРЕССИИ ДАННЫХ | 2017 |

|

RU2672625C1 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРАНИЦ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ | 2021 |

|

RU2759002C1 |

| ДВУХПОРОГОВЫЙ КОМПАРАТОР ДИАПАЗОНА ДВОИЧНЫХ БИТ | 2020 |

|

RU2758205C1 |

| АРБИТР ДИСПЕТЧЕРА ЗАДАЧ КАСКАДНОЙ СТРУКТУРЫ | 2022 |

|

RU2799990C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРАНИЦ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ | 2019 |

|

RU2717934C1 |

| УСТРОЙСТВО ДЛЯ КОМПРЕССИИ ДАННЫХ | 2019 |

|

RU2710987C1 |

| УСТРОЙСТВО ПИРАМИДАЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2019 |

|

RU2703335C1 |

| УСТРОЙСТВО КАСКАДНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ, ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА И МАКСИМАЛЬНЫХ ГРУПП | 2019 |

|

RU2701709C1 |

Изобретение относится к области вычислительной техники. Технический результат изобретения заключается в обеспечении реализации объединения старших разрядов групп данных с заданным количеством разрядов из групп. Указанный результат достигается за счет того, что устройство содержит первую А и вторую В внешние группы входных данных и выходную группу Q, содержащие по N разрядов, третью группу из (k+1) разрядов v0, v1, …, vk внешней входной шины задания количества разрядов М из второй группы В входных данных (где М задается в диапазоне от 0 до N, k=]log2N[(большее целое)), k внутренних шин BS0, BS1, …, BS(k-1) и внутреннюю шину сдвига SB, содержащие по (N-1) разрядов, и внутреннюю шину управления BU, содержащую N разрядов, а также содержит k каскадов 10, 11, …, 1(k-1), из которых каждый i-й каскад, где i=0, 1, …, (k-1), содержит по (N-1-2i) первых групп мультиплексоров, вторую группу из (N-1) мультиплексоров 21, 22, …, 2(N-1), третью группу из N мультиплексоров 31, 32, …, 3N, дешифратор 4, элемент И с инверсным входом 5 и группу из (N-1) элементов ИЛИ 62, 63, …, 6N. 2 табл., 2 ил.

Устройство для объединения групп данных содержит первую А и вторую В внешние группы входных данных и выходную группу Q, содержащие по N разрядов, третью группу из (k+1) разрядов v0, v1, …, vk внешней входной шины задания количества разрядов М из второй группы В входных данных (где М задается в диапазоне от 0 до N, k=log2N[(большее целое))], k внутренних шин BS0, BS1, …, BS(k-1) и внутреннюю шину сдвига SB, содержащие по (N-1) разрядов, и внутреннюю шину управления BU, содержащую N разрядов,

а также содержит k каскадов 10, 11, …, 1(k-1), из которых каждый i-й каскад, где i=0, 1, …, (k-1), содержит по (N-1-2i) первых групп мультиплексоров, вторую группу из (N-1) мультиплексоров 21, 22, …, 2(N-1), третью группу из N мультиплексоров 31, 32, …, 3N, дешифратор 4, элемент И с инверсным входом 5 и группу из (N-1) элементов ИЛИ 62, 63, …, 6N,

причем N разрядов первой А внешней группы входов соединены с первыми информационными входами одноименных элементов третьей группы из N мультиплексоров 31, 32, …, 3N,

k внутренних шин BS0, BS1, …, BS(k-1) являются входными шинами одноименных каскадов 10, 11, …, 1(k-1),

(N-1) разрядов второй В внешней группы входов, начиная со второго разряда до N-го разряда, являются соответствующими (N-1) разрядами нулевой внутренней шины BS0, начиная с первого разряда до (N-1)-го разряда, а также (N-1) разрядов второй В внешней группы входов, начиная со первого до (N-1)-го разряда, соединены с первыми информационными входами одноименных элементов второй группы из (N-1) мультиплексоров 21, 22, …, 2(N-1),

причем в каждом i-м каскаде из группы 10, 11, …, 1(k-1) первые информационные входы мультиплексоров соединены с одноименными разрядами соответствующей i-й внутренней шины BSi из группы BS0, BS1, …, BS(k-1), а нулевые информационные входы каждого j-го мультиплексора из первых групп мультиплексоров, где j=1, 2, …, (N-1-2i), соединены с соответствующим j+2i разрядом одноименной i-й внутренней шины BSi из группы BS0, BS1, …, BS(k-1),

кроме того, в каждом i-м каскаде из группы 10, 11, …, 1(k-1) входы управления мультиплексорами соединены между собой в i-м каскаде и соединены с соответствующим одноименным i-м разрядом vi из группы v0, v1, …, v(k-1) внешней входной шины задания количества разрядов М,

причем в каждом i-м каскаде из первых (k-1) каскадов 10, 11, …, 1(k-2), начиная с нулевого каскада до (k-2)-го каскада, выход каждого j-го мультиплексора из первых групп мультиплексоров является соответствующим одноименным j-м разрядом входной шины следующего каскада BS(i+1), в которой старшие 2i разрядов, начиная с (N-2i)-го разряда до (N-1)-го разряда, соединены с одноименными старшими 2i разрядами входной шины предыдущего i-го каскада BS(i),

кроме того, выходы (N-1-2(k-1)) мультиплексоров старшего k-го каскада 1(k-1) являются соответствующими одноименными разрядами внутренней шины сдвига SB, у которой старшие 2(k-1) разрядов, начиная с 2(k-1) разряда до (N-1) разряда, соединены с одноименными старшими 2i разрядами входной шины старшего каскада в BS(k-1),

причем все (N-1) разрядов внутренней шины сдвига SB соединены с нулевыми информационными входами одноименных элементов второй группы из (N-1) мультиплексоров 21, 22, …, 2(N-1), выходы которых соединены с нулевыми информационными входами одноименных элементов 31, 32, …, 3(N-1) из третьей группы мультиплексоров 31, 32, …, 3N, в которой нулевой информационный вход старшего мультиплексора 3N соединен с N-м разрядом второй группы В внешних входов,

старший vk-й разряд внешней входной шины задания количества разрядов М соединен с входами управления всех мультиплексоров второй группы 21, 22, …, 2(N-1), а также соединен с инверсным входом элемента И 5,

кроме того, младшие k разрядов v0, v1, …, v(k-1) внешней входной шины задания количества разрядов М соединены с соответствующими одноименными входами дешифратора 4, у которого нулевой выход соединен с прямым входом элемента И с инверсным входом 5, выход которого является первым разрядом внутренней шины управления BU, а выходы дешифратора 4, начиная с первого выхода до (2k-1)-го выхода, соединены со вторыми входами соответствующих элементов ИЛИ из группы 62, 63, …, 6N, выходы которых являются соответствующими разрядами внутренней шины управления BU, начиная со второго разряда до N-го разряда,

при этом выходы первых (N-2) элементов ИЛИ, начиная с первого элемента 62 до (N-2)-го элемента 6(N-1), соединены с первыми входами последующих (N-2) элементов ИЛИ, начиная со второго элемента 63 до (N-1)-го элемента 6N, а первый вход первого элемента ИЛИ 62 соединен с выходом элемента И с инверсным входом 5,

причем все N разрядов шины управления BU соединены с входами управления одноименных мультиплексоров третьей группы 31, 32, …, 3N, выходы которых являются одноименными N разрядами выходной группы Q.

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2728957C1 |

| US 7584233 B2, 01.09.2009 | |||

| WO 2017131579 A1, 03.08.2017 | |||

| УСТРОЙСТВО ДЛЯ РАСПАКОВКИ ДАННЫХ | 2019 |

|

RU2729509C1 |

| УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГО ТИПА ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680759C1 |

Авторы

Даты

2022-12-13—Публикация

2022-03-09—Подача