Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения средств автоматики и функциональных узлов систем управления, а также для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел.

Известны система и способ подсчета начальных нулевых разрядов и подсчета начальных единичных разрядов в цифровом процессоре сигналов (RU №2409837 С2, МПК G06F 7/74, заявлен 27.07.2006, опубликовано 20.01.2011, Бюл. №2) в котором определяется количество разрядов для различных размеров слов данных. В устройстве проводится расширение входных данных знаком до временного шестидесятичетырехразрядного слова данных. При подсчете нулевых разрядов проводится инвертирование разрядов слова. Для подсчета начальных разрядов используется двоичный счетчик.

Недостатком данного устройства является низкое быстродействие, а также подсчет только начальных нулевых разрядов и начальных единичных разрядов в цифровом сигнале.

Известно устройство для определения количества единиц в упорядоченном двоичном числе (RU №2522875, МПК Н03К 21/12, заявлено 24.05.2012, опубликовано 20.07.2014, Бюл. №20), содержащее буферы с тремя состояниями с прямым и инверсным входами разрешения, n разрядов входного двоичного числа, (k+1) разрядов выходного двоичного кода (k=[log2n] меньшее целое), причем буферы с тремя состояниями объединены в пирамидальную структуру, состоящую из (m-1) ступеней (m=]log2n[большее целое), и в выходной блок, содержащий k буферов с тремя состояниями с инверсным входом разрешения и k буферов с тремя состояниями с прямым входом разрешения, при этом каждая i-я ступень (i=1, …, (m-1)) содержит (2i-1) буферов с тремя состояниями с инверсным входом разрешения и 2i-1 буферов с тремя состояниями с прямым входом разрешения.

Недостатком данного устройства является определение количества единиц только в одной группе упорядоченного двоичного числа, а не в группах нулевых и единичных разрядов.

Известен сумматор для последовательных операндов (Угрюмов Е.П. Цифровая схемотехника: учеб. Пособие для вузов. - СПб.: БХВ-Петребург, 2010. - 816 с. Стр. 119, рис. 2.33) содержащий одноразрядный сумматор, D-триггер запоминания переноса с входом установки в нулевое состояние, два сдвигающих регистра слагаемых и сдвиговый регистр суммы, причем регистры тактируются синхроимпульсами СИ. Сумматор поочередно обрабатывает разряд за разрядом, начиная с младших разрядов, последовательно поступающие разряды слагаемых и вырабатывает значение суммы S, поступающее на вход сдвигового регистра суммы, и перенос СО в следующий старший разряд, который запоминается на D-триггере и на следующем такте поступает на вход CI переноса сумматора.

Недостатками данного устройства является поразрядное суммирование слагаемых и невозможность определения в группах данных количества единиц и количества нулей.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство для определения количества единиц (нулей) в двоичном числе (RU №2446442, МПК G06F 7/50, Н03К 21/00, заявлено 11.04.2011, опубликовано 27.03.2012, Бюл. №9), содержащее блок управляемой инверсии, состоящий из n-элементов «ИСКЛЮЧАЮЩЕЕ ИЛИ» (n - количество разрядов входного числа), элементы ИЛИ и модули, состоящие из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента И, которые объединены в группы, состоящие из ярусов, и объединены в k-каскадов (k=]log2n[), так, что каждый i-й каскад содержит g(i)=n/2i групп (i=1, …, k), каждая группа i-го каскада разделена на j ярусов (j=1, …, i), при этом первый ярус каждой группы i-го каскада содержит i модулей, а каждый j-й ярус каждой группы i-го каскада (j=2, …, i,) содержит (i-j) модулей и элемент «ИЛИ».

Недостатком данного устройства является определение только общего количества единиц (нулей) в двоичном числе, а не по группам нулевых и единичных разрядов.

К причинам, препятствующим достижению указанного ниже технического результата, относится отсутствие средств для выделения групп и определения количества нулевых и единичных разрядов в группах, и определение общего количества групп.

Техническим результатом изобретения является расширение функциональных возможностей в части возможности выявления групп единичных и нулевых бит, определение общего количества и по группам единичных и нулевых бит, определение соотношения разности между количеством единичных и нулевых бит во входной последовательности данных размерностью N.

Указанный технический результат при осуществлении изобретения достигается тем, что устройство содержит

внешний вход данных DI, группу внешних выходов данных QO, группу внешних выходов количества групп QG, группу внешних выходов количества нулей QZ, группу внешних выходов количества единиц QU, группу внешних выходов «разность единиц и нулей» QZU,

первый RS-триггер пуска-останова TSS 1, блок детектора единиц и нулей 2, который состоит из первого 3 и второго 4 элементов И с одним инверсным входом, элемента ИЛИ 5 и второго D-триггера управления битами TU 6, третий D-триггер разрешения счета групп ТСЕ 7, третий элемент И 8, первый счетчик групп CG 9, второй счетчик бит СВ 10, выходной буфер ОВ 11, четвертый 12, пятый 13 и шестой 14 элементы И, третий счетчик нулей CZ 15, четвертый счетчик единиц CU 16, пятый реверсивный счетчик нулей-единиц CZU 17 и блок преобразователя кода разности 18, который содержит группу из (М-2) элементов ИЛИ 19, группу из (М-1) элементов И 20 и группу из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 21, где M=[log2N]+1 (меньшее целое), а N - размерность входной последовательности данных, причем первый счетчик групп CG 9, второй счетчик бит СВ 10, выходной буфер ОВ 11, третий счетчик нулей CZ 15 и четвертый счетчик единиц CU 16 имеют разрядность М, а пятый реверсивный счетчик нулей-единиц CZU 17 имеет разрядность (М+1),

а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внешняя шина управления обменом ЕО, внешние флаг готовности результата FE, флаг «Буфер заполнен» FF, флаг «Буфер пуст» FZ и флаг «нулей больше единиц» F01, и внутренняя шина «разность единиц и нулей» ZU,

причем внешний вход асинхронной установки в нулевое состояние CLR соединен с соответствующим входом асинхронной установки в нулевое состояние CLR первого RS-триггера пуска-останова TSS 1,

внешний тактовый вход устройства С соединен с входами синхронизации первого 1 RS-триггера пуска-останова TSS, второго D-триггера управления битами TU 6, третьего D-триггера разрешения счета групп ТСЕ 7, первого счетчика групп CG 9, второго счетчика бит СВ 10, выходного буфера ОВ 11, третьего счетчика нулей CZ 15, четвертого счетчика единиц CU 16 и пятого реверсивного счетчика нулей-единиц CZU 17,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1 и входами R синхронной установки в нулевое состояние второго D-триггера управления битами TU 6, третьего D-триггера разрешения счета групп ТСЕ 7, первого счетчика групп CG 9, второго счетчика бит СВ 10, выходного буфера ОВ 11, третьего счетчика нулей CZ 15, четвертого счетчика единиц CU 16 и пятого реверсивного счетчика нулей-единиц CZU 17,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1 и первым входом элемента ИЛИ 5 в блоке детектора единиц и нулей 2,

причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с первыми входами первого 3 и второго 4 элементов И с одним инверсным входом в блоке детектора единиц и нулей 2, с входом СЕ разрешения работы второго счетчика бит СВ 10 и с первыми входами четвертого 12, пятого 13 и шестого 14 элементов И, а инверсный выход первого RS-триггера пуска-останова TSS 1 является внешним флагом готовности результата FE,

в блоке детектора единиц и нулей 2 внешний вход данных DI соединен со вторым прямым входом первого 3 элемента И и третьим инверсным входом второго 4 элемента И, выходы которых соединены соответственно со вторым и третьим входами элемента ИЛИ 5, выход LE которого соединен с входом СЕ разрешения работы второго D-триггера управления битами TU 6, у которого инверсный выход соединен с информационным D-входом второго D-триггера управления битами TU 6, прямой выход которого соединен с третьим инверсным входом первого 3 элемента И и со вторым прямым входом второго 4 элемента И, кроме того инверсный и прямой выходы второго D-триггера управления битами TU 6 являются соответственно первым и вторым выходами, а выход LE элемента ИЛИ 5 является третьим выходом блока детектора единиц и нулей 2,

причем третий выход LE блока детектора единиц и нулей 2 соединен с входом СЕ разрешения работы выходного буфера ОВ 11, первым входом третьего 8 элемента И и входом L разрешения записи второго счетчика бит СВ 10,

информационный D-вход третьего D-триггера разрешения счета групп ТСЕ 7 подключен к логической единице, а выход третьего D-триггера разрешения счета групп ТСЕ 7 соединен со вторыми входами третьего 8, четвертого 12, пятого 13 и шестого 14 элементов И, выход третьего 8 элемента И соединен с входом СЕ разрешения работы первого счетчика групп CG 9, выходы которого являются группой QG внешних выходов количества групп устройства,

на группу информационных D-входов второго счетчика бит СВ 10 подано значение двоичного кода «0…01», а группа выходов второго счетчика бит СВ 10 подключена к группе информационных D-входов выходного буфера ОВ 11, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 11 являются группой внешних выходов данных QO и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

причем первый выход блока детектора единиц и нулей 2 соединен с третьим входом четвертого 12 элемента И, а второй выход блока детектора единиц и нулей 2 соединен с третьим входом пятого 13 элемента И и входом UP направления счета реверсивного счетчика нулей единиц CZU 17,

кроме того выход четвертого 12 элемента И соединен с входом СЕ разрешения работы третьего счетчика нулей CZ 15, выходы которого являются группой внешних выходов количества нулей QZ, выход пятого 13 элемента И соединен с входом СЕ разрешения работы четвертого счетчика единиц CU 16, выходы которого являются группой внешних выходов количества единиц QU, выход шестого 14 элемента И соединен с входом СЕ разрешения работы пятого реверсивного счетчика нулей-единиц CZU 17, у которого первая М разрядная группа выходов является внутренней шиной «разность единиц и нулей» ZU и соединена с соответствующей первой группой блока преобразователя кода разности 18, а второй выход (М+1)-й разряд пятого реверсивного счетчика нулей-единиц CZU 17 является внешним флагом «нулей больше единиц» F01 и соединен с соответствующим вторым входом блока преобразователя кода разности 18, выходы которого являются группой внешних выходов «разность единиц и нулей» QZU,

причем в блоке преобразователя кода разности 18 вторые входы элементов ИЛИ, группы 19 из (М-2) элементов ИЛИ, соединены с соответствующими разрядами внутренней шины «разность единиц и нулей» ZU, начиная со второго разряда до (M-1)-го разряда, а первые входы элементов ИЛИ 19, начиная со второго до последнего (М-2)-го элемента, соединены с соответствующими выходами предыдущих элементов ИЛИ 19, начиная с первого до предпоследнего (М-3)-го элемента, а первый вход первого элемента ИЛИ 19 соединен с первым разрядом внутренней шины «разность единиц и нулей» ZU, вторые входы всех элементов И, группы 20 из (М-1) элементов И, соединены между собой и соединены со вторым входом F01 блока преобразователя кода разности 18, а первый вход первого элемента И из группы 20 соединен с первым разрядом внутренней шины «разность единиц и нулей» ZU, а первые входы элементов И 20, начиная со второго до последнего (М-1), соединены с соответствующими выходами элементов ИЛИ, группы 19 из (М-2) элементов, начиная с первого до (М-2)-го элемента ИЛИ, выходы элементов И, группы 20 из (М-1) элементов, соединены с соответствующими первыми входами одноименных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группы 21 из (М-1) элементов, вторые входы которых соединены с соответствующими разрядами внутренней шины «разность единиц и нулей» ZU, начиная со второго разряда до М-го разряда, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группы 21 из (М-1) элементов, являются (М-1) разрядами выходов QZU блока преобразователя кода разности 18, начиная со второго выхода до последнего М-го выхода QZU, а первый разряд выходов QZU блока преобразователя кода разности 18 соединен с первым разрядом внутренней шины «разность единиц и нулей» ZU.

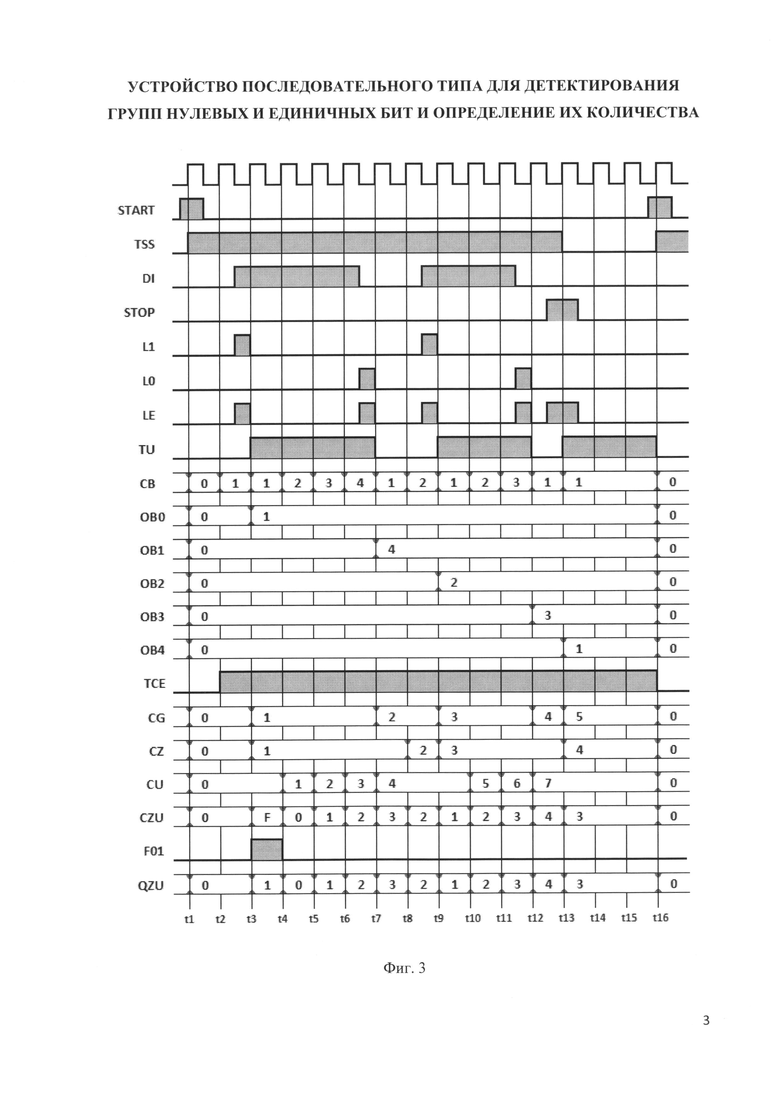

На фиг. 1 представлена схема предлагаемого устройства. На фиг. 2 приведена схема блока преобразователя кода разности 18. На фиг. 3 и фиг. 4 приведены временные диаграммы работы устройства.

На фиг. 1-4 и в тексте приняты следующие обозначения:

С - тактовый вход,

СВ - счетчик бит,

СЕ - вход разрешения работы,

CG - счетчик групп,

CLR - вход асинхронной установки в нулевое состояние,

CU - счетчик единиц,

CZ - счетчик нулей,

CZU - реверсивный счетчик нулей-единиц,

D - информационный вход триггера,

DI - внешний вход данных,

ЕО - внешняя шина управления обменом с выходным буфером ОВ,

F01 - флаг «нулей больше единиц»,

FE - флаг готовности,

FF - флаг «Буфер заполнен»,

FZ - флаг «Буфер пуст»,

L - вход разрешения записи,

L0 - разрешение счета нулей,

L1 - разрешение счета единиц,

LE - разрешение счета бит,

М - разрядность счетчиков M=[log2N]+1 (меньшее целое),

N - размерность (длина) входной последовательности данных,

ОВ - выходной буфер,

QG - группа внешних выходов количества групп,

QO - группа внешних выходов данных,

QU - группа внешних выходов количества единиц,

QZ - группа внешних выходов количества нулей,

QZU - группа внешних выходов «разность единиц и нулей»,

R - вход синхронной установки в нулевое состояние,

S - вход синхронной установки в единичное состояние,

START - внешний вход начала работы,

STOP - внешний вход останова,

Т - триггер,

ТСЕ - триггер разрешения счета групп,

TSS - триггер пуска-останова,

TU - триггер управления битами,

UP - вход направления счета реверсивного счетчика нулей единиц CZU,

ZU - внутренняя шина «разность единиц и нулей»,

1 - первый RS-триггер пуска-останова TSS,

2 - блок детектора единиц и нулей,

3 - первый элемент И с одним инверсным входом,

4 - второй элемент И с одним инверсным входом,

5 - элемент ИЛИ,

6 - второй D-триггер управления битами TU,

7 - третий D-триггер разрешения счета групп ТСЕ,

8 - третий элемент И,

9 - первый счетчик групп CG,

10 - второй счетчик бит СВ,

11 - выходной буфер ОВ,

12 - четвертый элемент И,

13 - пятый элемент И,

14 - шестой элемент И,

15 - третий счетчик нулей CZ,

16 - четвертый счетчик единиц CU,

17 - пятый реверсивный счетчик нулей-единиц CZU,

18 - блок преобразователя кода разности,

19 - группа из (М-2) элементов ИЛИ,

20 - группа из (М-1) элементов И,

21 - группа из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Предлагаемое устройство содержит внешний вход данных DI, группу внешних выходов данных QO, группу внешних выходов количества групп QG, группу внешних выходов количества нулей QZ, группу внешних выходов количества единиц QU, группу внешних выходов «разность единиц и нулей» QZU, первый RS-триггер пуска-останова TSS 1, блок детектора единиц и нулей 2, третий D-триггер разрешения счета групп ТСЕ 7, третий элемент И 8, первый счетчик групп CG 9, второй счетчик бит СВ 10, выходной буфер ОВ 11, четвертый 12, пятый 13 и шестой 14 элементы И, третий счетчик нулей CZ 15, четвертый счетчик единиц CU 16, пятый реверсивный счетчик нулей-единиц CZU 17 и блок преобразователя кода разности 18.

Блок детектора единиц и нулей 2 состоит из первого 3 и второго 4 элементов И с одним инверсным входом, элемента ИЛИ 5 и второго D-триггера управления битами TU 6 и содержит три выхода.

Блок преобразователя кода разности 18 содержит группу из (М-2) элементов ИЛИ 19, группу из (М-1) элементов И 20 и группу из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 21, где M=[log2N]+1 (меньшее целое), а N - размерность длина входной последовательности данных, причем первый счетчик групп CG 9, второй счетчик бит СВ 10, выходной буфер ОВ 11, третий счетчик нулей CZ 15 и четвертый счетчик единиц CU 16 имеют разрядность М, а пятый реверсивный счетчик нулей-единиц CZU 17 имеет разрядность (М+1).

В предлагаемое устройство также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внешняя шина управления обменом ЕО, внешние флаг готовности результата FE, флаг «Буфер заполнен» FF, флаг «Буфер пуст» FZ и флаг «нулей больше единиц» F01, и внутренняя шина «разность единиц и нулей» ZU.

Внешний вход асинхронной установки в нулевое состояние CLR соединен с соответствующим входом асинхронной установки в нулевое состояние CLR первого RS-триггера пуска-останова TSS 1.

Внешний тактовый вход устройства С соединен с входами синхронизации первого 1 RS-триггера пуска-останова TSS, второго D-триггера управления битами TU 6, третьего D-триггера разрешения счета групп ТСЕ 7, первого счетчика групп CG 9, второго счетчика бит СВ 10, выходного буфера ОВ 11, третьего счетчика нулей CZ 15, четвертого счетчика единиц CU 16 и пятого реверсивного счетчика нулей-единиц CZU 17.

Внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1 и входами R синхронной установки в нулевое состояние второго D-триггера управления битами TU 6, третьего D-триггера разрешения счета групп ТСЕ 7, первого счетчика групп CG 9, второго счетчика бит СВ 10, выходного буфера ОВ 11, третьего счетчика нулей CZ 15, четвертого счетчика единиц CU 16 и пятого реверсивного счетчика нулей-единиц CZU 17.

Внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1 и первым входом элемента ИЛИ 5 в блоке детектора единиц и нулей 2.

Прямой выход первого RS-триггера пуска-останова TSS 1 соединен с первыми входами первого 3 и второго 4 элементов И с одним инверсным входом в блоке детектора единиц и нулей 2, с входом СЕ разрешения работы второго счетчика бит СВ 10 и с первыми входами четвертого 12, пятого 13 и шестого 14 элементов И, а инверсный выход первого RS-триггера пуска-останова TSS 1 является внешним флагом готовности результата FE.

В блоке детектора единиц и нулей 2 внешний вход данных DI соединен со вторым прямым входом первого 3 элемента И и третьим инверсным входом второго 4 элемента И, выходы которых соединены соответственно со вторым и третьим входами элемента ИЛИ 5. Выход LE разрешения счета бит элемента ИЛИ соединен с входом СЕ разрешения работы второго D-триггера управления битами TU 6, у которого инверсный выход соединен с информационным D-входом второго D-триггера управления битами TU 6, прямой выход которого соединен с третьим инверсным входом первого 3 элемента И и со вторым прямым входом второго 4 элемента И. Выход первого 3 элемента И является выходом L1 разрешения счета единиц, а выход второго 4 элемента И является выходом L0 разрешения счета нулей. Кроме того, инверсный и прямой выходы второго D-триггера управления битами TU 6 являются соответственно первым и вторым выходами, а выход LE элемента ИЛИ 5 является третьим выходом блока детектора единиц и нулей 2.

Причем третий выход LE блока детектора единиц и нулей 2 соединен с входом СЕ разрешения работы выходного буфера ОВ 11, первым входом третьего элемента И 8 и входом L разрешения записи второго счетчика бит СВ 10.

Информационный D-вход третьего D-триггера разрешения счета групп ТСЕ 7 подключен к логической единице. Выход третьего D-триггера разрешения счета групп ТСЕ 7 соединен со вторыми входами третьего 8, четвертого 12, пятого 13 и шестого 14 элементов И. Выход третьего 8 элемента И соединен с входом СЕ разрешения работы первого счетчика групп CG 9, выходы которого являются группой QG внешних выходов количества групп устройства.

На группу информационных D-входов второго счетчика бит СВ 10 подано значение двоичного кода «0…01». Группа выходов второго счетчика бит СВ 10 подключена к группе информационных D-входов выходного буфера ОВ 11, который также подключен к внешней шине ЕО управления обменом. Соответствующие выходы выходного буфера ОВ 11 являются группой внешних выходов данных QO и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

Причем первый выход блока детектора единиц и нулей 2 соединен с третьим входом четвертого 12 элемента И, а второй выход блока детектора единиц и нулей 2 соединен с третьим входом пятого 13 элемента И и входом UP направления счета реверсивного счетчика нулей единиц CZU 17.

Кроме того выход четвертого 12 элемента И соединен с входом СЕ разрешения работы третьего счетчика нулей CZ 15, выходы которого являются группой внешних выходов количества нулей QZ. Выход пятого 13 элемента И соединен с входом СЕ разрешения работы четвертого счетчика единиц CU 16, выходы которого являются группой внешних выходов количества единиц QU. Выход шестого 14 элемента И соединен с входом СЕ разрешения работы пятого реверсивного счетчика нулей-единиц CZU 17, у которого первая М разрядная группа выходов является внутренней шиной «разность единиц и нулей» ZU и соединена с соответствующей первой группой блока преобразователя кода разности 18, а второй выход (М+1)-й разряд пятого реверсивного счетчика нулей-единиц CZU 17 является внешним флаг «нулей больше единиц» F01 и соединен с соответствующим вторым входом блока преобразователя кода разности 18, выходы которого являются группой внешних выходов «разность единиц и нулей» QZU.

В блоке преобразователя кода разности 18 вторые входы элементов ИЛИ, группы 19 из (М-2) элементов ИЛИ, соединены с соответствующими разрядами внутренней шины «разность единиц и нулей» ZU, начиная со второго разряда до (M-1)-го разряда, а первые входы элементов ИЛИ 19, начиная со второго до последнего (М-2)-го элемента, соединены с соответствующими выходами предыдущих элементов ИЛИ 19, начиная с первого до предпоследнего (М-3)-го элемента, а первый вход первого элемента ИЛИ 19 соединен с первым разрядом внутренней шины «разность единиц и нулей» ZU. Вторые входы всех элементов И, группы 20 из (М-1) элементов И, соединены между собой и соединены со вторым входом F01 блока преобразователя кода разности 18, а первый вход первого элемента И из группы 20 соединен с первым разрядом внутренней шины «разность единиц и нулей» ZU. Первые входы элементов И 20, начиная со второго до последнего (М-1), соединены с соответствующими выходами элементов ИЛИ, группы 19 из (М-2) элементов, начиная с первого до (М-2)-го элемента ИЛИ. Выходы элементов И, группы 20 из (М-1) элементов, соединены с соответствующими первыми входами одноименных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группы 21 из (М-1) элементов, вторые входы которых соединены с соответствующими разрядами внутренней шины «разность единиц и нулей» ZU, начиная со второго разряда до М-го разряда. Выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группы 21 из (М-1) элементов, являются (М-1) разрядами выходов QZU блока преобразователя кода разности 18, начиная со второго выхода до последнего М-го выхода QZU, а первый разряд выходов QZU блока преобразователя кода разности 18 соединен с первым разрядом внутренней шины «разность единиц и нулей» ZU.

Первый RS-триггер пуска-останова TSS 1 предназначен для выделения цикла работы предлагаемого устройства, между сигналами START и STOP, при подаче входной последовательности данных DI размерности N, и формирования флага FE готовности результата.

Блок детектора единиц и нулей 2 предназначен для определения начала групп нулей, при этом формируется сигнал L0, или групп единиц, при этом формируется сигнал L1. Второй D-триггер управления битами TU 6 определяет текущую группу единичных (прямой выход установлен в единичное состояние) или нулевых (инверсный выход установлен в единичное состояние) бит последовательности входных данных DI. Третий D-триггер разрешения счета групп ТСЕ 7 обеспечивает задержку счета групп на один первый такт в цикле работы.

Первый 9 счетчик групп CG предназначен для подсчета общего количества нулевых и единичных групп во входной последовательности данных DI размерности N. Второй счетчик бит СВ 10 осуществляет подсчет нулевых и единичных бит в каждой группе. Выходной буфер ОВ 11 предназначен для накопления сумм нулевых и единичных бит в каждой группе.

Третий счетчик нулей CZ 15 осуществляет подсчет общего количества нулевых бит во входной последовательности данных DI. Четвертый счетчик единиц CU 16 осуществляет подсчет общего количества единичных бит во входной последовательности данных DI. Пятый реверсивный счетчик нулей-единиц CZU 17 предназначен для определения соотношение между количеством нулевых и единичных бит во всей входной двоичной последовательности DI. При этом реверсивный счетчик нулей-единиц CZU 17 осуществляет суммирование единичных бит (вход UP=1) или вычитание нулевых бит (вход UP=0) и формирует флаг «нулей больше единиц» F01.

Блок преобразователя кода разности 18 осуществляет преобразование значения кода разности с внутренней шины «разность единиц и нулей» ZU от реверсивного счетчика нулей-единиц CZU 17 в код дополнения до 2M когда общее количество нулевых бит превышает общее количество единичных бит во всей входной двоичной последовательности DI (при этом флаг «нулей больше единиц» F01 установлен в единичное значение F01=1).

Принцип работы предлагаемого устройства состоит в следующем.

На внешний вход данных DI последовательно разряд за разрядом поступают биты входной последовательности данных размерностью N. Устройство начинает работать после подачи сигнала START, при котором по фронту тактового сигнала С в единичное состояние устанавливается первый RS-триггер пуска-останова TSS 1, в нулевое состояние устанавливаются второй D-триггер управления битами TU 6 и третий D-триггер разрешения счета групп ТСЕ 7, а также нулевые значения устанавливаются в первом счетчике групп CG 8, во втором счетчике бит СВ 9, в третьем счетчик нулей CZ 15, в четвертом счетчике единиц CU 16, пятом реверсивном счетчике нулей-единиц CZU 17 и устанавливается нулевой начальный адрес в выходном буфере ОВ 11. Единичное значение с прямого выхода первого RS-триггера пуска-останова TSS 1 разрешает работать в счетном режиме счетчику бит СВ 10, а также поступает на прямые входы первого 3 и второго 4 элементов И с инверсным входом.

В блоке детектора единиц и нулей 2 второй D-триггер управления битами TU 6 определяет группу единичных или нулевых разрядов входных данных DI следующим образом. Когда второй D-триггер управления битами TU 6 установлен в нулевое состояние, выход которого соединен с инверсным входом первого 3 элемента И и с прямым входом второго 4 элемента И, а также прямой вход первого 3 элемента И и инверсный вход второго 4 элемента И соединены с входом данных DI, то на выходе L1 первого 3 элемента И формируется единичное значение L1=1 при появлении единичного значения на входе данных DI или нулевое значение L1=0 при нулевом значении на входе данных DI, а также на выходе L0 второго 4 элемента И будет установлено нулевое значение L0=0 независимо от входного значения на входе данных DI. При единичном состоянии второго D-триггера управления битами TU 6 аналогично на выходе L0 второго 4 элемента И будет установлено единичное значение L0=1 при нулевом значении на входе данных DI или нулевое значение L0=0 при единичном значении на входе данных DI, а также на выходе L1 первого 3 элемента И будет установлено нулевое значение L1=0 независимо от входного значения на входе данных DI. Таким образом, блок детектора единиц и нулей 2 детектирует (выявляет) переход в последовательности входных данных DI от группы нулевых бит к группе единичных бит при нулевом состоянии второго D-триггер управления битами TU 6 и переход в последовательности входных данных DI от группы единичных бит к группе нулевых бит при единичном состоянии второго D-триггера управления битами TU 6. Сигналы L1 и L0 с выходов первого 3 и второго 4 элементов И с инверсным входом поступают на входы элемента ИЛИ 5, на выходе LE которого формируется единичное значение LE=1 при переходе от «нулевых» групп к «единичным» группам и наоборот в последовательности входных данных DI. Далее сигнал с выхода LE поступает на вход разрешения работы СЕ второго D-триггера управления битами TU 6, который по фронту тактового сигнала С переходит в противоположенное состояние, так как его информационный D-вход соединен с инверсным входом второго D-триггера управления битами TU 6.

Единичное значение сигнала LE=1 также поступает на вход разрешения СЕ первого счетчика групп CG 9, который работает в счетном режиме, а также на вход L разрешения записи кода данных «0…01» во второй счетчик бит СВ 10, у которого вход L имеет высший приоритет. Поэтому при единичном значении сигнала LE=1 (при переходе между группами разрядов в последовательности входных данных DI) увеличивается значение первого счетчика групп CG 9 и загружается код «0…01» во второй счетчик бит СВ 10 - выполняется счет одного текущего бита следующей группы в последовательности входных данных DI.

В начале работы устройство настроено на счет группы нулевых бит в последовательности входных данных DI (так как второй D-триггер управления битами TU 6 установлен в нулевое состояние) и выполняется счет нулевых бит до первого единичного бита данных DI, по которому второй D-триггер управления битами TU 6 переходит в единичное состояние и далее осуществляется счет единичных бит в последовательности входных данных DI до первого нулевого бита данных DI, по которому вновь переключается второй D-триггер управления битами TU 6.

При единичном значении первого бита в последовательности входных данных DI по первому единичному сигналу L1=1 и соответственно единичному значению сигнала LE=1 не осуществляется счет первой «нулевой» группы (которая отсутствует) в первом счетчике групп CG 8. Запрет счета групп осуществляется нулевым значением с выхода третьего D-триггера разрешения счета групп ТСЕ 7, который переключается в единичное состояние только по фронту первого тактового сигнала С в каждом цикле работы. Таким образом, третий D-триггер разрешения счета групп ТСЕ 7 осуществляет задержку счета групп на один такт сигнала С.

При единичном значение сигнала LE=1 по фронту тактового сигнала С также осуществляется запись в выходной буфер ОВ 11 кода с выхода второго счетчика бит СВ 10, значение которого соответствует количеству бит в соответствующей группе входных данных DI. При этом в четные адреса, начиная с нулевого адреса, выходного буфера ОВ 11 записываются значения, соответствующие количеству бит в «нулевых» группах, а в нечетных адресах, начиная с первого адреса, записываются значения, соответствующие количеству бит в «единичных» группах. Если во входной последовательности DI данные начинаются с единичного значения первого бита, то по нулевому адресу ОВ0 выходного буфера ОВ 11 записывается код «все нули», который в этот момент времени установлен на втором счетчике бит СВ 10.

При единичном значении сигнала STOP по фронту тактового сигнала С в нулевое состояние устанавливается первый RS-триггер пуска-останова TSS 1 и формируется флаг готовности результата FE=1. Одновременно также устанавливается единичное значение на выходе LE элемента ИЛИ 5 (LE=1) и по фронту тактового сигнала С осуществляется запись кода с выхода второго счетчика бит СВ 10 соответствующего последней группе бит в последовательности входных данных DI и увеличивается значение количества групп в первом счетчике групп CG 9.

При заполнении выходного буфера ОВ 11 формируется флаг «Буфер заполнен» FF=1. Считывание данных из выходного буфера ОВ 11 осуществляется по сигналам с внешней шины управления обменом ЕО и при достижении нулевого адреса формируется флаг «Буфер пуст» FZ=1.

Одновременно по каждому тактовому сигналу в третьем счетчике нулей CZ 15 осуществляется подсчет общего количества нулевых бит во входной последовательности данных DI при единичном значении на инверсном выходе второго D-триггера управления битами TU 6, в четвертом счетчике единиц CU 16 осуществляется подсчет общего количества единичных бит во входной последовательности данных DI при единичном значении на прямом выходе второго D-триггера управления битами TU 6. Кроме того в пятом 17 реверсивном счетчике нулей-единиц CZU осуществляется суммированием подсчет единичных бит и вычитанием подсчет нулевых бит. Таким образом, на выходе пятого 17 реверсивного счетчика нулей-единиц CZU на внутренней шине ZU будет установлен код разности между суммой единичных и нулевых бит в последовательности входных данных DI.

Далее если сумма нулевых бит превышает сумму единичных бит, то формируется единичное значение флага «нулей больше единиц» F01=1. По этому флагу F01 в блоке преобразователя кода разницы 18 формируется код дополнения до 2M, который будет соответствовать соотношению между нулевыми и единичными битами в последовательности входных данных DI.

Дополнение получается после изменения всех старших единиц на нули, кроме последней младшей единицы, и всех старших нулей на единицы, до последней младшей единицы, т.е. выполняется инверсия старших разрядов до последней младшей единицы. При этом самый младший разряд с внутренней шины ZU всегда остается неизменным.

Анализ единиц начинается с младшего разряда шины ZU в группе 19 из (М-2) элементов ИЛИ. При этом выявление единицы в одном из младших разрядов передается последовательно на все старшие разряды по цепочке последовательно соединенных элементов ИЛИ, в группе 19 из (М-2) элементов, и при единичном значении флага «нулей больше единиц» F01=1 через группу 20 из (М-1) элементов И поступает на группу 21 из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8, на которых проводится инверсия битов старших разрядов шины ZU. При нулевом значении флага «нулей больше единиц» F01=0 на выходах группы 20 из (М-1) элементов И формируется нулевой сигнал, поэтому через группу 21 из (М-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, который можно рассматривать как элемент «управляемый инвертор», передается значение разрядов шины ZU без преобразования.

Предлагаемое устройство работает следующим образом.

При подаче сигнала на вход CLR асинхронной установки в нулевое состояние устанавливается первый RS-триггер пуска-останова TSS 1. Тактовые сигналы с входа С постоянно поступают на входы синхронизации всех триггеров и счетчиков, режимы работы которых задаются сигналами на соответствующих входах управления, а исполняются по фронтам тактовых сигналов С.

На временных диаграммах на фиг. 3 и фиг. 4 приведена работа предлагаемого устройства. На фиг. 3 на внешний вход данных DI подана последовательность «01111001110» содержащая N=11 бит, а на фиг. 4 три последовательности «101», «000», «111» содержащие по N=3 бит, которые отражают основные особенности работы устройства.

Работа устройства в каждом цикле начинается после подачи сигнала START. При этом по фронту первого тактового сигнала С (момент времени t1 на фиг. 3 и t21, t27, t33 на фиг. 4) в единичное состояние устанавливается первый RS-триггер пуска-останова TSS 1, в нулевое состояние устанавливаются второй D-триггер управления битами TU 6 и третий D-триггер разрешения счета групп ТСЕ 7, а также нулевые значения устанавливаются в первом счетчике групп CG 9, во втором счетчике бит СВ 10, в третьем счетчик нулей CZ15, в четвертом счетчике единиц CU 16, пятом реверсивном счетчике нулей-единиц CZU17 и устанавливается начальный нулевой адрес в выходном буфере ОВ 11.

На внешний вход данных DI последовательно разряд за разрядом поступают биты входной последовательности данных размерностью N. В момент времени t2 (фиг. 3) на вход данных поступает нулевое значение первого бита входной последовательности DI и по фронту тактового сигнала С осуществляет суммирование второй счетчик бит СВ 10 (СВ=1), а также переходит в единичное состояние третий D-триггер разрешения счета групп ТСЕ 7. При этом не выполняется счет групп в первом счетчике групп CG 9, а также не выполняется счет нулей в счетчиках CZ 15 и CZU 17, так как установлены нулевые значения на входах СЕ разрешения работы до фронта в момент времени t2.

Между моментами времени t2 и t3 на вход данных DI поступает единичное значение, по которому в блоке детектора 2 осуществляется выявление единичного бита и на выходе первого 3 элемента И формируется единичный сигнал L1=1 разрешения счета единиц, и далее формируется единичный сигнал LE=1 разрешения счета бит на выходе элемента ИЛИ 5.

В момент времени t3 по фронту тактового сигнала С в единичное состояние переключается второй D-триггер управления битами TU 6, осуществляется суммирование в первом счетчике групп CG 9 (при сигналах LE=1 и ТСЕ=1), суммирование в третьем счетчике нулей CZ 15 и вычитание в пятом реверсивном счетчике нулей-единиц CZU 17 (на фиг. 3 счетчик CZU 17 содержит пять разрядов, так как М=4). При этом в пятом реверсивном счетчике нулей-единиц CZU 17 формируется код F (1111), который поступает на внутреннюю шину «разность единиц и нулей» ZU, а также формируется флаг «нулей больше единиц» F01=1. В блоке преобразователя кода разности 18 код F (1111), с внутренней шины ZU и при значении флага F01=1, преобразуется в код дополнения до 24 (выполняется инверсия старших разрядов до младшего единичного бита) и на группу внешних выходов QZU передается значение кода «1 (0001)».

Одновременно при сигнале LE=1, который поступает на вход СЕ разрешения работы, осуществляется запись в выходной буфер ОВ 11 по нулевому адресу ОВ0 значения с выхода второго счетчика бит СВ 10 (значение ОВ0=1 - соответствует количеству нулевых бит в первой группе входных данных DI), а также при сигнале LE=1, который поступает на вход L разрешения записи второго счетчика бит СВ 10, осуществляется запись двоичного кода «0…01» во второй счетчик бит СВ 10 (СВ=1 - выполняется счет первого единичного бита из второй группы). При переходе в единичное состояние второго D-триггера управления битами TU 6 блок детектора 2 настроен на выявление нулевых бит во входных данных DI.

Далее в моменты времени t4, t5, t6 по фронту тактовых сигналов С осуществляется суммирование единичных бит во втором счетчике бит СВ 10 (СВ=2, 3, 4 - фиг. 3), а также суммирование в четвертом счетчике единиц CU 16 и пятом реверсивном счетчике нулей-единиц CZU 17.

Между моментами времени t6 и t7 на вход данных DI поступает нулевое значение, по которому в блоке детектора 2 осуществляется выявление нулевого бита и на выходе второго 4 элемента И формируется единичный сигнал L0=1 разрешения счета нулей, и далее единичный сигнал LE=1 разрешения счета бит на выходе элемента ИЛИ 5.

В момент времени t7 по фронту тактового сигнала С при сигнале LE=1 осуществляется запись в выходной буфер ОВ 11 по первому адресу ОВ1 значения с выхода второго счетчика бит СВ 10 (значение ОВ1=4 - соответствует количеству единичных бит во второй группе входных данных DI), запись двоичного кода «0…01» во второй счетчик бит СВ 10 (СВ=1 выполняется счет первого нулевого бита третьей группы) и увеличение в первом счетчике групп CG 9 (CG=2). Одновременно осуществляется суммирование последнего четвертого единичного бита второй входной группы в четвертом счетчике единиц CU 16 (CU=4) и пятом реверсивном счетчике нулей-единиц CZU 17 (CZU=3 - соответствует сумме четырех единичных бит и вычитанию одного нулевого бита). Также в момент времени t7 в нулевое состояние переключается второй D-триггер управления битами TU 6 и блок детектора 2 настраивается на выявление следующей группы единичных бит во входных данных DI.

Далее по фронту тактовых сигналов С аналогично в моменты времени t8 и t9 осуществляется счет нулевых бит в третьей группе входных данных DI, а в моменты времени t10 и t11 осуществляется счет единичных бит в четвертой группе входных данных DI.

В момент времени t12 по фронту тактового сигнала С при нулевом бите входных данных DI осуществляется запись количества единичных бит в четвертой группе (ОВ3=3), увеличение первого счетчика групп CG 9 (CG=4), а также подсчет общего количества единичных бит в четвертом счетчике единиц CU 16 (CU=7) и вычисление разности в пятом реверсивном счетчике нулей-единиц CZU 17 (CZU=4 - соответствует разности между количеством единичных бит (CU=7) и нулевых бит (CZ=3)).

Между моментами времени t12 и t13 поступает сигнал STOP, по которому в момент времени t13 по фронту тактового сигнала С в нулевое состояние переходит первый RS-триггер пуска-останова TSS 1, который запрещает дальнейший счет бит и формируется флаг готовности FE=1. Одновременно также формируется единичный сигнал LE разрешение счета бит LE=1 по которому осуществляется увеличение первого счетчика групп CG 9 (CG=5 - указывает на общее количество групп равное пяти), и аналогично выше рассмотренному осуществляется запись в выходной буфер ОВ 11 по четвертому адресу ОВ4 (ОВ4=1), счет нулевого бита пятой группы в третьем счетчике нулей CZ 15 (CZ=4), вычисление разности единичных и нулевых бит в пятом реверсивном счетчике нулей-единиц CZU 17 (CZU=3).

Значения с выходов счетчиков первого групп CG 9, третьего нулей CZ15, четвертого единиц CU 16, пятого реверсивного CZU 17 поступают на соответствующие внешние выходы групп QG, QZ, QU, QZU, а также сформированные флаги поступают на соответствующие внешние выходы.

Таким образом, для входной последовательности «01111001110» сформированы следующие значения: количество групп CG=5, количество нулей CZ=4, количество единиц CU=7, разность единиц и нулей CZU=3, первая «нулевая» группа содержит один бит ОВ0=1, вторая «единичная» группа содержит четыре бита ОВ1=4, третья «нулевая» группа - ОВ2=2, четвертая «единичная» группа - ОВ3=3, пятая «нулевая» группа - ОВ4=1.

Считывание результатов из выходного буфера ВО 11 выполняется под управлением по внешней шине управления ЕО. При реализации выходного буфера в виде двухпортовой памяти FIFO, обмен можно выполнять в процессе цикла работы подсчета единичных и нулевых бит с учетом значений флагов «Буфер пуст» FZ и «Буфер заполнен» FF.

На фиг. 4 в отличие от последовательности на фиг. 3 в первой последовательности входных данных «101» первый бит, подаваемый на вход DI, имеет единичное значение (интервал времени между t21 и t22). Так как после подачи сигнала START (момент времени t21) второй D-триггер управления битами TU 6 устанавливается в нулевое состояние, то блок детектора 2 всегда в начале каждого цикла работы устройства настроен на выявление единичных бит. Поэтому одновременно с подачей единичного бита на вход DI на выходе L1 первого 3 элемента И формируется единичное значение L1=1 разрешения счета единиц и далее единичное значение LE=1 разрешения счета бит на выходе элемента ИЛИ 5.

В момент времени t22 по фронту тактового сигнала С при сигнале LE=1 осуществляется запись двоичного кода «0…01» во второй счетчик бит СВ 10 (СВ=1 - выполняется счет первого единичного бита), но запрещен подсчет групп в первом счетчике групп CG 9, так как третий D-триггер разрешения счета групп ТСЕ 7 до момента времени t22 был установлен в нулевое состояние. Одновременно при сигнале LE=1, который поступает на вход СЕ разрешения работы, осуществляется запись в выходной буфер ОВ 11 по нулевому адресу ОВ0 нулевого значения с выхода второго счетчика бит СВ 10 (значение ОВ0=0 - соответствует тому, что нулевые биты в первой группе входных данных DI отсутствуют).

Далее по фронту тактовых сигналов С в моменты времени t22, t23, t24, аналогично рассмотренным режимам, приведенным на фиг. 3, проводится выявление и подсчет нулевых и единичных бит в последовательности входных данных DI. В результате в момент времени t25 после подачи сигнала STOP для входной последовательности «101» будут сформированы следующие значения: количество групп CG=3, количество нулей CZ=1, количество единиц CU=2, разность единиц и нулей CZU=1, первая «нулевая» группа указывает на отсутствие нулевых бит ОВ0=0, вторая «единичная» группа содержит один бит ОВ1=1, третья «нулевая» группа также один бит ОВ2=1 и четвертая «единичная» группа также один бит ОВ3=1.

В моменты времени t27-t31 на фиг. 4 приведена временная диаграмма работы устройства при подаче на вход данных DI последовательности содержащей одну группу только нулевых бит «000». После подачи сигнала START (момент времени t27) второй D-триггер управления битами TU 6 устанавливается в нулевое состояние, поэтому блок детектора 2 (всегда в начале каждого цикла работы устройства) настроен на выявление единичных бит. Так как во входной последовательности отсутствуют единичные биты, которые поэтому не обнаруживаются блоком детектора 2, то в устройстве не формируется единичное значение L1=1 разрешения счета единиц. При этом осуществляется суммирование во втором счетчике бит СВ 10 (СВ=1, 2, 3), суммирование в третьем счетчике нулей CZ 15 (CZ=1, 2, 3) и вычитание в пятом реверсивном счетчике нулей-единиц CZU 17 (CZU=F, Е, D). Так как количество нулевых бит больше количества единичных бит, которые отсутствуют, то формируется также единичное значение флага «нулей больше единиц» F01=1, по которому в блоке преобразователя кода разности 18 входные коды F (1111), Е (1110), D (1101) с внутренней шины ZU преобразуются в коды дополнения до 24 (выполняется инверсия старших разрядов до младшего единичного бита) и на группу внешних выходов QZU передаются соответствующие значения кодов - «1 (0001)», «2 (0010)», «3 (0011)».

При подаче сигнала STOP в момент времени t32 приостанавливается работа устройства, завершается цикл распознавания бит второй входной последовательности «000», для которой будут сформированы следующие значения: количество групп CG=1, количество нулей CZ=3, количество единиц CU=0, разность единиц и нулей CZU=D (1101), разность единиц и нулей после преобразования на выходе QZU=3, первая «нулевая» группа содержит три бита ОВ0=3, последующие группы не содержат бит (значения равны 0).

В моменты времени t33-t34 на фиг. 4 приведена временная диаграмма работы устройства при подаче на вход данных DI последовательности содержащей одну группу только единичных бит «111». После подачи сигнала START (момент времени t23) второй D-триггер управления битами TU 6 устанавливается в нулевое состояние, поэтому блок детектора 2 (всегда в начале каждого цикла работы устройства) настроен на выявление единичных бит. Поэтому, аналогично как в моменты времени t22-t23, одновременно с подачей единичного бита на вход DI на выходе L1 первого 3 элемента И формируется единичное значение L1=1 разрешения счета единиц и далее единичное значение LE=1 разрешения счета бит на выходе элемента ИЛИ 5. Далее, так как во входной последовательности на DI присутствуют только единичные биты, то осуществляется суммирование во втором счетчике бит СВ 10 (СВ=1, 2, 3), суммирование в четвертом счетчике единиц CU 16 (CU=1, 2, 3), суммирование в пятом реверсивном счетчике нулей-единиц CZU 17 (CZU=1, 2, 3) и формирование нулевого значения флага «нулей больше единиц» F01=0.

При подаче сигнала STOP момент времени t37 завершается цикл распознавания бит третьей входной последовательности «111», для которой будут сформированы следующие значения: количество групп CG=1, количество нулей CZ=0, количество единиц CU=3, разность единиц и нулей CZU=3, первая «нулевая» группа указывает на отсутствие нулевых бит ОВ0=0, вторая «единичная» группа содержит три бит ОВ1=3, последующие группы не содержат бит (значения равны 0).

Предлагаемое устройство может быть применено для аппаратной реализации статистических тестов, разработанных лабораторией информационных технологий Национального института стандартов и технологий (NIST, США), целью которых является определение меры случайности двоичных последовательностей, порожденных генераторами случайных чисел. В частности, предлагаемое устройство реализует:

- частотный побитовый тест, суть которого определить соотношение между нулями и единицами во всей двоичной последовательности. Цель - выяснить действительно ли число нулей и единиц в последовательности приблизительно одинаковы. Тест оценивает, насколько близка доля единиц к 0,5.

- частотный блочный тест, суть которого определение доли единиц внутри блока длиной К бит. Цель - выяснить действительно ли частота повторения единиц в блоке длиной К бит приблизительно равна К/2.

- тест на последовательность одинаковых бит, суть которого состоит в подсчете полного числа рядов (групп) в исходной последовательности, где под рядом понимается непрерывная подпоследовательность одинаковых бит. Ряд (группа) длиной k бит состоит из k абсолютно идентичных бит, начинается и заканчивается с бита содержащего противоположное значение. Цель - сделать вывод о том, действительно ли количество рядов (групп), состоящих из единиц и нулей с различными длинами, соответствует их количеству в случайной последовательности. В частности, определяется быстро либо медленно чередуются единицы и нули в исходной последовательности.

Таким образом, в предлагаемом устройстве для входных последовательностей данных размерностью N, поступающих на внешний вход данных DI, на соответствующих внешних выходах групп устройства формируются двоичные коды, соответствующие количеству групп QG, количеству нулевых бит QZ, количеству единичных бит QU, разности между количеством единичных и нулевых бит QZU, количество бит по группам QO с выходного буфера ОВ 11 (при этом в четных адресах, начиная с нулевого адреса, указывается количество нулевых бит в группах, а в нечетных адресах, начиная с первого адреса, указывается количество единичных бит в группах), а также формируются флаг готовности FE, флаг «нулей больше единиц» F01, флаг «Буфер заполнен» FE и флаг «Буфер пуст» FZ.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу и соответствует заявляемому техническому результату - выявление групп единичных и нулевых бит, определение общего количества и по группам единичных и нулевых бит, определение соотношения разности между количеством единичных и нулевых бит во входной последовательности данных размерностью N.

Изобретение относится к области вычислительной техники. Технический результат заключается в расширении арсенала средств того же назначения. Таким образом, в предлагаемом устройстве для входных последовательностей данных размерностью N, поступающих на внешний вход данных DI, на соответствующих внешних выходах групп устройства формируются двоичные коды, соответствующие количеству групп QG, количеству нулевых бит QZ, количеству единичных бит QU, разности между количеством единичных и нулевых бит QZU, количество бит по группам QO с выходного буфера ОВ 11, при этом в четных адресах, начиная с нулевого адреса, указывается количество нулевых бит в группах, а в нечетных адресах, начиная с первого адреса, указывается количество единичных бит в группах, а также формируются флаг готовности FE, флаг «нулей больше единиц» F01, флаг «Буфер заполнен» FE и флаг «Буфер пуст» FZ. 4 ил.

Устройство последовательного типа для детектирования групп нулевых и единичных бит и определения их количества содержит внешний вход данных DI, группу внешних выходов данных QO, группу внешних выходов количества групп QG, группу внешних выходов количества нулей QZ, группу внешних выходов количества единиц QU, группу внешних выходов «разность единиц и нулей» QZU, первый RS-триггер пуска-останова TSS 1, блок детектора единиц и нулей 2, который состоит из первого 3 и второго 4 элементов И с одним инверсным входом, элемента ИЛИ 5 и второго D-триггера управления битами TU 6, третий D-триггер разрешения счета групп ТСЕ 7, третий элемент И 8, первый счетчик групп CG 9, второй счетчик бит СВ 10, выходной буфер ОВ 11, четвертый 12, пятый 13 и шестой 14 элементы И, третий счетчик нулей CZ 15, четвертый счетчик единиц CU 16, пятый реверсивный счетчик нулей-единиц CZU 17 и блок преобразователя кода разности 18, который содержит группу из (М-2) элементов ИЛИ 19, группу из (М-1) элементов И 20 и группу из (М-1) элементов исключающее ИЛИ 21, где M=[log2N]+1 (меньшее целое), а N - размерность входной последовательности данных, причем первый счетчик групп CG 9, второй счетчик бит СВ 10, выходной буфер ОВ 11, третий счетчик нулей CZ 15 и четвертый счетчик единиц CU 16 имеют разрядность М, а пятый реверсивный счетчик нулей-единиц CZU 17 имеет разрядность (М+1), а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внешняя шина управления обменом ЕО, внешние флаг готовности результата FE, флаг «Буфер заполнен» FF, флаг «Буфер пуст» FZ и флаг «нулей больше единиц» F01, и внутренняя шина «разность единиц и нулей» ZU, причем внешний вход асинхронной установки в нулевое состояние CLR соединен с соответствующим входом асинхронной установки в нулевое состояние CLR первого RS-триггера пуска-останова TSS 1, внешний тактовый вход устройства С соединен с входами синхронизации первого 1 RS-триггера пуска-останова TSS, второго D-триггера управления битами TU 6, третьего D-триггера разрешения счета групп ТСЕ 7, первого счетчика групп CG 9, второго счетчика бит СВ 10, выходного буфера ОВ 11, третьего счетчика нулей CZ 15, четвертого счетчика единиц CU 16 и пятого реверсивного счетчика нулей-единиц CZU 17, внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1 и входами R синхронной установки в нулевое состояние второго D-триггера управления битами TU 6, третьего D-триггера разрешения счета групп ТСЕ 7, первого счетчика групп CG 9, второго счетчика бит СВ 10, выходного буфера ОВ 11, третьего счетчика нулей CZ 15, четвертого счетчика единиц CU 16 и пятого реверсивного счетчика нулей-единиц CZU 17, внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1 и первым входом элемента ИЛИ 5 в блоке детектора единиц и нулей 2, причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с первыми входами первого 3 и второго 4 элементов И с одним инверсным входом в блоке детектора единиц и нулей 2, с входом СЕ разрешения работы второго счетчика бит СВ 10 и с первыми входами четвертого 12, пятого 13 и шестого 14 элементов И, а инверсный выход первого RS-триггера пуска-останова TSS 1 является внешним флагом готовности результата FE, в блоке детектора единиц и нулей 2 внешний вход данных DI соединен со вторым прямым входом первого 3 элемента И и третьим инверсным входом второго 4 элемента И, выходы которых соединены соответственно со вторым и третьим входами элемента ИЛИ 5, выход LE которого соединен с входом СЕ разрешения работы второго D-триггера управления битами TU 6, у которого инверсный выход соединен с информационным D-входом второго D-триггера управления битами TU 6, прямой выход которого соединен с третьим инверсным входом первого 3 элемента И и со вторым прямым входом второго 4 элемента И, кроме того, инверсный и прямой выходы второго D-триггера управления битами TU 6 являются соответственно первым и вторым выходами, а выход LE элемента ИЛИ 5 является третьим выходом блока детектора единиц и нулей 2, причем третий выход LE блока детектора единиц и нулей 2 соединен с входом СЕ разрешения работы выходного буфера ОВ 11, первым входом третьего 8 элемента И и входом L разрешения записи второго счетчика бит СВ 10, информационный D-вход третьего D-триггера разрешения счета групп ТСЕ 7 подключен к логической единице, а выход третьего D-триггера разрешения счета групп ТСЕ 7 соединен со вторыми входами третьего 8, четвертого 12, пятого 13 и шестого 14 элементов И, выход третьего 8 элемента И соединен с входом СЕ разрешения работы первого счетчика групп CG 9, выходы которого являются группой QG внешних выходов количества групп устройства, на группу информационных D-входов второго счетчика бит СВ 10 подано значение двоичного кода «0…01», а группа выходов второго счетчика бит СВ 10 подключена к группе информационных D-входов выходного буфера ОВ 11, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 11 являются группой внешних выходов данных QO и внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ, причем первый выход блока детектора единиц и нулей 2 соединен с третьим входом четвертого 12 элемента И, а второй выход блока детектора единиц и нулей 2 соединен с третьим входом пятого 13 элемента И и входом UP направления счета реверсивного счетчика нулей единиц CZU 17, кроме того, выход четвертого 12 элемента И соединен с входом СЕ разрешения работы третьего счетчика нулей CZ 15, выходы которого являются группой внешних выходов количества нулей QZ, выход пятого 13 элемента И соединен с входом СЕ разрешения работы четвертого счетчика единиц CU 16, выходы которого являются группой внешних выходов количества единиц QU, выход шестого 14 элемента И соединен с входом СЕ разрешения работы пятого реверсивного счетчика нулей-единиц CZU 17, у которого первая М разрядная группа выходов является внутренней шиной «разность единиц и нулей» ZU и соединена с соответствующей первой группой блока преобразователя кода разности 18, а второй выход (М+1)-й разряд пятого реверсивного счетчика нулей-единиц CZU 17 является внешним флагом «нулей больше единиц» F01 и соединен с соответствующим вторым входом блока преобразователя кода разности 18, выходы которого являются группой внешних выходов «разность единиц и нулей» QZU, причем в блоке преобразователя кода разности 18 вторые входы элементов ИЛИ, группы 19 из (М-2) элементов ИЛИ, соединены с соответствующими разрядами внутренней шины «разность единиц и нулей» ZU, начиная со второго разряда до (M-1)-го разряда, а первые входы элементов ИЛИ 19, начиная со второго до последнего (М-2)-го элемента, соединены с соответствующими выходами предыдущих элементов ИЛИ 19, начиная с первого до предпоследнего (М-3)-го элемента, а первый вход первого элемента ИЛИ 19 соединен с первым разрядом внутренней шины «разность единиц и нулей» ZU, вторые входы всех элементов И, группы 20 из (М-1) элементов И, соединены между собой и соединены со вторым входом F01 блока преобразователя кода разности 18, а первый вход первого элемента И из группы 20 соединен с первым разрядом внутренней шины «разность единиц и нулей» ZU, а первые входы элементов И 20, начиная со второго до последнего (М-1), соединены с соответствующими выходами элементов ИЛИ, группы 19 из (М-2) элементов, начиная с первого до (М-2)-го элемента ИЛИ, выходы элементов И, группы 20 из (М-1) элементов, соединены с соответствующими первыми входами одноименных элементов исключающее ИЛИ, группы 21 из (М-1) элементов, вторые входы которых соединены с соответствующими разрядами внутренней шины «разность единиц и нулей» ZU, начиная со второго разряда до М-го разряда, выходы элементов исключающее ИЛИ, группы 21 из (М-1) элементов, являются (М-1) разрядами выходов QZU блока преобразователя кода разности 18, начиная со второго выхода до последнего М-го выхода QZU, а первый разряд выходов QZU блока преобразователя кода разности 18 соединен с первым разрядом внутренней шины «разность единиц и нулей» ZU.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ (НУЛЕЙ) В ДВОИЧНОМ ЧИСЛЕ | 2011 |

|

RU2446442C1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2006 |

|

RU2316042C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260204C1 |

Авторы

Даты

2019-02-26—Публикация

2018-02-16—Подача