Изобретение относится к контрольно-измерительной технике и может быть использовано при создании систем автоматического контроля взаимного влияния сигналов в радиоканалах и в проводных каналах электросвязи.

Известно устройство для контроля радиоэлектронных изделий (Патент RU 2071107 от 27.12.96 г., кл. G05B 23/02), использующее измерение обобщенного показателя качества функционирования, определяющего соответствие технического состояния контролируемого изделия его целевому назначению -передаче информации с заданной или меньшей вероятностью ошибок.

Однако в прототипе не учитывался факт, когда эксплуатируются передатчики сигналов, имеющие соответствие их технического состояния их целевому назначению передаче информации с заданной или меньшей вероятностью ошибок, которые передают модулированные сигналы в радиоканалы или в проводные каналы электросвязи, но не учитывают взаимного влияния передаваемых сигналов в среде распространения. Проведенные исследования показали, что сигналы с частотной модуляцией (ЧМ), фазовой модуляцией (ФМ), амплитудной модуляцией (AM), квадратурной многоуровневой, многофазовой модуляцией (QAM) даже при использовании различных несущих частот, фаз и амплитуд могут оказывать взаимное влияние друг на друга, приводящее к потере передаваемой модулирующей информации (Научный журнал ВАК РФ. Современные наукоемкие технологии. №6 (июнь) 2020, стр. 31-37. Раздел Технические науки. Издательство и редакция: Издательский Дом «Академия Естествознания» Статья «Модель контроля безопасности информационных систем» авт. Власов В.И., Власов С.В.).

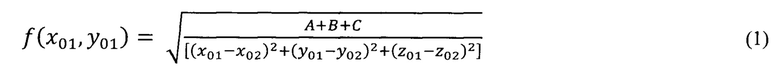

В соответствии с проведенными теоретическими исследованиями определена аналитическая модель для определения «расстояний» ƒ(x01, y01) между сигналами S1(t) и S2(t) в многомерном метрическом пространстве:

где:

r - амплитуда колебания; ω - циклическая частота; ϕ - начальная фаза сигнала.

Цель изобретения: повышение достоверности контроля взаимного влияния сигналов в линиях связи каналов передачи данных на основе многомерных метрических пространств.

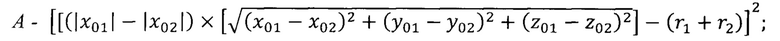

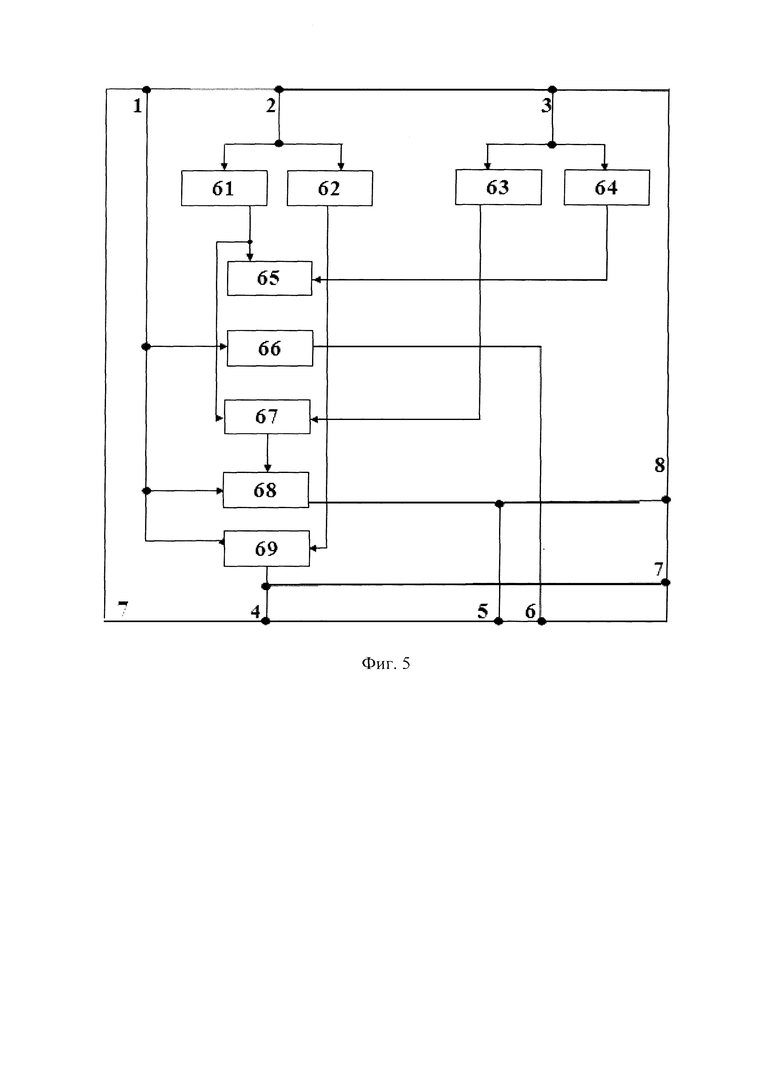

На фиг. 1 изображена структурная схема предложенного устройства; на фиг. 2 изображена функциональная схема блока вычисления величины взаимного влияния сигналов 3; на фиг. 3 изображена схема блока управления 4; на фиг. 4 изображена схема блока вычисления 11; на фиг. 5 изображена схема блока вычисления 12; на фиг. 6 изображена блок-схема алгоритма функционирования устройства.

Автоматизированное устройство контроля взаимного влияния сигналов содержит объект контроля 1, объект контроля 2, блок вычисления величины взаимного влияния сигналов 3, блок управления 4, аналого-цифровой преобразователь (АЦП) 5, элемент И 6, элемент И 7, регистр 8, компаратор 9, блок выводов результата контроля 10. В качестве объекта контроля может использоваться как передатчик модулированных сигналов, так и модулятор передатчика.

Блок вычисления величины взаимного влияния сигналов 3 содержит блок вычисления 11, блок вычисления 12, амплитудные детекторы 13, 16, частотные детекторы 14,17, фазовые детекторы 15, 18, сумматоры 19, 27, 34, 48, 49,квадраторы 20, 22, 26, 33, 42, 43, 44, 45, вычитающие устройства 21, 25,29, 30, 32, 35, 39, устройства модуля 23, 24, 28, 31, 40, 46, 50 (Авторское свидетельство на изобретение SU 284441 A1, МПК G06G 7/12), перемножители 36, 37, 38, устройства извлечения квадратного корня 41, 51 (Авторское свидетельство на изобретение SU 620986 A1 МПК G06G 7/20), делитель 47.

Блок вычисления 11 содержит устройство вычисления sinω1 52, устройство вычисления cosω1 53(Авторское свидетельство на изобретение SU 1494002 A2), устройство вычисления sinϕ1 54, устройство вычисления cosϕ1 55, перемножители 56, 57, 58, 59, 60. Блок вычисления 11 имеет контакты 1, 2, 3, 4, 5, 6, 7. Причем выход амплитудного детектора 13 через контакт 2 блока вычисления 11 подключен параллельно к контакту 1 и вторым входам перемножителей 57, 59, 60 блока вычисления 11. Выход частотного детектора 14 через контакт 3 блока вычисления 11 параллельно подключен к входам устройства вычисления sinω1 52 и устройства вычисления cosω1 53. Выход фазового детектора 15 подключен через контакт 4 блока вычисления 11 параллельно к входу устройства вычисления sinϕ1 54 и устройства вычисления cosϕ1 55. Выход устройства вычисления sinω1 52 параллельно подключен к первым входам перемножителей 56 и 58. Выход устройства вычисления cosω1 53 подключен к первому входу перемножителя 60. Выход устройства вычисления sinϕ1 54 подключен к первому входу перемножителя 58. Выход перемножителя 58 подключен к первому входу перемножителя 59. Выход устройства вычисления cosϕ1 55подключен к второму входу перемножителя 56. Выход перемножителя 56 подключен к первому входу перемножителя 57. Выход перемножителя 57 подключен к контакту 7 блока вычисления 11. Выход перемножителя 59 подключен к контакту 6 блока вычисления 11. Выход перемножителя 60 подключен к контакту 5 блока вычисления 11.

Блок вычисления 12 содержит устройство вычисления sinω2 61, устройство вычисления cosω2 62, устройство вычисления sinϕ2 63, устройство вычисления cosϕ2 64, перемножители 65, 66, 67, 68, 69. Блок вычисления 12 имеет контакты 1, 2, 3, 4, 5, 6, 7, 8. Причем выход амплитудного детектора 16 подключен к первому входу сумматора 19 и через контакт 1 блока вычисления 12 подключен к вторым входам перемножителей 66, 68, 69 блока вычисления 12. Выход частотного детектора 17 через контакт 2 блока вычисления 12 параллельно подключен к входам устройства вычисления sinω2 61 и устройства вычисления cosω2 62. Выход фазового детектора 18 подключен через контакт 3 блока вычисления 12 параллельно к входу устройства вычисления sinϕ2 63 и устройства вычисления cosϕ2 64. Выход устройства вычисления sinω2 61 параллельно подключен к первым входам перемножителей 65 и 67. Выход устройства вычисления cosω2 62 подключен к первому входу перемножителя 69. Выход устройства вычисления sinϕ2 63 подключен к второму входу перемножителя 67. Выход устройства вычисления cosϕ2 64 подключен к второму входу перемножителя 65. Выход перемножителя 66 подключен к контакту 6 блока вычисления 12. Выход перемножителя 68 подключен параллельно к контактам 5, 8 блока вычисления 12. Выход перемножителя 69 подключен параллельно к контактам 4, 7 блока вычисления 12. Контакт 1 блока вычисления величины взаимного влияния сигналов 3 параллельно подключен к входам амплитудного детектора 13, частотного детектора 14, фазового детектора 15, а контакт 2 блока вычисления величины взаимного влияния сигналов 3 параллельно подключен к амплитудному детектору 16, частотному детектору 17, фазовому детектору 18.

Первый вход сумматора 19 подключен к выходу амплитудного детектора 16, и к контакту 1 блока вычисления 12. Второй вход сумматора 19 подключен к контакту 1 блока вычисления 11, а выход сумматора 19 подключен к входу квадратора 20, выход которого подключен к первому входу вычитающего устройства 39, к второму входу которого подключен выход устройства модуля 28, вход которого подключен к выходу устройства извлечения квадратного корня 41, вход которого подключен параллельно к выходу сумматора 34 и к первому входу делителя 47. Выход вычитающего устройства 39 подключен к входу квадратора 45, выход которого параллельно подключен к вторым входам перемножителей 36, 37, 38.

Контакт 5 блока вычисления 11 подключен параллельно к первому входу вычитающего устройства 21 и к входу модуля 23. К второму входу вычитающего устройства 21 подключен контакт 4 блока вычисления 12. Выход вычитающего устройства 21 подключен к входу квадратора 22, выход которого подключен к первому входу сумматора 27. Выход устройства модуля 23 подключен к первому входу вычитающего устройства 29, второй вход которого подключен к выходу устройства модуля 46, а выход вычитающего устройства 29 подключен к первому входу перемножителя 36.

Контакт 6 блока вычисления 11 подключен параллельно к первому входу вычитающего устройства 25 и к входу устройства модуля 24, выход которого подключен к первому входу вычитающего устройства 30, выход которого подключен к первому входу перемножителя 37.

Контакт 7 блока вычисления 11 подключен параллельно к первому входу вычитающего устройства 32 и к входу устройства модуля 31, выход которого подключен к первому входу вычитающего устройства 35.

Контакт 5 блока вычисления 12 подключен к второму входу вычитающего устройства 25, выход которого подключен к квадратору 26, выход которого подключен к второму входу сумматора 27, выход которого подключен к первому входу сумматора 34, к второму входу которого подключен выход квадратора 33, к входу которого подключен выход вычитающего устройства 32.

Контакт 6 блока вычисления 12 подключен параллельно к второму входу вычитающего устройства 32 и к входу устройства модуля 40, выход которого подключен к второму входу вычитающего устройства 35, выход которого подключен к первому входу перемножителя 38.

Контакт 7 блока вычисления 12 подключен к входу устройства модуля 46.

Контакт 8 блока вычисления 12 подключен к входу устройства модуля 50, а выход устройства модуля 50 подключен к второму входу вычитающего устройства 30.

Выход перемножителя 36 последовательно через квадратор 42 подключен к первому входу сумматора 48, к второму входу которого последовательно через квадратор 43 подключен выход перемножителя 37. Выход сумматора 48 подключен к первому входу сумматора 49, к второму входу которого последовательно через квадратор 44 подключен выход перемножителя 38.

Выход сумматора 49 подключен к второму входу делителя 47, а выход делителя 47 подключен к входу устройства извлечения квадратного корня 51, выход которого через контакт 3 блока вычисления величины взаимного влияния сигналов 3 подключен к входу аналого-цифрового преобразователя (АЦП) 5, выход которого подключен параллельно к первым входам элементов И 6, И 7. К второму входу элемента И 6 подключен контакт 6 блока управления 4, а к второму входу элемента И 7 подключен контакт 7 блока управления 4. Выход элемента И 6 подключен к первому входу регистра 8, выход которого подключен к второму входу компаратора 9, к первому входу которого подключен выход элемента И 7. Три выхода компаратора 9 подключены к блоку выводов результатов контроля 10, а третий вывод компаратора 9 подключен также параллельно к второму входу регистра 8 и контакту 5 блока управления 4.

Кнопка «Пуск» 95 подключена к входу элемента ИЛИ 93, выход которого подключен к установочному входу триггера 92, прямой выход которого подключен к первому входу элемента И 90, ко второму входу которого подключен генератор импульсов 89. Выход элемента И 90 параллельно подключен к входам элемента задержки 87 и счетчика 88. Выход элемента задержки 87 подключен параллельно к входу усилителя 85 и к управляющему входу постоянного запоминающего устройства (ПЗУ) 86, к информационным входам которого параллельно подключены выходы счетчика 88 и эти выходы счетчика 88 параллельно подключены к входам дешифратора 74. Выходы ПЗУ 86 параллельно подключены к входам регистров 70, 72, 77, 79, 83. Выход усилителя 85 подключен параллельно к вторым входам элементов И 71, 73, 78, 82, 84.

Выход регистра 70 подключен к контакту 1 блока управления 4. Выход регистра 72 подключен к контакту 2 блока управления 4. Выход регистра 77 подключен к входу элемента задержки 76, выход которого параллельно подключен к контакту 3 блока управления 4 и к выходу элемента И 80. Выход регистра 79 подключен параллельно к контакту 4 блока управления 4 и к выходу элемента И 81. Выход регистра 83 подключен параллельно к вторым входам элементов И 80 и 81, к первым входам которых параллельно подключен выход элемента ИЛИ 75, контакт 7 блока управления 4 и сбросовые входы регистров 77 и 79.

Первый выход дешифратора 74 подключен к первому входу элемента И 71. Второй выход дешифратора 74 подключен к первому входу элемента И 73, третий выход дешифратора 74 подключен к первому входу элемента И 78, четвертый выход дешифратора 74 подключен параллельно к первому входу элемента И 82 и к контакту 6 блока управления 4. С 5-го по n-го выходы дешифратора 74 подключены параллельно к входам элемента ИЛИ 75, а n-й выход дешифратора 74 подключен параллельно к сбросовым входам регистров 70, 72.

Контакт 5 блока управления 4 подключен к первому входу элемента ИЛИ 94, ко второму входу которого подключена кнопка «Сброс» 96, а выход элемента ИЛИ 94 подключен параллельно к сбросовому входу триггера 92 и к входу усилителя 91, выход которого подключен параллельно к сбросовым входам всех регистров и счетчика 88.

Контакт 1 блока управления 4 подключен к второму входу объекта контроля 1, а контакт 3 блока управления 4 подключен к второму входу объекта контроля 2.

Контакт 2 блока управления 4 подключен к первому входу объекта контроля 1, а контакт 4 блока управления 4 подключен к первому входу объекта контроля 2.

Устройство работает следующим образом.

Перед началом работы устройство приводят в исходное состояние подачей сигнала «Сброс» от кнопки 96 через элемент ИЛИ 94 на сбросовый вход триггера 92 и через усилитель 91 на сбросовые входы всех регистров и счетчика 88. В исходном состоянии содержимое регистра 8, регистров 70, 72, 77, 79, 83 блока управления 4 равно нулю, триггер 92 и счетчик 88 сброшены, а элемент И 90 закрыт для прохождения импульсов от генератора импульсов 89. Также перед началом работы в постоянное запоминающее устройство 86 вводят последовательно код несущей частоты объекта контроля 1, код несущей частоты объекта контроля 2, код стимула формируемого сигнала с QAM-объекта контроля 1, код стимула формируемого сигнала с QAM-объекта контроля 2, причем эти коды стимула должны соответствовать сигналам диаграмм канстелляции объекта контроля 1 и объекта контроля 2, имеющие минимальные значения разницы амплитуд и фаз формируемых модулированных сигналов на выходах объектов контроля 1 и 2. Данные значения вводятся оператором на основе анализа кодовых слов одинаковых диаграмм канстелляции, установленных в объект контроля QAM-объектов контроля 1 и 2. Далее в постоянное запоминающее устройство 86 последовательно вводятся коды стимулов всех символов диаграмм канстелляции, установленных в объектах контроля 1 и 2.

Автоматический цикл контроля начинается подачей от кнопки 95 сигнала «Пуск», который, пройдя через элемент ИЛИ 93 на установочный вход триггера 92, обеспечивает на прямом выходе последнего сигнала, равного логической единице, чем открывает элемент И 90 для прохождения импульсов от генератора импульсов 89 на вход элемента задержки 87 и счетный вход счетчика 88.

Поступив на счетный вход счетчика 88, первый импульс от генератора 89 меняет содержимое этого счетчика на единицу, то есть в данном случае формирует на выходе счетчика 88 код адреса первого слова программы установки параметров объектов контроля 1 и 2. Очередной код адреса с выхода счетчика 88 поступает на управляющие входы постоянного запоминающего устройства 86 и параллельно на входы дешифратора 74. Спустя время, необходимое для завершения переходных процессов в счетчике 88, первый импульс с генератора импульсов 89 через элемент задержки 87 поступает на вход постоянного запоминающего устройства 86 в качестве сигнала «считывание», а на вход усилителя 85 в качестве синхроимпульса. По сигналу «считывание» постоянное запоминающее устройство 86 выполняет с частотой генератора импульсов 89 считывание слов программы контроля. При этом содержимое счетчика 88 меняется всякий раз при поступлении на его счетный вход импульсов от генератора импульсов 89. В постоянном запоминающем устройстве 86 перед началом работы последовательно записываются коды значений несущих частот первого объекта контроля 1, второго объекта контроля 2, код минимальной разности фаз двух возможных символов диаграммы канстелляции QAM, код минимальной разности амплитуд двух возможных символов диаграммы канстелляции QAM, и коды всех символов диаграммы канстелляции QAM (Лагутенко О.И. Современные модемы. - М.: Эко-Трендз, 2002).

С выхода постоянного запоминающего устройства 86 коды команд параллельно поступают на входы регистров 70, 72, 77, 79, 83. При поступлении на вход дешифратора 74 кода первого счетного импульса с выхода счетчика 88, на первом выходе дешифратора 74 формируется логическая единица, которая поступает на первый вход элемента И 71, на второй вход которого поступает сигнал с выхода усилителя 85, тем самым разрешая запись в регистр 70 кода несущей частоты объекта контроля 1. При поступлении на вход дешифратора 74 кода второго счетного импульса с выхода счетчика 88, на втором выходе дешифратора 74 формируется логическая единица, которая поступает на первый вход элемента И 73, на второй вход которого поступает сигнал с выхода усилителя 85, тем самым разрешая запись в регистр 72 кода несущей частоты объекта контроля 2. С выходов регистров 70 и 72 коды несущих частот через соответственно контакты 1, 2 блока управления 4 поступают на первые установочные входы объектов контроля 1 и 2 соответственно. При поступлении на вход дешифратора 74 кода третьего счетного импульса с выхода счетчика 88, на третьем выходе дешифратора 74 формируется логическая единица, которая поступает на первый вход элемента И 78, на второй вход которого поступает сигнал с выхода усилителя 85, тем самым разрешая запись в регистр 77 кода стимула, который соответствует настройке объекта контроля 1 на выдачу на своем выходе сигнала с заданными значениями амплитуды и фазы установленной ранее несущей частоты. При поступлении на вход дешифратора 74 кода четвертого счетного импульса с выхода счетчика 88, на четвертом выходе дешифратора 74 формируется логическая единица, которая поступает на первый вход элемента И 82, на второй вход которого поступает сигнал с выхода усилителя 85, тем самым разрешая запись в регистр 79 кода стимула, который соответствует настройке объекта контроля 2 на выдачу на своем выходе сигнала с заданными значениями амплитуды и фазы установленной ранее несущей частоты, причем значения кода стимула, поступающего на вход объекта контроля 2 соответствует минимальным значениям разницы фазы и амплитуды диаграммы канстелляции между значениями фазы и амплитуды объекта контроля 1 и объекта контроля 2. С выхода регистра 77 через элемент задержки 76, выполняющий задержку на время между импульсами генератора импульсов 89, код стимула через контакт 3 блока управления 4 поступает на первый вход объекта контроля 1, который на своем выходе выдает сигнал установленной несущей частоты и значений амплитуды и фазы модулированного сигнала в соответствие с диаграммой канстелляции. Элемент задержки 76 задерживает поступление кода стимула на первый вход объекта контроля 1 на интервал времени между импульсами генератора 89, чтобы обеспечить одновременное поступление кодов стимула на вторые входы объектов контроля 1 и 2. С выхода объекта контроля 1 модулированный QAM-сигнал поступает через контакт 1 блока вычисления величины взаимного влияния сигналов 3 параллельно на входы амплитудного детектора 13, частотного детектора 14, фазового детектора 15. С выхода объекта контроля 2 модулированный QAM-сигнал поступает через контакт 2 блока вычисления величины взаимного влияния сигналов 3 параллельно на входы амплитудного детектора 16, частотного детектора 17, фазового детектора 18. С выхода частотного детектора 14 амплитуда детектированного сигнала, соответствующая несущей частоте объекта контроля 1 через контакт 3 блока вычисления 11 параллельно поступает на вход устройства вычисления sinω1 52 и устройство вычисления cosω1 53. С выхода устройства вычисления sinω1 52 полученное значение sinω1 поступает параллельно на первые входы перемножителей 56 и 58. С выхода устройства вычисления cosω1 53 полученное значение cosω1 поступает на первый вход перемножителя 60. С выхода фазового детектора 15 через контакт 4 блока вычисления 11 амплитудное значение сигнала, соответствующее фазе модулированного QAM-сигнала поступает параллельно на входы устройства вычисления sinϕ1 54 и устройства вычисления cosϕ1 55. С выхода устройства вычисления sinϕ1 54 полученное значение поступает на второй вход перемножителя 58, а сигнал с выхода устройства вычисления cosϕ1 55 поступает на второй вход перемножителя 56. С выхода амплитудного детектора 13 через контакт 2 блока вычисления 11 сигнал поступает на вторые входы перемножителей 57, 59, 60 и через контакт 1 блока вычисления 11 на второй вход сумматора 19. Полученное значение с выхода перемножителя 56 поступает на первый вход перемножителя 57, с выхода которого полученный сигнал поступает через контакт 7 блока вычисления 11 параллельно на первый вход вычитающего устройства 32 и на вход устройства модуля 31. С выхода перемножителя 58 сигнал поступает на первый вход перемножителя 59, с выхода которого сигнал через контакт 6 блока вычисления 11 поступает параллельно на вход устройства модуля 24 и первый вход вычитающего устройства 25. С выхода перемножителя 60 через контакт 5 блока вычисления 11 сигнал параллельно поступает на первый вход вычитающего устройства 21 и на вход устройства модуля 23.

С выхода амплитудного детектора 16 сигнал параллельно поступает на первый вход сумматора 19 и через контакт 1 блока вычисления 12 параллельно на вторые входы перемножителей 66, 68, 69. С выхода частотного детектора 17 сигнал поступает через контакт 2 блока вычисления 12 параллельно на вход устройства вычисления sinω2 61 и устройства вычисления cosω2 62. С выхода устройства вычисления cosω2 62 сигнал поступает на первый вход перемножителя 69. С выхода фазового детектора 18 сигнал через контакт 3 блока вычисления 12 параллельно поступает на вход устройства вычисления sinϕ2 63 и устройства вычисления cosϕ2 64. С выхода устройства вычисления sinω2 61 сигнал поступает параллельно на первый вход перемножителя 65 и первый вход перемножителя 67. На второй вход перемножителя 65 поступает сигнал с выхода устройства вычисления cosϕ2 64. С выхода перемножителя 65 сигнал поступает на первый вход перемножителя 66. С выхода устройства вычисления sinϕ2 63 сигнал поступает на второй вход перемножителя 67, с выхода которого сигнал поступает на первый вход перемножителя 68, с выхода которого сигнал через контакт 8 блока вычисления 12 поступает на вход устройства модуля 50 и через контакт 5 блока вычисления 12 поступает на второй вход вычитающего устройства 25. С выхода перемножителя 69 сигнал через контакт 4 блока вычисления 12 поступает на второй вход вычитающего устройства 21 и через контакт 7 блока вычисления 12 поступает на вход устройства модуля 46. С выхода перемножителя 66 через контакт 6 блока вычисления 12 сигнал поступает параллельно на вход устройства модуля 40 и второй вход вычитающего устройства 32, с выхода которого сигнал поступает на вход квадратора 33.

С выхода сумматора 19 сигнал поступает на вход квадратора 20, с выхода которого сигнал поступает на первый вход вычитающего устройства 39.

С выхода вычитающего устройства 21 сигнал поступает на вход квадратора 22, с выхода которого сигнал поступает на первый вход сумматора 27. С выхода вычитающего устройства 25 сигнал поступает на вход квадратора 26, с выхода которого сигнал поступает на второй вход сумматора 27.

С выхода устройства модуля 23 сигнал поступает на первый вход вычитающего устройства 29, на второй вход которого поступает сигнал с выхода устройства модуля 46.

С выхода устройства модуля 24 сигнал поступает на первый вход вычитающего устройства 30, на второй вход которого поступает сигнал с выхода устройства модуля 50.

С выхода сумматора 27 сигнал поступает на первый вход сумматора 34, на второй вход которого поступает сигнал с выхода квадратора 33. С выхода сумматора 34 сигнал поступает параллельно на первый вход делителя 47 и на вход устройства извлечения квадратного корня 41, с выхода которого сигнал поступает через устройство модуля 28 на второй вход вычитающего устройства 39, с выхода которого сигнал поступает на вход квадратора 45, с выхода которого сигнал поступает параллельно на вторые входы перемножителей 36, 37, 38.

С выхода вычитающего устройства 29 сигнал поступает на первый вход перемножителя 36, с выхода которого сигнал поступает на вход квадратора 42, с выхода которого сигнал поступает на первый вход сумматора 48.

С выхода вычитающего устройства 30 сигнал поступает на первый вход перемножителя 37, с выхода которого сигнал через квадратор 43 поступает на второй вход сумматора 48, с выхода которого сигнал поступает на первый вход сумматора 49

На первый вход вычитающего устройства 35 поступает сигнал с выхода устройства модуля 31, на второй вход вычитающего устройства 35 поступает сигнал с выхода устройства модуля 40, а с выхода вычитающего устройства 35 сигнал поступает на первый вход перемножителя 38, с выхода которого сигнал через квадратор 44 поступает на второй вход сумматора 49, с выхода которого сигнал поступает на второй вход делителя 47, с выхода которого сигнал поступает на вход устройства извлечения квадратного корня 51, с выхода которого амплитудное значение величины минимально возможного «расстояния» между сигналами в многомерном метрическом пространстве, через контакт 3 блока вычисления величины взаимного влияния сигналов 3 поступает в аналого-цифровой преобразователь 5, где оцифровывается и поступает параллельно на первые входы элементов И 7 и И 6, на второй вход элемента И 6 поступает логическая единица с четвертого выхода дешифратора 74 через контакт 6 блока управления 4. А на второй вход элемента И 7 через контакт 7 блока управления 4 поступает сигнал с выхода элемента ИЛИ 75. С выхода элемента И 6 цифровой код порогового значения записывается в регистр 8, с выхода которого он поступает на второй вход компаратора 9.

При дальнейшем поступлении кодов счетных импульсов с выхода счетчика 88 на вход дешифратора 74, на пятом и последующих n-выходах последовательно формируются логические единицы, которые поступают на входы элемента ИЛИ 75. Сигналы с выхода элемента ИЛИ 75 поступают параллельно на первые входы элементов И 80 и 81, на сбросовый вход регистра кодов стимула 77, сбросовый вход регистра кодов стимула 79, обнуляя их и параллельно поступают на первый вход элемента И 84, на второй вход которого поступают тактовые импульсы с выхода усилителя 85. При появлении логической единицы на n-ом выходе логической единицы, она поступает на сбросовые входы регистров 70 и 72, обнуляя их. С выхода элемента И 84 импульсы поступают на управляющий вход регистра кодов стимула 83, разрешая запись в регистр 83 кодов символов диаграммы канстелляции, используемой в объектах контроля 1 и 2, а коды символов были записаны предварительно в ПЗУ 86.

Одинаковые коды стимула слов диаграмм канстелляции с выхода регистра 83 через элементы И 80 и 81 одновременно поступают соответственно через контакты 3,4 блока управления 4 на первые входы стимулирующих кодов объектов контроля 1 и 2. С выходов объектов контроля 1 и 2 QAM-модулированные сигналы одинаковых слов, но различных несущих частот поступают на контакты 1 и 2 блока вычисления величины взаимного влияния сигналов 3 и осуществляется автоматический расчет «расстояния» между сигналами в многомерном метрическом пространстве, то есть определения величины взаимного влияния двух сигналов.

На выходе устройства извлечения квадратного корня 51 будет присутствовать напряжение, представляющее собой результат измерения величины взаимного влияния сигналов с выходов объектов контроля 1 и 2, описываемого выражением 1, которое оцифровывается в аналого-цифровом преобразователе 5 и через элемент И 7 поступает на первый вход компаратора 9.

Если величина взаимного влияния (расстояние между сферами в многомерном метрическом пространстве) меньше допустимого значения, то на соответствующем третьем выходе компаратора возникает логическая единица, которая поступает параллельно на вход блока вывода результатов контроля 10, на второй (сбросовый) вход регистра 89, обнуляя его и через контакт 5 блока управления 4 на первый вход элемента ИЛИ 94, с выхода которого сигнал параллельно поступает на сбросовый вход триггера 92 и на вход усилителя 91, с выхода которого сигнал поступает на сбросовые входы регистров 70, 72, 77, 79, 83, обнуляя их, тем самым устройство приходит в исходное состояние. На блоке вывода результатов контроля 10 отображается информация, что использование данных исследуемых модулированных сигналов на данных несущих частотах неприемлемо и данное сочетание диаграмм канстелляции и несущих частот бракуется и выносится решение «не годен». Если величина взаимного влияния (расстояние между сферами в многомерном метрическом пространстве) больше или равно допустимому значению, записанному в регистре 8, то на соответствующих первом и втором выходе компаратора возникает логическая единица, что значит использование данных исследуемых модулированных сигналов на данных несущих частотах приемлемо и выносится решение «годен».

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО ДЛЯ ДИАГНОСТИКИ ЧЕЛОВЕКА ПО СОСТОЯНИЮ БИОЛОГИЧЕСКИ АКТИВНЫХ ТОЧЕК С АВТОМАТИЧЕСКИМ РАСПОЗНАВАНИЕМ ПАТОЛОГИИ ЧЕЛОВЕКА ПО ПРИЗНАК-ФУНКЦИЯМ | 2020 |

|

RU2750413C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2012 |

|

RU2504830C2 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО ПОВЫШЕНИЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2014 |

|

RU2603493C2 |

| СЛЕДЯЩИЙ ПРИЕМНИК ШИРОКОПОЛОСНОГО СИГНАЛА | 1999 |

|

RU2157052C1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА ЛИНИИ СВЯЗИ КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2003 |

|

RU2251723C2 |

| Устройство для диагностики неисправностей технических объектов | 1988 |

|

SU1536357A1 |

| Устройство контроля качества канала связи | 1988 |

|

SU1573543A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ ЛИНИИ СВЯЗИ КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2304847C2 |

Изобретение относится к области контрольно-измерительной техники и может быть использовано при создании систем автоматического контроля взаимного влияния сигналов в радиоканалах и в проводных каналах электросвязи. Технический результат заявленного решения заключается в повышении достоверности контроля взаимного влияния сигналов в линиях связи каналов передачи данных. Технический результат достигается тем, что в заявленном решении предусмотрены два объекта контроля, пять регистров, дешифратор, два усилителя, счетчик, постоянное запоминающее устройство (ПЗУ), элемент задержки, генератор импульсов, аналого-цифровой преобразователь (АЦП), триггер, три элемента ИЛИ, элемент И, кнопки «Сброс» и «Пуск», блок вывода результата контроля, компаратор, блок вычисления взаимного влияния сигналов, два блока вычисления, два амплитудных детектора, два частотных детектора, два фазовых детектора, пять сумматоров, восемь квадраторов, семь вычитающих устройств, семь устройств модуля, два устройства извлечения квадратного корня, делитель, регистр, девять элементов И. 6 ил.

Автоматизированное устройство контроля взаимного влияния сигналов. содержащее объект контроля, пять регистров, дешифратор, два усилителя, счетчик, постоянное запоминающее устройство (ПЗУ), элемент задержки, генератор импульсов, аналого-цифровой преобразователь (АЦП), триггер, три элемента ИЛИ, элемент И, кнопки «Сброс» и «Пуск», блок вывода результата контроля, компаратор, отличающееся тем, что введены второй объект контроля, блок вычисления взаимного влияния сигналов, два блока вычисления, два амплитудных детектора, два частотных детектора, два фазовых детектора, пять сумматоров, восемь квадраторов, семь вычитающих устройств, семь устройств модуля, два устройства извлечения квадратного корня, делитель, регистр, девять элементов И, причем первый блок вычисления содержит устройство вычисления sinω1, устройство вычисления cosω1, устройство вычисления sinϕ1, устройство вычисления cosϕ1, пять перемножителей, семь контактов, причем выход первого амплитудного детектора через второй контакт первого блока вычисления подключен параллельно к первому контакту первого блока вычисления и вторым входам второго, четвертого и пятого перемножителей первого блока вычисления, выход первого частотного детектора через третий контакт первого блока вычисления параллельно подключен к входам устройства вычисления sinω1 и устройства вычисления cosω1 первого блока вычисления, выход первого фазового детектора подключен через четвертый контакт первого блока вычисления параллельно к входу устройства вычисления sinϕ1 и устройства вычисления cosϕ1 первого блока вычисления, выход устройства вычисления sinω1 параллельно подключен к первым входам первого и третьего перемножителей первого блока вычисления, выход устройства вычисления cosω1 подключен к первому входу пятого перемножителя первого блока вычисления, выход устройства вычисления sinϕ1 подключен к первому входу третьего перемножителя первого блока вычисления, а выход третьего перемножителя подключен к первому входу четвертого перемножителя первого блока вычисления, выход устройства вычисления cosϕ1 подключен к второму входу первого перемножителя первого блока вычисления, а его выход подключен к первому входу второго перемножителя первого блока вычисления, выход второго перемножителя подключен к седьмому контакту первого блока вычисления, выход четвертого перемножителя первого блока вычисления подключен к шестому контакту первого блока вычисления, выход пятого перемножителя первого блока вычисления подключен к пятому контакту первого блока вычисления, второй блок вычисления содержит устройство вычисления sinω2, устройство вычисления cosω2, устройство вычисления sinϕ2, устройство вычисления cosϕ2, пять перемножителей, восемь контактов, причем выход второго амплитудного детектора подключен к первому входу первого сумматора и через первый контакт второго блока вычисления подключен к вторым входам второго, четвертого и пятого перемножителей второго блока вычисления, выход второго частотного детектора через второй контакт второго блока вычисления параллельно подключен к входам устройства вычисления sinω2 и устройства вычисления cosω2 второго блока вычисления, выход второго фазового детектора подключен через третий контакт второго блока вычисления параллельно к входу устройства вычисления sinϕ2 и устройства вычисления cosϕ2 второго блока вычисления, при этом выход устройства вычисления sinω2 параллельно подключен к первым входам первого и третьего перемножителей второго блока вычисления, а выход устройства вычисления cosω2 подключен к первому входу пятого перемножителя второго блока вычисления, выход устройства вычисления sinϕ2 подключен к второму входу третьего перемножителя второго блока вычисления, выход устройства вычисления cosϕ2 подключен к второму входу первого перемножителя второго блока вычисления, выход второго перемножителя второго блока вычисления подключен к шестому контакту второго блока вычисления, выход чевертого перемножителя второго блока вычисления подключен параллельно к пятому и восьмому контактам второго блока вычисления, выход пятого перемножителя второго блока вычисления подключен параллельно к четвертому и седьмому контактам второго блока вычисления, а первый контакт блока вычисления величины взаимного влияния сигналов параллельно подключен к первым входам первого амплитудного детектора, первого частотного детектора, первого фазового детектора, а второй контакт блока вычисления величины взаимного влияния сигналов параллельно подключен к входам второго амплитудного детектора, второго частотного детектора, второго фазового детектора блока вычисления величины взаимного влияния сигналов, первый вход первого сумматора подключен к выходу второго амплитудного детектора блока вычисления величины взаимного влияния сигналов, и к первому контакту второго блока вычисления, второй вход первого сумматора блока вычисления величины взаимного влияния сигналов подключен к первому контакту первого блока вычисления, а выход первого сумматора подключен к входу первого квадратора, выход которого подключен к первому входу первого вычитающего устройства, к второму входу которого подключен выход первого устройства модуля, вход которого подключен к выходу первого устройства извлечения квадратного корня, вход которого подключен параллельно к выходу второго сумматора и к первому входу первого делителя, выход первого вычитающего устройства подключен к входу второго квадратора, выход которого параллельно подключен к вторым входам первого, второго и третьего перемножителей блока вычисления величины взаимного влияния сигналов, пятый контакт первого блока вычисления подключен параллельно к первому входу первого вычитающего устройства и к входу второго устройства модуля, к второму входу первого вычитающего устройства подключен четвертый контакт второго блока вычисления, выход первого вычитающего устройства подключен к входу третьего квадратора, выход которого подключен к первому входу второго сумматора, выход второго устройства модуля подключен к первому входу второго вычитающего устройства, второй вход которого подключен к выходу третьего устройства модуля, а выход второго вычитающего устройства подключен к первому входу первого перемножителя, шестой контакт первого блока вычисления подключен параллельно к первому входу третьего вычитающего устройства и к входу четвертого устройства модуля, выход которого подключен к первому входу четвертого вычитающего устройства, выход которого подключен к первому входу второго перемножителя, седьмой контакт первого блока вычисления подключен параллельно к первому входу пятого вычитающего устройства и к входу пятого устройства модуля, выход которого подключен к первому входу первого вычитающего устройства, пятый контакт второго блока вычисления подключен к второму входу третьего вычитающего устройства, выход которого подключен к входу четвертого квадратора, выход которого подключен к второму входу второго сумматора, выход которого подключен к первому входу второго сумматора, к второму входу которого подключен выход пятого квадратора, к входу которого подключен выход пятого вычитающего устройства, шестой контакт второго блока вычисления подключен параллельно к второму входу пятого вычитающего устройства и к входу шестого устройства модуля, выход которого подключен к второму входу пятого вычитающего устройства 35, выход которого подключен к первому входу третьего перемножителя, седьмой контакт второго блока вычисления подключен к входу третьего устройства модуля, восьмой контакт второго блока вычисления подключен к входу шестого устройства модуля, а выход шестого устройства модуля подключен к второму входу четвертого вычитающего устройства, выход первого перемножителя последовательно через четвертый квадратор подключен к первому входу третьего сумматора, к второму входу которого последовательно через пятый квадратор подключен выход второго перемножителя, а выход третьего сумматора подключен к первому входу четвертого сумматора, к второму входу которого последовательно через шестой квадратор подключен выход третьего перемножителя, выход четвертого сумматора подключен к второму входу первого делителя, а выход первого делителя подключен к входу второго устройства извлечения квадратного корня, выход которого через третий контакт блока вычисления величины взаимного влияния сигналов подключен к входу аналого-цифрового преобразователя (АЦП), выход которого подключен параллельно к первым входам первого и второго элементов И, к второму входу элемента первого элемента И подключен шестой контакт блока управления, а к второму входу второго элемента И подключен седьмой контакт блока управления, выход элемента первого элемента И подключен к первому входу первого регистра, выход которого подключен к второму входу компаратора, к первому входу которого подключен выход второго элемента И, три выхода компаратора подключены к блоку выводов результатов контроля, а третий вывод компаратора подключен также параллельно к второму входу первого регистра и к пятому контакту блока управления, выходы счетчика блока управления параллельно подключены к входам дешифратора, выходы ПЗУ параллельно подключены к входам пяти регистров блока управления, выход первого усилителя подключен параллельно к вторым входам пяти элементов И блока управления, выход первого регистра блока управления подключен к первому контакту блока управления, выход второго регистра блока управления подключен к второму контакту блока управления, выход третьего регистра блока управления подключен к входу второго элемента задержки, выход которого параллельно подключен к третьему контакту блока управления и к выходу первого элемента И блока управления, выход четвертого регистра блока управления подключен параллельно к четвертому контакту блока управления и к выходу второго элемента И блока управления, выход пятого регистра блока управления подключен параллельно к вторым входам первого и второго элементов И блока управления, к первым входам которых параллельно подключены выход первого элемента ИЛИ блока управления, седьмой контакт блока управления и сбросовые входы третьего и четвертого регистров блока управления, первый выход дешифратора подключен к первому входу первого элемента И блока управления, второй выход дешифратора подключен к первому входу второго элемента И блока управления, третий выход дешифратора подключен к первому входу третьего элемента И блока управления, четвертый выход дешифратора подключен параллельно к первому входу четвертого элемента И блока управления и к шестому контакту блока управления, с 5-го по n-го выходы дешифратора подключены параллельно к входам первого элемента блока управления, а n-й выход дешифратора подключен параллельно к сбросовым входам первого и второго регистров, пятый контакт блока управления подключен к первому входу второго элемента ИЛИ, ко второму входу которого подключена кнопка «Сброс», первый контакт блока управления подключен к второму входу первого объекта контроля, а третий контакт блока управления подключен к второму входу второго объекта контроля, второй контакт блока управления подключен к первому входу первого объекта контроля, а четвертый контакт блока управления подключен к первому входу второго объекта контроля.

| УСТРОЙСТВО ДЛЯ АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ ЛИНИИ СВЯЗИ КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2304847C2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2012 |

|

RU2504830C2 |

| RU 2071107 C1, 27.12.1996 | |||

| MARIE SHINOTSUKA: "Analyzing radio interferometric positioning systems with undersampling receivers", 2015, [найдено: 26.10.2022] Найдено в: "https://asp-eurasipjournals.springeropen.com/articles/10.1186/s13634-015-0266-2" | |||

| GHAREEB I.: "Performance of MFSK signals | |||

Авторы

Даты

2022-12-14—Публикация

2022-01-14—Подача