ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам автоматического тестирования и может применяться для испытаний заказных СБИС на рабочих частотах и верификации их проектов на ПЛИС в процессе разработки.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

При создании высокопроизводительных вычислительных средств широкой номенклатуры заказных СБИС важно сокращение как общего срока их разработки и производства, так и снижение трудоемкости контроля работоспособности перед установкой их на вычислительные модули. Кроме этого при производстве крупных партий заказных СБИС актуальным является их сортировка по техническим характеристикам, например, предельные частоты и температура безотказной работы.

Известно устройство для диагностического контроля выполнения проверок (RU №2631989 С1, МПК G06F 11/273, заявлено 22.09.2016, опубликовано 29.09.2017 Бюл. №28), содержащее генератор тестов, модель объекта контроля, стандартные микромодули, коммутатор, схему сравнения, эталонный объект контроля, счетчик числа обнаруженных неисправностей, счетчик числа введенных неисправностей, делитель, датчик случайных чисел, блок ввода неисправностей, блок управления, элемент задержки, два элемента ИЛИ, счетчик установки числа неисправностей, триггер управления, элемент И, блок управления генератором тестов.

Недостатком данного устройства для диагностического контроля выполнения проверок является наличие эталонного объекта контроля, с помощью которого формируется система тестирования.

Причиной, препятствующей достижению технического результата, является отсутствие возможности верификации проектов объектов контроля при их разработке.

Известен автономный вычислительный модуль с субмодулями (RU №2748299 С1, МПК G06F 13/00, G06F 15/00, заявлен 02.10.2020, опубликован 21.05.2021 Бюл. №15), содержащий внешний порт 2 консольного управления, группу из N внешних сетевых портов 31, …, 3N, блок 4 индикации состояния, внешний порт 6 контроля и управления вычислительными ПЛИС, внешний порт 8 мониторинга и управления, блок 9 контроля и управления питанием, консоль 16 ручного управления, внешний порт 20 контроля и управления СБИС, блок 29 консольного управления, и группу из N субмодулей 221, …, 22N, каждый из которых содержит вычислительную ПЛИС 1, группу из K вычислительных СБИС 51, …, 5K, процессорное ядро 7, блок 15 контроля и управления питанием вычислительных СБИС, память 10 конфигураций вычислительной ПЛИС, оперативную память 11 процессорного ядра, оперативную память 12, блок 13 мониторинга, блок 14 индивидуальной настройки рабочих частот вычислительных СБИС, Flash память 19, блок 27 оперативной реконфигурации вычислительной ПЛИС и память 28 стартовой программы процессорного ядра.

Недостатком данного автономного вычислительного модуля с субмодулями является отсутствие возможности организации оперативного контроля работоспособности партий вычислительных СБИС, например, при осуществлении входного контроля компонент перед их установкой в рабочие модули.

Причиной, препятствующей достижению технического результата является трудоемкость замены проверяемых СБИС на их посадочных местах.

Известны тестеры микросхем FORMULA-HF и FORMULA-HF-ULTRA предназначенные для функционального и параметрического контроля СБИС (http://www.form.ru/products/chip/), содержащие входной интерфейс взаимодействия с управляющей вычислительной машиной, память тестовых векторов воздействий и память векторов реакций, блок управления тестированием, блоки входных и выходных преобразователей уровней сигналов, плату прижимного устройства и комплект плат адаптеров для установки контролируемых СБИС.

Недостатком данных тестеров микросхем является отсутствие возможности контроля работоспособности СБИС на рабочих частотах.

Причиной, препятствующей достижению технического результата, является ограничение рабочей частоты СБИС тактом подачи тестовых векторов воздействий.

Наиболее близким устройством, к заявленному изобретению, по совокупности признаков является принятый за прототип тестер-верификатор заказных СБИС (RU №2777449 С1, МПК G01R 31/3177, G06F 11/273, заявлен 29.11.2021, опубликован 04.08.2022 Бюл. №22), содержащий внешний порт 1 мониторинга состояния, внешний порт 2 сетевого интерфейса, внешний порт 3 интерфейса PCI_Express, внешний порт 4 контроля и управления JTAG, генератор 5 опорной частоты, память 6 данных и результатов тестирования, программируемый генератор 7 частоты обмена, управляющую ПЛИС 8, память 9 стартовой конфигурации, память 10 рабочей конфигурации, программируемый генератор 11 рабочей частоты СБИС, блок 12 мониторинга состояния, контактирующее устройство 13 с вентилятором и радиатором охлаждения СБИС, блок 14 управляемых источников питания СБИС и блок 15 управления питанием СБИС.

Недостатком данного тестера-верификатора заказных СБИС являются трудоемкость оперативного контроля и сортировки по частотным характеристикам больших партий СБИС, а также отсутствие возможности сортировки СБИС по температурным группам.

Причиной, препятствующей достижению технического результата, является большое время подготовки тестера-верификатора заказных СБИС к работе и выполнения тестирования после установки очередного испытуемого СБИС в контактирующее устройство и отсутствие возможности стабилизации температурного режима СБИС при испытаниях.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задача, на решение которой направлено предлагаемое изобретение, заключается в создании компактного и простого в эксплуатации тестера-верификатора для проведения функционального контроля и контроля работоспособности заказных СБИС, верификации проектов на ПЛИС в процессе разработки СБИС и выполнения оперативного контроля больших партий СБИС.

Техническим результатом предлагаемого изобретения являются расширение функциональных возможностей тестирования за счет сортировки СБИС по температурным и частотным характеристикам и сокращение времени испытания заказных СБИС за счет автоматической проверки заказных СБИС в автономном режиме.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что в тестер-верификатор содержащий внешний порт 1 мониторинга состояния, внешний порт 2 сетевого интерфейса, внешний порт 3 интерфейса PCI_Express, внешний порт 4 контроля и управления JTAG, генератор 5 опорной частоты, память 6 данных и результатов тестирования, программируемый генератор 7 частоты обмена, управляющую ПЛИС 8, память 9 стартовой конфигурации, память 10 рабочей конфигурации, программируемый генератор 11 рабочей частоты, блок 12 мониторинга состояния, контактирующее устройство 13 с вентилятором и радиатором охлаждения, блок 14 управляемых источников питания и блок 15 управления питанием,

причем внешние порты 2 сетевого интерфейса, 3 интерфейса PCI_Express и 4 контроля и управления JTAG соединены с управляющей ПЛИС 8, которая соединена с генератором 5 опорной частоты, с памятью 6 данных и результатов тестирования, с программируемым генератором 7 частоты обмена, с программируемым генератором 11 рабочей частоты, с блоком 12 мониторинга состояния, с блоком 15 управления питанием и шинами 16 управления и обмена данными и 17 конфигурирования с контактирующим устройством 13 с вентилятором и радиатором охлаждения, которое соединено с программируемыми генераторами 7 частоты обмена и 11 рабочей частоты, блоком 12 мониторинга состояния и блоком 14 управляемых источников питания,

кроме того внешний порт 4 контроля и управления JTAG соединен с контактирующим устройством 13 с вентилятором и радиатором охлаждения, а внешний порт 1 мониторинга состояния соединен с блоком 12 мониторинга состояния, который соединен с блоком 14 управляемых источников питания, который соединен с блоком 15 управления питанием,

дополнительно введены энергонезависимая память 18 подпрограмм настройки параметров испытаний, контроллер 19 энергонезависимой памяти программ испытаний, внешний порт 20 подключения энергонезависимой памяти программ испытаний, блок 21 отображения состояния, консоль 22 ручного управления, блок 23 управления конфигурированием управляющей ПЛИС 8, блок 24 управления стабилизацией температурного режима, память 25 конфигурации автономного режима управляющей ПЛИС 8, блок 26 управления скоростью вращения вентилятора охлаждения,

причем внешний порт 20 подключения энергонезависимой памяти программ испытаний соединен с контроллером 19 энергонезависимой памяти программ испытаний, который соединен с управляющей ПЛИС 8, которая соединена с энергонезависимой памятью 18 подпрограмм настройки параметров испытаний, блоком 21 отображения состояния, консолью 22 ручного управления, блоком 23 управления конфигурированием управляющей ПЛИС 8, блоком 24 управления стабилизацией температурного режима, который соединен с блоком 26 управления скоростью вращения вентилятора охлаждения и с блоком 12 мониторинга состояния,

кроме того консоль 22 ручного управления соединена с блоком 21 отображения состояния и блоком 23 управления конфигурированием управляющей ПЛИС 8, который соединен с памятью 9 стартовой конфигурации, памятью 10 рабочей конфигурации и памятью 25 конфигурации автономного режима управляющей ПЛИС 8.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

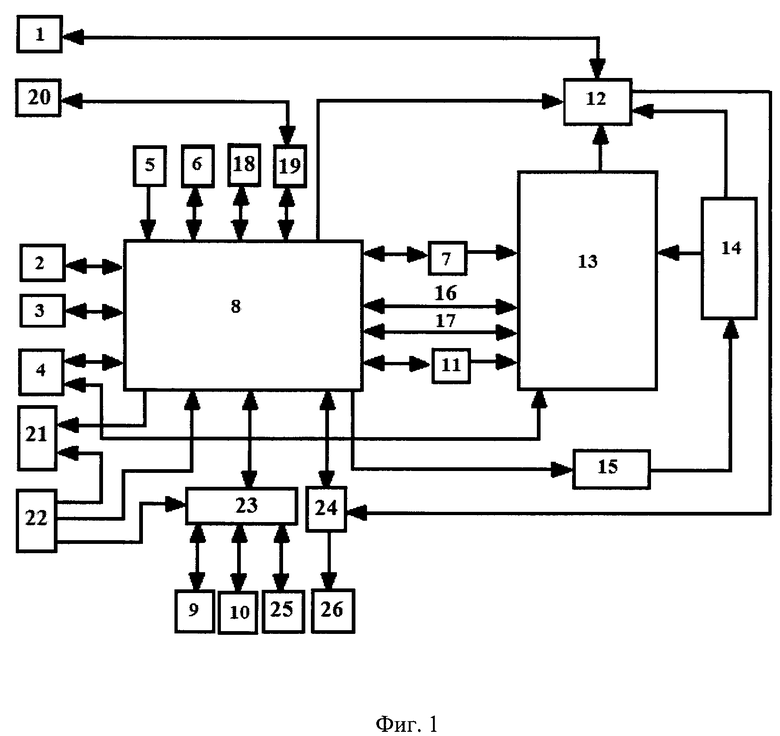

На фиг. 1 приведена функциональная схема тестера-верификатора.

На фиг. 1 и в тексте приняты следующие сокращения и обозначения:

КУ - контактирующее устройство с вентилятором и радиатором охлаждения;

1 - внешний порт мониторинга состояния;

2 - внешний порт сетевого интерфейса;

3 - внешний порт интерфейса PCI_Express;

4 - внешний порт контроля и управления JTAG;

5 - генератор опорной частоты;

6 - память данных и результатов тестирования;

7 - программируемый генератор частоты обмена;

8 - управляющая ПЛИС;

9 - память стартовой конфигурации;

10 - память рабочей конфигурации;

11 - программируемый генератор рабочей частоты;

12 - блок мониторинга состояния;

13 - контактирующее устройство с вентилятором и радиатором охлаждения;

14 - блок управляемых источников питания;

15 - блок управления питанием;

16 - шина управления и обмена данными;

17 - шина конфигурирования;

18 - энергонезависимая память подпрограмм настройки параметров испытаний;

19 - контроллер энергонезависимой памяти программ испытаний;

20 - внешний порт подключения энергонезависимой памяти программ испытаний;

21 - блок отображения состояния;

22 - консоль ручного управления;

23 - блок управления конфигурированием управляющей ПЛИС 8;

24 - блок управления стабилизацией температурного режима;

25 - память конфигурации автономного режима управляющей ПЛИС 8;

26 - блок управления скоростью вращения вентилятора охлаждения.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Предлагаемый тестер-верификатор осуществляет тестирование заказных СБИС или верификацию проектов СБИС на ПЛИС, устанавливаемых в контактирующее устройство 13 с вентилятором и радиатором охлаждения.

Предлагаемый тестер-верификатор может работать как под управлением ЭВМ (управляющая ЭВМ), к которой он подключается своими внешними портами 1^· непосредственно или через соответствующие коммутаторы, так и автономно при испытании больших партий заказных СБИС.

При работе тестера-верификатора с ЭВМ последняя осуществляет управление верификацией проектов заказных СБИС на этапе их разработки, управление тестированием заказных СБИС на этапе их входного контроля, запись энергонезависимой памяти 18 подпрограмм настройки параметров испытаний и внешней энергонезависимой памяти программ испытаний, подключаемой к внешнему порту 20 через контроллер 19, по внешнему порту 2 сетевого интерфейса или по внешнему порту 3 интерфейса PCI_Express управляющей ПЛИС 8 в зависимости от условий применения. Кроме того управляющая ЭВМ производит загрузку конфигурации в управляющую ПЛИС 8 и ПЛИС, устанавливаемую в контактирующее устройство 13 для верификации проектов СБИС, в памяти стартовой конфигурации 9, рабочей конфигурации 10 и конфигурации автономного режима 25 по внешнему порту 4 контроля и управления JTAG. Также управляющая ЭВМ осуществляет мониторинг состояния (температура, напряжение питания) испытуемых заказных СБИС и ПЛИС, предназначенных для верификации проектов СБИС, по внешнему порту 1.

Управляющая ПЛИС 8 предназначена для выполнения программы загруженной из памяти 9 стартовой конфигурации, памяти 10 рабочей конфигураций и памяти 25 конфигурации автономного режима, подключенной к нему посредством блока 23 управления конфигурированием, по включению питания, или загруженной по внешнему порту 4 контроля и управления JTAG при отладке программ.

Блок 23 управления конфигурированием управляющей ПЛИС 8 предназначен для выбора источника (память 9 стартовой, память 10 рабочей или память 25 конфигурации автономного режима) и организации конфигурирования управляющей ПЛИС 8 в зависимости от режима работы тестера-верификатора.

Память 9 стартовой конфигурации предназначена для хранения базовой программы управляющей ПЛИС 8, которая загружается в нее при включении питания и обеспечивает настройку программируемого генератора 11 рабочей частоты, программируемого генератора 7 частоты обмена, управление блоком 14 управляемых источников питания путем взаимодействия с блоком 15 управления питанием. Кроме этого базовая программа управляющей ПЛИС 8 обеспечивает поддержку интерфейсов взаимодействия с управляющей ЭВМ по внешнему порту 2 сетевого интерфейса, внешнему порту 3 PCI_Express, перезапись памяти конфигурации, подключенной к управляющей ПЛИС 8, и реализует выполнение команды переконфигурирования управляющей ПЛИС 8 из данной памяти конфигурации.

Память 10 рабочей конфигурации предназначена для хранения текущей программы управляющей ПЛИС 8, которая реализует тоже, что и базовая программа из памяти 9 стартовой конфигурации, а также обеспечивает еще и текущий (рабочий) обмен с памятью 6 данных и результатов тестирования и текущий (рабочий) интерфейс взаимодействия по шине 16 управления и обмена данными через контактирующее устройство 13 с тестируемой заказной СБИС или ПЛИС (на этапе верификации проектов заказных СБИС). Кроме этого текущая программа, при необходимости, обеспечивает запись программы в СБИС и конфигурирование ПЛИС, установленной в КУ 13, по шине 17 конфигурирования на этапе верификации проектов СБИС.

Память 25 конфигурации автономного режима предназначена для хранения программы управляющей ПЛИС 8 для работы в автономном режиме, которая реализует тоже, что и программа из памяти 10 рабочей конфигурации за исключением взаимодействия с управляющей ЭВМ по внешнему порту 3 PCI_Express, но обеспечивает работу консоли 22 ручного управления. Кроме того данная программа обеспечивает поддержку соответствующих интерфейсов взаимодействия управляющей ПЛИС 8 с энергонезависимой памятью 18 подпрограмм настройки параметров испытаний, с блоком 21 отображения состояния, с контроллером 19 энергонезависимой памяти, к которому через внешний порт 20 подключается внешняя память программ испытаний, и с блоком 24 управления стабилизацией температурного режима.

Память 6 данных и результатов тестирования предназначена для хранения исходных векторов воздействий и эталонных векторов реакций, а также хранения результатов тестирования СБИС или верификации их проектов.

Программируемый генератор 7 частоты обмена предназначен для задания частоты обмена между тестируемой заказной СБИС и управляющей ПЛИС 8.

Программируемый генератор 11 рабочей частоты предназначен для формирования сетки рабочих частот СБИС или ПЛИС на этапе верификации проектов СБИС, установленных в КУ 13.

Генератор 5 опорной частоты предназначен для формирования управляющей ПЛИС 8 опорных частот взаимодействия по внешнему порту 2 сетевого интерфейса и внешнему порту 3 интерфейса PCI_Express, а также формирования внутренней частоты работы управляющей ПЛИС 8 как с управляющей ЭВМ, так и в автономном режиме.

Блок 12 мониторинга состояния предназначен для контроля температурного режима заказной СБИС или ПЛИС (на этапе верификации проектов СБИС), установленной в КУ 13, и напряжений блока 14 управляемых источников питания, а также для взаимодействия с блоком 24 при стабилизации температурного режима СБИС.

Контактирующее устройство 13 с вентилятором и радиатором охлаждения предназначено для установки и подключения испытуемого заказного СБИС или ПЛИС (на этапе верификации проектов СБИС) к управляющей ПЛИС 8, а также охлаждения во время испытаний.

Блок 14 управляемых источников питания совместно с блоком 15 управления питанием предназначены для обеспечения питания СБИС или ПЛИС (на этапе верификации проектов СБИС) заданными номиналами.

Внешний порт 2 сетевого интерфейса предназначен для взаимодействия с управляющей ЭВМ, в случае организации нескольких рабочих мест для контроля, или для удаленной работы разработчиков заказных СБИС при верификации проектов. В данном случае тестеры-верификаторы могут работать как с индивидуальными управляющими ЭВМ, так и подключаться к сети пользователей через сетевой коммутатор.

ВЕРИФИКАЦИЯ ПРОЕКТОВ СБИС

В предлагаемом изобретении, вместо трудоемкого математического временного моделирования проектов заказных СБИС, осуществляется верификация проектов реализованных на ПЛИС, которая устанавливается в КУ 13 вместо заказной СБИС.

Исходными векторами воздействий и эталонными векторами реакций для верификации проектов заказных СБИС могут служить данные и результаты функционального моделирования их проектов. Формальные описания заказных СБИС компилируются (реализуются) на ПЛИС, которая устанавливается в КУ 13, с целью осуществления проверки данных описаний на корректность перед выпуском документации на изготовление СБИС.

При проведении верификации проектов СБИС тестер-верификатор работает следующим образом.

После установки в КУ 13 ПЛИС для верификации проектов заказных СБИС и включения питания в управляющую ПЛИС 8 загружается базовая программа из памяти 9 стартовой конфигурации. Если данная программа не соответствует верифицируемому проекту заказной СБИС, то соответствующая программа загружается из управляющей ЭВМ в память 10 рабочей конфигурации. После этого выполняется переконфигурирование управляющей ПЛИС 8 из памяти 10 уже рабочей конфигурации соответствующей программой.

Далее, после подачи питания на КУ 13 с установленной ПЛИС, осуществляется конфигурирование ПЛИС очередной программой верификации разрабатываемого СБИС по внешнему порту 3 интерфейса PCI_Express. После этого управляющая ЭВМ осуществляет настройку программируемых генераторов 7 частоты обмена и 11 рабочей частоты, а также загрузку памяти 6 данных и результатов тестирования для верификации проектов разрабатываемых СБИС. Верификация проекта СБИС выполняется путем подачи исходных векторов воздействий из памяти 6 и записи в память 6 векторов результата верификации. По окончании очередного интервала верификации, результаты верификации считываются из памяти 6 в управляющую ЭВМ для сравнения с эталоном.

При этом во время верификации управляющая ЭВМ осуществляет температурный контроль ПЛИС и контроль напряжений ее питания по внешнему порту 1 посредством блока 12 мониторинга состояния. В случае выхода температуры или напряжений питания из заданных пределов предусмотрено аварийное отключение питания. Это связано с тем, что на этапе верификации осуществляется отладка проектов заказных СБИС, которые могут содержать ошибки, приводящие к перегревам ПЛИС, установленной в КУ 13.

Так как интервалы верификации достаточно короткие и соответствуют интервалам функционального математического (машинного) моделирования, тестеры-верификаторы могут подключаться к сети пользователей-разработчиков заказных СБИС в многопользовательском режиме работы, что приводит к сокращению сроков разработки заказных СБИС и ускорению подготовки тестов для проверки заказных СБИС.

ИСПЫТАНИЯ СБИС С УПРАВЛЯЮЩЕЙ ЭВМ

Испытания изготовленных заказных СБИС с управляющей ЭВМ осуществляется на индивидуальных рабочих местах для обеспечения оперативной замены испытуемых заказных СБИС в КУ 13, и проводятся по внешнему порту 3 интерфейса PCI_Express, который предназначен для высокоскоростного взаимодействия с управляющей ЭВМ в монопольном режиме.

При проведении испытаний заказных СБИС с управляющей ЭВМ тестер-верификатор работает следующим образом.

После установки очередной заказной СБИС в КУ 13 осуществляется включение питания тестера-верификатора, при этом в управляющую ПЛИС 8 загружается программа из памяти 9 стартовой конфигурации. Затем включается управляющая ЭВМ и, если программа управляющей ПЛИС 8 не соответствует испытуемой заказной СБИС, то соответствующая программа предварительно загружается из управляющей ЭВМ в память 10 рабочей конфигурации и даются команды переконфигурирования управляющей ПЛИС 8 из памяти 10 рабочей конфигурации и перезагрузки управляющей ЭВМ.

После перезагрузки управляющая ЭВМ осуществляет программирование генератора 7 требуемой частотой обмена, генератора 11 требуемой рабочей частотой, а также загрузку исходных векторов воздействий в память 6 данных и результатов тестирования и настройку блока 14 управляемых источников питания блоком 15 управления питанием.

Перед подачей питания на КУ 13 выполняется проверка короткого замыкания питания СБИС с землей. Наличие короткого замыкания говорит о неисправности СБИС или о некорректной ее установке в КУ 13. После проверки корректности установки СБИС в КУ 13 и наличии короткого замыкания СБИС отбраковывается.

При отсутствии короткого замыкания питания СБИС с землей осуществляется включение питания на испытуемой заказной СБИС и выполняется ее тестирование.

Исходные вектора воздействий из памяти 6 выдаются на испытуемую СБИС, а результаты тестирования записываются в память 6 данных и результатов тестирования и, по окончании тестирования, выгружаются из нее для сравнения в управляющей ЭВМ с эталонными векторами реакций и выработки признаков "годен" или "брак".

Интервалов проверки для одного заказного СБИС может быть несколько, в зависимости от сложности решаемых задач. Так как испытания проводятся на рабочих (высоких) частотах СБИС, на протяжении всей проверки управляющая ЭВМ осуществляет температурный контроль испытуемой СБИС и контроль напряжений ее питания по внешнему порту 1 посредством блока 12 мониторинга состояния. В случае выхода температуры или напряжений питания из заданных пределов также предусмотрено аварийное отключение питания.

По окончании всех интервалов проверки с испытуемого СБИС в КУ 13 снимается напряжение питания, выключается вентилятор охлаждения, проверенная СБИС вынимается из обесточенного КУ 13.

ИСПЫТАНИЯ СБИС В АВТОНОМНОМ РЕЖИМЕ

Подготовка тестера-верификатора к автономной работе осуществляется с помощью управляющей ЭВМ следующим образом. С помощью консоли 22 ручного управления, которая предназначена для задания режимов работы тестера-верификатора и управления его работой в автономном режиме, блок 23 управления конфигурированием управляющей ПЛИС 8 переводится в режим конфигурирования управляющей ПЛИС 8 и загружается из памяти 25 конфигурации автономного режима. Первоначально память 25 конфигурации автономного режима загружается по внешнему порту 4 контроля и управления JTAG средствами САПР ПЛИС.

После включения питания и загрузки автономной конфигурации в управляющую ПЛИС 8, предварительно по внешнему порту 2 сетевого интерфейса осуществляется запись энергонезависимой памяти 18 подпрограмм настройки параметров испытаний и, через контроллер 19 энергонезависимой памяти программ испытаний, которая также предварительно подключается к внешнему порту 20.

После данных предварительных настроек тестер-верификатор становится готовым к самостоятельной работе без управляющей ЭВМ и может быть от нее отключен.

Программы испытаний, хранящиеся на внешней энергонезависимой памяти, подключаемой к внешнему порту 20 выполняются последовательно и состоят из следующих этапов:

- загрузка параметров (напряжение питания, рабочая частота и частота обмена, температура испытания) с помощью подпрограмм из энергонезависимой памяти 18;

- включение питания испытуемой СБИС;

- загрузка рабочей программы в испытуемую СБИС, если необходимо;

- загрузка в память 6 исходных векторов воздействий и эталонных векторов реакций;

- запуск теста, анализ окончания теста и, в случае успешного окончания, переход к следующей программе.

Подпрограммы из энергонезависимой памяти 18 позволяют осуществлять автономную (без ЭВМ) установку частоты обмена, с использованием программируемого генератора 7 частоты обмена, рабочей частоты, с использованием программируемого генератора 11 рабочей частоты, напряжений питания, с использованием блока 15 управления питанием СБИС, и рабочих температур, с использованием блока 12 мониторинга состояния, по параметрам, содержащимся в программах испытаний.

Консоль 22 ручного управления позволяет устанавливать:

- режим работы (с управляющей ЭВМ или без) (переключатель);

- подавать питание на тестер-верификатор (выключатель);

- разрешать управлять питанием СБИС (выключатель);

- осуществлять общий сброс (кнопка);

- выполнить очередной запуск тестирования (кнопка);

- устанавливать автоматический или шаговый (по одной программе) порядок выполнения программ испытаний (переключатель).

Блок 21 отображения состояния предназначен для индикации текущего состояния тестера-верификатора, к которому относится:

- наличие питания на тестере-верификаторе (включено/выключено);

- наличие питания на испытуемом СБИС (включено/выключено);

- режим работы (с управляющей ЭВМ или без);

- конфигурация управляющей ПЛИС (да/нет);

- готовность к запуску программы испытания (да/нет);

- завершение испытания СБИС (да/нет);

- ошибки при проведении испытаний (да/нет);

- код временной группы испытуемого СБИС;

- код температурная группы испытуемого СБИС.

Блок 24 управления стабилизацией температурного режима предназначен для сравнения текущей температуры испытуемого СБИС с заданной по программе, и для управления стабилизацией температуры в процессе выполнения проверки путем взаимодействия с блоком 26 управления скоростью вращения вентилятора охлаждения предназначенного для плавного изменения скорости вентилятора охлаждения (на чертеже не показан).

Проведение испытаний больших партий заказных СБИС осуществляется тестером-верификатором на индивидуальных рабочих местах без управляющей ЭВМ в автоматическом режиме следующим образом.

После установки очередного испытуемого заказного СБИС в КУ 13 на консоли 22 ручного управления устанавливается режим конфигурирования управляющей ПЛИС 8 через блок 23 управления конфигурированием из памяти 25 конфигурации автономного режима, разрешение управление питанием СБИС и подается питание на тестер-верификатор. В случае успешного конфигурирования управляющей ПЛИС 8, о чем свидетельствует соответствующий индикатор блока 21 отображения, без подачи питания на испытуемый СБИС выполняется проверка короткого замыкания питания СБИС с землей. Наличие короткого замыкания говорит о неисправности СБИС или о некорректной ее установке в КУ 13. После проверки корректности установки СБИС в КУ 13 и наличии короткого замыкания СБИС отбраковывается.

При отсутствии короткого замыкания питания СБИС с землей из энергонезависимой памяти программ, подключаемой к внешнему порту 20 последовательно считываются и выполняются все программы в соответствии с их содержанием в автоматическом или шаговом режиме, заданному на консоли 22 ручного управления.

Каждая программа из внешней энергонезависимой памяти программ состоит из двух частей. В первой части осуществляется настройка параметров испытания: напряжение питания, рабочая частота и частота обмена, а также стабилизируемая температура испытуемого СБИС, что осуществляется выполнением соответствующих подпрограмм из энергонезависимой памяти 18 подпрограмм настройки параметров. Во второй части сначала осуществляется запись в память 6 исходных векторов воздействий и эталонных векторов реакций, затем вектора воздействий из памяти 6 выдаются на испытуемую СБИС, а результаты тестирования автоматически сравниваются с соответствующими эталонными векторами реакций для выработки признаков "годен" или "брак".

В автоматическом режиме исполнения программ испытаний осуществляется последовательное выполнение всех программ из внешней энергонезависимой памяти программ испытания, подключаемой к внешнему порту 20, с соответствующими им параметрами. При шаговом выполнении испытаний требуется давать старт каждой программе через консоль управления 22, что бывает необходимо для детализации ошибок испытаний.

Если среди программ испытаний присутствуют программы определения временных и температурных характеристик СБИС, то по окончанию испытаний на блоке 21 отображения будут зафиксированы коды временной и температурной группы испытуемого заказного СБИС.

Испытания СБИС для определения их технических характеристик осуществляются на специальных стресс-тестах, при которых СБИС наиболее подвержены ошибкам, как при увеличении рабочей частоты, так и при увеличении рабочей температуры. Так как энергопотребление СБИС, а, следовательно, и его температура сильно зависят от частоты его работы, то сначала определяется временная группа путем выполнения задачи на нескольких заданных рабочих частотах, зависящих от типа испытуемого СБИС при номинальной температуре. Это обеспечивается блоком 24 управления стабилизацией температурного режима путем сравнения текущей температуры СБИС с номинальной и изменения скорости вращения вентилятора охлаждения. Определенная таким образом рабочая частота будет с большой вероятностью определять его временную группу. Определение температурной группы исследуемого СБИС осуществляется путем проверки правильности его работы на данной частоте и при других (более высоких) стабилизированных температурах.

Подпрограммы настройки параметров испытаний соответствуют компонентам конкретного тестера-верификатора, записываются в энергонезависимую память 18 однократно. Программы испытаний соответствуют конкретному испытуемому СБИС и могут изменяться как при переходе испытаний от одного типа СБИС к другому, так и при доработке (модификации) системы испытаний конкретного СБИС. В связи с этим имеет предпочтение реализация памяти программ испытаний на внешнем носителе, подключаемому к внешнему порту 20, что также упрощает (облегчает) ее тиражирование.

Сокращение времени проверки партий заказных СБИС осуществляется за счет простого тиражирования рабочих мест и использования автоматической проверки заказных СБИС в автономном режиме. Кроме того испытания заказных СБИС на различных рабочих частотах в заданных температурных режимах позволяют расширить функциональные возможности тестера-верификатора за счет осуществления сортировки заказных СБИС по температурным и частотным характеристикам.\

ПРИМЕР ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Тестер-верификатор может быть выполнен на следующих элементах:

управляющая ПЛИС 8 - на микросхеме фирмы Xilinx ZYNQ-7 XC7Z007S-2CLG400E;

памяти 9 стартовой, 10 рабочей, и 25 конфигурации автономного режима управляющей ПЛИС 8 - на микросхемах на SPI-памяти N25Q064A11EF640;

блок 23 управления конфигурированием управляющей ПЛИС 8 с использованием микросхем CPLD ХС2С64А;

внешний порт 4 контроля и управления JTAG с использованием разъема MOLEX;

блок 12 мониторинга состояния - на микросхемах TMP461AIRUNT, МАХ6656 и МАХ1239ЕЕЕ;

программируемые генераторы 7 частоты обмена и 11 рабочей частоты - на микросхемах 570FCA000133DG.

память 6 данных и результатов тестирования - с использованием микросхем MT46H128M16LFDD-48;

энергонезависимая память 18 подпрограмм настройки параметров испытаний - с использованием микросхем NAND Flash памяти MTFC32GAXATEA-WT фирмы MICRON;

блок 24 управления стабилизацией температурного режима, блок 26 управления скоростью вращения вентилятора охлаждения и контроллер 19 энергонезависимой памяти программ испытаний с использованием микросхем CPLD ХС2С64А;

в качестве энергонезависимой памяти программ испытаний может быть использована micro SD card MTSD256AHC6MS-1WT фирмы MICRON;

в качестве внешнего порта 20 может использоваться Memory Card Sockets, фирмы MOLEX.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый тестер-верификатор решает поставленную задачу и соответствует заявляемому техническому результату - расширение функциональных возможностей тестирования за счет сортировки СБИС по температурным и частотным характеристикам и сокращение времени испытания заказных СБИС за счет автоматической проверки заказных СБИС в автономном режиме.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕСТЕР-ВЕРИФИКАТОР ЗАКАЗНЫХ СБИС | 2021 |

|

RU2777449C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ДИАГНОСТИЧЕСКИЙ КОМПЛЕКС | 2023 |

|

RU2815706C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ | 2018 |

|

RU2686004C1 |

| АВТОНОМНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ | 2019 |

|

RU2720556C1 |

| АВТОНОМНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ С СУБМОДУЛЯМИ | 2020 |

|

RU2748299C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ С ДИНАМИЧЕСКИМ ПЕРЕРАСПРЕДЕЛЕНИЕМ ВЫЧИСЛИТЕЛЬНЫХ РЕСУРСОВ | 2023 |

|

RU2823113C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2017 |

|

RU2677363C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ ДЛЯ МНОГОЗАДАЧНЫХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2021 |

|

RU2780169C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2019 |

|

RU2713757C1 |

| РЕКОНФИГУРИРУЕМАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2022 |

|

RU2798443C1 |

Изобретение относится к устройствам тестирования интегральных схем. Технический результат заключается в расширении функциональных возможностей тестирования за счет сортировки СБИС по температурным и частотным характеристикам и сокращении времени испытания заказных СБИС за счет автоматической проверки заказных СБИС в автономном режиме. Технический результат достигается за счет того, что в тестер-верификатор дополнительно введены энергонезависимая память подпрограмм настройки параметров испытаний, контроллер энергонезависимой памяти программ испытаний, внешний порт подключения энергонезависимой памяти программ испытаний, блок отображения состояния, консоль ручного управления, блок управления конфигурированием управляющей ПЛИС, блок управления стабилизацией температурного режима, память конфигурации автономного режима управляющей ПЛИС, блок управления скоростью вращения вентилятора охлаждения. 1 ил.

Тестер-верификатор, содержащий внешний порт (1) мониторинга состояния, внешний порт (2) сетевого интерфейса, внешний порт (3) интерфейса PCI_Express, внешний порт (4) контроля и управления JTAG, генератор (5) опорной частоты, память (6) данных и результатов тестирования, программируемый генератор (7) частоты обмена, управляющую ПЛИС (8), память (9) стартовой конфигурации, память (10) рабочей конфигурации, программируемый генератор (11) рабочей частоты, блок (12) мониторинга состояния, контактирующее устройство (13) с вентилятором и радиатором охлаждения, блок (14) управляемых источников питания и блок (15) управления питанием,

причем внешние порты (2) сетевого интерфейса, (3) интерфейса PCI_Express и (4) контроля и управления JTAG соединены с управляющей ПЛИС (8), которая соединена с генератором (5) опорной частоты, с памятью (6) данных и результатов тестирования, с программируемым генератором (7) частоты обмена, с программируемым генератором (11) рабочей частоты, с блоком (12) мониторинга состояния, с блоком (15) управления питанием и шинами (16) управления и обмена данными и (17) конфигурирования с контактирующим устройством (13) с вентилятором и радиатором охлаждения, которое соединено с программируемыми генераторами (7) частоты обмена и (11) рабочей частоты, блоком (12) мониторинга состояния и блоком (14) управляемых источников питания,

кроме того, внешний порт 4 контроля и управления JTAG соединен с контактирующим устройством (13) с вентилятором и радиатором охлаждения, а внешний порт (1) мониторинга состояния соединен с блоком (12) мониторинга состояния, который соединен с блоком (14) управляемых источников питания СБИС, которые соединены с блоком (15) управления питанием,

отличающийся тем, что в него дополнительно введены энергонезависимая память (18) подпрограмм настройки параметров испытаний, контроллер (19) энергонезависимой памяти программ испытаний, внешний порт (20) подключения энергонезависимой памяти программ испытаний, блок (21) отображения состояния, консоль (22) ручного управления, блок (23) управления конфигурированием управляющей ПЛИС (8), блок (24) управления стабилизацией температурного режима, память (25) конфигурации автономного режима управляющей ПЛИС (8), блок (26) управления скоростью вращения вентилятора охлаждения,

причем внешний порт (20) подключения энергонезависимой памяти программ испытаний соединен с контроллером (19) энергонезависимой памяти программ испытаний, который соединен с управляющей ПЛИС (8), которая соединена с энергонезависимой памятью (18) подпрограмм настройки параметров испытаний, блоком (21) отображения состояния, консолью (22) ручного управления, блоком (23) управления конфигурированием управляющей ПЛИС (8), блоком (24) управления стабилизацией температурного режима, который соединен с блоком (26) управления скоростью вращения вентилятора охлаждения и с блоком (12) мониторинга состояния,

кроме того, консоль (22) ручного управления соединена с блоком (21) отображения состояния и блоком (23) управления конфигурированием управляющей ПЛИС (8), который соединен с памятью (9) стартовой конфигурации, памятью (10) рабочей конфигурации и памятью (25) конфигурации автономного режима управляющей ПЛИС (8).

| АВТОНОМНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ С СУБМОДУЛЯМИ | 2020 |

|

RU2748299C1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| АВТОНОМНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ | 2019 |

|

RU2720556C1 |

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| US 9563599 B2, 07.02.2017. | |||

Авторы

Даты

2023-05-03—Публикация

2022-10-28—Подача