Изобретение относится к электротехнике и может быть использовано для управления вторичными источниками питания (ВИЛ).

Целью изобретения является расширение функциональных возможностей % устройства за счет обеспечения возможности работы устройства с быстродействующим ВИЛ с частотно-импульсной модуляцией (Ч ИМ) .

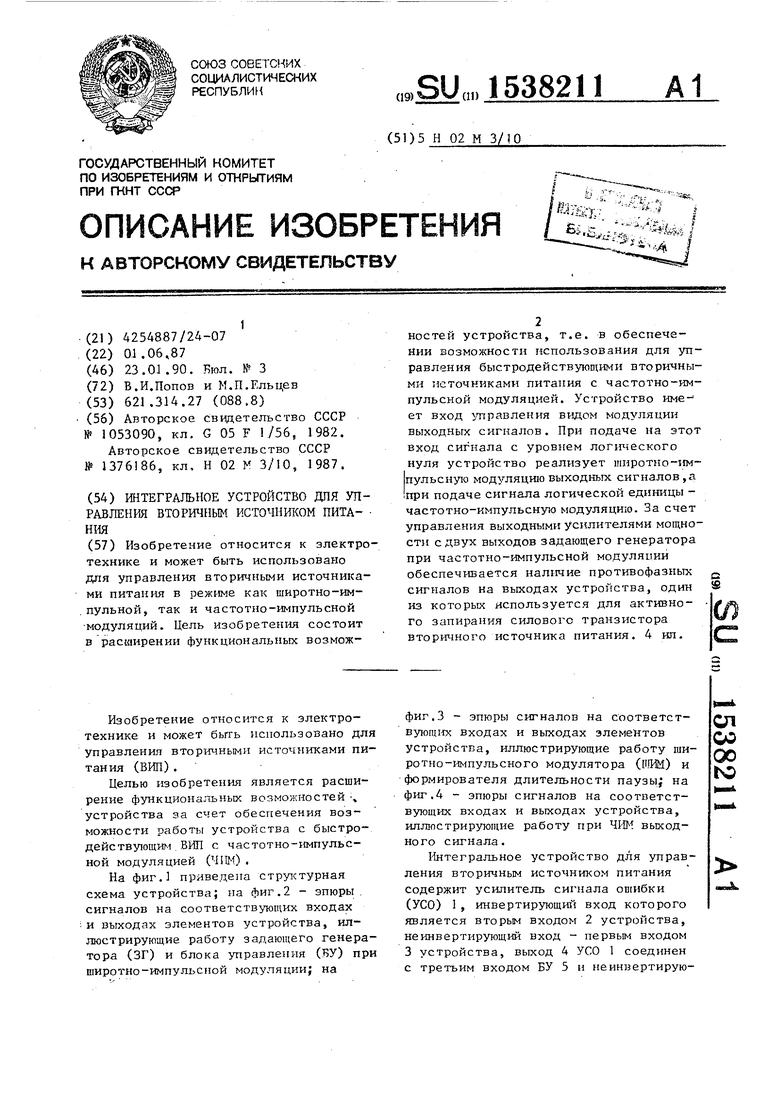

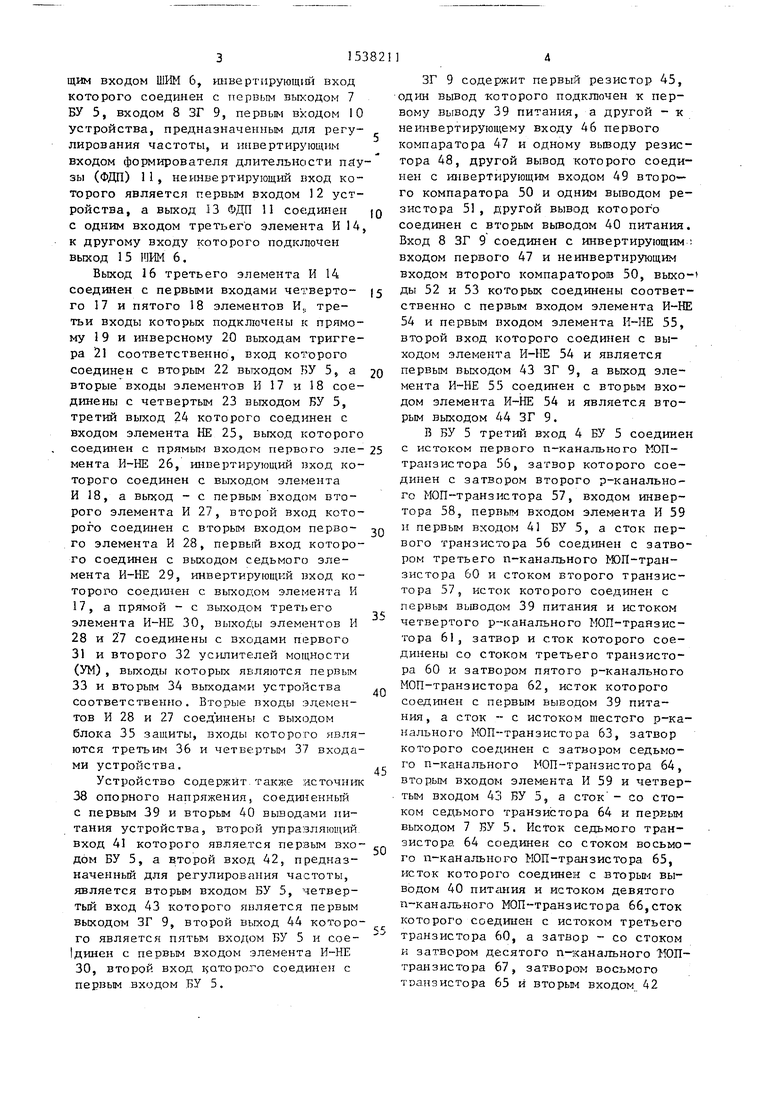

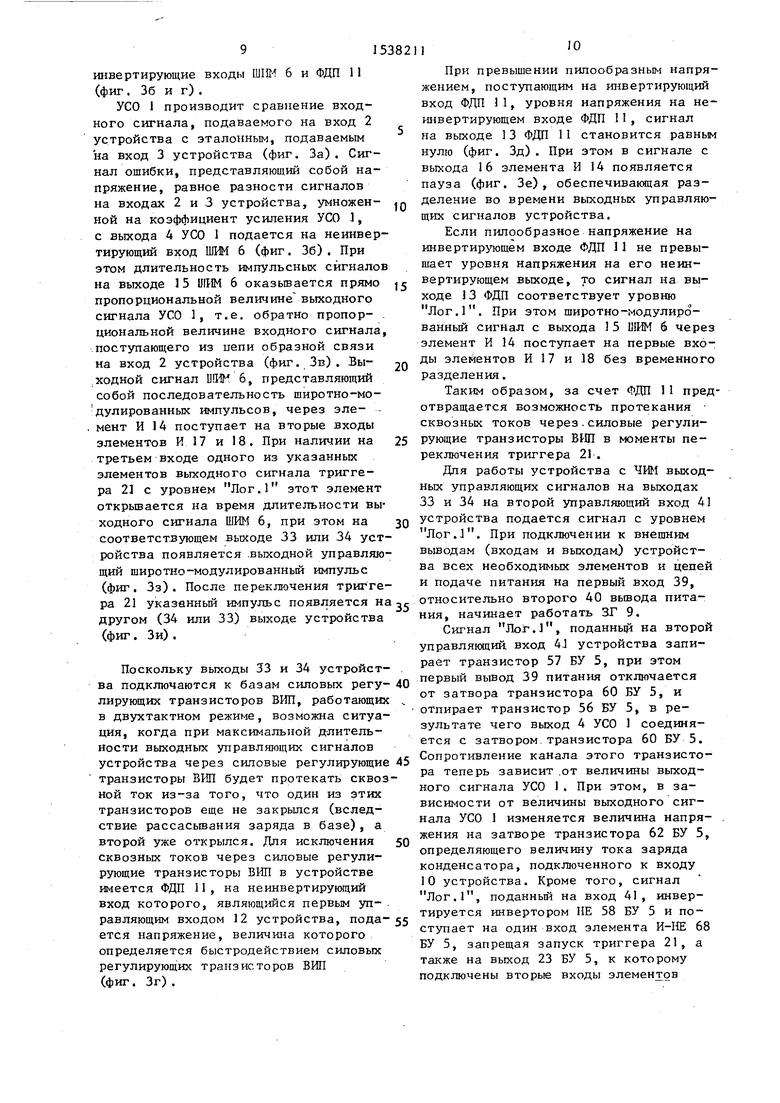

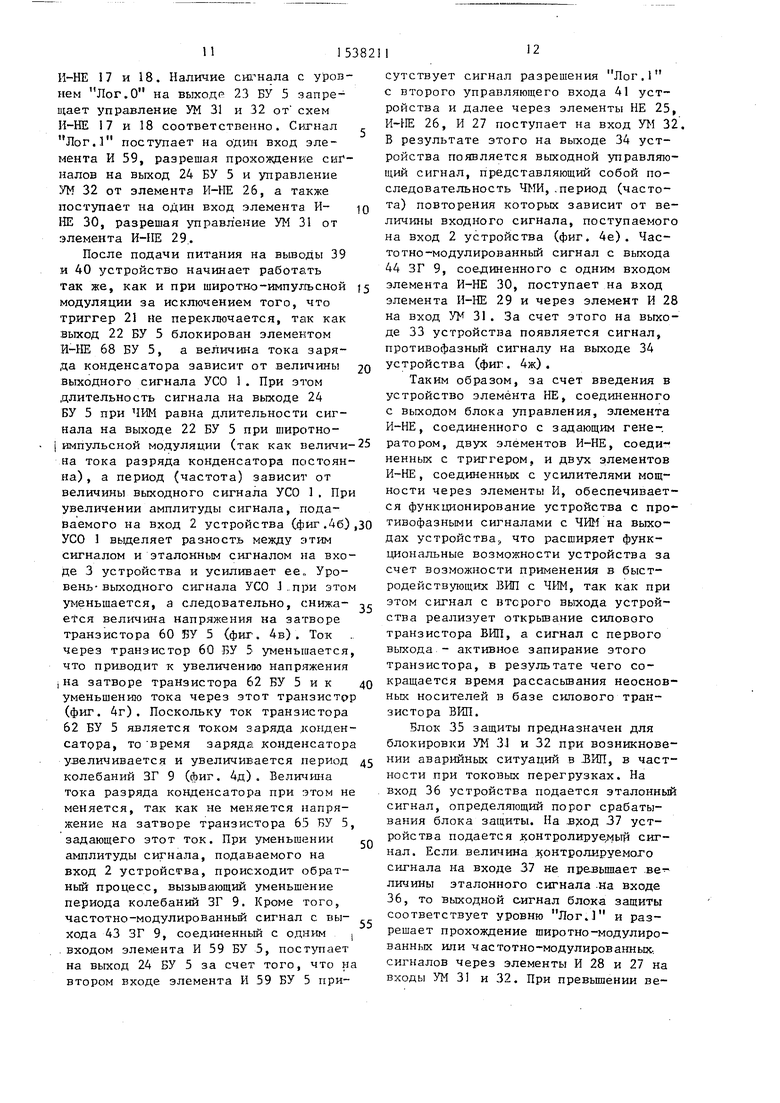

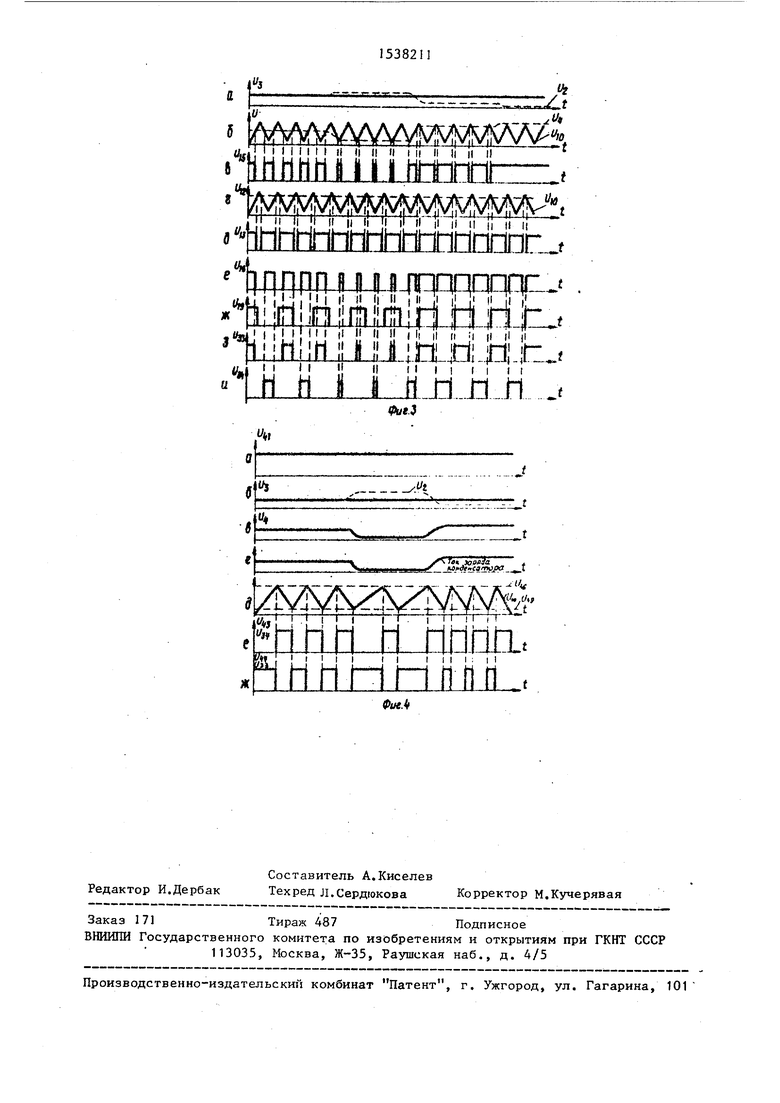

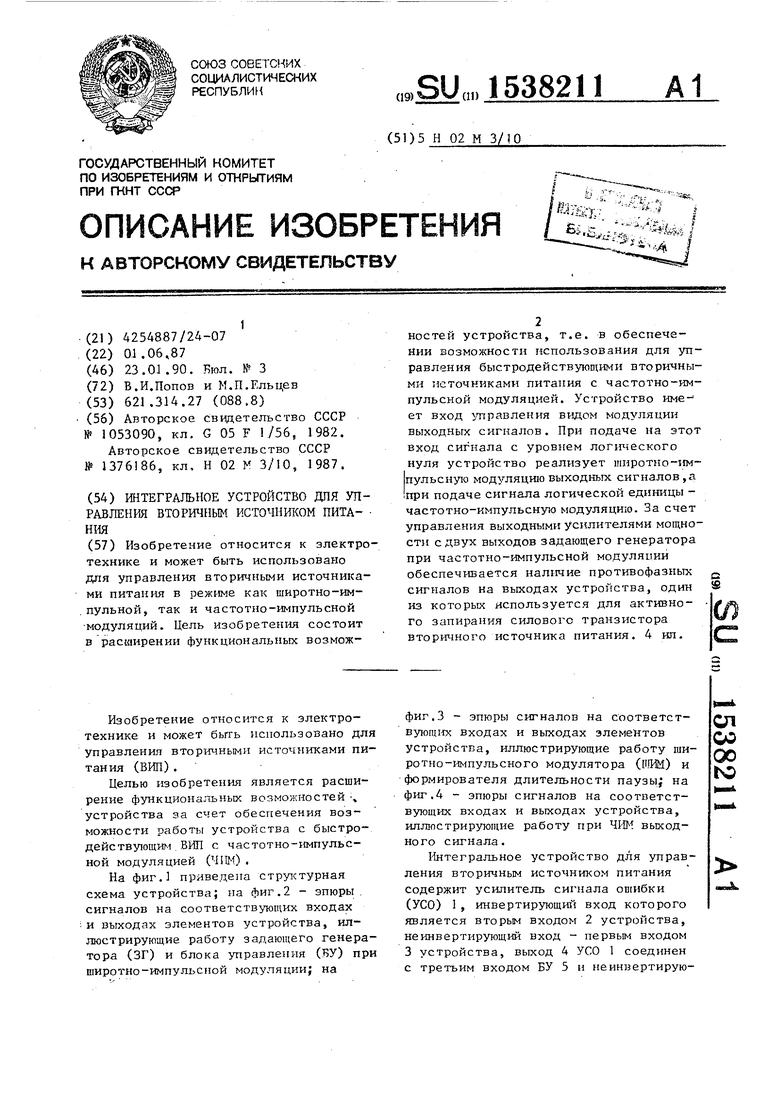

На фиг.1 приведена структурная схема устройства; на фиг.2 - эпюры сигналов на соответствующих входах и выход-чх элементов устройства, иллюстрирующие работу задающего генератора (ЗГ) и блока управления (БУ) при широтно-импульсной модуляции; на

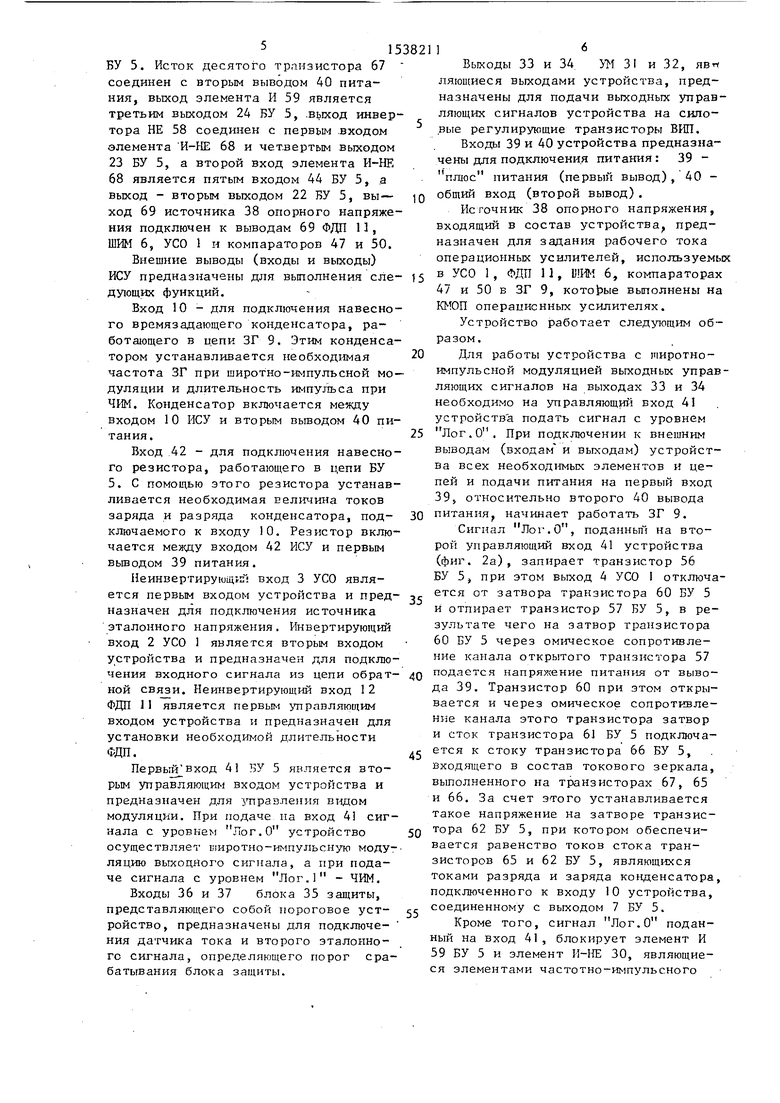

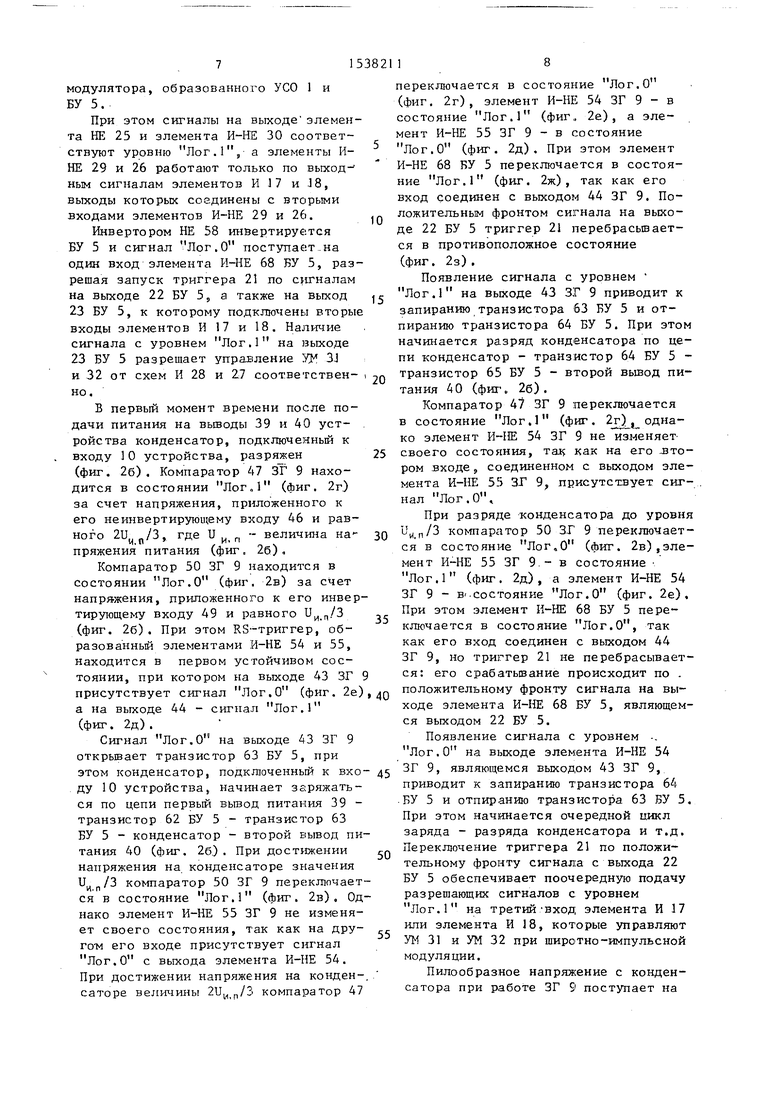

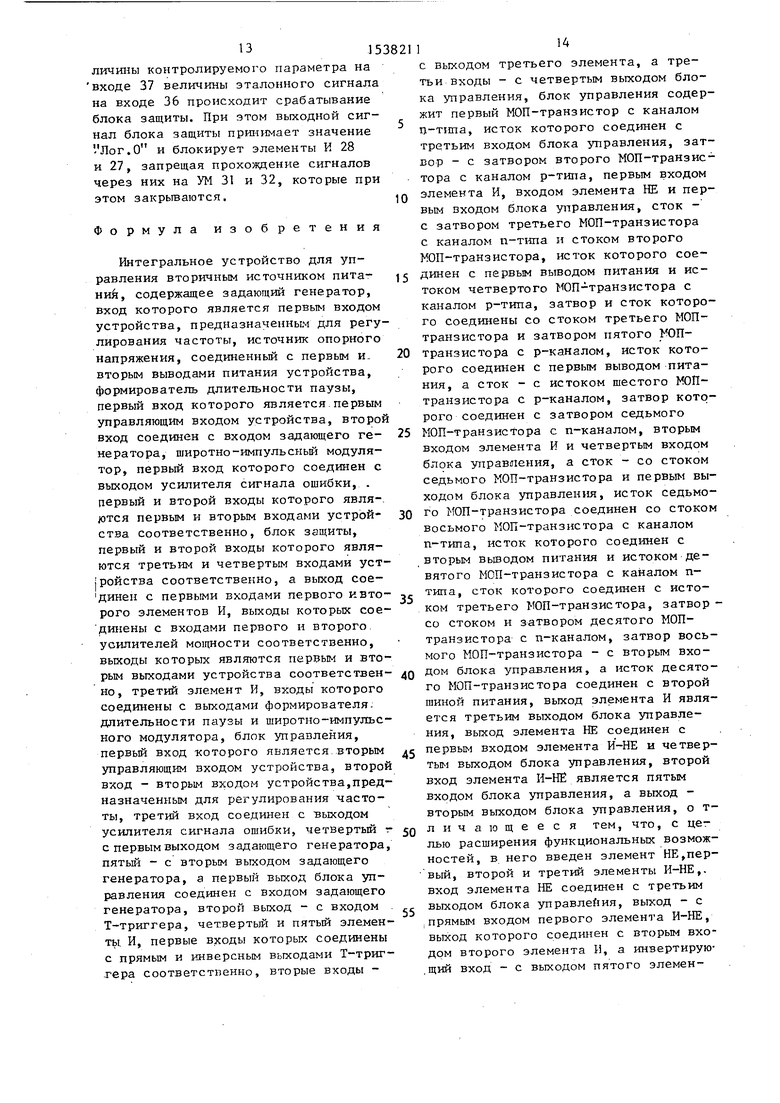

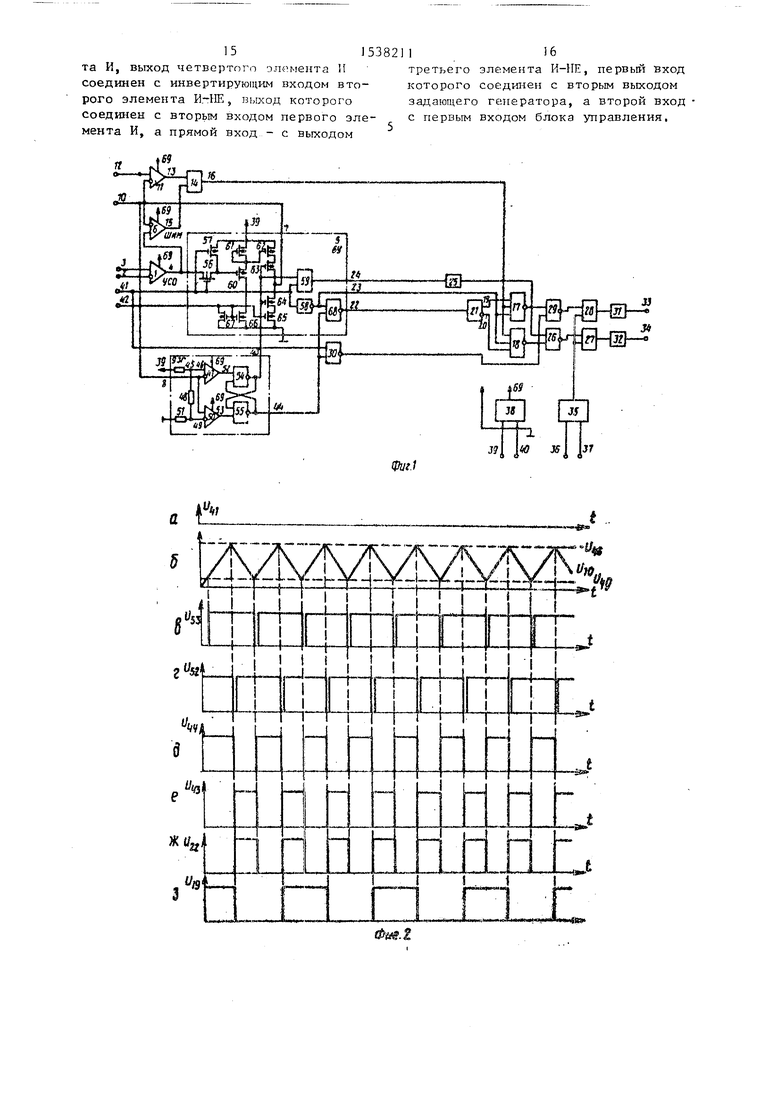

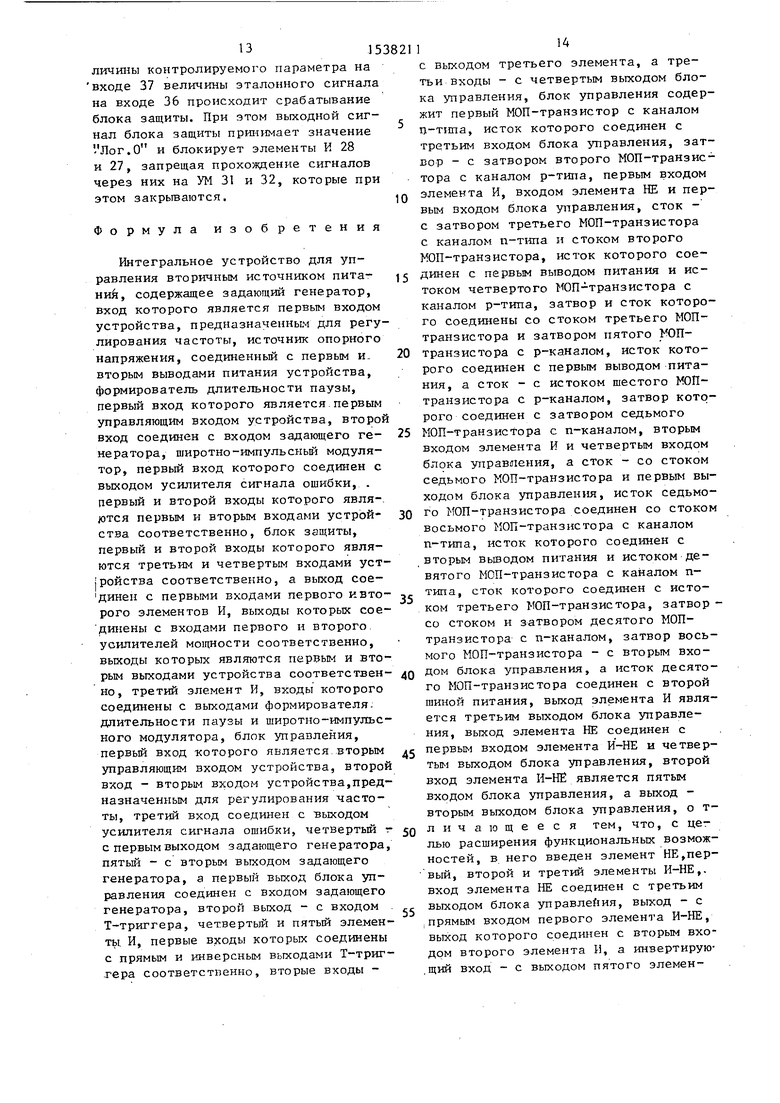

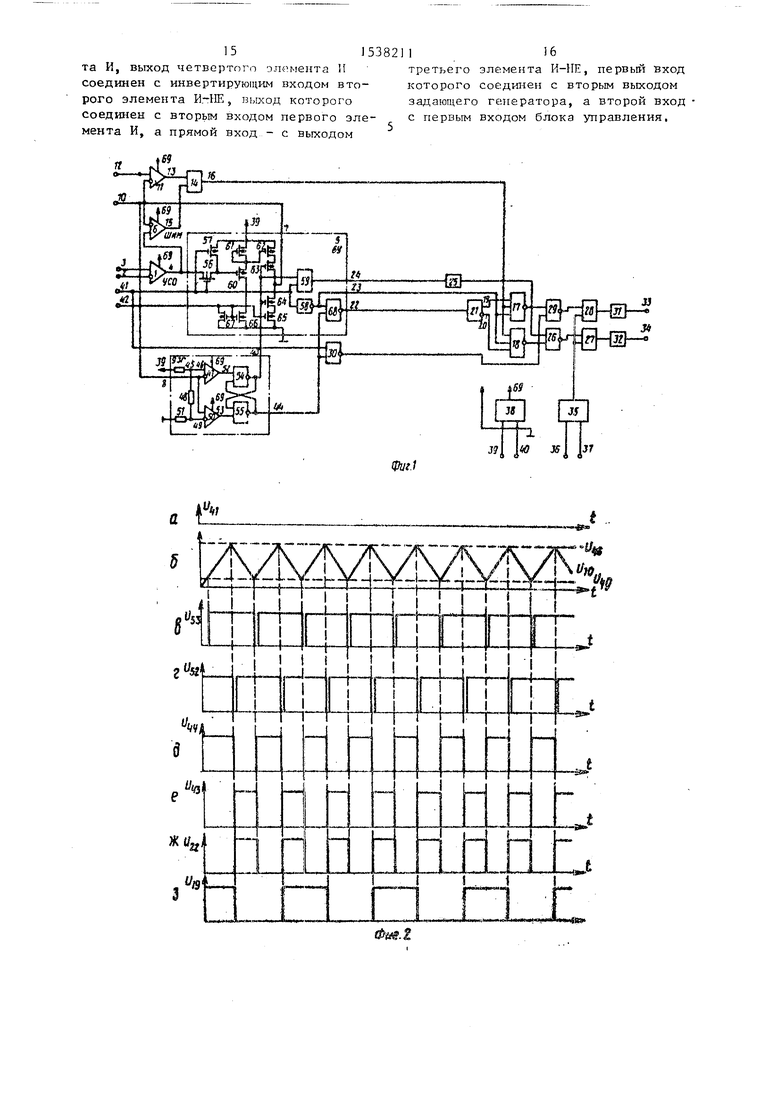

фиг.З - эпюры сигналов на соответствующих входах и выходах элементов устройства, иллюстрирующие работу широтно -импульсного модулятора (ШВД) и формирователя длительности паузы; на фиг.4 - эпюры сигналов на соответствующих входах и выходах устройства, иллюстрирующие работу при ЧИМ выходного сигнала.

Интегральное устройство для управления вторичным источником питания содержит усилитель сигнала ошибки (УСО) 1, инвертирующий вход которого является вторым входом 2 устройства, неинвертирующий вход - первым входом 3 устройства, выход 4 УСО 1 соединен с третьим входом БУ 5 и неинвертируюсд со

00

го

3153

щим входом ШИМ 6, инвертирующий вход которого соединен с первым выходом 7 БУ 5, входом 8 ЗГ 9, первым входом 10 устройства, предназначенным для регулирования частоты, и инвертирующим входом формирователя длительности паузы (ФДП) 11, неинвертирующий вход которого является первым входом 12 устройства, а выход 13 ФДП 11 соединен с одним входом третьего элемента И 14, к другому входу которого подключен выход 15 1ЧИМ 6.

Выход 16 третьего элемента И 14 соединен с первыми входами четверто- го 17 и пятого 18 элементов И,, третьи входы которых подключены к прямому 1 9 и инверсному 20 выходам триггера 21 соответственно, вход которого соединен с вторым 22 вьгходом БУ 5, а вторые входы элементов И 17 и 18 соединены с четвертым 23 выходом БУ 5, третий выход 24 которого соединен с входом элемента НЕ 25, выход которого соединен с прямым входом первого эле- мента И-НЕ 26, инвертирующий вход, которого соединен с выходом элемента И 18, а выход - с первым входом второго элемента И 27, второй вход которого соединен с вторым входом первого элемента И 28, первый вход которо го соединен с выходом седьмого элемента И-НЕ 29, инвертирующий вход которого соединен с выходом элемента И 17, а прямой - с выходом третьего элемента И-НЕ 30, выхоДы элементов И 28 и 27 соединены с входами первого 31 и второго 32 усилителей мощности (УМ), выходы которых являются первым 33 и вторым 34 выходами устройства соответственно. Вторые входы элементов И 28 и 27 соединены с выходом блока 35 защиты, входы которого являются третьим 36 и четвертым 37 входами устройства.

Устройство содержит также источник 38 опорного напряжения, соединенный с первым 39 и вторым 40 выводами питания устройства, второй управляющий вход 41 которого является первым входом БУ 5, а второй вход 42, предназначенный для регулирования частоты, является вторым входом БУ 5, четвертый вход 43 которого является первым выходом ЗГ 9, второй выход 44 которо- го является пятым входом БУ 5 и сое- 1динен с первым входом элемента И-НЕ 30, второй вход каторото соединен с первым входом БУ 5.

0

21

Q

5 5

0

35

40

45

50

1Л

ЗГ 9 содержит первый резистор 45, один вывод -которого подключен к первому выводу 39 питания, а другой - к не инвертирующему входу 46 первого компаратора 47 и одному выводу резистора 48, другой вывод которого соединен с инвертирующим входом 49 второго компаратора 50 и одним выводом резистора 51, другой вывод которого соединен с вторым выводом 40 питания. Вход 8 ЗГ 9 соединен с инвертирующим : входом первого 47 и неинвертирующим входом второго компараторов 50, выхо- ды 52 и 53 которых соединены соответственно с первым входом элемента И-НЕ 54 и первым входом элемента И-НЕ 55, второй вход которого соединен с выходом элемента И-НЕ 54 и является первым выходом 43 ЗГ 9, а выход элемента И-НЕ 55 соединен с вторым входом элемента И-НЕ 54 и является вторым выходом 44 ЗГ 9.

В ВУ 5 третий вход 4 БУ 5 соединен с истоком первого п-канального КОП- транэистора 56, затвор которого соединен с затвором второго р-канально- го МОП-транзистора 57, входом инвертора 58, первым входом элемента И 59 и первым входом 41 БУ 5, а сток первого транзистора 56 соединен с затвором третьего п-канального МОП-транзистора 60 и стоком второго транзистора 57, исток которого соединен с первым выводом 39 питания и истоком четвертого р-канального МОП-траНзис- тора 61, затвор и сток которого соединены со стоком третьего транзистора 60 и затвором пятого р-канального МОП-транзистора 62, исток которого соединен с первым выводом 39 питания, а сток - с истоком шестого р-канального МОП-транзистора 63, затвор которого соединен с затвором седьмого п-канального МОП-транзистора 64, вторым входом элемента И 59 и четвертым входом 43 БУ 5, а сток - со стоком седьмого транзистора 64 и первым выходом 7 БУ 5. Исток седьмого транзистора 64 соединен со стоком восьмого п-канального МОП-транзистора 65, исток которого соединен с вторым выводом 40 питания и истоком девятого п-канального МОП-транзистора 66,сток которого соединен с истоком третьего транзистора 60, а затвор - со стоком и затвором десятого n-каналъного 1ЮП- транзистора 67, затвором восьмого тоанзистора 65 и вторым входом 42

БУ 5. Исток десятого транзистора 67 соединен с вторым выводом 40 питания, выход элемента И 59 является третьим выходом 24 БУ 5, выход инвертора НЕ 58 соединен с первым входом элемента И-НЕ 68 и четвертым выходом 23 БУ 5, а второй вход элемента И-НЕ 68 является пятым входом 44 БУ 5, а выход - вторым выходом 22 БУ 5, вы- Q ход 69 источника 38 опорного напряжения подключен к выводам 69 ФДП 1, ШИМ 6, УСО 1 и компараторов 47 и 50.

Внешние выводы (входы и выходы) ИСУ предназначены для выполнения еле- 15 дующих функций.

Вход 10 - для подключения навесного времязадающего конденсатора, работающего в иепи ЗГ 9. Этим конденсатором устанавливается необходимая20 частота ЗГ при широтно-импульсной модуляции и длительность импульса при ЧИМ. Конденсатор включается между входом 10 ИСУ и вторым выводом 40 питания.

Вход 42 - для подключения навесного резистора, работающего в цепи БУ 5. С помощью этого резистора устанавливается необходимая величина токов заряда и разряда конденсатора, под- 30 ключаемого к входу 10. Резистор включается между входом 42 ИСУ и первым выводом 39 питания.

Неинвертируклций вход 3 УСО явля25

Выходы 33 и 34 УМ 31 и 32, яв ляющиеся выходами устройства, предназначены для подачи выходных управ ляющих сигналов устройства на силовые регулирующие транзисторы ВИЛ.

Входы 39 и 40 устройства предназна чены для подключения питания: 39 - плюс питания (первый вывод), 40 - общий вход (второй вывод).

Источник 38 опорного напряжения, входящий в состав устройства, предназначен для задания рабочего тока операционных усилителей, используем в УСО 1, ФДП П, ШИМ 6, компаратора 47 и 50 в ЗГ 9, которые выполнены н КМОП операционных усилителях.

Устройство работает следующим об разом.

Для работы устройства с пшротно- импульсной модуляцией выходных упра ляющих сигналов на выходах 33 и 34 необходимо на управляющий вход 41 устройства подать сигнал с уровнем Лог.О. При подключении к внешним выводам (входам и выходам) устройст ва всех необходимых элементов и цепей и подачи питания на первый вход 39, относительно второго 40 вывода питания, начинает работать ЗГ 9.

Сигнал Лог.О, поданный на второй управляющий вход 41 устройства (фиг. 2а), запирает транзистор 56 БУ 5} при этом выход 4 УСО I отключ

ется первым входом устройства и пред- 35 ется от затвора транзистора 60 БУ 5 назначен для подключения источника эталонного напряжения. Инвертирующий УСО 1 является вторым входом

вход 2

устройства и предназначен для подключения входного сигнала из цепи обрат- 40 ной связи. Неинвертирующий вход 12 ФДП 1 является первым управляющим входом устройства и предназначен для установки необходимой длительности ФДП.45

Первый вход 4 БУ 5 является вторым управляющим входом устройства и предназначен для управления видом модуляции. При подаче па вход 4 сигнала с уровнем Лог.О устройство50 осуществляет широтно-импульсную модуляцию выходного сигнала, а при подаче сигнала с уровнем Лог.1 - ЧИМ.

Входы 36 и 37 блока 35 защиты, представляющего собой пороговое уст- $5 ройство, предназначены для подключения датчика тока и второго эталонного сигнала, определяющего порог срабатывания блока защиты.

и отпирает транзистор 57 БУ 5, в ре зультате чего на затвор транзистора 60 БУ 5 через омическое сопротивление канала открытого транзистора 57 подается напряжение питания от вывода 39. Транзистор 60 при этом открывается и через омическое сопротивление канала этого транзистора затвор и сток транзистора 61 БУ 5 подключается к стоку транзистора 66 БУ 5, входящего в состав токового зеркала, выполненного на транзисторах 67, 65 и 66. За счет этого устанавливается такое напряжение на затворе транзистора 62 БУ 5, при котором обеспечивается равенство токов стока транзисторов 65 и 62 БУ 5, являющихся токами разряда и заряда конденсатора подключенного к входу 10 устройства, соединенному с выходом 7 БУ 5.

Кроме того, сигнал Лог.О поданный на вход 41, блокирует элемент И 59 БУ 5 и элемент Н-НЕ 30, являющиеся элементами частотно-импульсного

Q

5

0

0

5

Выходы 33 и 34 УМ 31 и 32, яв ляющиеся выходами устройства, предназначены для подачи выходных управляющих сигналов устройства на силовые регулирующие транзисторы ВИЛ.

Входы 39 и 40 устройства предназначены для подключения питания: 39 - плюс питания (первый вывод), 40 - общий вход (второй вывод).

Источник 38 опорного напряжения, входящий в состав устройства, предназначен для задания рабочего тока операционных усилителей, используемых в УСО 1, ФДП П, ШИМ 6, компараторах 47 и 50 в ЗГ 9, которые выполнены на КМОП операционных усилителях.

Устройство работает следующим образом.

Для работы устройства с пшротно- импульсной модуляцией выходных управляющих сигналов на выходах 33 и 34 необходимо на управляющий вход 41 устройства подать сигнал с уровнем Лог.О. При подключении к внешним выводам (входам и выходам) устройства всех необходимых элементов и цепей и подачи питания на первый вход 39, относительно второго 40 вывода питания, начинает работать ЗГ 9.

Сигнал Лог.О, поданный на второй управляющий вход 41 устройства (фиг. 2а), запирает транзистор 56 БУ 5} при этом выход 4 УСО I отключается от затвора транзистора 60 БУ 5

и отпирает транзистор 57 БУ 5, в результате чего на затвор транзистора 60 БУ 5 через омическое сопротивление канала открытого транзистора 57 подается напряжение питания от вывода 39. Транзистор 60 при этом открывается и через омическое сопротивление канала этого транзистора затвор и сток транзистора 61 БУ 5 подключается к стоку транзистора 66 БУ 5, входящего в состав токового зеркала, выполненного на транзисторах 67, 65 и 66. За счет этого устанавливается такое напряжение на затворе транзистора 62 БУ 5, при котором обеспечивается равенство токов стока транзисторов 65 и 62 БУ 5, являющихся токами разряда и заряда конденсатора, подключенного к входу 10 устройства, соединенному с выходом 7 БУ 5.

Кроме того, сигнал Лог.О поданный на вход 41, блокирует элемент И 59 БУ 5 и элемент Н-НЕ 30, являющиеся элементами частотно-импульсного

модулятора, образованного УСО 1 и БУ 5. При этом сигналы на выходе элемента НЕ 25 и элемента И-НЕ 30 соответствуют уровню Лог.1,- а элементы И- НЕ 29 и 26 работают только по выход- ным сигналам элементов И 17 и J8, выходы которых соединены с вторыми входами элементов И-НЕ 29 и 26.

Инвертором НЕ 58 инвертируемся БУ 5 и сигнал Лог.О поступает.на один вход элемента И-НЕ 68 БУ 5, разрешая запуск триггера 21 по сотналам на выходе 22 БУ 5, а также на выход 23 БУ 5, к которому подключены вторые входы элементов И 17 и 18. Наличие сигнала с уровнем Лог.1 на выходе 23 БУ 5 разрешает управление W 3J и 32 от схем И 28 и 27 соответствен- но.

В первый момент времени после подачи питания на выводы 39 и 40 устройства конденсатор, подключенный к входу 10 устройства, разряжен

(фиг. 2б). Компаратор 47 ЗГ 9 находится в состоянии Лог„1 (фиг. 2г) за счет напряжения, приложенного к его неинвертирующему входу 46 и равного 2U /3, где U и% п - величина на пряжения питания (фиг. 2б)„

Компаратор 50 ЗГ 9 находится в состоянии Лог.О (фиг. 2в) за счет напряжения, приложенного к его инвертирующему входу 49 и равного (фиг. 2б). При этом RS -триггер, образованный элементами И-НЕ 54 и 55, находится в первом устойчивом состоянии, при котором на выходе 43 ЗГ 9 присутствует сигнал Лог.О (фиг. 2е) а на выходе 44 - сигнал Лог. (фиг. 2д) .

Сигнал Лог.О на выходе 43 ЗГ 9 открывает транзистор 63 БУ 5, при этом конденсатор, подключенный к вхо ду 10 устройства, начинает заряжаться по цепи первый вывод питания 39 - транзистор 62 БУ 5 - транзистор 63 БУ 5 - конденсатор - второй вывод питания 40 (фиг. 26.) . При достижении напряжения на конденсаторе значения UMn/3 компаратор 50 ЗГ 9 переключается в состояние Лог.1 (фиг. 2в). Однако элемент И-НЕ 55 ЗГ 9 не изменяет своего состояния, так как на дру- го-м его входе присутствует сигнал Лог.О с выхода элемента И-НЕ 54. При достижении напряжения на конденсаторе величины компаратор 47

переключается в состояние Лог.О (фиг. 2г), элемент И-НЕ 54 ЗГ 9 - в состояние Лог.1 (фиг,, 2е) , а элемент И-НЕ 55 ЗГ 9 - в состояние Лог.О (фиг. 2д). При этом элемент И-НЕ 68 БУ 5 переключается в состояние Лог.1 (фиг. 2ж), так как его вход соединен с выходом 44 ЗГ 9. Положительным фронтом сигнала на выходе 22 БУ 5 триггер 21 перебрасывается в противоположное состояние (фиг. 2з).

Появление сигнала с уровнем Лог.1 на выходе 43 ЗГ 9 приводит к запиранию транзистора 63 БУ 5 и отпиранию транзистора 64 БУ 5. При этом начинается разряд конденсатора по цепи конденсатор - транзистор 64 БУ 5 - транзистор 65 БУ 5 - второй вывод питания 40 (фиг„ 2б).

Компаратор 4 ЗГ 9 переключается в состояние Лог.1 (фиг. 2jr)a однако элемент И-НЕ 54 ЗГ 9 не изменяет своего состояния, так как на его .втором входе, соединенном с выходом элемента И-НЕ 55 ЗГ 9, присутствует сигнал Лог.О,

При разряде конденсатора до уровня компаратор 50 ЗГ 9 переключается в состояние Лог.О (фиг. 2в),элемент И-НЕ 55 ЗГ 9.- в состояние Лог.1 (фиг. 2д), а элемент И-НЕ 54 ЗГ 9 - в-.состояние Лог.О (фиг. 2е) , При этом элемент И-НЕ 68 БУ 5 пере ключается в состояние Лог.О, так как его вход соединен с выходом 44 ЗГ 9, но триггер 21 не перебрасывается: его срабатывание происходит по . положительному фронту сигнала на выходе элемента И-НЕ 68 БУ 5, являющемся выходом 22 БУ 5.

Появление сигнала с уровнем -. Лог.О на выходе элемента И-НЕ 54 ЗГ 9, являющемся выходом 43 ЗГ 9, приводит к запиранию транзистора 64 .БУ 5 и отпиранию транзистора 63 БУ 5. При этом начинается очередной цикл заряда - разряда конденсатора и т.д. Переключение триггера 21 по положительному фронту сигнала с выхода 22 БУ 5 обеспечивает поочередную подачу разрешающих сигналов с уровнем Лог.1 на третий-вход элемента И 17 или элемента И 18, которые управляют УМ 31 и УМ 32 при широтно-импульсной модуляции.

Пилообразное напряжение с конденсатора при работе ЗГ 9 поступает на

инвертирующие входы ИЛИ- 6 и ФДП 11 (фиг. Зб и г) .

УСО 1 производит сравнение входного сигнала, подаваемого на вход 2 устройства с эталонным, подаваемым на вход 3 устройства (фиг. За). Сигнал ошибки, представляющий собой напряжение, равное разности сигналов на входах 2 и 3 устройства, умножен- ной на коэффициент усиления УСО 1, с выхода 4 УСО 1 подается на неинвертирующий вход ШИМ 6 (фиг. Зб). При этом длительность импульсных сигналов на выходе 15 ШИМ 6 оказывается прямо пропорциональной величине выходного сигнала УСО 1, т.е. обратно пропорциональной величине входного сигнала, поступающего из иепи образной связи на вход 2 устройства (фиг. Зв). Вы- ходной сигнал 111ИМ 6, представляющий собой последовательность широтно-мо- дулированных импульсов, через эле- - мент И 14 поступает на вторые входы элементов И 17 и 18. При наличии на третьем входе одного из указанных элементов выходного сигнала триггера 21 с уровнем Лог.1 этот элемент открывается на время длительности выходного сигнала ШИМ 6, при этом на соответствующем выходе 33 или 34 устройства появляется выходной управляющий широтно-модулированный импульс (фиг. Зз). После переключения триггера 21 указанный импульс появляется на другом (34 или 330 выходе устройства (фиг. Зи) .

Поскольку выходы 33 и 34 устройства подключаются к базам силовых регу- лирующих транзисторов ВИЛ, работающих в двухтактном режиме, возможна ситуация, когда при максимальной длительности выходных управляющих сигналов устройства через силовые регулирующие транзисторы ВИЛ будет протекать сквозной ток из-за того, что один из этих транзисторов еще не закрылся (вследствие рассасывания заряда в базе), а второй уже открылся. Для исключения сквозных токов через силовые регулирующие транзисторы ВИЛ в устройстве имеется ФДП 11, на неинвертирующий вход которого, являющийся первым управляющим входом 12 устройства, подается напряжение, величина которого определяется быстродействием силовых регулирующих транзисторов ВИЛ (фиг. Зг) .

При превышении пилообразным напряжением, поступающим на инвертирующий вход ФДП 11, уровня напряжения на неинвертирующем входе ФДП 11, сигнал на выходе 13 ФДП 11 становится равным нулю (фиг. Зд). При этом в сигнале с выхода 16 элемента И 14 появляется пауза (фиг. Зе), обеспечивающая разделение во времени выходных управляющих сигналов устройства.

Если пилообразное напряжение на инвертирующем входе ФДП 11 не превышает уровня напряжения на его неинвертирующем выходе, то сигнал на выходе J3 ФДП соответствует уровню Лог.1. При этом широтно-модулиро- ванный сигнал с выхода 15 ШИМ 6 через элемент И 14 поступает на первые входы элементов И 17 и 18 без временного разделения.

Таким образом, за счет ОДП 11 предотвращается возможность протекания сквозных токов через.силовые регулирующие транзисторы ВИЛ в моменты переключения триггера 21.

Для работы устройства с ЧИМ выходных управляющих сигналов на выходах 33 и 34 на второй управляющий вход 41 устройства подается сигнал с уровнем Лог.1. При подключении к внешним выводам (входам и выходам) устройства всех необходимых элементов и цепей и подаче питания на первый вход 39, относительно второго 40 вывода питания, начинает работать ЗГ 9.

Сигнал Лог.1, поданный на второй управляющий, вход 4J устройства запирает транзистор 57 БУ 5, при этом первый вывод 39 питания отключается от затвора транзистора 60 БУ 5, и отпирает транзистор 56 БУ 5, в результате чего выход 4 УСО 1 соединяется с затвором транзистора 60 БУ 5. Сопротивление канала этого транзистора теперь зависит от величины выходного сигнала УСО 1 . При этом, в зависимости от величины выходного сигнала УСО 1 изменяется величина напряжения на затворе транзистора 62 БУ 5, определяющего величину тока заряда конденсатора, подключенного к входу 10 устройства. Кроме того, сигнал Лог.1, поданный на вход 41, инвертируется инвертором НЕ 58 БУ 5 и поступает на один вход элемента И-НЕ 68 БУ 5, запрещая запуск триггера 21, а также на выход 23 БУ 5, к которому подключены вторые входы элементов

11

53821

И-НЕ 17 и 18. Наличие сигнала с уровнем Лог.О на выходг- 23 БУ 5 запрещает управление УМ 31 и 32 от схем И-НЕ 17 и 18 соответственно. Сигнал Jtor.l поступает на один вход элемента И 59, разрешая прохождение сигналов на выход 24 БУ 5 и управление УМ 32 от элемента И-НЕ 26, а также поступает на один вход эпемента И- НЕ 30, разрешая управление УМ 31 от элемента И-НЕ 29.

После подачи питания на выводы 39 и 40 устройство начинает работать так же, как и при широтно-импульсной модуляции за исключением того, что триггер 21 Не переключается, так как выход 22 БУ 5 блокирован элементом И-НЕ 68 БУ 5, а величина тока заряда конденсатора зависит от величины выходного сигнала УСО 1. При этом длительность сигнала на выходе 24 БУ 5 при ЧИМ равна длительности сигнала на выходе 22 БУ 5 при широтно- | импульсной модуляции (так как величина тока разряда конденсатора постоянна), а период (частота) зависит от величины выходного сигнала УСО 1. При увеличении амплитуды сигнала, подаваемого на вход 2 устройства (фиг.46} УСО 1 выделяет разность между сигналом и эталонным сигналом на входе 3 устройства и усиливает ее,, Уровень-выходного сигнала УСО J при этом уменьшается, а следовательно, снижа- ется величина напряжения на затворе транзистора 60 БУ 5 (фиг. 4в). Ток через транзистор 60 БУ 5 уменьшается, что приводит к увеличению напряжения i на затворе транзистора 62 БУ 5 и к уменьшению тока через этот транзистрр (фиг. 4г). Поскольку ток транзистора 62 БУ 5 является током заряда донден- сатора, то время заряда конденсатора увеличивается и увеличивается период колебаний ЗГ 9 (сЬиг. 4д) . Величина тока разряда конденсатора при этом не меняется, так как не меняется напряжение на затворе транзистора 65 БУ 5, задающего этот ток. При уменьшении амплитуды сигнала, подаваемого на вход 2 устройства, происходит обратный процесс, вызывающий уменьшение периода колебаний ЗГ 9. Кроме того, частотно-модулированный сигнал с вы- хода 43 ЗГ 9, соединенный с одним ( входом элемента И 59 БУ 5, поступает на выход 24 БУ 5 за счет того, что на втором входе элемента И 59 БУ 5 при112

сутствует сигнал разрешения Лог . 1 второго управляющего входа 41 устройства и далее через элементы НЕ 25, И-НЕ 26, И 27 поступает на вход УМ 32, В результате этого на выходе 34 устройства появляется выходной управляюий сигнал, представляющий собой последовательность ЧМИ,.период (частота) повторения которых зависит от веичины входного сигнала, поступаемого на вход 2 устройства (фиг. 4е). Частотно-модулированный сигнал с выхода 44 ЗГ 9, соединенного с одним входом элемента И-НЕ 30, поступает на вход элемента И-НЕ 29 и через элемент И 28 на вход УК 31. За счет этого на выходе 33 устройства появляется сигнал, противофазный сигналу на выходе 34 устройства (фиг. 4ж).

Таким образом, за счет введения в устройство элемента НЕ, соединенного с выходом блока управления, элемента И-НЕ, соединенного с задающим гене-. ратором, двух элементов И-НЕ, соеди ненных с триггером, и двух элементов И-НЕ, соединенных с усилителями мощности через элементы И, обеспечивается функционирование устройства с противофазными сигналами с ЧИМ на выходах устройства, что расширяет функциональные возможности устройства за счет возможности применения в быстродействующих ВИЛ с ЧИМ, так как при этом сигнал с второго выхода устройства реализует открывание силового транзистора ВИЛ, а сигнал с первого выхода - активное запирание этого транзистора, в результате чего сокращается время рассасывания неосновных носителей в базе силового транзистора ВКЛ.

Блок 35 защиты предназначен для блокировки УМ 3J и 32 при возникновении аварийных ситуаций в -ВИЛ, в частности при токовых перегрузках. На вход 36 устройства подается эталонньй сигнал, определяющий порог срабатывания блока защиты. На .вход 37 устройства подается контролируемый сигнал. Если величина контролируемого сигнала на входе 37 не превышает величины эталонного сигнала На входе 36, то выходной сигнал блока защиты соответствует уровню Лог.1 и разрешает прохождение широтно-модулированных или частотно-модулированных- сигналов через элементы И 28 и 27 на входы УМ 31 и 32. При превышении ве1315

личины контролируемого параметра на входе 37 величины эталонного сигнала на входе 36 происходит срабатывание блока защиты. При этом выходной сигнал блока защиты принимает значение Лог.О и блокирует элементы И 28 и 27, запрещая прохождение сигналов через них на УМ 31 и 32, которые при этом закрываются.

Формула изобретения

Интегральное устройство для управления вторичным источником пита- ния, содержащее задающий генератор, вход которого является первым входом устройства, предназначенным для регулирования частоты, источник опорного напряжения, соединенный с первым и„ вторым выводами питания устройства, формирователь длительности паузы, первый вход которого является первым управляющим входом устройства, второй вход соединен с входом задающего ге- нератора, широтно-импульсный модулятор, первый вход которого соединен с выходом усилителя сигнала ошибки, . первый и второй входы которого явля- #тся первым и вторым входами устрой- ства соответственно, блок защиты, первый и второй входы которого являются третьим и четвертым входами уст- (ройства соответственно, а выход сое- динен с первыми входами первого ивто- рого элементов И, выходы которых соединены с входами первого и второго усилителей мощности соответственно, выходы которых являются первым и вторым выходами устройства соответствен- но, третий элемент И, входы которого соединены с выходами формирователя, длительности паузы и широтно-импульсного модулятора, блок управления, первый вход которого является вторым управляющим входом устройства, второй вход - вторь м входом устройства,предназначенным для регулирования частоты, третий вход соединен с выходом усилителя сигнала ошибки, четвертый - с первым выходом задающего генератора, пятый - с вторым выходом задающего генератора, а первый выход блока управления соединен с входом задающего генератора, второй выход - с входом Т-триггера, четвертый и пятый элементы И, первые входы которых соединены с прямым и инверсным выходами Т-триг- тера соответственно, вторые входы 14

с выходом третьего элемента, а третьи входы - с четвертым выходом блока управления, блок управления содержит первый МОП-транзистор с каналом n-типа, исток которого соединен с третьим входом блока управления, затвор - с затвором второго МОП-транзистора с каналом р-типа, первым входом элемента И, входом элемента НЕ и первым входом блока управления, сток - с затвором третьего МОП-транзистора с каналом n-типа и стоком второго МОП-транзистора, исток которого соединен с первым выводом питания и истоком четвертого МОП-транзистора с каналом р-типа, затвор и сток которого соединены со стоком третьего МОП- транзистора и затвором пятого МОП- транзистора с р-каналом, исток которого соединен с первым выводом питания, а. сток - с истоком шестого МОП- транзистора с р-каналом, затвор которого соединен с затвором седьмого МОП-транзистора с n-каналом, вторым входом элемента И и четвертым входом блока управления, а сток - со стоком седьмого МОП-транзистора и первым выходом блока управления, исток седьмого МОП-транзистора соединен со стоком восьмого МОП-транзистора с каналом n-типа, исток которого соединен с вторым выводом питания и истоком девятого МСП-транзистора с каналом п- типа, сток которого соединен с истоком третьего МОП-транзистора, затвор - со стоком и затвором десятого МОП- транзистора с n-каналом, затвор восьмого МОП-транзистора - с вторым входом блока управления, а исток десятого МОП-транзистора соединен с второй шиной питания, выход элемента И является третьим выходом блока управления, выход элемента НЕ соединен с первым входом элемента И-НЕ и четвертым выходом блока управления, второй вход элемента И-НЕ является пятым входом блока управления, а выход - вторым выходом блока управления, о т- личающееся тем, что, с целью расширения функциональных возможностей, в него введен элемент НЕ,первый, второй и третий элементы И-НЕ,. вход элемента НЕ соединен с третьим выходом блока управлейия, выход - с прямым входом первого элемента И-НЕ, выход которого соединен с вторым входом второго элемента И, а инвертирующий вход - с выходом пятого элеменЯ

J7

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральное устройство для управления вторичным источником питания | 1986 |

|

SU1376186A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| Формирователь мощных наносекундных импульсов с лавинообразным переключением | 2019 |

|

RU2712098C1 |

| Способ хранения информации на МДП-транзисторе и запоминающий элемент для осуществления этого способа | 1977 |

|

SU943846A1 |

| ТРОИЧНЫЙ К-МОП-С ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИЛИ-НЕ" | 2011 |

|

RU2468510C1 |

| ТРОИЧНЫЙ К-МОП-С ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕ" | 2011 |

|

RU2481701C2 |

| Многоканальный коммутатор | 1989 |

|

SU1644373A1 |

| Усилитель считывания на КМДП транзисторах | 1984 |

|

SU1241285A1 |

| Способ быстрого включения силового транзистора с изолированным затвором и устройства с его использованием | 2018 |

|

RU2713559C2 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

Изобретение относится к электротехнике и может быть использовано для управления вторичными источниками питания в режиме как широтно-импульсной, так и частотно-импульсной модуляции. Цель изобретения состоит в расширении функциональных возможностей устройства, т.е.в обеспечении возможности использования для управления быстродействующими вторичными источниками питания с частотно-импульсной модуляцией. Устройство имеет вход управления видом модуляции выходных сигналов. При подаче на этот вход сигнала с уровнем логического нуля устройство реализует широтно-импульсную модуляцию выходных сигналов, а при подаче сигнала логической единицы - частотно-импульсную модуляцию. За счет управления выходными усилителями мощности с двух выходов задающего генератора при частотно-импульсной модуляции обеспечивается наличие противофазных сигналов на выходах устройства, один из которых используется для активного запирания силового транзистора вторичного источника питания. 4 ил.

«

u

и П мм и i ii ii 11 ii i и ц ц ц

а%|ШИИНИИНГ1МППГf

I/JVIK

11 ii II I I I l I I lii и I

fihhrtiHhhhmnnrihnr t

mnc

ifc.ii M i i i и и i i и i

MMiffiirtrlJlb

t

. j - К| -Н-|Л1..-§ Д т ft-..1 --Д i-r- 41« If

IM; i и i i ii ii i 5 I , ii „ ,,

1 Tii.riiiHiiiiiin i-i ..д .c.i

it

f i i

ii i i

ii i i i i i i

JLJLJLJUtJdJ3.J1 ..

Фае.)

m.

ihh И ПППП.

finnnnnn,.

л

t

iiin i-i ..д .c

it

f i i

ii i i

ii i i i i i i

UtJdJ3.J1

Jt

/ r«« jo wSi4

S fj dt tam}f a ..t

(/

| Импульсный стабилизатор постоянного напряжения | 1982 |

|

SU1053090A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Интегральное устройство для управления вторичным источником питания | 1986 |

|

SU1376186A1 |

Авторы

Даты

1990-01-23—Публикация

1987-06-01—Подача