Заявляемое техническое решение относится к автоматике и вычислительной технике, а также к системам автоматического управления и может найти применение в системах числового программного управления, в измерительных и вычислительных устройствах и при создании элементов импульсных нейронных сетей, в частности прототипов импульсных нейронов.

Известно устройство [Патент РФ №2006918, МПК G 06 F 7/68, 1994] реализующее формирование выходной частоты пропорционально входному коду, содержащее двоичный счетчик, элемент задержки, n-канальный мультиплексор, первый и второй элементы И, триггер и формирователь импульсов, первый вход первого элемента И соединен с выходом элемента задержки, выходы разрядов двоичного счетчика соединены с соответствующими адресными входами n-канального мультиплексора, нулевой информационный вход которого соединен с управляющим входом преобразователя, а информационные входы – со входами соответствующих разрядов цифрового входа преобразователя, причем первый информационных вход соединен со счетным входом двоичного счетчика и выходом второго элемента И, первый вход которого соединен со входом опорной частоты, с входом формирователя импульсов и со стробирующим входом n-канального мультиплексора, причем вход расширения, выход переноса, информационный вход, вход задания режима работы, счетный вход триггера и вход сброса соединены функционально соответствующим образом.

Недостатком преобразователя является отсутствие возможности воздействия на выходную частоту для снижения погрешности.

Из числа аналогов наиболее близким по совокупности признаков и по технической сущности является преобразователь кода в частоту [Патент РФ № 2285946, опубл. 20.10.2006], который и выбран в качестве прототипа.

В прототипе снижена погрешность преобразования за счет введения цифровой коррекции аддитивной и мультипликативной составляющих.

Преобразователь кода в частоту, содержащий вход опорной частоты F0, выход Fвых преобразователя, входную шину NG, двоичные умножители с цифровыми входами Nп и Nк, при этом каждый двоичный умножитель состоит из первого и второго двоичных счетчиков, и первого и второго мультиплексоров соответственно, а выходы разрядов первого и второго двоичных счетчиков соединены с соответствующими адресными входами первого и второго мультиплексоров, информационные входы которых являются соответствующими цифровыми входами Nп и Nк двоичных умножителей, а вход опорной частоты F0 преобразователя соединен со входами тактирования F первого и второго двоичных умножителей, одновременно являясь входами тактирования первого и второго двоичных счетчиков, а также нулевыми информационными входами первого и второго мультиплексоров соответственно, при этом выходы мультиплексоров Fy1 и Fy2 одновременно являются выходами первого и второго двоичных умножителей соответственно.

Кроме того, преобразователь содержит третий двоичный счетчик, три инвертора, три компаратора, третий мультиплексор, элемент И, вторую и третью входные шины, причем все входные шины подключены к соответствующим компараторам, которые управляются третьим двоичным счетчиком, а их выходы соединены соответственно с третьим инвертором и третьим двоичным счетчиком, с первым входом элемента И, со вторым входом элемента И, при этом выход элемента И соединен с нулевым входом двухканального мультиплексора, первый и второй выход которого подключены к выходам соответственно первого и второго двоичных умножителей, а выход этого мультиплексора является выходом всего преобразователя, причем первый и второй инвертор включены в цепи младших разрядов соответственно преобразуемого и корректирующего кодов, причем выход третьего инвертора соединен со вторым входом третьего двоичного счетчика, а третий вход этого третьего счетчика объединен со входом опорной частоты преобразователя.

Прототип работает следующим образом.

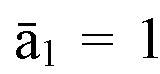

Пусть число разрядов первого двоичного умножителя равно четырем, а второго – двум. Пусть в начальный момент времени все двоичные счетчики находятся в нулевом состоянии, а на вход опорной частоты F0 подается входная импульсная последовательность, под воздействием которой двоичные счетчики могут изменять свои выходные значения. На вход первого инвертора подается старший (знаковый) разряд а1 входного преобразуемого кода Nп, а на вход второго инвертора – корректирующего кода Nк.

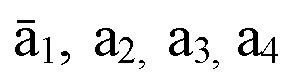

Таким образом, на цифровые входы первого и второго двоичных умножителей подаются коды  и

и  соответственно. Первый двоичный счетчик последовательно во времени формирует на своем выходе значения в диапазоне от 0 до 2n-1 = 15, а второй счетчик – от 0 до 2к-1 = 3. Выходные значения первого двоичного счетчика являются адресными входами первого мультиплексора.

соответственно. Первый двоичный счетчик последовательно во времени формирует на своем выходе значения в диапазоне от 0 до 2n-1 = 15, а второй счетчик – от 0 до 2к-1 = 3. Выходные значения первого двоичного счетчика являются адресными входами первого мультиплексора.

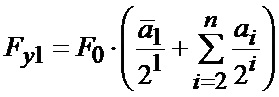

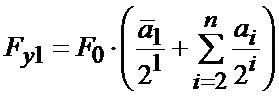

Так, при выходном значении первого двоичного счетчика равном «0», «2», «4», «6», «8», «10», «12» или «14», в выходную неравномерную последовательность импульсов Fy1 вставится импульс опорной частоты F0 преобразователя, если  . При входном значении первого двоичного счетчика, равном «1», «5», «9» или «13», в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а2 = 1. При выходном значении первого двоичного счетчика, равном «3» или «11», в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а3 = 1. При выходном значении первого двоичного счетчика, равном «7», в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а4 = 1. Выходная последовательность импульсов Fy1 на выходе первого двоичного умножителя характеризуется частотой

. При входном значении первого двоичного счетчика, равном «1», «5», «9» или «13», в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а2 = 1. При выходном значении первого двоичного счетчика, равном «3» или «11», в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а3 = 1. При выходном значении первого двоичного счетчика, равном «7», в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а4 = 1. Выходная последовательность импульсов Fy1 на выходе первого двоичного умножителя характеризуется частотой

,

,

где i – номер разряда преобразуемого кода Nпр.

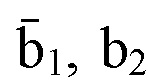

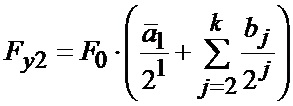

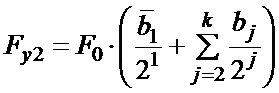

Выходные значения второго двоичного счетчика являются адресными входами второго мультиплексора. Так, при выходном значении второго двоичного счетчика, равном «0» или «2», в выходную неравномерную последовательность импульсов Fy2 вставится импульс опорной частоты F0 преобразователя, если b̄1 = 1. При выходном значении второго двоичного счетчика, равном «1», в выходную неравномерную последовательность импульсов Fy2 вставится импульс, если b2 = 1. Выходная последовательность импульсов Fy2 на выходе второго двоичного умножителя характеризуется частотой

,

,

где j – номер разряда корректирующего кода Nкорр.

Разрядность третьего двоичного счетчика равна n+1. Этот счетчик последовательно во времени формирует на своем выходе значения в диапазоне от 0 до 2n + 2k–1 = 19, а первый компаратор соответственно ограничивает диапазон изменения выходных значений третьего счетчика. Если выходное значение третьего двоичного счетчика меньше величины 2n + 2k–1 = 19, то на выходе первого компаратора формируется единичный сигнал, служащий сигналом разрешения счета третьего двоичного счетчика. В противном случае на выходе первого компаратора формируется нулевой сигнал. Третий инвертор инвертирует сигнал с выхода третьего компаратора. При нулевом сигнале на выходе первого компаратора выходной сигнал третьего инвертора равен единице. Когда выходной сигнал третьего инвертора равен единице, приходит сброс третьего двоичного счетчика в нулевое значение, после чего процесс счета возобновляется.

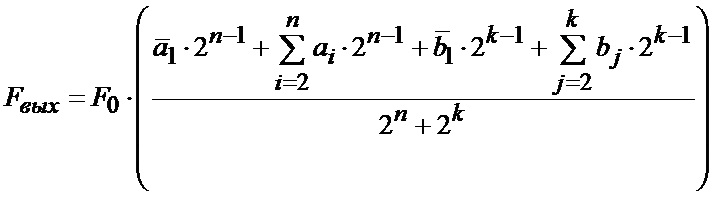

Второй компаратор сравнивает выходное значение третьего двоичного счетчика с константой ТN–1 = 15. Третий компаратор сравнивает выходное значение третьего двоичного счетчика с константой ТN + ТК= 20. Элемент И объединяет результаты сравнения второго и третьего компараторов. Если выходное значение третьего двоичного счетчика больше величины ТN–1 = 15 и при этом меньше величины ТN + ТК = 20, то на нулевой информационный вход третьего мультиплексора подается единичный сигнал, иначе подается сигнал равный нулю, и выходной частотно – импульсный поток преобразователя становится выходным потоком первого двоичного умножителя. Когда же сигнал на нулевом информационном входе третьего мультиплексора равен единице, выходной частотно – импульсный поток преобразователя становится выходным частотно – импульсным потоком второго двоичного умножителя. Таким образом, выходная последовательность импульсов Fвых преобразователя характеризуется частотой

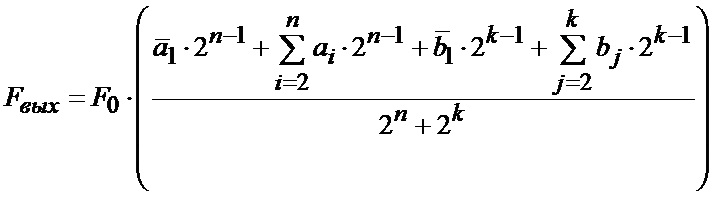

.

.

При этом применение цифровой коррекции позволяет снизить аддитивную и мультипликативную составляющие погрешности преобразования.

Недостатком прототипа является сложность организации внешней коррекции.

Задачей, на решение которой направлено заявляемое изобретение, является упрощение устройства за счет организации внутренней компенсирующей обратной связи при формировании выходного импульсного потока.

Техническим результатом является упрощение устройства преобразования кода в частоту с автоматической компенсацией без коррекции.

Указанный технический результат достигается за счет того, что в преобразователь кода в частоту, содержащий вход опорной частоты F0 , выход Fвых. преобразователя, входную шину NG, двоичные умножители с цифровыми входами Nп и Nк, при этом каждый двоичный умножитель и состоит из первого и второго двоичных счетчиков, и первого и второго мультиплексоров соответственно, а выходы разрядов первого и второго двоичных счетчиков соединены с соответствующими адресными входами первого и второго мультиплексоров, информационные входы которых являются соответствующими цифровыми входами Nп и Nк двоичных умножителей, а вход опорной частоты F0 преобразователя соединен со входами тактирования F первого и второго двоичных умножителей, одновременно являясь входами тактирования первого и второго двоичных счетчиков, а также нулевыми информационными входами первого и второго мультиплексоров соответственно, при этом выходы мультиплексоров Fy1 и Fy2 одновременно являются выходами первого и второго двоичных умножителей соответственно, введены реверсивный двоичный счетчик и вход записи WR, подключенный к соответствующему входу реверсивного счетчика, цифровой вход которого соединен с входной шиной NG, суммирующий вход – с выходом Fy1 мультиплексора, а вычитающий вход реверсивного счетчика объединен с выходом Fвых преобразователя и с выходом Fy2 мультиплексора, при этом цифровой выход счетчика Nк подключен к цифровому входу второго двоичного умножителя.

Сущность предлагаемого изобретения состоит в создании преобразователя кода в частоту без исходной сложной корректировки с использованием итерационного метода реализации оператора усреднения путем функционального обобщения процесса преобразования кода в частоту, как для цепи прямой связи, так и для цепи обратной связи.

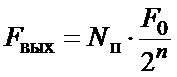

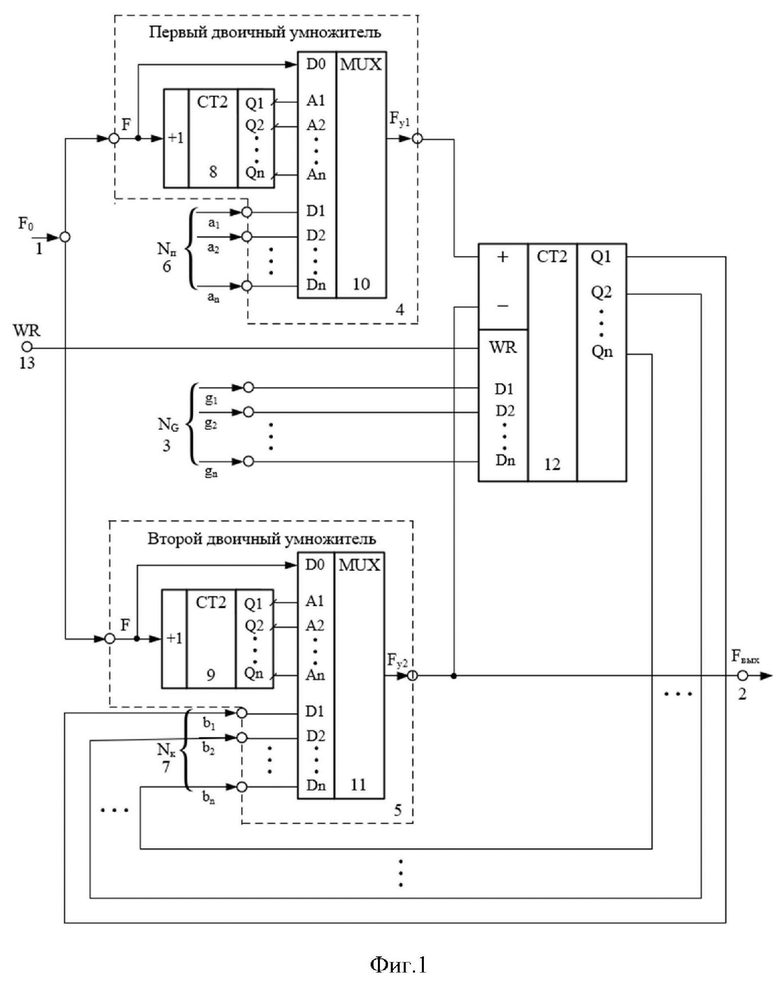

Сущность предлагаемого изобретения поясняется чертежами, где на фиг. 1 изображена функциональная схема предлагаемого преобразователя кода в частоту;

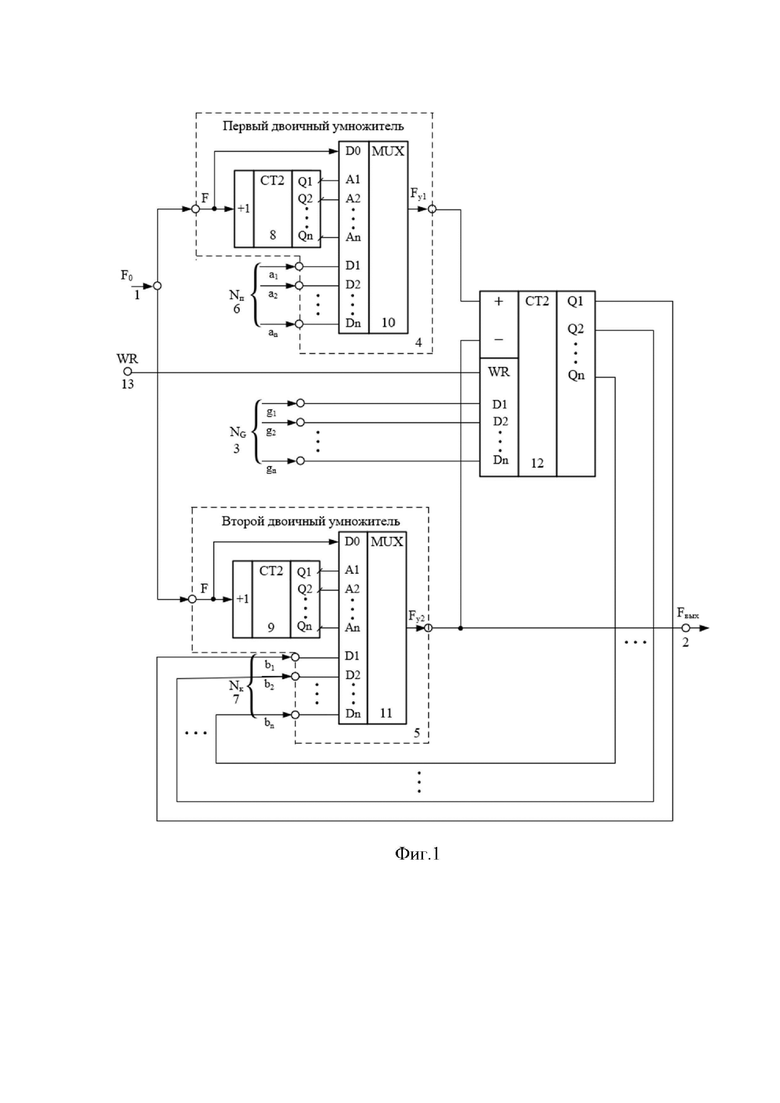

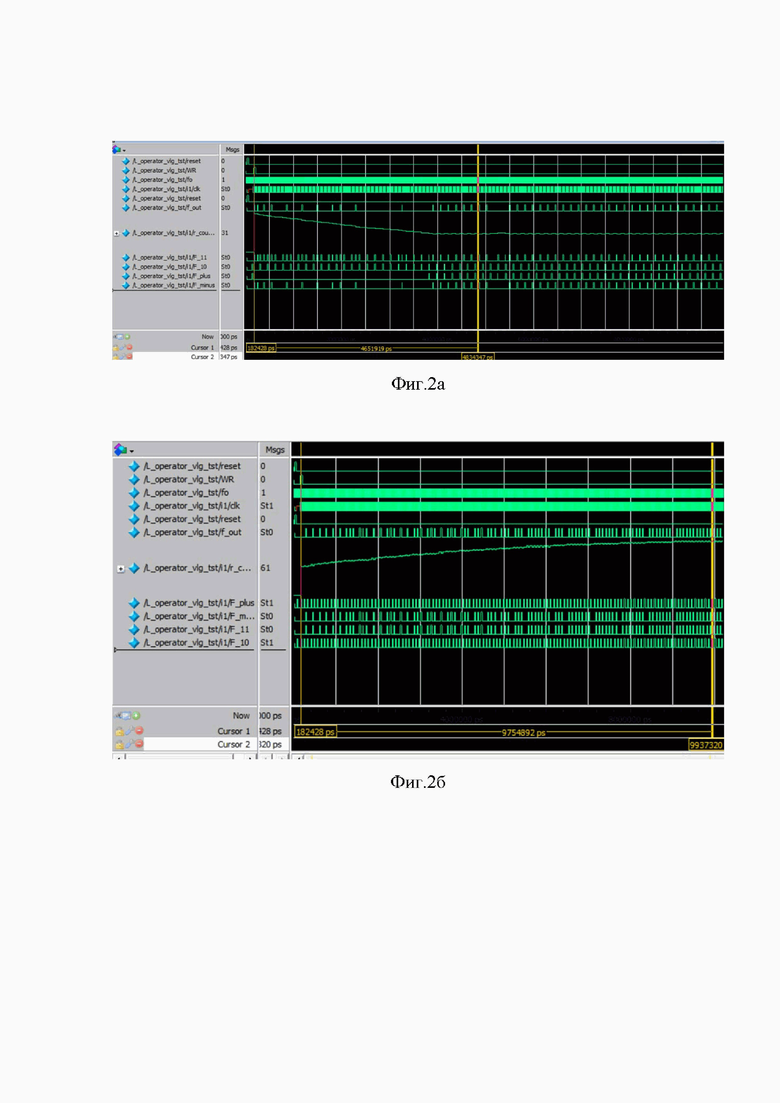

на фиг. 2 показаны примеры тестирования схемы, которое проводилось с использованием VerilogHDL модули устройства, синтезированной с использованием САПР Quartus Prime; при моделировании разрядность устанавливалась равной 8; на фиг.2а показана реакция устройства на воздействие сигнала при декременте, а на фиг.2б – при инкременте значений счетчика СТ2.

Преобразователь кода в частоту (фиг.1), содержащий вход 1 опорной частоты F0 , выход 2 F вых преобразователя, входную шину 3 NG, двоичные умножители 4 и 5 с цифровыми входами 6 Nп и 7 Nк, при этом каждый двоичный умножитель 4 и 5 состоит из первого 8 и второго 9 двоичных счетчиков, и первого 10 и второго 11 мультиплексоров соответственно, а выходы разрядов первого 8 и второго 9 двоичных счетчиков соединены с соответствующими адресными входами первого 10 и второго 11 мультиплексоров, информационные входы которых являются соответствующими цифровыми входами 6 Nп и 7 Nк двоичных умножителей 4 и 5, а вход 1 опорной частоты F0 преобразователя соединен со входами тактирования F первого 4 и второго 5 двоичных умножителей, которые одновременно являются входами тактирования первого 8 и второго 9 двоичных счетчиков, а также нулевыми информационными входами первого 10 и второго 11 мультиплексоров соответственно, при этом выходы мультиплексоров 10 Fy1 и 11 Fy2 одновременно являются выходами первого 4 и второго 5 двоичных умножителей соответственно.

Кроме того, преобразователь содержит реверсивный двоичный счетчик 12 и вход записи WR 13, подключенный к соответствующему входу реверсивного счетчика 12, цифровой вход которого соединен с входной шиной 3 NG, суммирующий вход – с выходом первого 4 двоичного умножителя, а вычитающий вход реверсивного счетчика 12 объединен с выходом 2 F вых преобразователя и с выходом второго 5 двоичного умножителя, при этом цифровой выход счетчика 12 Nк подключен к цифровому входу 7 второго двоичного умножителя 5.

Устройство работает следующим образом.

На вход 1 преобразователя поступает импульсная последовательность с опорной частотой F0. По сигналу на вход WR 13 происходит запись кода NG с входной шины 3 в реверсивный счетчик 12.

Пусть число разрядов двоичных умножителей 4 и 5 равно n, а двоичные счетчики 8 и 9 находятся в нулевом состоянии. Под воздействием опорной частоты F0 двоичные счетчики могут изменять свои выходные значения.

Таким образом, на цифровые входы первого 6 и второго 7 двоичных умножителей 4 и 5 подаются коды a1, а2, а3, …, an и b1, b2, b3, …, bn соответственно. Двоичные счетчики первый 8 и второй 9 последовательно во времени формируют на своих выходах значения в диапазоне от 0 до 2n–1, которые являются адресными входами первого 10 и второго 11 мультиплексоров соответственно.

Так для примера, при выходных значениях первого 8 двоичного счетчика равных «0», «2», «4», «6», «8», «10», «12» или «14», в выходную неравномерную последовательность импульсов Fy1 вставится импульс опорной частоты F0 преобразователя, если a1 = 1. При входном значении первого 8 двоичного счетчика, равном «1», «5», «9» или «13», в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а2 = 1. При выходном значении первого 8 двоичного счетчика, равном «3» или «11», в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а3 = 1. При выходном значении первого 8 двоичного счетчика, равном «7», в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а4 = 1. Выходная последовательность импульсов Fy1 на выходе первого 4 двоичного умножителя характеризуется частотой

,

,

где i – номер разряда преобразуемого кода Nп.

Выходные значения второго 9 двоичного счетчика являются адресными входами второго 11 мультиплексора. Так для примера, при выходном значении второго 9 двоичного счетчика, равном «0», «2», «4», «6», «8», «10», «12» или «14», в выходную неравномерную последовательность импульсов Fy2 вставится импульс опорной частоты F0 преобразователя, если b1 = 1. При выходном значении второго 9 двоичного счетчика, равном «1», «5», «9» или «13», в выходную неравномерную последовательность импульсов Fy2 вставится импульс, если b2 = 1.

Далее аналогично первому 4 двоичному умножителю выходная последовательность импульсов Fy2 на выходе второго 5 двоичного умножителя характеризуется частотой

,

,

где j – номер разряда компенсирующего кода Nк.

Выходной частотно – импульсный поток второго 5 двоичного умножителя становится частотно – импульсным выходом 2 преобразователя.

Таким образом, выходная последовательность импульсов Fвых преобразователя характеризуется частотой

.

.

В основу работы преобразователя положен принцип автоматической компенсации частотно-импульсных последовательностей, реализуемый с помощью отрицательной обратной связи, а в качестве схемы сравнения, вырабатывающей сигнал рассогласования в контуре обратной связи, используется реверсивный счетчик, с помощью которого осуществляется вычитание частот и интегрирование полученной разности с выдачей результата в виде двоичного кода для управления двоичным умножителем, вырабатывающим выходную частоту.

Условием динамического равновесия преобразователя является равенство приращений кодов суммирующей и вычитающей цепей в реверсивном счетчике ΔN+ = ΔN-.

В результате средние значения частот последовательностей импульсов Fy1 и Fy2 за цикл Тц интервала неравномерности равны между собой Fy1 = Fy2, и не требуется организация внешней коррекции

.

.

На временной диаграмме (фиг. 2а) показана реакция устройства на воздействие сигнала WR при G=64, A=32. В момент 180 нс в счетчик загружается число 64, которое постепенно декрементируется до значения 31, после чего усредненное за период работы устройства значение кода на счетчике составляет 32. В начале работы интенсивность импульсов на выходе устройства (на выходе второго двоичного умножителя 5, на диаграмме сигнал F_11) соответствует среднему значению 64, постепенно снижаясь до значения 31/32.

На фиг. 2б показана реакция устройства на воздействие сигнала WR при G=32, A=64. В момент 180 нс в счетчик загружается число 32, которое постепенно инкрементируется до значения 61, после чего усредненное за период работы устройства значение кода на счетчике составляет 61/62. В начале работы интенсивность импульсов на выходе устройства (на выходе второго двоичного умножителя 5, на диаграмме сигнал F_11) соответствует среднему значению 32, постепенно снижаясь до значения 61/62.

Предлагаемый преобразователь в сравнении с прототипом является более простым устройством – в отличительной части содержит только один реверсивный счетчик и вход записи WR, в то время как в прототипе в отличительную часть входят двоичный счетчик, три инвертора, три компаратора, мультиплексор, элемент И, две входные шины.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОСЕТЕВОЙ ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2008 |

|

RU2380752C2 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2005 |

|

RU2285946C1 |

| Устройство для измерения температуры | 1987 |

|

SU1536218A1 |

| Манипулятор частоты без разрыва фазы | 1987 |

|

SU1515384A1 |

| Устройство для измерения температуры | 1988 |

|

SU1642270A1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1022202A1 |

| Широтно-импульсный преобразователь | 2018 |

|

RU2683180C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ТЕМПЕРАТУРЫ | 2016 |

|

RU2623196C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| Цифровой многофазный генератор | 1990 |

|

SU1750032A1 |

Настоящее техническое решение относится к области вычислительной техники. Техническим результатом является упрощение устройства преобразования кода в частоту с автоматической компенсацией без коррекции. Технический результат достигается за счёт того, что преобразователь кода в частоту содержит вход 1 опорной частоты F0, выход 2 F вых преобразователя, входную шину 3 NG, двоичные умножители 4 и 5 с цифровыми входами 6 Nп и 7 Nк, при этом каждый двоичный умножитель 4 и 5 состоит из первого 8 и второго 9 двоичных счетчиков и первого 10 и второго 11 мультиплексоров соответственно. Также преобразователь содержит реверсивный двоичный счетчик 12 и вход записи WR 13, подключенный к соответствующему входу реверсивного счетчика 12, цифровой вход которого соединен с входной шиной 3 NG, суммирующий вход – с выходом первого 4 двоичного умножителя, а вычитающий вход реверсивного счетчика 12 объединен с выходом 2 F вых преобразователя и с выходом второго 5 двоичного умножителя, при этом цифровой выход счетчика 12 Nк подключен к цифровому входу 7 второго двоичного умножителя 5. 3 ил.

Преобразователь кода в частоту, содержащий вход опорной частоты, выход преобразователя, входную шину и два двоичных умножителя с цифровыми входами, при этом каждый двоичный умножитель состоит из первого и второго двоичного счетчика и первого и второго мультиплексора соответственно, а выходы разрядов первого и второго двоичных счетчиков соединены с соответствующими адресными входами первого и второго мультиплексоров, информационные входы которых являются соответствующими цифровыми входами двоичных умножителей, а вход опорной частоты преобразователя соединен со входами тактирования первого и второго двоичных умножителей, которые одновременно являются входами тактирования первого и второго двоичных счетчиков, а также нулевыми информационными входами первого и второго мультиплексоров соответственно, при этом выходы мультиплексоров одновременно являются выходами первого и второго двоичных умножителей соответственно, отличающийся тем, что преобразователь дополнительно содержит реверсивный двоичный счетчик и вход записи, подключенный к соответствующему входу реверсивного счетчика, цифровой вход которого соединен с входной шиной, суммирующий вход – с выходом первого двоичного умножителя, а вычитающий вход реверсивного счетчика объединен с выходом преобразователя и с выходом второго двоичного умножителя, при этом цифровой выход счетчика подключен к цифровому входу второго двоичного умножителя.

| ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2005 |

|

RU2285946C1 |

| Преобразователь кода в частоту | 1975 |

|

SU577673A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОД-ЧАСТОТА | 2000 |

|

RU2175813C1 |

| US 4066954, 03.01.1978 | |||

| US 5521556, 28.05.1996. | |||

Авторы

Даты

2023-10-13—Публикация

2023-04-17—Подача