Предлагаемое изобретение относится к вычислительной технике и может найти применение в телеметрических информационно-измерительных системах, в вычислительных управляющих комплексах с применением широтно-импульсной модуляции.

Известно устройство для воспроизведения функций на основе методов сквозной аппроксимации [А.С. 703825, G06F 15/353, 1977]. Это устройство ориентировано на обработку входного широтно-импульсного модулированного (ШИМ) сигнала в следящем режиме, обладает высокой помехоустойчивостью и надежностью за счет применения принципа усреднения импульсных потоков и воспроизводит функции типа тангенсной.

Известное устройство воспроизводит функции, представленные отношением простых дробей, основываясь на принципе автоматической компенсации частотно-импульсных последовательностей, реализуемом с помощью отрицательной обратной связи.

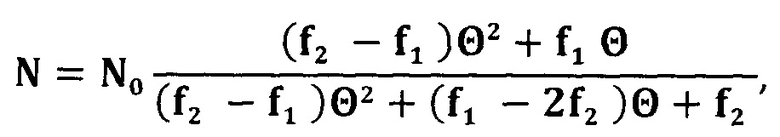

Функциональная характеристика устройства в общем виде описывается рациональной дробью

где N0 и N - входной и выходной коды устройства,

Θ - относительная длительность ШИМ-сигнала.

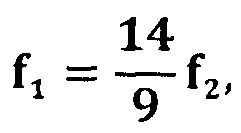

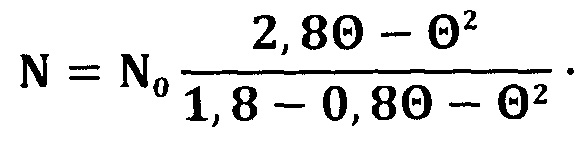

Для получения аппроксимации тангенсной зависимости достаточно задаться следующим соотношением опорных входных частот f1 и f2

тогда

Это выражение является дробно-рациональной аппроксимацией тангенсной функции с погрешностью не выше 0,2% в диапазоне 0≤Θ≤0,98.

Недостатком данного устройства является невысокая точность, особенно при воспроизведении функций типа тангенсной.

Наиболее близким по технической сущности к заявляемому устройству является широтно-импульсный преобразователь [А.С. 1056208, G06F 15/353, 1982], который и принят в качестве прототипа.

Прототип реализует взвешенно-полиномиальное приближение и более точно воспроизводит функции с особенностями, например, arcsin х, arctg х, tg х, и т.д.

Прототип содержит два реверсивных счетчика, элемент НЕ, три элемента И и элемент ИЛИ, двоичный умножитель, включающий в себя последовательно соединенные счетчик и блок логического умножения, а также четыре блока логического умножения и элемент задержки, причем вход частоты импульсов преобразователя соединен с частотным входом двоичного умножителя, частотный выход которого соединен с первым входом первого элемента И и с суммирующим входом первого реверсивного счетчика, второй вход первого элемента И соединен с вторым входом второго элемента И и с выходом элемента НЕ, а выход первого элемента И соединен с вычитающим входом второго реверсивного счетчика, подключенного суммирующим входом к выходу первого блока логического умножения, кодовый вход которого соединен с кодовым входом первого коэффициента аппроксимации, а частотный вход - с выходом всех разрядов счетчика двоичного умножителя и частотными входами второго, третьего и четвертого блоков логического умножения, при этом кодовый вход второго и третьего блоков логического умножения соединены соответственно с кодовыми входами второго и третьего коэффициентов аппроксимации преобразователя, а выходы второго и третьего блоков логического умножения соединены с первыми входами соответственно второго и третьего элементов И, причем второй вход последнего соединен с входом широтно-импульсного сигнала преобразователя и с входом элемента НЕ, а выходы второго и третьего элементов И соединены с первым и вторым входами элемента ИЛИ, третий вход которого, через элемент задержки, подключен к выходу четвертого логического блока, кодовый вход которого соединен с кодовым выходом преобразователя, а выход элемента ИЛИ соединен с вычитающим входом первого реверсивного счетчика. Кроме того, выход первого реверсивного счетчика подключен к кодовому выходу преобразователя, а выход второго реверсивного счетчика подключен к кодовому входу двоичного умножителя, которым является кодовый вход блока логического умножения, входящего в состав двоичного умножителя.

В основу построения устройства положен итерационный принцип усреднения импульсных потоков, формируемых от одной опорной частоты и ШИМ-сигналами, с использованием частотно-импульсной следящей системы. В качестве схемы сравнения, вырабатывающей сигнал рассогласования в контуре обратной связи, используется реверсивный счетчик, с помощью которого осуществляется, во-первых, суммирование частот, во-вторых, вычитание, и в-третьих, интегрирование полученной разности с выдачей результата в виде двоичного кода. Кроме главного контура отрицательной обратной связи, здесь имеется дополнительный - на основе второго счетчика, который образует функциональный узел в прямой цепи главного контура. Здесь первый счетчик выполняет одновременно две операции: вычитание частот и интегрирование полученной разности с представлением результата в виде двоичного кода.

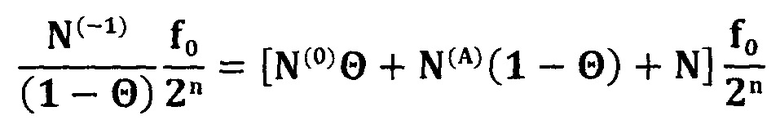

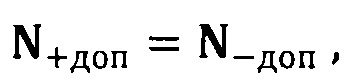

Условием динамического равновесия схемы является равенство приращений кодов суммирующих и вычитающих цепей в каждом реверсивном счетчике в течение периода широтно-импульсной модуляции, то есть, равенство средних значений частот импульсных последовательностей, поступающих на суммирующие и вычитающие входы счетчиков:

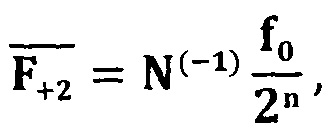

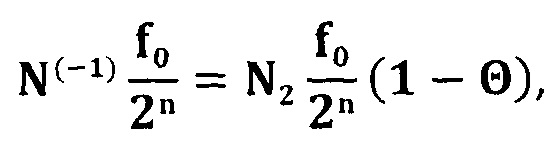

На суммирующий вход второго реверсивного счетчика поступает импульсная последовательность, пропорциональная входному коду N(-1)

где n - разрядность преобразователя.

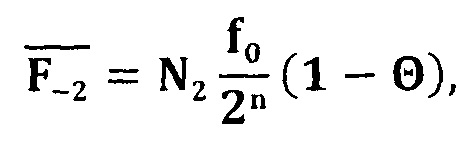

На вычитающий вход этого счетчика проходит широтно-модулированная импульсная последовательность, среднее значение которой определяется выражением

где N2 - выходной код второго реверсивного счетчика дополнительного контура. Приравнивая импульсные последовательности с суммирующего и вычитающего входов второго реверсивного счетчика

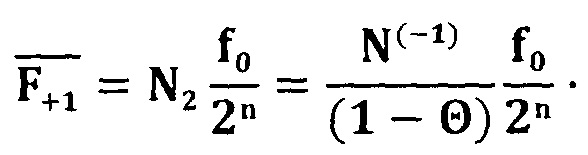

получим функциональную характеристику узла в прямой цепи главного контура

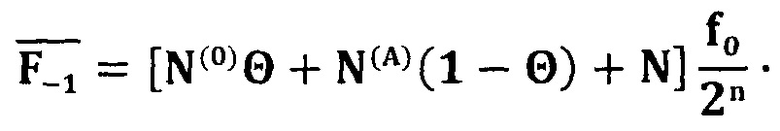

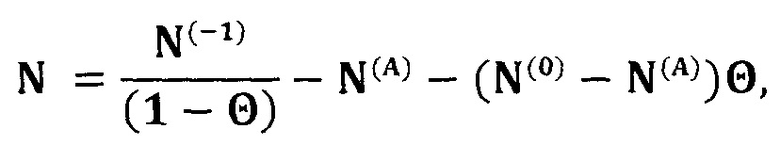

Импульсная последовательность в цепи обратной связи главного контура формируется на выходе элемента ИЛИ и имеет среднее значение за период под воздействием выходного кода N и входных кодов N(0), N(A) устройства

Из условия динамического равновесия

определяется функциональная характеристика преобразователя в общем виде

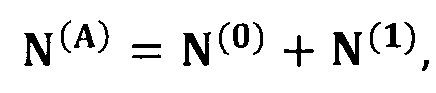

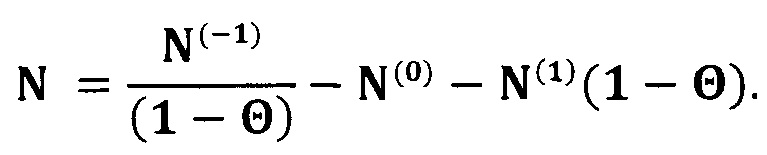

которая представляет собой взвешенно-полиноминальное выражение первой степени. Для одинакового представления аргумента с отрицательной и положительной степенью положим

тогда

Таким образом, широтно-импульсный преобразователь, реализует взвешенно-полиноминальное приближение эффективно воспроизводя функции типа тангенсной.

Недостатком прототипа является наличие флуктуации среднего значения результата, обусловленное неравномерностью бит-потоковых частотных последовательностей при реализации оператора усреднения.

Задачей, на решение которой направлено заявляемое изобретение, является создание устройства функционального преобразования широтно-импульсных сигналов без флуктуаций результата для функций с особенностями, например, arcsin х, arctg х, tg х и т.д.

Техническим результатом является повышение точности широтно-импульсного преобразователя за счет исключения флуктуаций выходного сигнала.

Решение поставленной задачи состоит в том, что в широтно-импульсный преобразователь, содержащий два реверсивных счетчика, элемент НЕ, три элемента И и элемент ИЛИ, двоичный умножитель, включающий в себя последовательно соединенные счетчик и блок логического умножения, а также четыре блока логического умножения и элемент задержки, причем вход частоты импульсов широтно-импульсного преобразователя соединен с частотным входом двоичного умножителя, частотный выход которого соединен с первым входом первого элемента И и с суммирующим входом первого реверсивного счетчика, второй вход первого элемента И соединен с вторым входом второго элемента И и с выходом элемента НЕ, а выход первого элемента И соединен с вычитающим входом второго реверсивного счетчика, подключенного суммирующим входом к выходу первого блока логического умножения, кодовый вход которого соединен с кодовым входом первого коэффициента аппроксимации, а частотный вход - с выходом всех разрядов счетчика двоичного умножителя и частотными входами второго, третьего и четвертого блоков логического умножения, при этом кодовый вход второго и третьего блоков логического умножения соединены соответственно с кодовыми входами второго и третьего коэффициентов аппроксимации широтно-импульсного преобразователя, а выходы второго и третьего блоков логического умножения соединены с первыми входами соответственно второго и третьего элементов И, причем второй вход последнего соединен с входом широтно-импульсного сигнала широтно-импульсного преобразователя и с входом элемента НЕ, а выходы второго и третьего элементов И соединены с первым и вторым входами элемента ИЛИ, третий вход которого, через элемент задержки, подключен к выходу четвертого логического блока, кодовый вход которого соединен с кодовым выходом широтно-импульсного преобразователя, а выход элемента ИЛИ соединен с вычитающим входом первого реверсивного счетчика, введены два регистра, вход первого из которых соединен с выходом второго реверсивного счетчика, а выход подключен к кодовому входу двоичного умножителя, которым является кодовый вход блока логического умножения, входящего в состав двоичного умножителя, а вход второго регистра подключен к выходу первого реверсивного счетчика, причем выход этого регистра является кодовым выходом широтно-импульсного преобразователя, а тактирование обоих регистров осуществляется соединением соответствующих входов с входом широтно-импульсного сигнала.

Сущность предлагаемого изобретения состоит в создании функционального преобразователя широтно-импульсных сигналов, поступающих периодически, с использованием итерационного метода реализации оператора усреднения с запоминающей обратной связью, путем функционального обобщения двоичного умножителя частоты за счет совмещения фазирования и модуляции импульсных последовательностей и получения возможности вычисления функций.

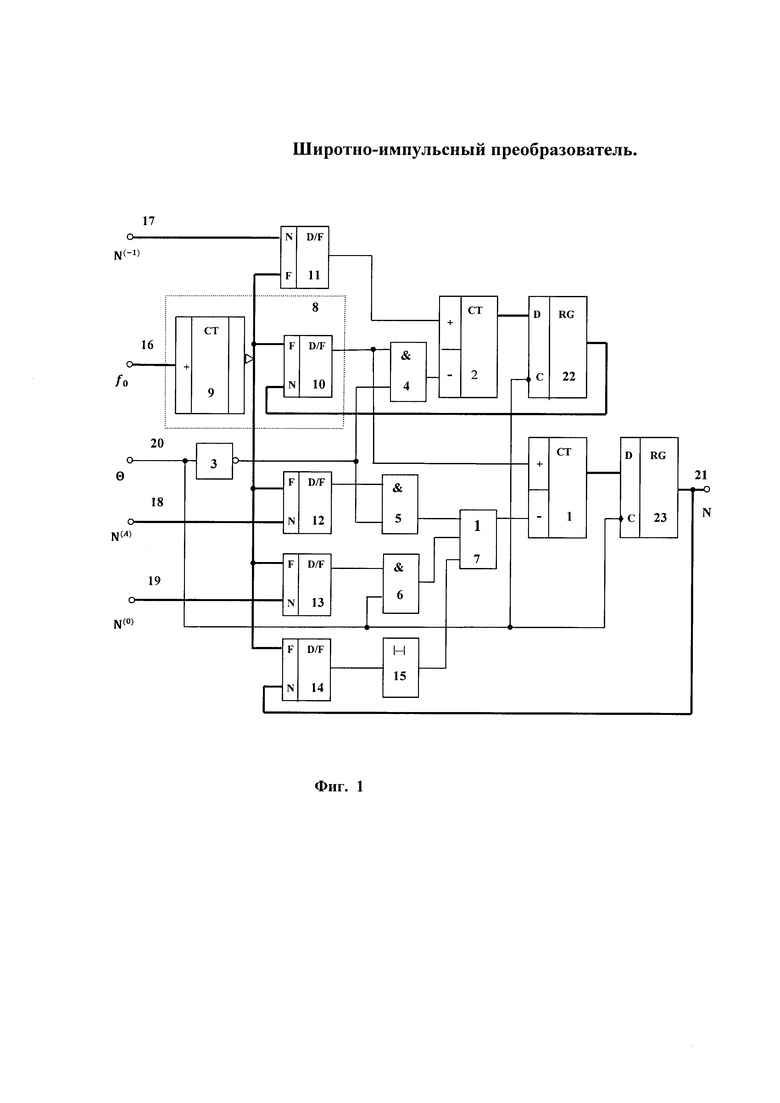

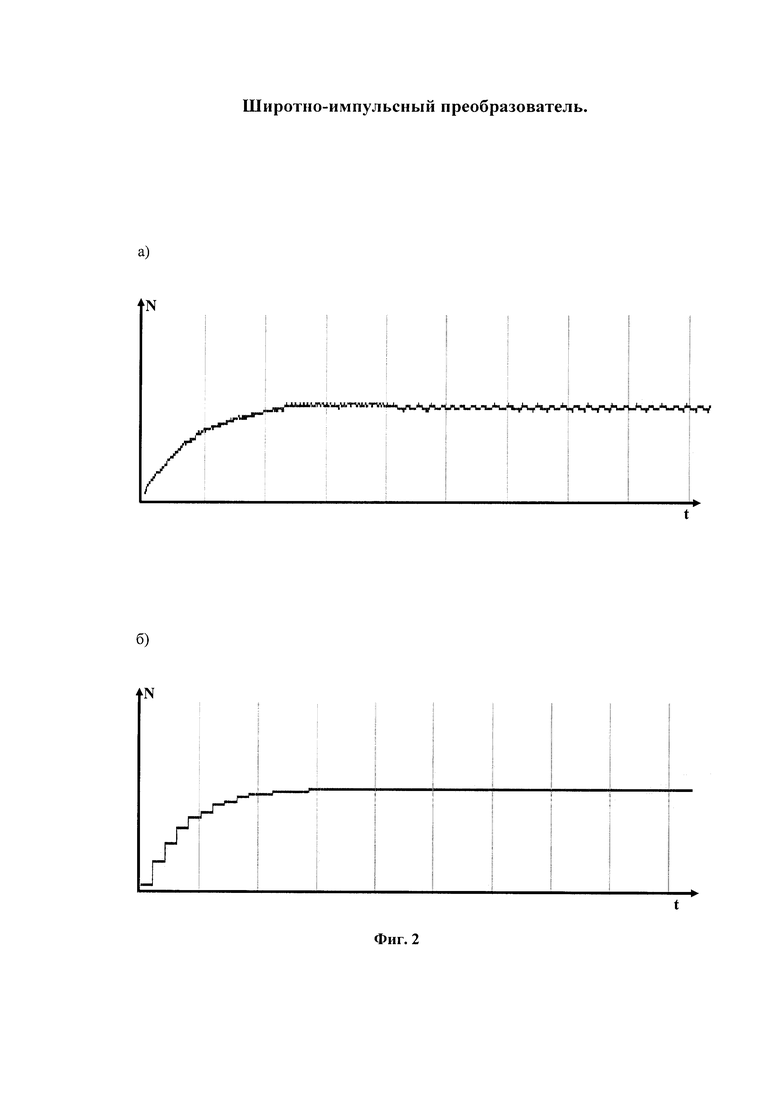

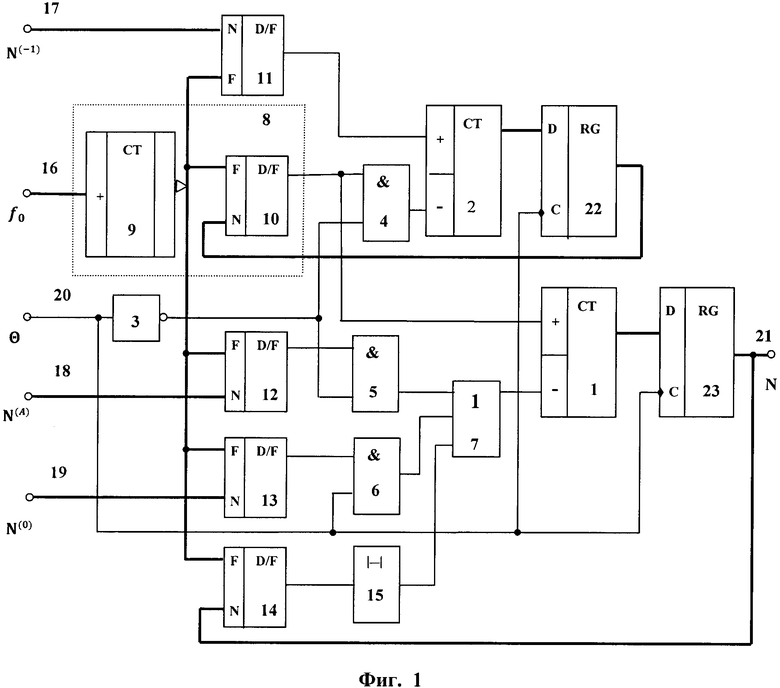

Сущность предполагаемого изобретения поясняется графическими материалами, где на фиг. 1 представлена функциональная схема широтно-импульсного преобразователя, а на фиг. 2 представлена временная диаграмма выходного кода широтно-импульсного преобразователя (б) в сравнении с прототипом (а), для 16 - разрядной структуры.

Широтно-импульсный преобразователь содержит реверсивные счетчики 1 и 2, элемент НЕ 3, три элемента И 4, 5 и 6, элемент ИЛИ 7, двоичный умножитель 8, включающий в себя последовательно соединенные счетчик 9 и блок логического умножения 10, а также четыре блока логического умножения 11, 12, 13 и 14, элемент задержки 15, причем вход 16 частоты импульсов преобразователя соединен с частотным входом двоичного умножителя 8, частотный выход которого соединен с первым входом элемента И 4 и с суммирующим входом реверсивного счетчика 1, второй вход элемента И 4 соединен с вторым входом элемента И 5 и с выходом элемента НЕ 3, а выход элемента И 4 соединен с вычитающим входом реверсивного счетчика 2, подключенного суммирующим входом к выходу блока логического умножения 11, кодовый вход которого соединен с кодовым входом 17 первого коэффициента аппроксимации, а частотный вход - с выходом всех разрядов счетчика 9 двоичного умножителя 8 и частотными входами блоков логического умножения 12, 13 и 14, при этом кодовые входы блоков логического умножения 12 и 13 соединены соответственно с кодовыми входами 18 и 19 второго и третьего коэффициентов аппроксимации широтно-импульсного преобразователя, а выходы блоков логического умножения 12 и 13 соединены с первыми входами элементов И 5 и И 6 соответственно, причем второй вход элемента И 6 соединен с входом 20 широтно-импульсного сигнала широтно-импульсного преобразователя и с входом элемента НЕ 3, а выходы элементов И 5 и И 6 соединены с первым и вторым входами элемента ИЛИ 7, третий вход которого, через элемент задержки 15, подключен к выходу логического блока 14, кодовый вход которого соединен с кодовым выходом широтно-импульсного преобразователя 21, а выход элемента ИЛИ 7 соединен с вычитающим входом реверсивного счетчика 1, причем вход регистра 22 соединен с выходом реверсивного счетчика 2, а выход подключен к кодовому входу двоичного умножителя 8, которым является кодовый вход блока логического умножения 10, входящего в состав двоичного умножителя 8, а вход второго регистра 23 подключен к выходу реверсивного счетчика 1, причем выход этого регистра 23 является кодовым выходом широтно-импульсного преобразователя 21, а тактирование обоих регистров 22 и 23 осуществляется соединением соответствующих входов с входом широтно-импульсного сигнала 20.

В качестве схемы сравнения, вырабатывающей сигнал рассогласования, в цепи запоминающей обратной связи используется реверсивный счетчик 1, с помощью которого осуществляется, во-первых, суммирование частот, во-вторых, вычитание, и в третьих, интегрирование полученной разности с выдачей результата в виде двоичного кода на регистр 23 в конце периода ШИМ-сигнала. Кроме главной цепи запоминающей отрицательной обратной связи на основе счетчика 1 и регистра 23, здесь имеется дополнительная цепь на основе реверсивного счетчика 2 и регистра 22.

Условием динамического равновесия широтно-импульсного преобразователя является равенство приращений кодов суммирующих и вычитающих цепей в каждом реверсивном счетчике в течение периода Т следования ШИМ-сигнала аргумента

т.е. равенства средних значений частот импульсных последовательностей, поступающих на суммирующие и вычитающие входы реверсивных счетчиков.

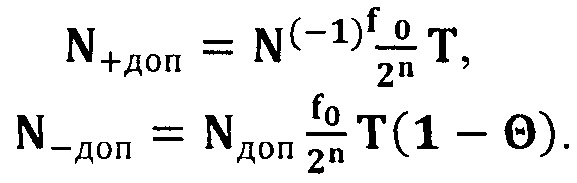

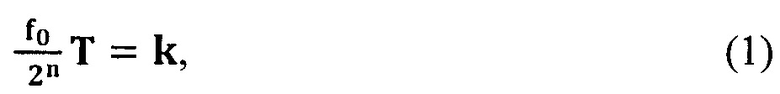

Количество импульсов, пришедших на суммирующий и вычитающий входы реверсивного счетчика 2 дополнительной цепи в течение одного периода Т широтно-импульсной модуляции, определяется соотношениями

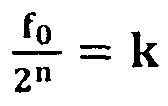

Обозначая

получим

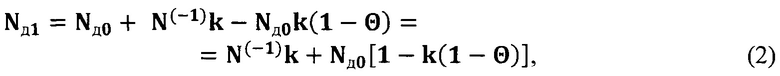

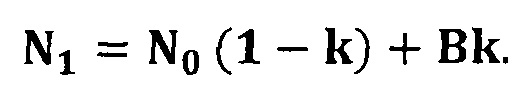

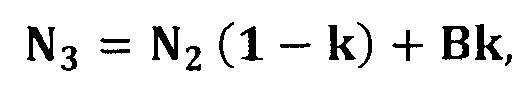

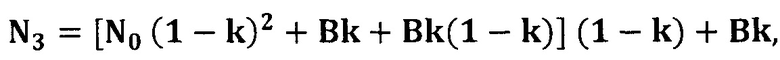

После первого периода работы дополнительной цепи реверсивный счетчик 2 сформирует код, который будет записан в регистр 22

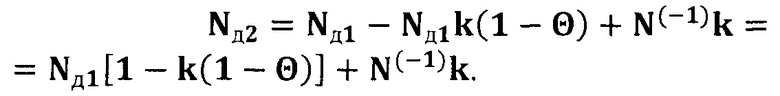

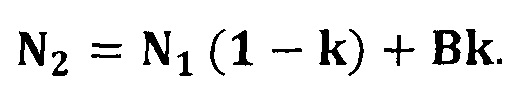

где Nд0 - начальное значение выходного кода дополнительной цепи. После второго периода работы дополнительной цепи реверсивный счетчик 2 сформирует код

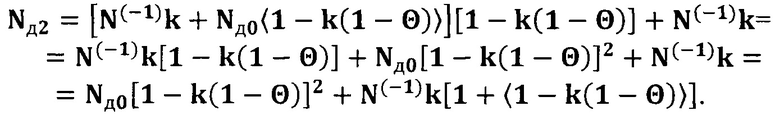

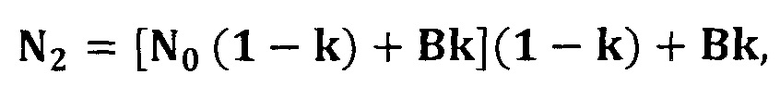

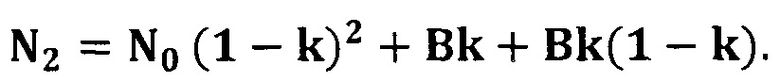

Подставляя выражение (2) для Nд1, получим

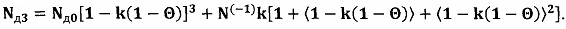

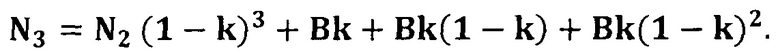

После третьего периода работы дополнительной цепи реверсивный счетчик 2 сформирует код

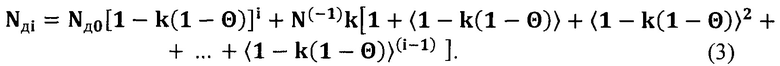

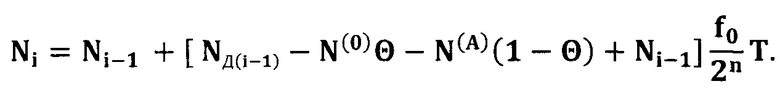

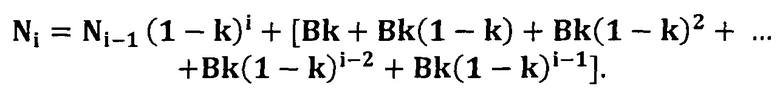

После i-ro периода работы дополнительной цепи реверсивный счетчик 2 сформирует код

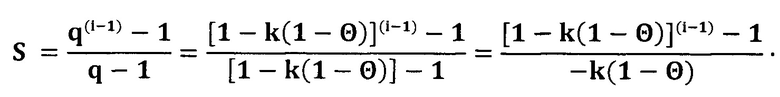

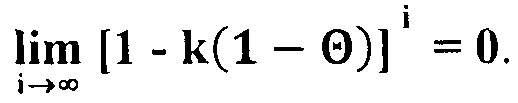

Второе слагаемое этого выражения характеризуется геометрической прогрессией с основанием q=1-k(1-Θ) и может быть представлено суммой

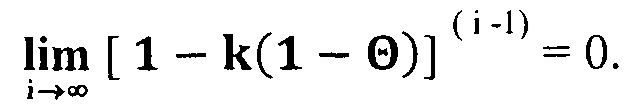

Поскольку величина Θ находятся в диапазоне 0<Θ<1 и величина k находится в диапазоне 0<k<1, получим 0<k(1-Θ)<1 и, следовательно,

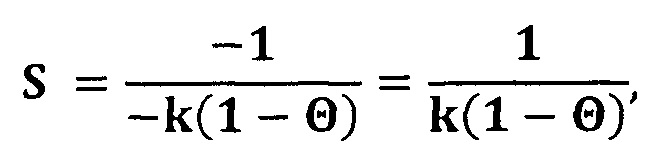

В пределе геометрическая прогрессия второго слагаемого выражения (3) преобразуется к виду

а первое слагаемое выражения (2) будет равно нулю, так как

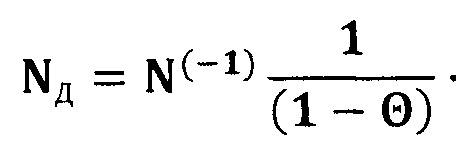

Таким образом, на выходе дополнительной цепи с регистра 22 будет сниматься код

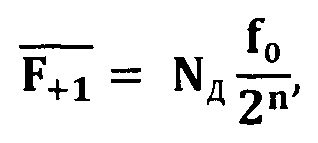

На суммирующий вход реверсивного счетчика 1 основной вычислительной цепи поступит импульсная последовательность со средней частотой

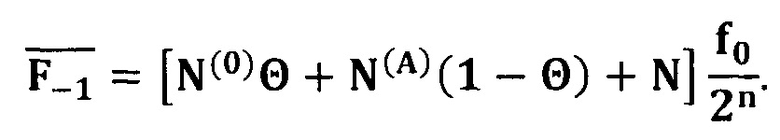

а на его вычитающий вход

Последовательность состояний устройства в процессе работы описывается уравнением

Для анализа характеристик переходного процесса в главной цепи запоминающей обратной связи используем конечный результат работы дополнительной цепи, когда Nд=const, что является допустимым благодаря сходимости числового ряда, образованного последовательностью состояний кода в регистре 22.

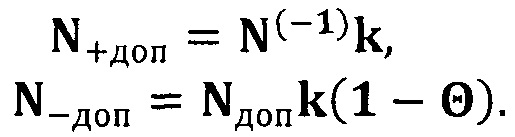

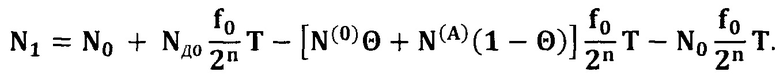

После первого периода Т работы устройства код, зафиксированный в регистре 23 с выхода реверсивного счетчика 1, определится следующим образом

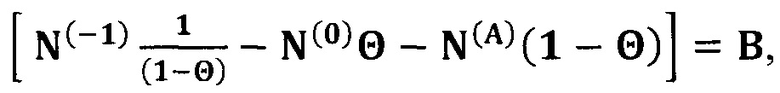

Принимая  , и обозначая

, и обозначая  получаем

получаем

После второго периода работы устройства в регистре 23 будет сформирован код, описываемый равенством

Подставляя в равенство значение N1, имеем

упрощая которое получаем

Код сформированный реверсивным счетчиком 1 и зафиксированный в регистре 23 по окончании третьего периода работы устройства, определяется равенством

подставляя в которое значение N0CH 2, получаем

или

По окончании i-го периода работы в регистре 23 будет зафиксирован код

Второе слагаемое этого выражения характеризуется геометрической прогрессией с основанием (1-k) и может быть представлено суммой

Учитывая, что 0<k<1, тогда

и получаем

Таким образом, преобразователь реализует взвешенно-полиноминальное приближение, эффективно воспроизводя функции типа arcsin х, arctg х, tg х, и т.д.. При этом, выходной код в регистре, в каждый период, будет фиксированным и не будет иметь флуктуаций обусловленных импульсными потоками.

На фиг. 2 приведена временная диаграмма выходного кода широтно-импульсного преобразователя (б) в сравнении с прототипом (а), для 16 - разрядной структуры. На диаграмме выходного кода прототипа видно, что даже в установившемся значении выходного кода присутствуют флуктуации, что влияет на точность. Диаграмма выходного кода широтно-импульсного преобразователя показывает, что значение выходного кода в установившемся значении не меняется.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1977 |

|

SU703825A1 |

| Устройство для вычисления тангенса | 1990 |

|

SU1734091A1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2006935C1 |

| УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ШИРОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ | 2003 |

|

RU2240652C1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 2008 |

|

RU2389065C1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1995 |

|

RU2097829C1 |

| Множительно-делительное устройство | 1977 |

|

SU788128A1 |

| Устройство для аппроксимации функций | 1989 |

|

SU1661789A1 |

| КОДИРУЮЩИЙ ВРЕМЯИМПУЛЬСНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2141721C1 |

| ЦИФРОВОЙ ТЕРМОМЕТР | 2012 |

|

RU2519860C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении точности широтно-импульсного преобразователя. Устройство содержит два регистра, вход первого из которых соединен с выходом второго реверсивного счетчика, а выход подключен к кодовому входу двоичного умножителя, вход второго регистра подключен к выходу первого реверсивного счетчика, причем выход этого регистра является кодовым выходом широтно-импульсного преобразователя и одновременно подключен к кодовому входу четвертого блока логического умножения, а тактирование обоих регистров осуществляется соединением соответствующих входов с входным широтно-импульсным сигналом. 2 ил.

Широтно-импульсный преобразователь, содержащий два реверсивных счетчика, элемент НЕ, три элемента И и элемент ИЛИ, двоичный умножитель, включающий в себя последовательно соединенные счетчик и блок логического умножения, а также четыре блока логического умножения и элемент задержки, причем вход частоты импульсов преобразователя соединен с частотным входом двоичного умножителя, частотный выход двоичного умножителя соединен с первым входом первого элемента И и суммирующим входом первого реверсивного счетчика, второй вход первого элемента И соединен с вторым входом второго элемента И и через элемент НЕ - с входом широтно-импульсного модулированного сигнала, а выход первого элемента И соединен с вычитающим входом второго реверсивного счетчика, суммирующий вход которого соединен с выходом двоичного умножителя первого блока логического умножения, кодовый вход которого соединен с первым коэффициентом аппроксимации, а частотный вход - с частотным входом двоичного умножителя, выходом счетчика и первыми входами второго, третьего и четвертого блоков логического умножения, второй вход второго и третьего блоков логического умножения соединены соответственно с входами второго и третьего коэффициентов аппроксимации широтно-импульсного преобразователя, выходы второго и третьего блоков логического умножения соединены с вторыми входами соответственно второго и третьего элементов И, причем первый вход последнего соединен с входом широтно-импульсного сигнала широтно-импульсного преобразователя, а выходы второго и третьего элементов И соединены с первым и вторым входами элемента ИЛИ, третий вход элемента ИЛИ через элемент задержки соединен с выходом двоичного умножителя четвертого логического блока, второй вход которого соединен с кодовым выходом широтно-импульсного преобразователя, а выход элемента ИЛИ соединен с вычитающим входом первого реверсивного счетчика, отличающийся тем, что в широтно-импульсный преобразователь введены два регистра, вход первого из которых соединен с выходом второго реверсивного счетчика, а выход подключен к кодовому входу двоичного умножителя, вход второго регистра подключен к выходу первого реверсивного счетчика, причем выход этого регистра является кодовым выходом широтно-импульсного преобразователя и одновременно подключен к кодовому входу четвертого блока логического умножения, а тактирование обоих регистров осуществляется соединением соответствующих входов с входным широтно-импульсным сигналом.

| Широтно-импульсный функциональный преобразователь | 1982 |

|

SU1056208A1 |

| Устройство для вычисления элементарных функций | 1985 |

|

SU1275433A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2276457C2 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Токарный резец | 1924 |

|

SU2016A1 |

Авторы

Даты

2019-03-26—Публикация

2018-05-28—Подача