Изобретение относится к автоматике и вычислительной технике и может быть использовано для цифроаналогового преобразования знакопеременного кода в частоту с возможностью цифровой коррекции, а также в вычислительных устройствах для умножения частоты следования импульсных сигналов на параллельный двоичный код.

Наиболее близким по совокупности признаков и по технической сущности к заявляемому устройству является двоичный умножитель (патент РФ №2006918, МПК G 06 F 7/68, 1994), который обеспечивает формирование выходной частоты, пропорциональной входному коду; содержащий двоичный счетчик, элемент задержки, n-канальный мультиплексор (n - число разрядов счетчика), первый и второй элементы И, триггер и формирователь импульсов, первый вход первого элемента И соединен с выходом элемента задержки, выходы разрядов двоичного счетчика соединены с соответствующими адресными входами n-канального мультиплексора, нулевой информационный вход которого соединен с управляющим входом умножителя, а информационные входы с первого по n-й - со входами соответствующих разрядов цифрового входа умножителя, причем первый информационный вход умножителя соединен со счетным входом двоичного счетчика и выходом второго элемента И, первый вход которого соединен со входом опорной частоты умножителя, входом формирователя импульсов и стробирующим входом n-канального мультиплексора, вход расширения и выход переноса которого соединены соответственно со входом расширения и выходом переноса умножителя, второй информационный выход которого соединен с выходом n-канального мультиплексора и входом элемента задержки, вход задания режима работы умножителя соединен со вторым входом первого элемента И, выход которого соединен со счетным входом триггера, вход сброса которого соединен с выходом формирователя импульсов, а инверсный выход - со вторым входом второго элемента И.

Недостатками прототипа являются его ограниченные функциональные возможности, а именно схемно-конструктивно не предусмотрены возможность преобразования знакопеременных кодов и возможность цифровой коррекции выходной частоты, так как он предназначен только для преобразования однополярного кода в частотно-импульсную последовательность.

Технический результат предлагаемого изобретения направлен на расширение функциональных возможностей, а именно на реализацию преобразования знакопеременного кода в частоту, а также на снижение погрешности преобразования за счет введения цифровой коррекции аддитивной и мультипликативной составляющих погрешностей преобразования.

Технический результат достигается тем, что преобразователь кода в частоту содержит первый двоичный умножитель, состоящий из первого двоичного счетчика и первого мультиплексора (n - число разрядов первого счетчика и число каналов первого мультиплексора), выходы разрядов первого двоичного счетчика соединены с соответствующими адресными входами первого мультиплексора, вход опорной частоты Fо преобразователя соединен со входом тактирования первого двоичного умножителя, вход тактирования первого двоичного умножителя одновременно является входом тактирования первого двоичного счетчика и нулевым информационным входом первого мультиплексора, разряды цифрового входа первого двоичного умножителя одновременно являются соответствующими информационными входами первого мультиплексора, информационные входы входного преобразуемого кода Nпр со второго по n-й соединены со входами соответствующих разрядов цифрового входа первого двоичного умножителя, выход первого двоичного умножителя одновременно является выходом первого мультиплексора, второй двоичный умножитель, аналогичный первому двоичному умножителю, первый и второй инверторы для инверсии старших разрядов входного преобразуемого кода Nпр и входного корректирующего кода Nкорр и устройство мультиплексирования выходных сигналов двоичных умножителей, включающее в себя третий инвертор, третий мультиплексор, третий двоичный счетчик, первый, второй и третий компараторы, элемент И, старший разряд а1 входного преобразуемого кода Nпр соединен со входом первого инвертора, выход первого инвертора соединен со входом старшего разряда цифрового входа первого двоичного умножителя, разряды цифрового входа второго двоичного умножителя одновременно являются соответствующими информационными входами второго мультиплексора, разряды b2...bk входного корректирующего кода Nкорр соединены со входами соответствующих разрядов цифрового входа второго двоичного умножителя, а старший разряд b1 входного корректирующего кода Nкорр соединен со входом второго инвертора, выход второго инвертора соединен со входом старшего разряда цифрового входа второго двоичного умножителя, выходы разрядов второго двоичного счетчика соединены с соответствующими адресными входами второго мультиплексора, вход опорной частоты Fо преобразователя соединен со входом тактирования второго двоичного умножителя и входом тактирования устройства мультиплексирования выходных сигналов двоичных умножителей, вход тактирования второго двоичного умножителя одновременно является входом тактирования второго двоичного счетчика и нулевым информационным входом второго мультиплексора, вход тактирования устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является третьим входом тактирования третьего двоичного счетчика, выход первого двоичного умножителя соединен с первым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей, выход второго двоичного умножителя одновременно является выходом второго мультиплексора, первый частотный вход устройства мультиплексирования выходных сигналов двоичных умножителей является одновременно первым входом третьего мультиплексора, второй частотный вход устройства мультиплексирования выходных сигналов двоичных умножителей является одновременно вторым входом третьего мультиплексора, выход второго двоичного умножителя соединен со вторым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей, нулевой информационный вход третьего мультиплексора соединен с выходом элемента И, выход третьего мультиплексора одновременно является выходом устройства мультиплексирования выходных сигналов двоичных умножителей и выходом преобразователя, счетный выход третьего двоичного счетчика соединен с первой входной шиной первого, второго и третьего компараторов, выход первого компаратора соединен с первым входом разрешения счета третьего двоичного счетчика и со входом третьего инвертора, первая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной первого компаратора, вторая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной второго компаратора, третья входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной третьего компаратора, первая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой С, вторая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой Е, третья входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой G, выход второго компаратора соединен с первым входом элемента И, выход третьего компаратора соединен со вторым входом элемента И, выход третьего инвертора соединен со вторым входом сброса третьего двоичного счетчика.

Отличительными признаками предлагаемого изобретения является то, что в преобразователь кода в частоту введены второй двоичный умножитель, аналогичный первому двоичному умножителю, первый и второй инверторы для инверсии старших разрядов входного преобразуемого кода Nпр и входного корректирующего кода Nкорр и устройство мультиплексирования выходных сигналов двоичных умножителей, включающее в себя третий инвертор, третий мультиплексор, третий двоичный счетчик, первый, второй и третий компараторы, элемент И, старший разряд а1 входного преобразуемого кода Nпр соединен со входом первого инвертора, выход первого инвертора соединен со входом старшего разряда цифрового входа первого двоичного умножителя, разряды цифрового входа второго двоичного умножителя одновременно являются соответствующими информационными входами второго мультиплексора, разряды b2...bk входного корректирующего кода Nкорр соединены со входами соответствующих разрядов цифрового входа второго двоичного умножителя, а старший разряд b1 входного корректирующего кода Nкорр соединен со входом второго инвертора, выход второго инвертора соединен со входом старшего разряда цифрового входа второго двоичного умножителя, выходы разрядов второго двоичного счетчика соединены с соответствующими адресными входами второго мультиплексора, вход опорной частоты Fо преобразователя соединен со входом тактирования второго двоичного умножителя и входом тактирования устройства мультиплексирования выходных сигналов двоичных умножителей, вход тактирования второго двоичного умножителя одновременно является входом тактирования второго двоичного счетчика и нулевым информационным входом второго мультиплексора, вход тактирования устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является третьим входом тактирования третьего двоичного счетчика, выход первого двоичного умножителя соединен с первым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей, выход второго двоичного умножителя одновременно является выходом второго мультиплексора, первый частотный вход устройства мультиплексирования выходных сигналов двоичных умножителей является одновременно первым входом третьего мультиплексора, второй частотный вход устройства мультиплексирования выходных сигналов двоичных умножителей является одновременно вторым входом третьего мультиплексора, выход второго двоичного умножителя соединен со вторым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей, нулевой информационный вход третьего мультиплексора соединен с выходом элемента И, выход третьего мультиплексора одновременно является выходом устройства мультиплексирования выходных сигналов двоичных умножителей и выходом преобразователя, счетный выход третьего двоичного счетчика соединен с первой входной шиной первого, второго и третьего компараторов, выход первого компаратора соединен с первым входом разрешения счета третьего двоичного счетчика и со входом третьего инвертора, первая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной первого компаратора, вторая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной второго компаратора, третья входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной третьего компаратора, первая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой С, вторая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой Е, третья входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой G, выход второго компаратора соединен с первым входом элемента И, выход третьего компаратора соединен со вторым входом элемента И, выход третьего инвертора соединен со вторым входом сброса третьего двоичного счетчика.

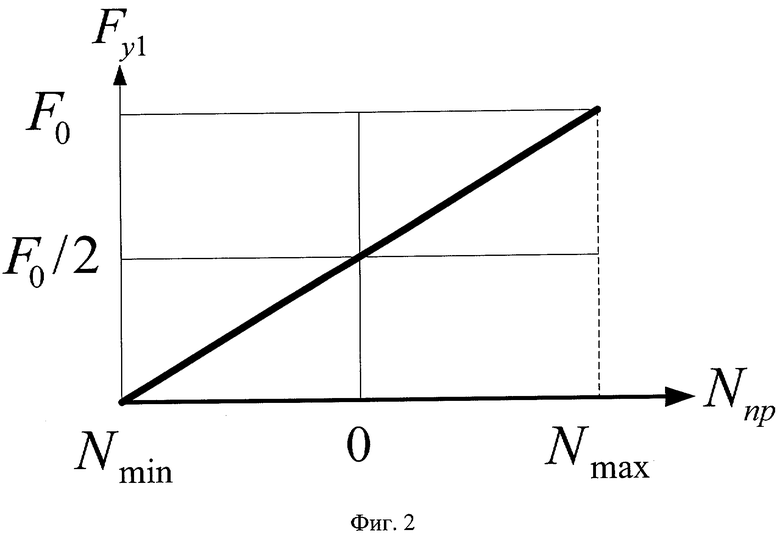

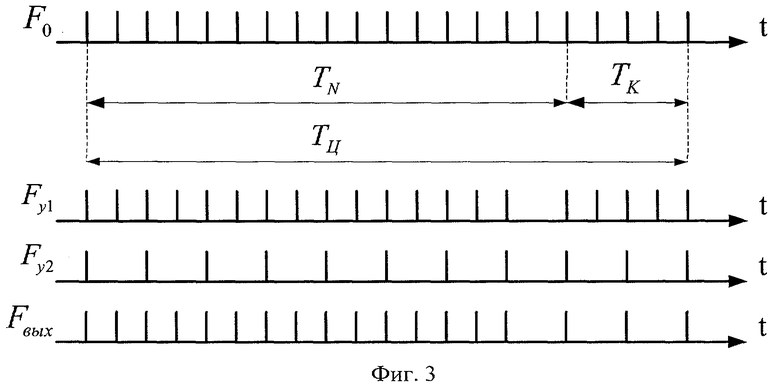

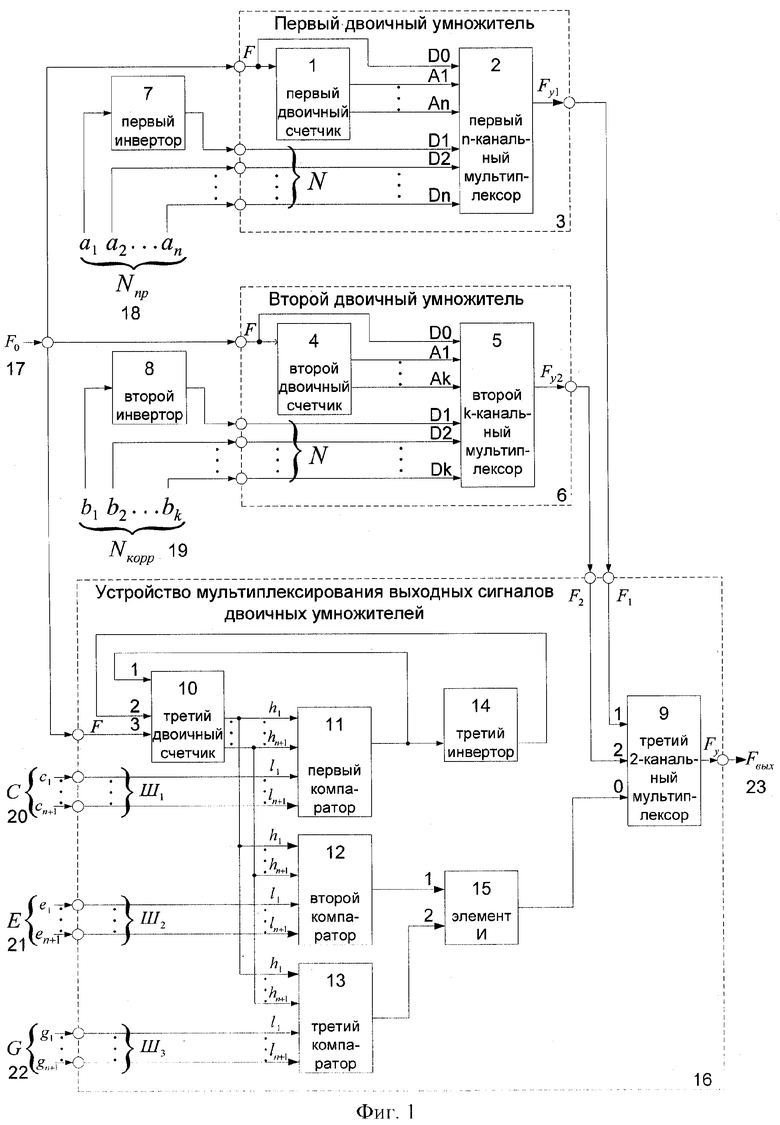

На фиг.1 представлена структурная схема предлагаемого преобразователя, на фиг.2 - график зависимости диапазона выходной частоты Fy1 первого двоичного умножителя от входного преобразуемого кода Nпр, на фиг.3 - временные диаграммы работы преобразователя.

Преобразователь кода в частоту содержит первый двоичный умножитель 3, второй двоичный умножитель 6, устройство мультиплексирования выходных сигналов двоичных умножителей 16, первый инвертор 7, второй инвертор 8, входной преобразуемый код Nпр 18, входной корректирующий код Nкорр 19, вход опорной частоты преобразования Fо 17, три входные константы С 20, E 21, G 22 и выходную частоту преобразователя Fвых 23.

Первый инвертор 7 предназначен для обеспечения возможности преобразования знакопеременного входного преобразуемого кода Nпр 18 в частоту, а именно для инверсии его старшего (знакового) разряда a1.

Второй инвертор 8 предназначен для обеспечения возможности преобразования знакопеременного входного корректирующего кода Nкорр 19 в частоту, а именно для инверсии его старшего (знакового) разряда b1.

Вход опорной частоты преобразователя Fо 17 соединен со входами тактирования первого 3 и второго 6 двоичных умножителей и входом тактирования устройства мультиплексирования выходных сигналов двоичных умножителей 16. Старший разряд а1 входного преобразуемого кода Nпр 18 соединен со входом первого инвертора 7, старший разряд b1 входного корректирующего кода Nкорр 19 соединен со входом второго инвертора 8. Выход первого инвертора 7, а также разряды а2...аn входного преобразуемого кода Nпр 18 соединены с соответствующими разрядами цифрового входа N первого двоичного умножителя 3. Выход второго инвертора 8, а также разряды b2...bk входного корректирующего кода Nкорр 19 соединены с соответствующими разрядами цифрового входа N второго двоичного умножителя 6. Выход первого двоичного умножителя 3 соединен с первым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей 16. Выход второго двоичного умножителя 6 соединен со вторым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей 16. Входная константа С 20 соединена с первой входной шиной Ш1 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Входная константа Е 21 соединена со второй входной шиной Ш2 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Входная константа G 22 соединена с третьей входной шиной Ш3 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Выход устройства мультиплексирования выходных сигналов двоичных умножителей 16 одновременно является выходной частотой Fвых 23 преобразователя.

Первый двоичный умножитель 3 содержит первый двоичный счетчик 1 и первый мультиплексор 2 (n - число разрядов первого счетчика и число каналов первого мультиплексора), вход тактирования F, цифровой вход N и частотный выход Fy1.

Вход тактирования F первого двоичного умножителя 3 одновременно является входом тактирования первого двоичного счетчика 1 и нулевым информационным входом D0 первого мультиплексора 2. Разряды а1...an цифрового входа N первого двоичного умножителя 3 одновременно являются информационными входами D1-Dn первого мультиплексора 2. Выходы разрядов первого двоичного счетчика 1 соединены с соответствующими адресными входами А1-Аn первого мультиплексора 2. Выход первого мультиплексора 2 одновременно является выходом первого двоичного умножителя 3.

Первый двоичный умножитель 3 осуществляет преобразование входного преобразуемого кода Nпр 18 в частоту Fy1, пропорциональную знакопеременному коду Nпр=а1а2...аn с интервалом неравномерности ТN=2n (фиг.3).

Второй двоичный умножитель 6 схемно-конструктивно аналогичен первому двоичному умножителю 3 и содержит второй двоичный счетчик 4 и второй мультиплексор 5 (k - число разрядов второго счетчика и число каналов второго мультиплексора), вход тактирования F, цифровой вход N и частотный выход Fy2.

Вход тактирования F второго двоичного умножителя 6 является одновременно входом тактирования второго двоичного счетчика 4 и нулевым информационным входом D0 второго мультиплексора 5. Разряды b1...bk цифрового входа N второго двоичного умножителя 6 одновременно являются информационными входами D1-Dk, второго мультиплексора 5. Выходы разрядов второго двоичного счетчика 4 соединены с соответствующими адресными входами А1-Ak второго мультиплексора 5. Выход второго мультиплексора 5 одновременно является выходом второго двоичного умножителя 6.

Второй двоичный умножитель 6 осуществляет преобразование входного корректирующего кода Nкорр 19 в частоту Fy2, пропорциональную знакопеременному корректирующему коду Nкорр=b1b2...bk с интервалом неравномерности ТK=2k. Работа двоичных умножителей разнесена во времени. В результате интервал неравномерности преобразователя кода в частоту равен ТЦ=ТN+ТK (фиг.3).

Устройство мультиплексирования выходных сигналов двоичных умножителей 16 содержит третий двоичный счетчик 10, первый компаратор 11, второй компаратор 12, третий компаратор 13, третий инвертор 14, элемент И 15, третий мультиплексор 9 выполнен двухканальным, вход тактирования F, первый частотный вход F1, второй частотный вход F2, первую входную шину Ш1, вторую входную шину Ш2, третью входную шину Ш3 и выходную частоту преобразования Fy.

Третий двоичный счетчик 10 вычисляет номер текущего такта преобразования внутри интервала неравномерности ТЦ преобразователя.

Первый компаратор 11 сравнивает номер текущего такта преобразования внутри интервала неравномерности ТЦ преобразователя с константой С 20, равной ТN+ТK-1. Выходной сигнал первого компаратора 11 равен единице, если выходное значение третьего двоичного счетчика 10 меньше константы С 20. В противном случае выходной сигнал первого компаратора 11 равен нулю. Таким образом, первый компаратор 11 разрешает инкрементирование выходного значения третьего двоичного счетчика 10, пока оно не достигнет величины ТЦ.

Второй компаратор 12 сравнивает номер текущего такта преобразования внутри интервала неравномерности ТЦ преобразователя с константой E 21, равной ТN-1. Выходной сигнал второго компаратора 12 равен единице, если выходное значение третьего двоичного счетчика 10 больше константы E 21. В противном случае выходной сигнал второго компаратора 12 равен нулю.

Третий компаратор 13 сравнивает номер текущего такта преобразования внутри интервала неравномерности ТЦ преобразователя с константой F 22, равной ТN+ТK. Выходной сигнал третьего компаратора 13 равен единице, если выходное значение третьего двоичного счетчика 10 меньше константы F 22. В противном случае выходной сигнал третьего компаратора 13 равен нулю.

Элемент И 15 выполняет объединение результатов сравнения второго 12 и третьего 13 компараторов. Выход элемента И 15 равен единице, если выходные значения второго 12 и третьего 13 компараторов равны единице. В противном случае выход элемента И 15 равен нулю. Третий двоичный счетчик 10, второй компаратор 12, третий компаратор 13 и элемент И 15 предназначены для формирования управляющего входа третьего мультиплексора 9.

Третий мультиплексор 9 осуществляет выбор выходной частоты преобразователя. Нулевой информационный вход третьего мультиплексора 9 является сигналом выбора. Когда сигнал на нулевом информационном входе третьего мультиплексора 9 равен нулю, на его выходе сигнал равен первому входному сигналу третьего мультиплексора 9. Когда сигнал на нулевом информационном входе третьего мультиплексора 9 равен единице, на его выходе сигнал равен второму входному сигналу третьего мультиплексора 9.

Вход тактирования F устройства мультиплексирования выходных сигналов двоичных умножителей 16 одновременно является входом тактирования третьего двоичного счетчика 10. Первый частотный вход F1 устройства мультиплексирования выходных сигналов двоичных умножителей 16 одновременно является первым входом третьего мультиплексора 9. Второй частотный вход F2 устройства мультиплексирования выходных сигналов двоичных умножителей 16 одновременно является вторым входом третьего мультиплексора 9. Нулевой информационный вход третьего мультиплексора 9 соединен с выходом элемента И 15. Выход третьего мультиплексора 9 одновременно является выходом устройства мультиплексирования выходных сигналов двоичных умножителей 16 и выходом устройства. Счетный выход третьего двоичного счетчика 10 соединен с первой входной шиной Н=h1h2...hn+1 первого 11, второго 12 и третьего 13 компараторов. Выход первого компаратора 11 соединен с первым входом разрешения счета третьего двоичного счетчика 10 и входом третьего инвертора 14. Вторая входная шина L=l1l2...ln+1 первого компаратора 11 одновременно является первой входной шиной Ш1 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Вторая входная шина L=l1l2...ln+1 второго компаратора 12 одновременно является второй входной шиной Ш2 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Вторая входная шина L=l1l2...ln+1 третьего компаратора 13 одновременно является третьей входной шиной Ш3 устройства мультиплексирования выходных сигналов двоичных умножителей 16. Выход второго компаратора 12 соединен с первым входом элемента И 15. Выход третьего компаратора 13 соединен со вторым входом элемента И 15. Выход третьего инвертора 14 соединен со вторым входом сброса третьего двоичного счетчика 10.

Устройство мультиплексирования выходных сигналов двоичных умножителей 16 осуществляет мультиплексирование выходных частот первого 3 и второго 6 двоичных умножителей, а именно вставляет в частотно-импульсный поток, пропорциональный входному преобразуемому коду Nпр, импульсы, пропорциональные входному корректирующему коду Nкорр.

Преобразователь работает следующим образом.

Пусть число разрядов n первого двоичного умножителя равно четырем, а число разрядов k второго двоичного умножителя равно двум (фиг.3). Пусть в начальный момент времени первый 1, второй 4 и третий 10 двоичные счетчики находятся в нулевом состоянии. На вход 17 подается импульсная последовательность входной частоты Fо. Первый 1, второй 4 и третий 10 двоичные счетчики могут изменять свои выходные значения только при появлении очередного импульса входной частоты Fо преобразователя. На вход первого инвертора 7 подается старший (знаковый) разряд а1 входного преобразуемого кода Nпр. Если a1=1, то на выходе первого инвертора 7 формируется сигнал, равный единице. Если а1=0, то на выходе первого инвертора 7 формируется сигнал, равный нулю. На вход второго инвертора 8 подается старший (знаковый) разряд b1 входного корректирующего кода Nкорр 19. Если b1=1, то на выходе второго инвертора 8 формируется сигнал, равный единице. Если b1=0, то на выходе второго инвертора формируется сигнал, равный нулю. Таким образом, на цифровой вход первого двоичного умножителя 3 и соответствующие разряды информационного входа первого мультиплексора 2 подается код  , а на цифровой вход второго двоичного умножителя 6 и соответствующие разряды информационного входа второго мультиплексора 5 подается код

, а на цифровой вход второго двоичного умножителя 6 и соответствующие разряды информационного входа второго мультиплексора 5 подается код  . Разрядность первого двоичного счетчика 1 совпадает с разрядностью первого двоичного умножителя 3, а разрядность второго двоичного счетчика 4 совпадает с разрядностью второго двоичного умножителя 6. Таким образом, первый двоичный счетчик 1 последовательно во времени формирует на своем выходе значения в диапазоне от 0 до 2n-1=15. Второй же двоичный счетчик 4 последовательно во времени формирует на своем выходе значения в диапазоне от 0 до 2k-1=3.

. Разрядность первого двоичного счетчика 1 совпадает с разрядностью первого двоичного умножителя 3, а разрядность второго двоичного счетчика 4 совпадает с разрядностью второго двоичного умножителя 6. Таким образом, первый двоичный счетчик 1 последовательно во времени формирует на своем выходе значения в диапазоне от 0 до 2n-1=15. Второй же двоичный счетчик 4 последовательно во времени формирует на своем выходе значения в диапазоне от 0 до 2k-1=3.

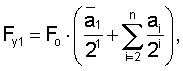

Выходные значения первого двоичного счетчика 1 являются адресными входами первого мультиплексора 2. Так, при выходном значении первого двоичного счетчика 1, равном "0", "2", "4", "6", "8", "10", "12" или "14", в выходную неравномерную последовательность импульсов Fy1, одновременно являющуюся выходом первого мультиплексора 2 и выходом первого двоичного умножителя 3, вставится импульс длительности верхнего фронта опорной частоты Fо преобразователя, если  . При выходном значении первого двоичного счетчика 1, равном "1", "5", "9" или "13", в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а2=1. При выходном значении первого двоичного счетчика 1, равном "3" или "11", в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а3=1. При выходном значении первого двоичного счетчика 1, равном "7", в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а4=1. Выходная последовательность импульсов Fy1 на выходе первого двоичного умножителя характеризуется частотой

. При выходном значении первого двоичного счетчика 1, равном "1", "5", "9" или "13", в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а2=1. При выходном значении первого двоичного счетчика 1, равном "3" или "11", в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а3=1. При выходном значении первого двоичного счетчика 1, равном "7", в выходную неравномерную последовательность импульсов Fy1 вставится импульс, если а4=1. Выходная последовательность импульсов Fy1 на выходе первого двоичного умножителя характеризуется частотой

где i - номер разряда преобразуемого кода Nпр.

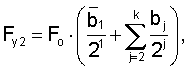

Выходные значения второго двоичного счетчика 4 являются адресными входами второго мультиплексора 5. Так, при выходном значении второго двоичного счетчика 4, равном "0" или "2", в выходную неравномерную последовательность импульсов Fy2, одновременно являющуюся выходом второго мультиплексора 5 и выходом второго двоичного умножителя 6, вставится импульс длительности верхнего фронта опорной частоты Fо преобразователя, если  . При выходном значении второго двоичного счетчика 4, равном "1", в выходную неравномерную последовательность импульсов Fy2 вставится импульс, если b2=1. Выходная последовательность импульсов Fy2 на выходе второго двоичного умножителя характеризуется частотой

. При выходном значении второго двоичного счетчика 4, равном "1", в выходную неравномерную последовательность импульсов Fy2 вставится импульс, если b2=1. Выходная последовательность импульсов Fy2 на выходе второго двоичного умножителя характеризуется частотой

где j - номер разряда корректирующего кода Nкорр.

Разрядность третьего двоичного счетчика 10 равна n+1. Третий двоичный счетчик 10 последовательно во времени формирует на своем выходе значения в диапазоне от 0 до 2n+2k-1=19. Первый компаратор 11 ограничивает диапазон изменения выходных значений третьего двоичного счетчика от 0 до 2n+2k-1=19. Если выходное значение третьего двоичного счетчика 10 меньше величины 2n+2k-1=19, то на выходе первого компаратора 10 формируется единичный сигнал, служащий сигналом разрешения счета третьего двоичного счетчика 10. В противном случае на выходе первого компаратора 10 формируется нулевой сигнал. Третий инвертор 14 инвертирует сигнал с выхода третьего компаратора 11. При нулевом сигнале на выходе первого компаратора 11 выходной сигнал третьего инвертора 14 равен единице. Когда выходной сигнал третьего инвертора 14 равен единице, происходит сброс третьего двоичного счетчика 10 в нулевое значение. После чего процесс счета возобновляется.

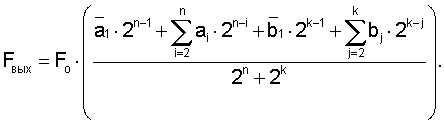

Второй компаратор 12 сравнивает выходное значение третьего двоичного счетчика 10 с константой TN-1=15. Третий компаратор 13 сравнивает выходное значение третьего двоичного счетчика 10 с константой TN+TK=20. Элемент И 15 объединяет результаты сравнения второго 12 и третьего 13 компараторов. Если выходное значение третьего двоичного счетчика 10 больше величины TN-1=15 и при этом меньше величины TN+TK=20, то на нулевой информационный вход третьего мультиплексора 9 подается единичный сигнал. Иначе на нулевой информационный вход третьего мультиплексора 9 подается сигнал, равный нулю. Когда сигнал на нулевом информационном входе третьего мультиплексора 9 равен нулю, выходной частотно-импульсный поток преобразователя становится выходным частотно-импульсным потоком первого двоичного умножителя 3. Когда же сигнал на нулевом информационном входе третьего мультиплексора 9 равен единице, выходной частотно-импульсный поток преобразователя становится выходным частотно-импульсным потоком второго двоичного умножителя 6. Таким образом, выходная последовательность импульсов Fвых на выходе преобразователя характеризуется частотой

Таким образом, применение предлагаемого преобразователя кода в частоту позволяет расширить функциональные возможности, а именно реализовать преобразование знакопеременного кода в частоту с применением цифровой коррекции, позволяющей снизить аддитивную и мультипликативную составляющие погрешности преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОСЕТЕВОЙ ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2008 |

|

RU2380752C2 |

| Преобразователь кода в частоту | 2023 |

|

RU2805259C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ОСУЩЕСТВЛЕНИЯ БЫСТРОЙ СВЕРТКИ | 1991 |

|

RU2028666C1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Преобразователь код-напряжение | 1988 |

|

SU1508348A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2016 |

|

RU2622852C1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1989 |

|

SU1679598A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для цифроаналогового преобразования знакопеременного кода в частоту с возможностью цифровой коррекции, а также в вычислительных устройствах для умножения частоты следования импульсных сигналов на параллельный двоичный код. Технический результат заключается в реализации преобразования знакопеременного кода в частоту, а также в снижении погрешности преобразования за счет введения цифровой коррекции аддитивной и мультипликативной составляющих погрешностей преобразования. Преобразователь (фиг.1) содержит первый двоичный умножитель (ДУ) (3), преобразующий входной знакопеременный код Nпр (18) в частоту Fу1, второй ДУ (6), преобразующий знакопеременный корректирующий код Nкорр в частоту Fу2, устройство (16) мультиплексирования выходных сигналов ДУ, осуществляющее мультиплексирование выходных частот двоичных умножителей (3) и (6), т.е. вставляет в частотно-импульсный поток, пропорциональный преобразуемому коду Nпр, импульсы, пропорциональные корректирующему коду Nкорр. 3 ил.

Преобразователь кода в частоту, содержащий первый двоичный умножитель, состоящий из первого двоичного счетчика и первого мультиплексора (n - число разрядов первого счетчика и число каналов первого мультиплексора), выходы разрядов первого двоичного счетчика соединены с соответствующими адресными входами первого мультиплексора, вход опорной частоты F0 преобразователя соединен со входом тактирования первого двоичного умножителя, вход тактирования первого двоичного умножителя одновременно является входом тактирования первого двоичного счетчика и нулевым информационным входом первого мультиплексора, разряды цифрового входа первого двоичного умножителя одновременно являются соответствующими информационными входами первого мультиплексора, информационные входы входного преобразуемого кода Nпр со второго по n-й соединены со входами соответствующих разрядов цифрового входа первого двоичного умножителя, выход первого двоичного умножителя одновременно является выходом первого мультиплексора, отличающееся тем, что в преобразователь введены второй двоичный умножитель, аналогичный первому двоичному умножителю, первый и второй инверторы для инверсии старших разрядов входного преобразуемого кода Nпр и входного корректирующего кода Nкорр и устройство мультиплексирования выходных сигналов двоичных умножителей, включающее в себя третий инвертор, третий мультиплексор, третий двоичный счетчик, первый, второй и третий компараторы, элемент И, старший разряд а1 входного преобразуемого кода Nпр соединен со входом первого инвертора, выход первого инвертора соединен со входом старшего разряда цифрового входа первого двоичного умножителя, разряды цифрового входа второго двоичного умножителя одновременно являются соответствующими информационными входами второго мультиплексора, разряды b2...bk входного корректирующего кода Nкорр соединены со входами соответствующих разрядов цифрового входа второго двоичного умножителя, а старший разряд b1 входного корректирующего кода Nкорр соединен со входом второго инвертора, выход второго инвертора соединен со входом старшего разряда цифрового входа второго двоичного умножителя, выходы разрядов второго двоичного счетчика соединены с соответствующими адресными входами второго мультиплексора, вход опорной частоты F0 преобразователя соединен со входом тактирования второго двоичного умножителя и входом тактирования устройства мультиплексирования выходных сигналов двоичных умножителей, вход тактирования второго двоичного умножителя одновременно является входом тактирования второго двоичного счетчика и нулевым информационным входом второго мультиплексора, вход тактирования устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является третьим входом тактирования третьего двоичного счетчика, выход первого двоичного умножителя соединен с первым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей, выход второго двоичного умножителя одновременно является выходом второго мультиплексора, первый частотный вход устройства мультиплексирования выходных сигналов двоичных умножителей является одновременно первым входом третьего мультиплексора, второй частотный вход устройства мультиплексирования выходных сигналов двоичных умножителей является одновременно вторым входом третьего мультиплексора, выход второго двоичного умножителя соединен со вторым частотным входом устройства мультиплексирования выходных сигналов двоичных умножителей, нулевой информационный вход третьего мультиплексора соединен с выходом элемента И, выход третьего мультиплексора одновременно является выходом устройства мультиплексирования выходных сигналов двоичных умножителей и выходом преобразователя, счетный выход третьего двоичного счетчика соединен с первой входной шиной первого, второго и третьего компараторов, выход первого компаратора соединен с первым входом разрешения счета третьего двоичного счетчика и со входом третьего инвертора, первая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной первого компаратора, вторая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной второго компаратора, третья входная шина устройства мультиплексирования выходных сигналов двоичных умножителей одновременно является второй входной шиной третьего компаратора, первая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой С, вторая входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой Е, третья входная шина устройства мультиплексирования выходных сигналов двоичных умножителей соединена с константой G, выход второго компаратора соединен с первым входом элемента И, выход третьего компаратора соединен со вторым входом элемента И, выход третьего инвертора соединен со вторым входом сброса третьего двоичного счетчика.

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Двоичный умножитель | 1983 |

|

SU1159018A1 |

| Двоичный умножитель | 1985 |

|

SU1575179A1 |

| US 4809211, 28.02.1989 | |||

| DE 4228767 A1, 04.03.1993 | |||

| US 6076096 A, 13.06.2000. | |||

Авторы

Даты

2006-10-20—Публикация

2005-03-21—Подача