Изобретение относится к радиосвязи и может быть использовано при демодуляции сигналов амплитудной манипуляции (АМ) в каналах с замираниями.

Известен «Демодулятор сигналов с относительной фазовой модуляцией» (ОФМ) (Патент РФ №2460225, H04L 27/22 (2006.01), H03D 3/02 (2006.01). опубл.: 27.08.2012, Бюл. № 24).

В известном демодуляторе содержащем генератор опорного сигнала, выход которого подключен к входу опорного напряжения коррелятора, сигнальный вход которого подключен к выходу стабилизатора амплитуды, вход которого подключен к выходу фильтра, вход которого является входом демодулятора, генератор тактовых импульсов, первый выход которого подключен к тактовому входу коррелятора, выход которого подключен к сигнальному входу блока стробирования, тактовый вход которого подключен к второму выходу генератора тактовых импульсов и тактовому входу решающего блока, сигнальный вход которого подключен к выходу блока вычисления модуля, вход которого подключен к выходу блока вычитания, вход которого подключен к выходу блока стробирования и входу блока задержки на длительность Т, генератор константы, причем выход решающего блока является выходом демодулятора, дополнительно введены ограничитель амплитуды, вход которого подключен к выходу блока задержки на длительность Т, а выход подключен к второму входу блока вычитания, формирующий блок, вход уровня порога, сигнальный вход и выход которого подключены соответственно к выходу генератора константы, к выходу решающего блока и к входу уровня порога решающего блока.

Недостатком известного демодулятора является ограниченность области применения, поскольку он предназначен только для приема цифровых сигналов с относительной фазовой модуляцией (ОФМ), и не обеспечивает возможность приема и демодуляции сигналов АМ в каналах с замираниями.

Известен «Демодулятор сигналов с относительной фазовой модуляцией» (Патент РФ №2460224, H04L 27/22 (2006.01), H03C 3/00 (2006.01). опубл.: 27.08.2012, Бюл. № 24).

В известном демодуляторе, содержащем генератор константы, определяющий пороговый уровень напряжения, фильтр, вход которого является входом демодулятора, а выход подключен к первому сигнальному входу коррелятора, ко второму сигнальному входу которого подключен выход генератора опорного сигнала, выход коррелятора подключен к сигнальному входу блока стробирования, тактовый вход которого подключен ко второму выходу генератора тактовых импульсов, первый выход которого подключен к установочному входу коррелятора, выход блока стробирования подключен к входу блока задержки на длительность Т и ко второму входу блока вычитания, первый вход которого подключен к выходу блока задержки на длительность Т, выход блока вычитания подключен к входу блока вычисления модуля, выход которого подключен к первому сигнальному входу решающего блока, выход которого является выходом демодулятора, а тактовый вход решающего блока подключен ко второму выходу генератора тактовых импульсов, причем коррелятор состоит из умножителя напряжений, первый и второй входы которого являются соответственно первым и вторым входами коррелятора, и интегратора, выход и установочный вход которого являются соответственно выходом и установочным входом коррелятора, причем выход умножителя напряжений подключен к сигнальному входу интегратора, решающий блок состоит из компаратора напряжений, первый сигнальный вход которого является соответственно первым сигнальным входом решающего блока, выход компаратора напряжений подключен к первому входу D-триггера, тактовый вход и выход которого являются соответственно тактовым входом и выходом решающего блока, отличающимся тем, что дополнительно введены регистр из L элементов памяти, выход которого подключен к входу счетчика единичных элементов в ячейках регистра, выход которого подключен к входу блока вычисления отклонения корреляционной функции, выход которого подключен ко второму входу блока коррекции порогового уровня напряжения, к первому входу которого подключен выход генератора константы, выход блока коррекции порогового уровня напряжения подключен ко второму сигнальному входу решающего блока, который является вторым сигнальным входом его компаратора напряжений, а вход регистра из L элементов памяти подключен к выходу решающего блока.

Недостатком устройства является ограниченность области применения, поскольку он предназначен только для приема цифровых сигналов с ОФМ. И не обеспечивает возможность приема и демодуляции сигналов АМ в каналах с замираниями.

Наиболее близким по своей технической сущности к заявленному устройству, является «Демодулятор сигналов амплитудной манипуляции» (Патент РФ №2781271, H03D 5/00 (2022.08), H04L 27/38 (2022.08). опубл.: 11.10.2022, Бюл. № 29).

Устройство-прототип содержит последовательно соединенные фильтр, умножитель напряжения и интегратор, а также блок задержки на длительность Т, компаратор напряжений и генератор опорного сигнала, выход которого соединен со вторым входом умножителя напряжения, а вход фильтра является входом устройства, кроме того, в устройство дополнительно введены последовательно соединенные сумматор и делитель напряжения на четыре, выход интегратора соединен соответственно с первыми входами компаратора напряжения, сумматора и блока задержки на длительность, выход которого соединен со вторым входом сумматора, выход делителя напряжения на четыре соединен со вторым входом компаратора напряжения, выход которого является выходом устройства.

Недостатком прототипа является ограниченность области применения, поскольку он допускает ошибки демодуляции сигналов АМ в каналах с замираниями в условиях шумов, когда на выходе интегратора уровень напряжение сохраняется как после демодуляции логической единицы, так и после демодуляции логического нуля.

Задачей изобретения является создание устройства, обеспечивающего возможность адаптивно изменять значение порога принятия решения по результатам суммирования амплитудных значений сигнальных посылок обрабатываемых на текущем и предыдущем тактах, даже при наличии на выходе интегратора ненулевого уровня напряжение как после демодуляции логической единицы, так и после демодуляции логического нуля.

Техническим результатом является снижение ошибок демодуляции сигналов АМ в каналах с замираниями в условиях шумов.

Технический результат достигается тем, что в демодулятор сигналов амплитудной манипуляции содержащий последовательно соединенные фильтр, умножитель напряжений и интегратор, последовательно соединенные сумматор и компаратор напряжений, а также генератор опорного сигнала и блок задержки на длительность символа, при этом второй вход умножителя напряжения соединен с выходом генератора опорного сигнала, а выход интегратора соединен со входом блока задержки на длительность символа и вторым входом компаратора напряжений, выход которого является выходом устройства дополнительно содержит первый делитель напряжения на два, вход которого соединен с выходом интегратора, а выход – с первым входом сумматора, а также второй делитель напряжения на два, вход которого соединен с выходом блока задержки на длительность символа, а выход – со вторым входом сумматора.

Благодаря новой совокупности существенных признаков, а именно блоков и связей, в заявленном устройстве происходит адаптивное изменение значение порога принятия решения по результатам суммирования амплитудных значений сигнальных посылок обрабатываемых на текущем и предыдущем тактах, даже при наличии на выходе интегратора ненулевого уровня напряжение как после демодуляции логической единицы, так и после демодуляции логического нуля, что обеспечивает возможность снижения ошибок демодуляции сигналов АМ в каналах с замираниями.

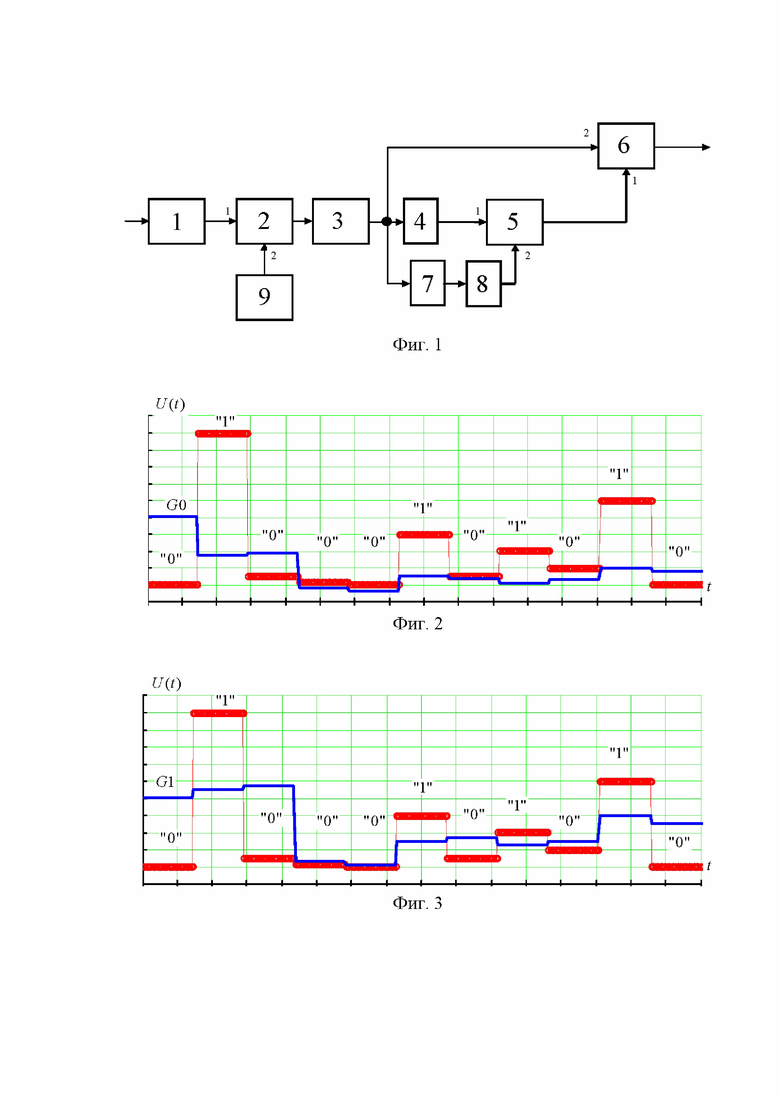

Заявленное изобретение поясняется чертежами, где на фиг.1 – блок-схема демодулятора сигналов АМ:

1 – фильтр;

2 – умножитель напряжений;

3 – интегратор;

4 – первый делитель напряжения на два;

5 – сумматор;

6 – компаратор напряжений;

7 – блок задержки на длительность символа;

8 – второй делитель напряжения на два;

9 – генератор опорного сигнала;

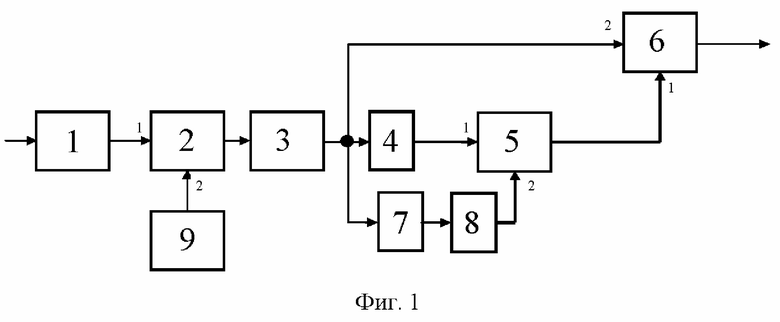

на фиг. 2 – фрагмент демодулированной последовательности сигнала АМ, прошедшего канал с замираниями, и нанесенным значением уровня порога принятия решения G0 – порог принятия решения, значение которого вычисляют по результатам суммирования амплитудных значений сигнальных посылок обрабатываемых на текущем и предыдущем тактах в соответствии с прототипом.

на фиг. 3 – фрагмент демодулированной последовательности сигнала АМ, прошедшего канал с замираниями, и нанесенным значением уровня порога принятия решения G1 – порог принятия решения, значение которого вычисляют по результатам суммирования амплитудных значений сигнальных посылок обрабатываемых на текущем и предыдущем тактах в соответствии с заявляемым демодулятором.

Демодулятор сигналов амплитудной манипуляции содержит последовательно соединенные фильтр 1, умножитель напряжений 2, интегратор 3, первый делитель напряжения на два 4, сумматор 5 и компаратор напряжений 6, при этом вход фильтра 1 является входом устройства, а выход компаратора напряжений 6 – выходом устройства, последовательно соединенные блок задержки на длительность символа 7 и второй делитель напряжения на два 8, выход которого соединен со вторым входом сумматора 5, генератор опорного сигнала 9, выход которого соединен со вторым входом умножителя напряжений 2, при этом выход интегратора 3 соединен со вторым входом компаратора напряжений 6 и входом блока задержки на длительность символа 7.

Блоки, входящие в общую схему устройства, имеют следующее назначение.

Фильтр 1 предназначен для фильтрации принятого сигнала АМ.

В качестве фильтра 1 используется фильтр, аналогичный представленному в см. (патент RU № 2460225, H04L 27/22 (2006.01), H03D 3/02 (2006.01). Опубликовано: 27.08.2012 Бюл. № 24).

Умножитель напряжений 2 предназначен для вычисления корреляционной функции посредством перемножения принятого сигнала АМ и опорного сигнала.

В качестве умножителя напряжений 2 используется умножитель, аналогичный умножителю в см. (патент RU № 2549360, H03D 3/00 (2006.01). Опубликовано: 27.04.2015 Бюл. № 12).

В качестве интегратора 3 используется интегратор, аналогичный интегратору в см. (патент RU № 2549360, H03D 3/00 (2006.01). Опубликовано: 27.04.2015 Бюл. № 12, или см. патент RU № 2454014, H04L 13/18 (2006.01), H04L 27/00 (2006.01). Опубликовано: 20.06.2012 Бюл. № 17).

В качестве сумматора 5 может быть использован блок, аналогичный блоку в см. (патент RU № 2486681, H04L 7/00 (2006.01). Опубликовано: 27.06.2013 Бюл. № 18).

Компаратор напряжений 6 предназначен для установления требуемого значения уровня порога под действием напряжения с блока 8, и принятия решения о демодулированном символе.

В качестве компаратора напряжений 6 может быть использован блок, аналогичный блоку из состава устройства, описанного в способе-прототипе, см. (патент RU № 2460224, H04L 27/22 (2006.01), H03C 3/00 (2006.01). Опубликовано: 27.08.2012 Бюл. № 24). Работа пороговых устройств подробно рассмотрена в (патент RU № 2382495, H04B 1/10 (2006.01), Опубликовано: 20.02.2010 Бюл. № 5).

Блок задержки на длительность символа 7 предназначен для задержки сигнала на длительность сигнальной посылки.

В качестве блока задержки на длительность символа можно использовать блок, аналогичный блоку в см. (патент RU № 2460224, H04L 27/22 (2006.01), H03C 3/00 (2006.01). Опубликовано: 27.08.2012 Бюл. № 24).

Генератор опорного сигнала 9 предназначен для формирования опорного гармонического сигнала, соответствующего структуре гармонического сигнала, используемого в передающем устройстве для формирования сигнала АМ.

Делитель напряжения на два, обозначенный на фиг.1 как блок 4 и 8, предназначен для уменьшения поступающего на его вход значения напряжения в два раза.

Делитель напряжения на два можно реализовать или на микросхеме 174ПС1, см. Справочник разработчика и конструктора РЭА. Элементная база. Кн.1. – М., 1993. Сост. Масленников М.Ю., Соболев Е.А. и др., в соответствии с (патент RU № 2549360, H03D 3/00 (2006.01). Опубликовано: 27.04.2015 Бюл. № 12), или см. (патент RU № 2382495, H04B 1/10 (2006.01). Опубликовано: 20.02.2010 Бюл. № 5).

Заявленное устройство работает следующим образом.

Приходящий по каналу связи сигнал S1(t) подают на вход фильтра 1, который является входом демодулятора. В фильтре 1 осуществляют ослабление частотных составляющих, находящихся вне полосы частот демодулируемого сигнала.

На выходе фильтра 1 получают отфильтрованный сигнал Z(t), который подают на вход умножителя напряжений 2, на второй вход которого с генератора опорного сигнала 9 подают опорный сигнал с постоянной амплитудой S0(t), который является аналогичным по своей структуре сигналу, используемому на передающей стороне для формирования сигнала АМ. Разница между сигнала S1(t) и S0(t) будет обусловлена влиянием аддитивных шумов и замираний в канале связи.

На выходе умножителя напряжений 2 получают результирующий сигнал Y(t), который подают вход интегратора 3, на выходе которого формируют низкочастотную импульсную последовательность U(t).

При наличии замираний в канале связи амплитуда сигнал S1(t) будет различной, и ее величина будет определяться характером замираний. Поэтому и амплитуда импульсов последовательности U(t), получаемой после интегратора 3 также будет различной. При этом, в случае наличия шумов в канале приема, на выходе интегратора будет наблюдаться ненулевой уровень напряжения как после демодуляции логической единицы, так и после демодуляции логического нуля.

В качестве примера на фиг. 3 показаны импульсы последовательности U(t) с различной амплитудой (на фиг. 3 показано, что напряжение на выходе компаратора в результате шумов аддитивного характера сохраняется даже при передаче логического нуля).

С выхода интегратора 3 импульсы последовательности U(t) одновременно подают на вход компаратора напряжений 6, на вход первого делителя напряжений на два 4 и на вход блока задержки на длительность символа 7.

В блоке 7 происходит задержка импульса на длительность, равную длительности сигнальной посылки, т.е. на длительность импульса. В результате, в тот момент, когда на вход сумматора 5 через первый делитель напряжения на два 4 поступает очередной импульс последовательности U(t), на второй вход сумматора 5 через второй делитель напряжения на два 7 поступает импульс предыдущей сигнальной посылки этой же последовательности U(t).

Таким образом, на выходе сумматора 5 формируют импульсную последовательность С(t), каждый импульс которой равен сумме половины напряжения текущего и половине напряжения предыдущего импульса последовательности U(t).

С выхода сумматора 5 импульсную последовательность С(t) подают на вход компаратора напряжений 6, где происходит пороговое сравнение импульсов последовательности U(t), поступающих на его первый вход, с пороговыми значениями, определяемыми импульсами последовательности С(t). В качестве примера на фиг. 3 введено обозначение «1» для импульсов превысивших пороговое значение и «0» для импульсов, не превысивших пороговое значение.

По результатам попарного сравнения, на длительности каждой сигнальной посылки на выходе компаратора напряжений 6, являющегося выходом демодулятора, происходит принятие решения о соответствии принятого импульса информационному значению «1» или «0».

В качестве примера на фиг 3 показан фрагмент импульсов последовательности U(t) с различной амплитудой и установленные значения порога принятия решения G1. Здесь G1 – сформирован из импульсов последовательности С(t).

Импульсы последовательности U(t) превысившие порог принятия решения соответствуют информационному значению «1», а не превысившие - информационному значению «0» (обозначены на фиг. 3).

Импульсы последовательности U(t) превысившие порог принятия решения соответствуют информационному значению «1», а не превысившие - информационному значению «0» (обозначены на фиг. 2).

В качестве примера, на фиг. 2 показан результат демодуляции фрагмента импульсов последовательности U(t) с использованием порог принятия решения G0, значение которого сформировано в соответствии с наиболее близким аналогом

Очевидно, что выбор значения порога принятия решения G0 не обеспечивает возможность демодуляции сигналов АМ, принятых в каналах с замираниями, так как возможны ошибочные решения. А применение порога принятия решения G1 обеспечивает, что указывает на достижение заявляемого технического результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор сигналов амплитудной манипуляции | 2022 |

|

RU2781271C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460225C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| Способ демодуляции сигналов | 2022 |

|

RU2786193C1 |

| Способ демодуляции сигналов | 2021 |

|

RU2766877C1 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2003 |

|

RU2271071C2 |

| ИЗМЕРИТЕЛЬ ФАЗ ОСЦИЛЛОГРАФИЧЕСКИЙ | 2005 |

|

RU2314543C2 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| Автокорреляционный демодулятор псевдослучайных сигналов с относительной фазовой модуляцией второго порядка | 2017 |

|

RU2660594C1 |

Изобретение относится к радиосвязи и может быть использовано при демодуляции сигналов амплитудной манипуляции (АМ) в каналах с замираниями. Техническим результатом является снижение ошибок демодуляции сигналов АМ в каналах с замираниями в условиях шумов. Такой технический результат обеспечивается за счет адаптивного изменения значения порога принятия решения по результатам суммирования половинных амплитудных значений сигнальных посылок, обрабатываемых на текущем и предыдущем тактах, которое осуществляется за счет дополнительного введения в демодулятор первого делителя напряжения на два, вход которого соединен с выходом интегратора, а выход – с первым входом сумматора, а также за счет введения второго делителя напряжения на два, вход которого соединен с выходом блока задержки на длительность символа, а выход – со вторым входом сумматора. 3 ил.

Демодулятор сигналов амплитудной манипуляции, содержащий последовательно соединенные фильтр, умножитель напряжений и интегратор, последовательно соединенные сумматор и компаратор напряжений, а также генератор опорного сигнала и блок задержки на длительность символа, при этом второй вход умножителя напряжения соединен с выходом генератора опорного сигнала, а выход интегратора соединен со входом блока задержки на длительность символа и вторым входом компаратора напряжений, выход которого является выходом устройства, отличающийся тем, что устройство дополнительно содержит первый делитель напряжения на два, вход которого соединен с выходом интегратора, а выход – с первым входом сумматора, а также второй делитель напряжения на два, вход которого соединен с выходом блока задержки на длительность символа, а выход – со вторым входом сумматора.

| Демодулятор сигналов амплитудной манипуляции | 2022 |

|

RU2781271C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| US 5270666 A, 14.12.1993 | |||

| US 5661761 A, 26.08.1997 | |||

| Тормозной инерционный стенд для испытаний инерционных регуляторов торможения | 1983 |

|

SU1122532A1 |

| EP 1959624 B1, 12.08.2015. | |||

Авторы

Даты

2023-11-28—Публикация

2023-07-05—Подача