ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области электротехники, автоматики, электроники, микроэлектроники и может использоваться при проектировании интегральных схем, стабилизаторов напряжения, аналого-цифровых и цифроаналоговых преобразователей и других элементов автоматики.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известен источник опорного напряжения (RU №2332702 С1, МПК G05F 3/24, заявлен 07.03.2007, опубл. 27.08.2008, БИ №24), содержащий токостабилизирующий двухполюсник, три n-канальных МОП транзистора и резистор.

Недостатком источника опорного напряжения является то, что повышенная стабильность выходного напряжения обеспечивается только по отношению к изменению напряжения питания, и не учитывает влияние температуры.

Известен источник опорного напряжения (RU №2473951 С1, МПК G05F 3/26, заявлен 17.01.2012, опубл. 27.01.2013, БИ №3), содержащий два p-n-р и четыре n-р-n биполярных транзисторов, 5 резисторов.

Недостатком схемы является:

- применение биполярных транзисторов различного типа проводимости, что требует усложнения технологии при использовании этой схемы в составе КМОП микросхем,

- обеспечение высокой стабильности выходного напряжения только при изменении температуры,

- сложность схемы.

Известен источник опорного напряжения (RU №2673243 С1 МПК G05F 3/24, 3/26, заявлен 24.01.2018, опубл. 23.11.2018, БИ №33), содержащий пять р-канальных, четыре n-канальных МДП транзисторов, два резистора, два диода.

Недостатком схемы является:

- сложность схемы,

- повышение стабильности выходного напряжения только по отношению к изменению напряжения питания,

- использование МДП транзисторов и биполярных структур - диодов, что усложняет технологию изготовления.

Наиболее близким устройством того же назначения, к заявленному изобретению, по совокупности признаков, является принятый за прототип источник опорного напряжения (US 9471084 В2 МПК G05F 3/16, заявлен 13.08.2015, опубл. 18.10.2016), содержащий три р-канальных МОП транзистора PMOS1, PMOS2, PMOS3 три биполярных n-р-n транзистора NPN1, NPN2, NPN3, четыре резистора Rl, R2, R3, R4, вывод VDD питания верхнего уровня, вывод питания нижнего уровня (символ «земля»), вывод VREF опорного напряжения, причем истоки первого PMOS1, второго PMOS2 и третьего PMOS3 р-канальных МОП транзисторов соединены с выводом VDD питания верхнего уровня, затворы первого PMOS1 и второго PMOS2 р-канальных МОП транзисторов соединены со стоком первого PMOS1 р-канального МОП транзистора, затвор третьего PMOS3 р-канального МОП транзистора соединен со стоком второго PMOS2 р-канального МОП транзистора, сток третьего PMOS3 р-канального МОП транзистора соединен с выводом VREF опорного напряжения и первым выводом четвертого R4 резистора, базы первого NPN1, второго NPN2 и третьего NPN3 n-р-n транзисторов соединены с коллектором третьего NPN3 n-р-n транзистора и вторым выводом четвертого R4 резистора, коллекторы первого NPN1 и второго NPN2 n-р-n транзисторов соединены со стоками первого PMOS1 и второго PMOS2 р-канальных МОП транзисторов соответственно, эмиттер второго NPN2 n-р-n транзистора соединен с первым выводом первого R1 резистора, эмиттер первого NPN1 n-р-n транзистора соединен со вторым выводом первого R1 резистора и первым выводом второго R2 резистора, эмиттер третьего NPN3 n-р-n транзистора соединен с первым выводом третьего R3 резистора, второй вывод второго R2 резистора соединен со вторым выводом третьего R3 резистора и с выводом питания нижнего уровня.

Недостатком данного технического решения является повышенная потребляемая мощность, относительная сложность схемы - совместное использование биполярных и МОП транзисторов, что нарушает однородность и усложняет технологию изготовления КМОП микросхем.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задача, на решение которой направлено предлагаемое изобретение, заключается в создании компактного, малопотребляющего, простого в изготовлении устройства с высокой стабильностью выходного напряжения при изменении напряжения питания и температуры.

Техническим результатом предлагаемого изобретения является расширение арсенала средств того же назначения, в части возможности сохранения стабильности вырабатываемого выходного опорного напряжения при изменении напряжения питания и температуры, при одновременном упрощении схемы и повышении ее однородности, снижении потребляемой мощности и уменьшении площади, занимаемой на кристалле.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что в источник опорного напряжения, содержащий первый ТР1, второй ТР2 и третий ТП3 р-канальные МОП транзисторы, первый R1 и второй R2 резисторы, вывод питания верхнего уровня VDD, вывод питания нижнего уровня VSS, вывод опорного напряжения VREF, причем истоки первого ТР1, второго ТР2 и третьего ТП3 р-канальных МОП транзисторов соединены с выводом питания верхнего уровня VDD, затворы первого TP1 и второго ТР2 р-канальных МОП транзисторов соединены со стоком первого ТР1 р-канального МОП транзистора, затвор третьего ТП3 р-канального МОП транзистора соединен со стоком второго ТР2 р-канального МОП транзистора, сток третьего ТП3 р-канального МОП транзистора соединен с выводом опорного напряжения VREF, второй вывод первого резистора R1 соединен с первым выводом второго резистора R2, второй вывод второго резистора R2 соединен с выводом питания нижнего уровня VSS, дополнительно введены первый TN1 и второй TN2 n-канальные МОП транзисторы, четвертый ТР4 р-канальный МОП транзистор, исток первого TN1 n-канального МОП транзистора соединен с первым выводом второго резистора R2, исток второго TN2 n-канального МОП транзистора соединен с первым выводом первого резистора R1, затворы первого TN1 и второго TN2 n-канальных МОП транзисторов соединены с выводом опорного напряжения VREF, сток первого TN1 n-канального МОП транзистора соединен со стоком первого ТР1 р-канального МОП транзистора, сток второго TN2 n-канального МОП транзистора соединен со стоком второго ТР2 р-канального МОП транзистора, исток четвертого ТР4 р-канального МОП транзистора соединен с выводом опорного напряжения VREF, а затвор и сток четвертого ТР4 р-канального МОП транзистора соединены с выводом питания нижнего уровня VSS.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

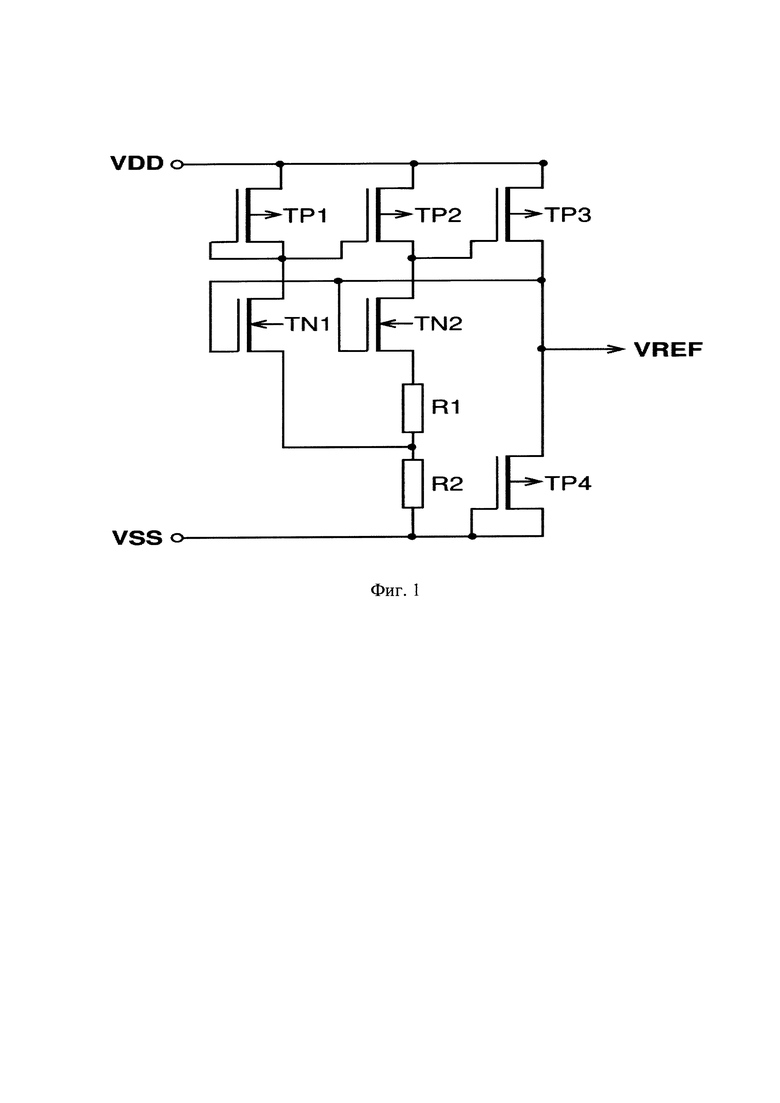

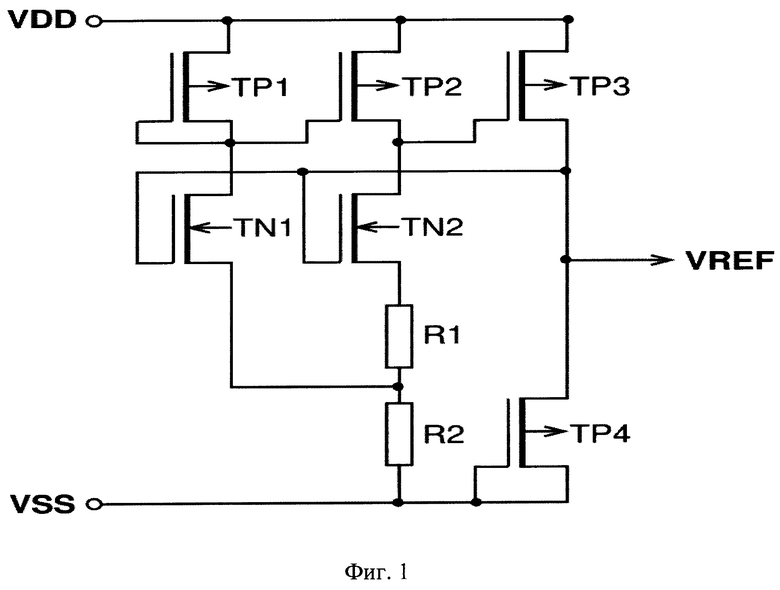

На фиг. 1 приведена электрическая схема предлагаемого источника опорного напряжения.

На фиг. 1 и в тексте приняты следующие обозначения:

VDD - вывод питания верхнего уровня,

VREF - вывод опорного напряжения,

VSS - вывод питания нижнего уровня,

ТР1, ТР2, ТП3, ТР4 - первый, второй, третий и четвертый р-канальные МОП транзисторы,

TN1, TN2 - первый и второй n-канальные МОП транзисторы,

R1, R2 - первый и второй резисторы.

Предлагаемый источник опорного напряжения содержит первый ТР1, второй ТР2, третий ТП3 и четвертый ТР4 р-канальные МОП транзисторы, первый TN1 и второй TN2 n-канальные МОП транзисторы, первый R1 и второй R2 резисторы, вывод питания верхнего уровня VDD, вывод питания нижнего уровня VSS, вывод опорного напряжения VREF.

Причем истоки первого ТР1, второго ТР2 и третьего ТП3 р-канальных МОП транзисторов соединены с выводом питания верхнего уровня VDD. Затворы первого ТР1 и второго ТР2 р-канальных МОП транзисторов соединены со стоком первого ТР1 р-канального МОП транзистора.

Затвор третьего ТП3 р-канального МОП транзистора соединен со стоком второго ТР2 р-канального МОП транзистора, а сток третьего ТП3 р-канального МОП транзистора соединен с выводом опорного напряжения VREF.

Кроме того, второй вывод первого резистора R1 соединен с первым выводом второго резистора R2, а второй вывод второго резистора R2 соединен с выводом питания нижнего уровня VSS.

Причем исток первого TN1 n-канального МОП транзистора соединен с первым выводом второго резистора R2, а исток второго TN2 n-канального МОП транзистора соединен с первым выводом первого резистора R1. Затворы первого TN1 и второго TN2 n-канальных МОП транзисторов соединены с выводом опорного напряжения VREF, а сток первого TN1 n-канального МОП транзистора соединен со стоком первого ТР1 р-канального МОП транзистора, сток второго TN2 n-канального МОП транзистора соединен со стоком второго ТР2 р-канального МОП транзистора.

Кроме того, исток четвертого ТР4 р-канального МОП транзистора соединен с выводом опорного напряжения VREF, а затвор и сток четвертого ТР4 р-канального МОП транзистора соединены с выводом питания нижнего уровня VSS.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

В основу работы предлагаемого устройства положен бандгап Пола Брокау.

В устройстве первый ТР1 и второй ТР2 р-канальные МОП транзисторы, включенные по схеме токового зеркала, служат источниками постоянного тока равной величины для работы транзисторной пары первого TN1 и второго TN2 n-канальных МОП транзисторов. При этом плотность тока во втором транзисторе TN2 должна быть меньше, чем в первом транзисторе TN1. Второй транзистор TN2 выполнен составным, состоящим из нескольких параллельно включенных транзисторов, идентичных транзистору TN1. Из-за разности плотностей тока напряжение VTN1 между затвором и истоком в первом транзисторе TN1 больше, чем напряжение VTN2 во втором транзисторе TN2 на величину разности напряжения ΔV=VTN1-VTN2. При этом разность напряжения ΔV определяется по формуле:

где k - постоянная Больцмана, Τ - температура кристалла, q - заряд электрона, χ - коэффициент, равный отношению плотностей тока первого ΤΝ1 и второго ΤΝ2 n-канальных МОП транзисторов.

Разность напряжения ΔV транзисторной пары первого ΤΝ1 и второго ΤΝ2 n-канальных МОП транзисторов зависит от коэффициента χ, прямо пропорциональна температуре Τ и не зависит от разброса технологических параметров, которые на кристалле одинаково влияют на первый ΤΝ1 и второй ΤΝ2 n-канальные МОП транзисторы.

Через первый ΤΝ1 и второй ΤΝ2 n-канальные МОП транзисторы протекают равные токи, величиной I=ΔV/R1. При этом ток, протекающий через резистор R2, равен удвоенному значению тока I. Выходное опорное напряжение VREF определяется по формуле:

VREF=VTN1+2×ΔV×(R2/R1),

где VTN1 - напряжение между затвором и истоком первого TN1 n-канального МОП транзистора при постоянном токе I. Разность напряжения ΔV линейно возрастает с ростом температуры (1). Напряжение VTN1 убывает с ростом температуры почти линейно на величину близкую к минус 2 мВ/град. Для значения тока I и коэффициента χ определяют величину сопротивлений резисторов R2, R1 и их отношение, при которых изменение напряжений VTN1 и ΔV компенсируют друг друга и обеспечивают стабильность выходного опорного напряжения VREF. Усилитель напряжения на третьем ТП3 р-канальном МОП транзисторе с диодной нагрузкой на четвертом ТР4 р-канальном МОП транзисторе позволяет уменьшить влияние напряжения питания на выходное опорное напряжение VREF.

ПРИМЕР ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Работоспособность предлагаемого источника опорного напряжения и его сравнение с прототипом была проверена средствами САПР компании Cadence. Моделирование проводилось с использованием КМОП технологических библиотек с проектными нормами 28 нм и транзисторов с минимальной площадью. Проведена оптимизация параметров и аналоговое моделирование схем предлагаемого источника и прототипа.

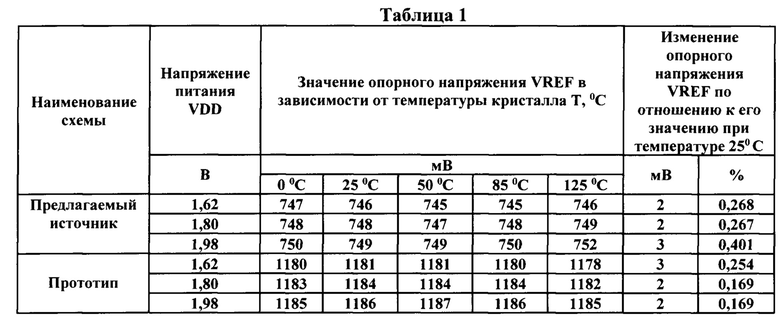

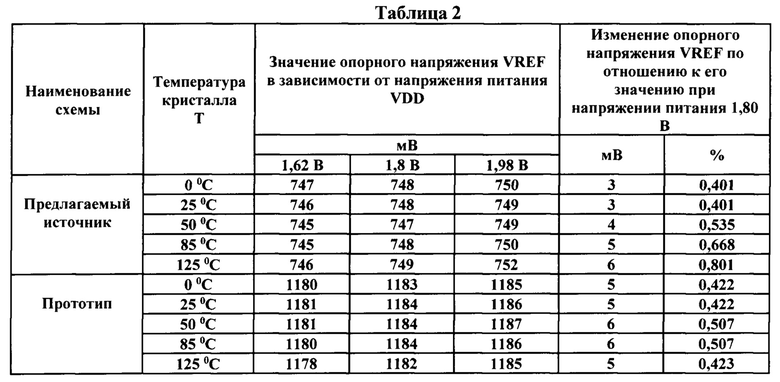

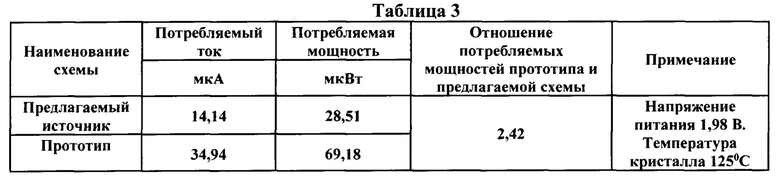

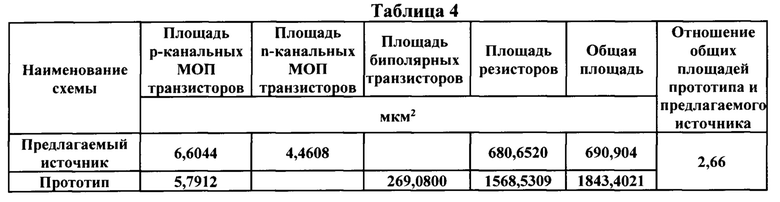

Результаты моделирования предлагаемого устройства и прототипа приведены в таблицах 1-4.

В таблице 1 приведены результаты значений и изменений опорного напряжения VREF при напряжении питания 1,62 В; 1,80 В и 1,98 В в зависимости от изменения температуры Τ в диапазоне от 0°С до 125°С. При этом изменение опорного напряжения VREF не превышают 3 мВ.

В таблице 2 приведены результаты значений и изменений опорного напряжения VREF при изменении температуры Τ в диапазоне от 0°С до 125°С в зависимости от изменения напряжения питания от 1,62 В до 1,98 В. При этом изменение опорного напряжения VREF не превышают 6 мВ.

Таким образом, предлагаемое устройство и прототип обеспечивают высокую стабильность опорного напряжения VREF.

В таблице 3 приведены значения потребляемых тока и мощности для предлагаемого устройства и прототипа. При этом при напряжении питания VDD=1,98 В и температуре Τ=125°С предлагаемое устройство потребляет в 2,4 раза меньшую мощность, чем прототип.

В таблице 4 приведены значения площади, занимаемой компонентами предлагаемого устройства и прототипа. При этом предлагаемое устройство обладает однородностью, так как содержит только МОП транзисторы, а его компоненты занимают в 2,6 раза меньшую площадь на кристалле по сравнению с прототипом.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый источник опорного напряжения соответствует заявляемому техническому результату в части возможности сохранения стабильности вырабатываемого выходного опорного напряжения VREF при изменении напряжения питания VDD и температуры кристалла Т, при одновременном упрощении схемы и повышении ее однородности, потребляет меньшую мощность, занимает меньшую площадь на кристалле.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОРРЕКЦИИ СКВАЖНОСТИ ВХОДНОГО СИГНАЛА | 2011 |

|

RU2467473C1 |

| СПОСОБ И СХЕМА УМЕНЬШЕНИЯ УТЕЧЕК И СТАБИЛИЗАЦИИ ПОРОГОВЫХ НАПРЯЖЕНИЙ МОП ТРАНЗИСТОРОВ В ИС | 2013 |

|

RU2520426C1 |

| Малошумящий источник опорного напряжения | 2023 |

|

RU2813175C1 |

| ЕМКОСТНАЯ МОП ДИОДНАЯ ЯЧЕЙКА ФОТОПРИЕМНИКА-ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2014 |

|

RU2583955C1 |

| РЕГУЛИРУЕМОЕ ВХОДНОЕ ПРИЕМНОЕ УСТРОЙСТВО ДЛЯ ВЫСОКОСКОРОСТНОГО ИНТЕРФЕЙСА С НИЗКИМ УРОВНЕМ МОЩНОСТИ | 2008 |

|

RU2468509C2 |

| СВЕТОДИОДНЫЕ ИСТОЧНИКИ ПОДСВЕТКИ ДЛЯ ЖИДКОКРИСТАЛЛИЧЕСКИХ УСТРОЙСТВ И ЖИДКОКРИСТАЛЛИЧЕСКИЕ УСТРОЙСТВА | 2014 |

|

RU2669061C2 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА ОСНОВЕ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ | 2014 |

|

RU2620502C2 |

| Устройство управления яркостью светодиодов коллиматора (варианты) | 2021 |

|

RU2778343C1 |

| ТРОИЧНЫЙ К-МОП-С ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИЛИ-НЕ" | 2011 |

|

RU2468510C1 |

Изобретение относится к области электротехники, автоматики, электроники, микроэлектроники и может использоваться при проектировании интегральных схем, стабилизаторов напряжения, аналого-цифровых и цифроаналоговых преобразователей и других элементов автоматики. Задача, на решение которой направлено предлагаемое изобретение, заключается в создании компактного, малопотребляющего, простого в изготовлении устройства с высокой стабильностью выходного напряжения при изменении напряжения питания и температуры. Техническим результатом предлагаемого изобретения является расширение арсенала средств того же назначения, в части возможности сохранения стабильности вырабатываемого выходного опорного напряжения при изменении напряжения питания и температуры, при одновременном упрощении схемы и повышении ее однородности, снижении потребляемой мощности и уменьшении площади, занимаемой на кристалле. Указанный результат достигается за счет того, что устройство содержит первый ТР1, второй ТР2, третий ТР3 и четвертый ТР4 р-канальные МОП транзисторы, первый TN1 и второй TN2 n-канальные МОП транзисторы, первый R1 и второй R2 резисторы, вывод питания верхнего уровня VDD, вывод питания нижнего уровня VSS, вывод опорного напряжения VREF. 4 табл., 1 ил.

Источник опорного напряжения, содержащий первый ТР1, второй ТР2 и третий ТР3 р-канальные МОП транзисторы, первый R1 и второй R2 резисторы, вывод питания верхнего уровня VDD, вывод питания нижнего уровня VSS, вывод опорного напряжения VREF, причем истоки первого ТР1, второго ТР2 и третьего ТР3 р-канальных МОП транзисторов соединены с выводом питания верхнего уровня VDD, затворы первого ТР1 и второго ТР2 р-канальных МОП транзисторов соединены со стоком первого ТР1 р-канального МОП транзистора, затвор третьего ТР3 р-канального МОП транзистора соединен со стоком второго ТР2 р-канального МОП транзистора, сток третьего ТР3 р-канального МОП транзистора соединен с выводом опорного напряжения VREF, второй вывод первого резистора R1 соединен с первым выводом второго резистора R2, второй вывод второго резистора R2 соединен с выводом питания нижнего уровня VSS, отличающийся тем, что в него дополнительно введены первый TN1 и второй TN2 n-канальные МОП транзисторы, четвертый ТР4 р-канальный МОП транзистор, исток первого TN1 n-канального МОП транзистора соединен с первым выводом второго резистора R2, исток второго TN2 n-канального МОП транзистора соединен с первым выводом первого резистора R1, затворы первого TN1 и второго TN2 n-канальных МОП транзисторов соединены с выводом опорного напряжения VREF, сток первого TN1 n-канального МОП транзистора соединен со стоком первого ТР1 р-канального МОП транзистора, сток второго TN2 n-канального МОП транзистора соединен со стоком второго ТР2 р-канального МОП транзистора, исток четвертого ТР4 р-канального МОП транзистора соединен с выводом опорного напряжения VREF, а затвор и сток четвертого ТР4 р-канального МОП транзистора соединены с выводом питания нижнего уровня VSS.

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2007 |

|

RU2332702C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2012 |

|

RU2473951C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2018 |

|

RU2673243C1 |

| US 9471084B2, 18.10.2016 | |||

| US 6118266A, 12.09.2000. | |||

Авторы

Даты

2022-03-22—Публикация

2021-07-21—Подача