Изобретение относится к устройствам автоматической регулировки усиления и может быть использовано в приёмных устройствах, в частности в приемных устройствах радиорелейной связи.

Известны устройства автоматической регулировки усиления, например, описанные в [1], [2, стр.101], [3, стр. 134], [4, стр. 87], [5, стр. 223], [6], [7]. Однако эти устройства не обеспечивают корректное функционирование в приёмо-передающей аппаратуре, работающей в полудуплексном режиме.

Наиболее близким аналогом по технической сущности к предлагаемому является устройство, описанное в [1], которое принято за прототип.

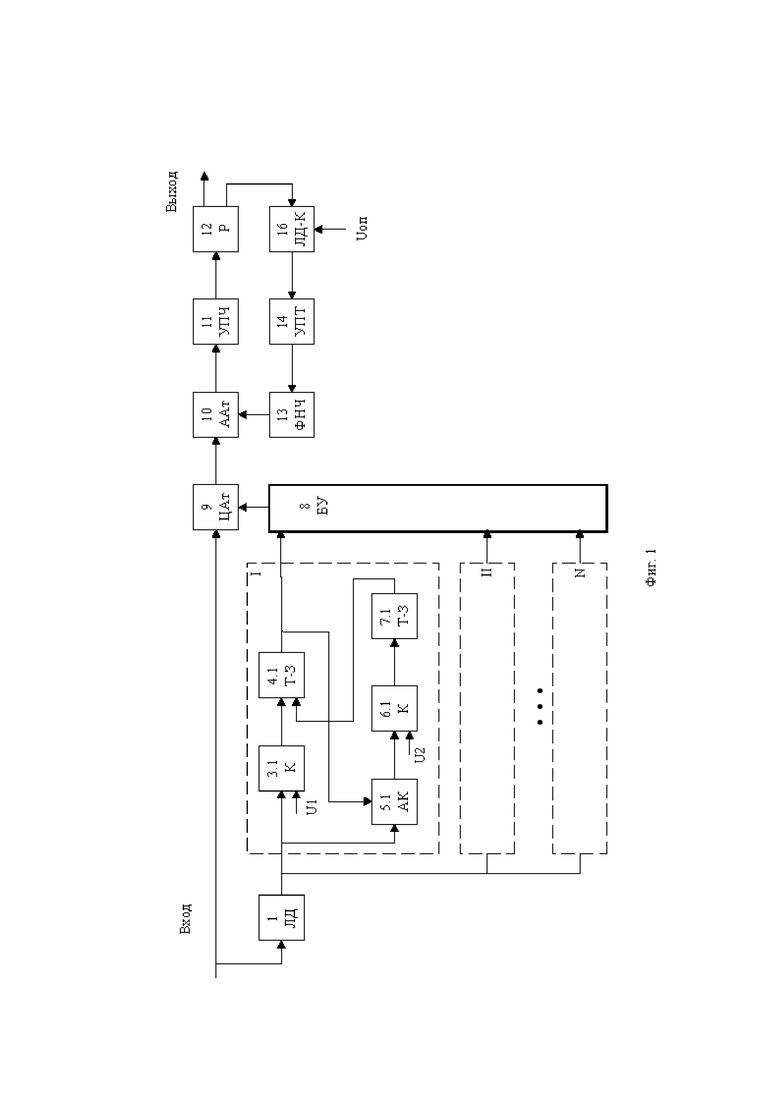

Функциональная схема устройства-прототипа приведена на фиг. 1 где введены следующие обозначения:

1 – логарифмический детектор (ЛД);

I, II, N – блоки регистрации уровня входного сигнала;

3.1, 6.1 – первый и второй компараторы (К);

4.1, 7.1 – первый и второй триггеры-защёлки (Т-З);

5.1 – аналоговый ключ (АК);

8 – блок управления (БУ);

9 – цифровой аттенюатор (ЦАт);

10 – аналоговый аттенюатор (ААт);

11 – усилитель промежуточной частоты (УПЧ);

12 – разветвитель (Р);

13 – фильтр нижних частот (ФНЧ);

14 – усилитель постоянного тока (УПТ);

16 – логарифмический детектор/контроллер (ЛД-К).

Устройство-прототип содержит последовательно соединенные цифровой аттенюатор 9, аналоговый аттенюатор 10, усилитель промежуточной частоты 11, выход которого соединен с входом разветвителя 12, один выход которого является выходом устройства, а другой выход соединен с сигнальным входом логарифмического детектора/контроллера 16, другой вход которого является входом опорного напряжения Uоп. При этом выход логарифмического детектора/контроллера 16 через последовательно соединенные усилитель постоянного тока 14 и фильтр нижних частот 13 соединен со вторым входом аналогового аттенюатора 10. Входы логарифмического детектора 1 и цифрового аттенюатора 9 объединены и являются входом устройства.

Выход логарифмического детектора 1 соединен с объединенными входами N идентичных блоков регистрации уровня входного сигнала I, II…N. Каждый из N блоков регистрации уровня входного сигнала содержит последовательно соединенные первый компаратор 3.1, первый триггер-защёлку 4.1, выход которого подключен к управляющему входу аналогового ключа 5.1, выход которого через последовательно соединенные второй компаратор 6 и второй триггер-защёлку 7.1 соединен со входом сброса первого триггера-защёлки 4.1, выход которого является выходом блока регистрации уровня входного сигнала и соединен с соответствующим входом блока управления 8, выход которого соединен со вторым входом цифрового аттенюатора 9. При этом первый вход первого компаратора 3.1 соединен с входом аналогового ключа 5.1 и является входом блока регистрации уровня входного сигнала. Второй вход первого компаратора 3.1 является входом первого порогового напряжения U1. Второй вход второго компаратора 6 является входом второго порогового напряжения U2. Выходы остальных (N-1) блоков регистрации уровня входного сигнала соединены с соответствующими входами блока управления 8.

Устройство-прототип работает следующим образом.

Входной сигнал устройства через цифровой аттенюатор 9 поступает на первый вход аналогового аттенюатора 10, работающего в составе петли автоматической регулировки усиления (АРУ), состоящей из аналогового аттенюатора 10, усилителя промежуточной частоты 11, разветвителя 12, логарифмического детектора/контроллера 16, усилителя постоянного тока 14 и фильтра нижних частот 13. Усилитель промежуточной частоты 11 обеспечивает усиление входного сигнала устройства до минимального уровня, необходимого для нормальной работы логарифмического детектора/контроллера 16. Напряжение Uоп, подаваемое на опорный вход логарифмического детектора/контроллера 16, задаёт уровень выходного сигнала петли аналоговой АРУ, который поддерживается постоянным.

При увеличении уровня входного сигнала устройства напряжение на выходе логарифмического детектора 1 растёт и при увеличении уровня сигнала, превышающего порог U1 компаратора 3.1 первого блока регистрации уровня входного сигнала I первый компаратор 3.1 изменяет логический уровень на своём выходе и тем самым приводит к срабатыванию первого триггера-защёлки 4.1. Выходной сигнал триггера-защёлки 4.1 поступает на блок управления 8, который вырабатывает команду на увеличение ослабления цифрового аттенюатора 9. Блок управления 8 может быть реализован в виде логического дешифратора.

После этого аналоговый аттенюатор 10 вынужден уменьшить ослабление, чтобы петля АРУ вернулась в состояние равновесия. Если входной сигнал будет флуктуировать и несколько уменьшаться, аналоговый аттенюатор 10 будет компенсировать это уменьшение, имея запас на уменьшение ослабления. Таким образом, не произойдёт хаотичного переключения цифрового аттенюатора 9 из рабочего состояния в исходное состояние 0 дБ и обратно.

При снижении уровня входного сигнала сигнал с выхода аналогового ключа 5.1 становится меньше порога U2 второго компаратора 6.1, компаратор срабатывает и переключает второй триггер-защёлку 7.1, который в свою очередь сбрасывает первый триггер-защёлку 4.1 в первоначальное состояние. Сигнал с выхода триггера-защёлки 4.1 уменьшает ослабление цифрового аттенюатора 8 и дальнейшее регулирование коэффициента усиления приёмного тракта осуществляет аналоговый аттенюатор 10.

В современных приёмниках уровень входного сигнала может изменяться в широких пределах: от 60 дБ в приёмниках радиосвязи и до 120 дБ в радиолокационных. Нормальная работа оконечного аппарата требует, чтобы изменения выходного сигнала приёмника не превышали 4-6 дБ. Для выполнения этих требований глубина регулировки коэффициента передачи приёмного тракта системой АРУ должна составлять 56-116 дБ [7, стр. 32].

Уровень сигнала на входе приёмника может изменяться в зависимости от расстояния до передатчика корреспондента или в зависимости от интенсивности осадков на трассе, что особенно существенно для линий связи, работающих в диапазонах СВЧ и КВЧ.

Поскольку аналоговый аттенюатор в устройстве-прототипе обеспечивает диапазон регулирования не более 30 – 35 дБ (см., например, аттенюаторы MA4VAT2000-1277T ф. M/A-COM, SVA-2000 ф. Mini-Circuits), в тракт приёма для увеличения диапазона регулирования вводится второй цифровой аттенюатор, который будет дополнительно увеличивать диапазон регулирования на 31 дБ (см., например, аттенюаторы MAATCC0009 ф. M/A-COM, CHT4012-ODG ф. UMS). Суммарное ослабление двух аттенюаторов, а, следовательно, и диапазон регулирования составит 61 – 66 дБ.

Однако устройство-прототип не обеспечивает корректное функционирование в приёмо-передающей аппаратуре, работающей в полудуплексном режиме. Полудуплексный режим предусматривает работу приёмопередатчика на одной частоте приёма и передачи. Поэтому при работе приёмопередатчика на излучение, вход собственного приёмника должен быть заблокирован. Поэтому входной сигнал приёмника в этот период времени резко уменьшается по сравнению с входным сигналом при работе приёмопередатчика на приём. Уменьшение входного сигнала заставляет систему АРУ увеличивать усиление тракта приёма, в чём на самом деле необходимости нет. После того, как приёмопередатчик вновь перейдёт в режим приёма, система АРУ начнёт восстанавливать (уменьшать) коэффициент усиления, поддерживавшийся в предыдущий период приёма и который необходим для оптимальной работы приёмника. Такой переходной процесс отрицательно влияет на качество приёма информации.

Задача предлагаемого технического решения состоит в расширении функциональных возможностей за счет функционирования устройства автоматической регулировки усиления как в полудуплексном, так и в дуплексном режиме работы приёмопередатчика.

Для решения поставленной задачи в устройство автоматической регулировки усиления, содержащее последовательно соединённые цифровой аттенюатор, аналоговый аттенюатор, усилитель промежуточной частоты, выход которого соединен с входом разветвителя, один выход которого является выходом устройства, а другой выход соединен с сигнальным входом логарифмического детектора/контроллера, другой вход которого является входом опорного напряжения Uоп, последовательно соединённые усилитель постоянного тока и фильтр нижних частот, выход которого соединен со вторым входом аналогового аттенюатора; входы логарифмического детектора и цифрового аттенюатора объединены и являются входом устройства, кроме того, N идентичных блоков регистрации уровня входного сигнала, входы которых объединены, при этом выход каждого из N блоков регистрации уровня входного сигнала подключён к соответствующему входу блока управления, выход которого соединен с входом управления цифрового аттенюатора; каждый из N блоков регистрации уровня входного сигнала содержит последовательно соединенные первый компаратор и первый триггер-защёлку, выход которого является выходом блока регистрации уровня входного сигнала и соединен с управляющим входом аналогового ключа, выход которого через последовательно соединенные второй компаратор и второй триггер-защелку соединен с входом сброса первого триггера-защёлки, причем входы первого компаратора и аналогового ключа объединены и являются входом блока регистрации уровня входного сигнала, вторые входы первого и второго компараторов являются входами первого и второго опорного напряжения, согласно изобретению введены первое и второе устройства выборки-хранения (УВХ), выход логарифмического детектора соединен с входом первого УВХ, второй вход которого является управляющим, а выход соединён с объединёнными входами блоков регистрации уровня входного сигнала; выход логарифмического детектора/контроллер соединен с входом второго устройства выборки-хранения, второй вход которого является управляющим, а выход соединён с входом усилителя постоянного тока.

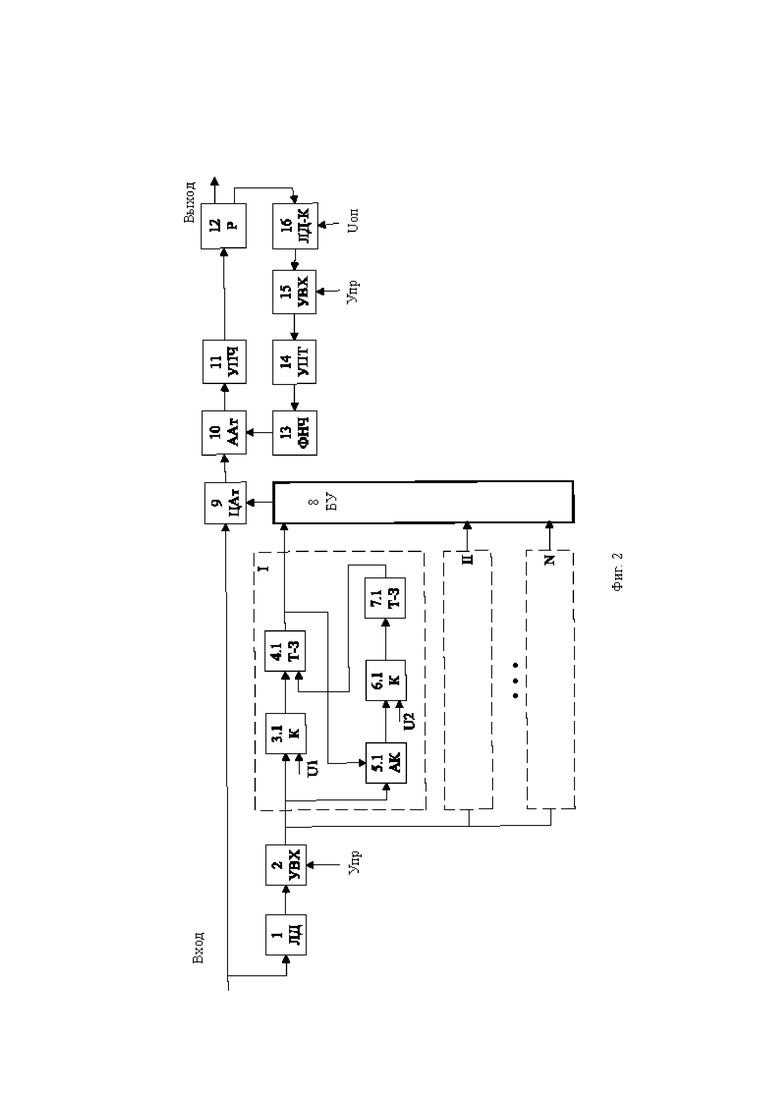

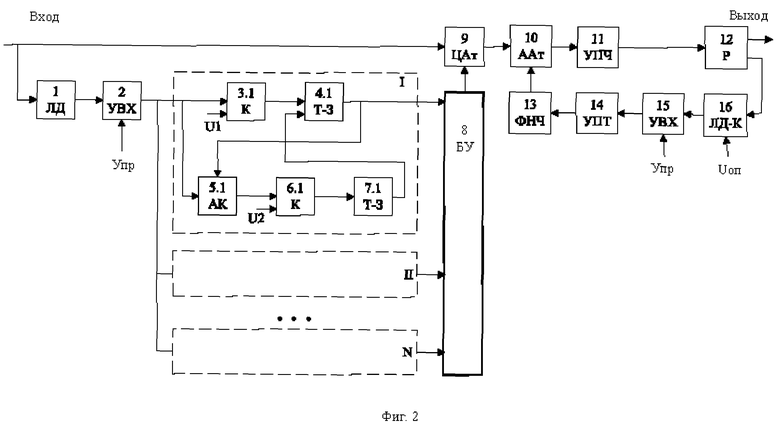

На фиг. 2 приведена функциональная схема заявляемого устройства автоматической регулировки усиления, где введены следующие обозначения:

1 – логарифмический детектор (ЛД);

2, 15 – первое и второе устройства выборки-хранения (УВХ);

I, II, N – блоки регистрации уровня входного сигнала;

3.1, 6.1 – первый и второй компараторы (К);

4.1, 7.1 – первый и второй триггеры-защёлки (Т-З);

5.1 – аналоговый ключ (АК);

8 – блок управления (БУ);

9 – цифровой аттенюатор (ЦАт);

10 – аналоговый аттенюатор (ААт);

11 – усилитель промежуточной частоты (УПЧ);

12 – разветвитель (Р);

13 – фильтр нижних частот (ФНЧ);

14 – усилитель постоянного тока (УПТ);

16 – логарифмический детектор/контроллер (ЛД-К).

Заявляемое устройство содержит последовательно соединенные цифровой аттенюатор 9, аналоговый аттенюатор 10, усилитель промежуточной частоты 11, выход которого соединен с входом разветвителя 12, один выход которого является выходом устройства, а другой выход соединен с сигнальным входом логарифмического детектора/контроллера 16, другой вход которого является входом опорного напряжения Uоп. При этом выход логарифмического детектора/контроллера 16 соединен с сигнальным входом второго устройства выборки-хранения 15, другой вход которого является управляющим входом, а его выход через последовательно соединенные усилитель постоянного тока 14 и фильтр нижних частот 13 соединен со вторым входом аналогового аттенюатора 10. Входы логарифмического детектора 1 и цифрового аттенюатора 9 объединены и являются входом устройства, а выход логарифмического детектора 1 соединен с сигнальным входом первого устройства выборки-хранения 2, другой вход которого является управляющим входом, а выход соединён с объединенными входами N идентичных блоков регистрации уровня входного сигнала I, II…N. Каждый из N блоков регистрации уровня входного сигнала содержит последовательно соединенные первый компаратор 3, первый триггер-защёлку 4, выход которого подключен к управляющему входу аналогового ключа 5, выход которого через последовательно соединенные второй компаратор 6 и второй триггер-защёлку 7 соединен с входом сброса первого триггера-защёлки 4, выход которого является выходом блока регистрации уровня входного сигнала и соединен с соответствующим входом блока управления 8, выход которого соединен со вторым входом цифрового аттенюатора 9. При этом первый вход первого компаратора 3.1 соединен с входом аналогового ключа 5.1 и является входом блока регистрации уровня входного сигнала.

Второй вход первого компаратора 3 является входом первого порогового напряжения U1. Второй вход второго компаратора 6 является входом второго порогового напряжения U2. Выходы остальных (N-1) блоков регистрации уровня входного сигнала соединены с соответствующими входами блока управления 8.

Заявляемое устройство автоматической регулировки усиления работает следующим образом.

Входной сигнал устройства через цифровой аттенюатор 9 поступает на первый вход аналогового аттенюатора 10, работающего в составе петли автоматической регулировки усиления (АРУ), состоящей из аналогового аттенюатора 10, усилителя промежуточной частоты 11, разветвителя 12, логарифмического детектора/контроллера 16, второго УВХ 15, усилителя постоянного тока 14 и фильтра нижних частот 13. Усилитель промежуточной частоты 11 обеспечивает усиление входного сигнала заявляемого устройства до минимального уровня, необходимого для нормальной работы логарифмического детектора/контроллера 16. Напряжение Uоп, подаваемое на опорный вход логарифмического детектора/контроллера 16, задаёт уровень выходного сигнала петли аналоговой АРУ, который поддерживается постоянным.

При отсутствии входного принимаемого сигнала необходимо поддерживать на входе компараторов 3.N, а также на управляющем входе аналогового аттенюатора 10 напряжение, существовавшее при наличии входного принимаемого сигнала.

По сигналу перехода приёмопередатчика в режим приёма первое 3 и второе 15 устройства выборки-хранения отслеживают уровень сигнала, поступающего на их входы, то есть транслируют его на свои выходы. По сигналу перехода приёмопередатчика в режим передачи устройства выборки-хранения 3 и 15 запоминают текущий уровень входного сигнала и сохраняют его до момента подачи сигнала перехода приёмопередатчика в режим приёма. Благодаря этому, исключается переходной процесс при функционировании приёмопередатчика в полудуплексном режиме.

При функционировании приёмопередатчика в дуплексном режиме устройства выборки-хранения 3 и 15 работают в режиме слежения.

Реализация вновь введённых устройств выборки-хранения общеизвестна и не представляет сложностей. Блок управления 8 в предлагаемом устройстве не отличается от блока управления в прототипе.

Технический результат – расширение функциональных возможностей за счет функционирования устройства автоматической регулировки усиления как в полудуплексном, так и в дуплексном режиме работы приёмопередатчика.

Источники информации.

1. Патент RU 2778438 С1 Устройство автоматической регулировки усиления. Опубликовано 18.08.2022. Бюл. № 23.

2 А.А. Макаренко, М.Ю. Плотников. Устройства приёма и преобразования сигналов. Санкт-Петербург, Редакционно-издательский отдел Университета ИТМО, 2019 г.

3. В.П. Пушкарёв. Аналоговые и цифровые радиоприёмные устройства. Томск, 2018 г.

4. Ю.В. Марков, А.С. Боков. Проектирование устройств приёма и обработки сигналов. Екатеринбург, издательство Уральского университета, 2015 г.

5. Устройства приёма и обработки сигналов. Под ред. В.С. Плаксиенко М.: Учебно-методический издательский центр «Учебная литература», 2004.

6. Патент США № 5,721,757. 1998 г. Петля автоматической регулировки усиления.

7. Н.П. Никитин, В.В. Кийко. Проектирование радиоприёмных устройств на базе аналоговых блоков. Екатеринбург: ГОУ ВПО УГТУ-УПИ, 2004.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической регулировки усиления | 2022 |

|

RU2778438C1 |

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2256937C1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Цифровое устройство формирования огибающей выходных сигналов передатчиков радиолокационных систем | 2018 |

|

RU2711507C2 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| ИЗМЕРИТЕЛЬ ОТНОСИТЕЛЬНЫХ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 2015 |

|

RU2584730C1 |

| Логарифмический аналого-цифровой преобразователь | 1981 |

|

SU955110A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| ЛИНЕАРИЗОВАННАЯ ЦИФРОВАЯ АВТОМАТИЧЕСКАЯ РЕГУЛИРОВКА УСИЛЕНИЯ | 1996 |

|

RU2158474C2 |

| Устройство для акустического каротажа | 1981 |

|

SU998991A1 |

Изобретение относится к устройствам автоматической регулировки усиления и может быть использовано в приёмных устройствах, в частности в приемных устройствах радиорелейной связи. Технический результат - расширение функциональных возможностей за счет функционирования устройства автоматической регулировки усиления как в полудуплексном, так и в дуплексном режиме работы приёмопередатчика. Такой результат обеспечивается за счет введения двух устройств выборки-хранения, вторые входы которых являются управляющими. При этом вход первого устройства выборки-хранения соединен с выходом логарифмическим детектором, а выход - с объединенными входами блоков регистрации уровня входного сигнала. Вход второго устройства выборки-хранения соединен с выходом логарифмического детектора/контроллера, а выход - с входом усилителя постоянного тока. 2 ил.

Устройство автоматической регулировки усиления, содержащее последовательно соединённые цифровой аттенюатор, аналоговый аттенюатор, усилитель промежуточной частоты, выход которого соединен с входом разветвителя, один выход которого является выходом устройства, а другой выход соединен с сигнальным входом логарифмического детектора/контроллера, другой вход которого является входом опорного напряжения Uоп, последовательно соединённые усилитель постоянного тока и фильтр нижних частот, выход которого соединен со вторым входом аналогового аттенюатора; входы логарифмического детектора и цифрового аттенюатора объединены и являются входом устройства, кроме того, N идентичных блоков регистрации уровня входного сигнала, входы которых объединены, при этом выход каждого из N блоков регистрации уровня входного сигнала подключён к соответствующему входу блока управления, выход которого соединен с входом управления цифрового аттенюатора; каждый из N блоков регистрации уровня входного сигнала содержит последовательно соединенные первый компаратор и первый триггер-защёлку, выход которого является выходом блока регистрации уровня входного сигнала и соединен с управляющим входом аналогового ключа, выход которого через последовательно соединенные второй компаратор и второй триггер-защелку соединен с входом сброса первого триггера-защёлки, причем входы первого компаратора и аналогового ключа объединены и являются входом блока регистрации уровня входного сигнала, вторые входы первого и второго компараторов являются входами первого и второго опорного напряжения, отличающееся тем, что введены первое и второе устройства выборки-хранения (УВХ), выход логарифмического детектора соединен с входом первого УВХ, второй вход которого является управляющим, а выход соединён с объединёнными входами блоков регистрации уровня входного сигнала; выход логарифмического детектора/контроллера соединен с входом второго устройства выборки-хранения, второй вход которого является управляющим, а выход соединён с входом усилителя постоянного тока.

| Устройство автоматической регулировки усиления | 2022 |

|

RU2778438C1 |

| Способ отделки обувных картонов | 1938 |

|

SU56652A1 |

| АН СССР J „T.'^i''; • •-^^^••';• ^--i^A,. .jf;:.\tC2CO!GC;ri'^^>& плг^иткз •->& | 0 |

|

SU172567A1 |

| ДОПЛЕРОВСКИЙ ИЗМЕРИТЕЛЬ СОСТАВЛЯЮЩИХ ВЕКТОРА СКОРОСТИ, ВЫСОТЫ И МЕСТНОЙ ВЕРТИКАЛИ ДЛЯ ВЕРТОЛЕТОВ И КОСМИЧЕСКИХ АППАРАТОВ ВЕРТИКАЛЬНОЙ ПОСАДКИ | 1995 |

|

RU2083998C1 |

| US 2023110275 A1, 13.04.2023 | |||

| US 11356208 B2, 07.06.2022 | |||

| US 2020389206 A1, 10.12.2020. | |||

Авторы

Даты

2024-04-11—Публикация

2023-11-01—Подача