ОБЛАСТЬ ТЕХНИКИ

[1] Настоящее раскрытие относится к области технологий интегральных схем, и в частности к схеме задержки, схеме генерирования импульсов, микросхеме и серверу.

ПРЕДПОСЫЛКИ ИЗОБРЕТЕНИЯ

[2] Схема задержки обычно используется в структуре интегральной схемы. Схема задержки может быть выполнена с возможностью осуществления задержки сигнала, устранения фазового дрожания сигнала, генерирования сигнала и т.п.

[3] Электронное устройство, например компьютер, мобильный телефон или запоминающее устройство, может содержать интегральную схему, в которую интегрированы различные компоненты или схемы. Каждая интегральная схема может быть соединена с одной или несколькими внешними схемами или устройствами и содержит узлы, выполненные с возможностью соединения с внешними схемами или устройствами через интерфейсы. Например, периферийное устройство, подобное запоминающему устройству, может быть соединено с контроллером запоминающего устройства. Как правило, скорость работы запоминающего устройства и контроллера запоминающего устройства может различаться. Поэтому в интегральной микросхеме необходима схема задержки, выполненная с возможностью регулирования времени прохождения сигнала между запоминающим устройством и контроллером запоминающего устройства.

[4] Чтобы реализовать различную обработку с задержкой сигнала в разных случаях, в одной цепи задержки может быть предусмотрено множество выходных портов сигнала, а расстояния между выходными портами и входным портом цепи задержки не совпадают. Поэтому для управления задержками при обработке с задержкой сигнала можно управлять выводом сигнала из разных выходных портов.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[5] Основной целью настоящего раскрытия является предоставление схемы задержки, схемы генерирования импульсов, микросхемы и сервера.

[6] Согласно первому аспекту в варианте осуществления настоящего раскрытия предлагается схема задержки, содержащая блок управления и по меньшей мере две подсхемы задержки. Входные концы подсхем задержки соединены друг с другом и выполнены с возможностью приема импульсного сигнала. Выходные концы подсхем задержки соединены друг с другом и выполнены с возможностью вывода задержанного импульсного сигнала. Выходной конец каждой подсхемы задержки соединен с входным концом смежной подсхемы задержки через блок переключения. Каждая подсхема задержки содержит блок задержки и блок переключения. Блок задержки выполнен с возможностью выполнения обработки с задержкой входного импульсного сигнала. Блок переключения выполнен с возможностью управления подсхемой задержки для ее подсоединения или не подсоединения. Блок управления соединен со всеми блоками переключения и выполнен с возможностью отдельного управления множеством блоков переключения для их включения или выключения, чтобы выполнять соответствующую обработку с задержкой импульсного сигнала.

[7] В некоторых вариантах реализации подсхемы задержки включают первую схему задержки и вторую схему задержки. Первая схема задержки содержит первый блок задержки и первый блок переключения. Вторая схема задержки содержит второй блок задержки и второй блок переключения. Выходной конец первого блока задержки соединен с первым концом первого блока переключения. Входной конец первого блока задержки соединен с первым концом второго блока переключения. Входной конец второго блока задержки соединен с вторым концом второго блока переключения. Выходной конец второго блока задержки соединен с вторым концом первого блока переключения. Первый конец третьего блока переключения соединен с выходным концом первого блока задержки. Второй конец третьего блока переключения соединен с входным концом второго блока задержки. Блок управления соединен с первым блоком переключения, вторым блоком переключения и третьим блоком переключения и выполнен с возможностью управления первым блоком переключения, вторым блоком переключения и третьим блоком переключения для их включения или выключения, чтобы выполнять соответствующую обработку с задержкой импульсного сигнала.

[8] В некоторых вариантах реализации управление первым блоком переключения, вторым блоком переключения и третьим блоком переключения для их включения или выключения, чтобы выполнять соответствующую обработку с задержкой импульсного сигнала, включает: отправку блоком управления соответствующего управляющего сигнала на первый блок переключения, второй блок переключения и третий блок переключения. Когда управляющий сигнал предназначен для управления первым блоком переключения и вторым блоком переключения для их выключения и управления третьим блоком переключения для его включения, первый блок задержки соединяется с вторым блоком задержки последовательно и входной импульсный сигнал последовательно проходит через первый блок задержки и второй блок задержки, вследствие чего выводится импульсный сигнал, задержанный на первое время задержки; или когда управляющий сигнал предназначен для управления первым блоком переключения и вторым блоком переключения для их включения и управления третьим блоком переключения для его выключения, первый блок задержки соединяется с вторым блоком задержки параллельно и входной импульсный сигнал одновременно проходит через первый блок задержки и второй блок задержки, вследствие чего выводится импульсный сигнал, задержанный на второе время задержки. Первое время задержки больше второго времени задержки.

[9] В некоторых вариантах реализации каждый из первого блока задержки и второго блока задержки содержит множество фазоинверторов, соединенных последовательно. Количество фазоинверторов, включенных в первый блок задержки и второй блок задержки, является одинаковым и четным.

[10] В некоторых вариантах реализации фазоинвертор содержит p-канальный МОП (металлооксидный полупроводниковый с положительными каналами) транзистор и n-канальный МОП (металлооксидный полупроводниковый с отрицательными каналами) транзистор. Исток p-канального МОП-транзистора соединен с источником питания. Затвор p-канального МОП-транзистора и затвор n-канального МОП-транзистора соединены, действуя как входной конец. Сток p-канального МОП-транзистора и сток n-канального МОП-транзистора соединены, действуя как выходной конец. Исток n-канального МОП-транзистора соединен с выводом заземления.

[11] В некоторых вариантах реализации каждый из первого блока переключения, второго блока переключения и третьего блока переключения содержит третий конец и четвертый конец. Как третий конец, так и четвертый конец соединены с блоком управления и выполнены с возможностью приема управляющего сигнала, переданного блоком управления, для управления состояниями первого блока переключения, второго блока переключения и третьего блока переключения на основании управляющего сигнала, вследствие чего схема задержки выводит импульсный сигнал, задержанный на соответствующее время задержки.

[12] Согласно второму аспекту в варианте осуществления настоящего раскрытия предлагается схема генерирования импульсов, содержащая триггер и схему задержки. Входной конец триггера соединен с источником сигнала, а выходной конец триггера соединен с входным концом схемы задержки. Триггер выполнен с возможностью вывода соответствующего импульсного сигнала на основании сигнала, отправленного источником сигнала. Схема задержки является такой, как описано в представленных выше вариантах реализации.

[13] В некоторых вариантах реализации триггер представляет собой D-триггер (триггер данных, сокращенно DFF). Входной конец для сигнала D-триггера соединен с источником сигнала. Входной конец для тактового импульса D-триггера выполнен с возможностью приема тактового импульса. Выходной конец для сигнала и конец для сигнала сброса D-триггера соединены с входным концом схемы задержки.

[14] Согласно третьему аспекту в варианте осуществления настоящего раскрытия предлагается микросхема. Микросхема интегрирована со схемой генерирования импульсов, которая описана в представленных выше вариантах реализации.

[15] Согласно четвертому аспекту в варианте осуществления настоящего раскрытия предлагается сервер, содержащий множество микросхем, которые описаны в представленных выше вариантах реализации.

[16] Входные концы подсхем задержки соединены друг с другом, и выходные концы соединены друг с другом. Выходные концы подсхем задержки соединены с входными концами смежных подсхем задержки через блоки переключения. Каждая подсхема задержки снабжена блоком переключения. Таким образом блок управления управляет включением или выключением блоков переключения для дальнейшего управления подсхемами задержки для выполнения соответствующей обработки с задержкой входного импульсного сигнала. Таким образом, можно управлять временем задержки схемы задержки. Кроме того, при обработке импульсного сигнала на основе короткой задержки подсхемы задержки подсоединяют параллельно. Таким образом, при выполнении обработки на основе короткой задержки управляющая способность схемы задержки улучшается за счет параллельного соединения между цепями задержки, так что уменьшается флуктуация процесса цепей задержки и достигается надлежащий эффект использования ресурсов.

КРАТКОЕ ОПИСАНИЕ ГРАФИЧЕСКИХ МАТЕРИАЛОВ

[17] Для более ясного описания технических решений в вариантах осуществления настоящей заявки ниже кратко описаны прилагаемые графические материалы, необходимые для описания вариантов осуществления. Очевидно, в прилагаемых графических материалах в нижеследующем описании показаны некоторые варианты осуществления настоящей заявки, и специалисты в данной области техники могут получить другие графические материалы из этих прилагаемых графических материалов без творческих усилий.

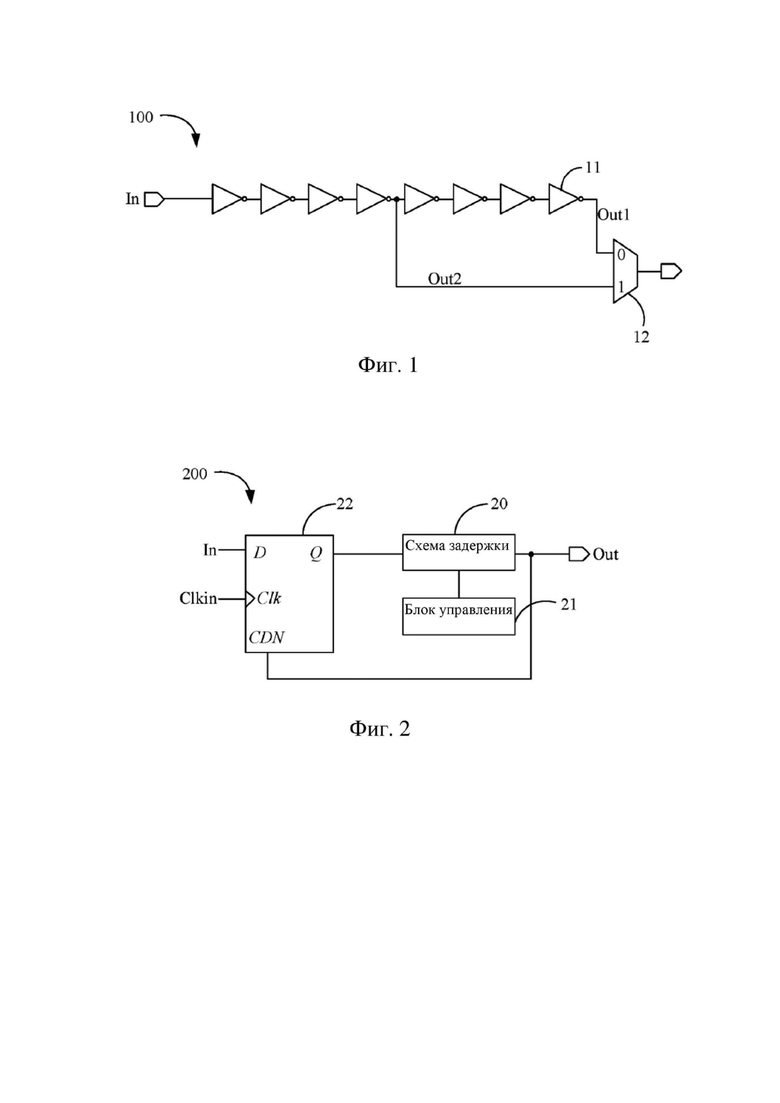

[18] На фиг. 1 представлено схематическое изображение конструкции схемы задержки согласно существующему решению.

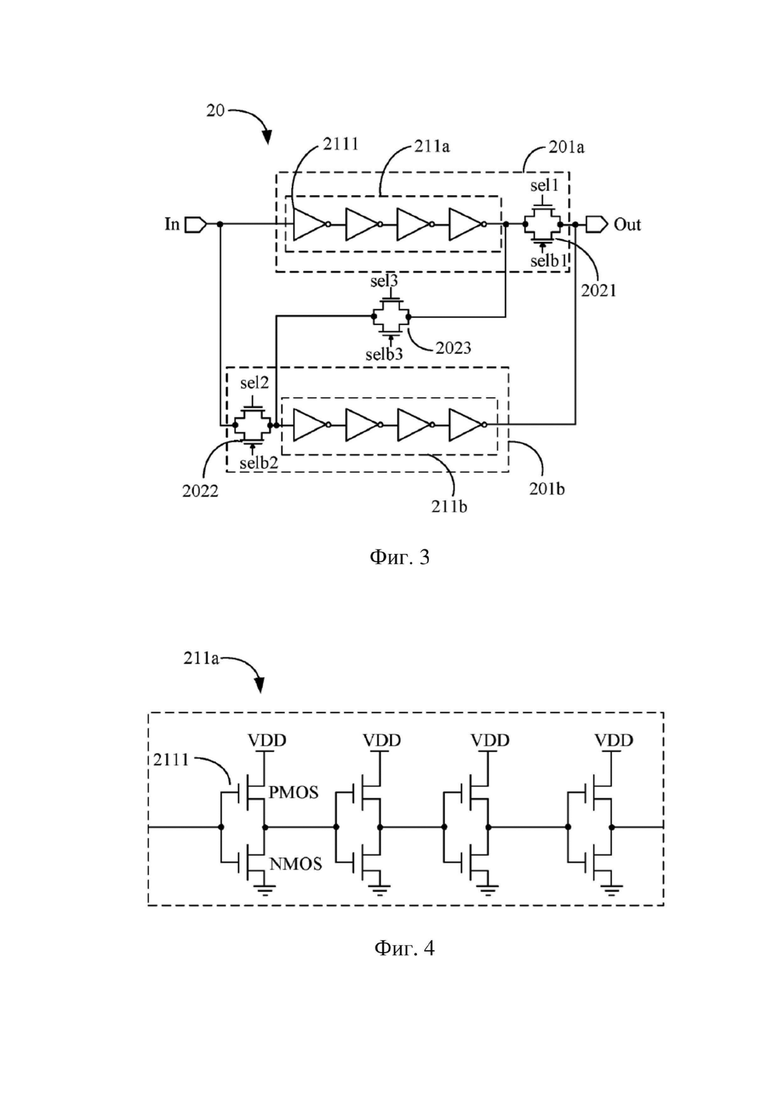

[19] на фиг. 2 представлено схематическое изображение конструкции импульсной схемы согласно одному варианту осуществления настоящего раскрытия.

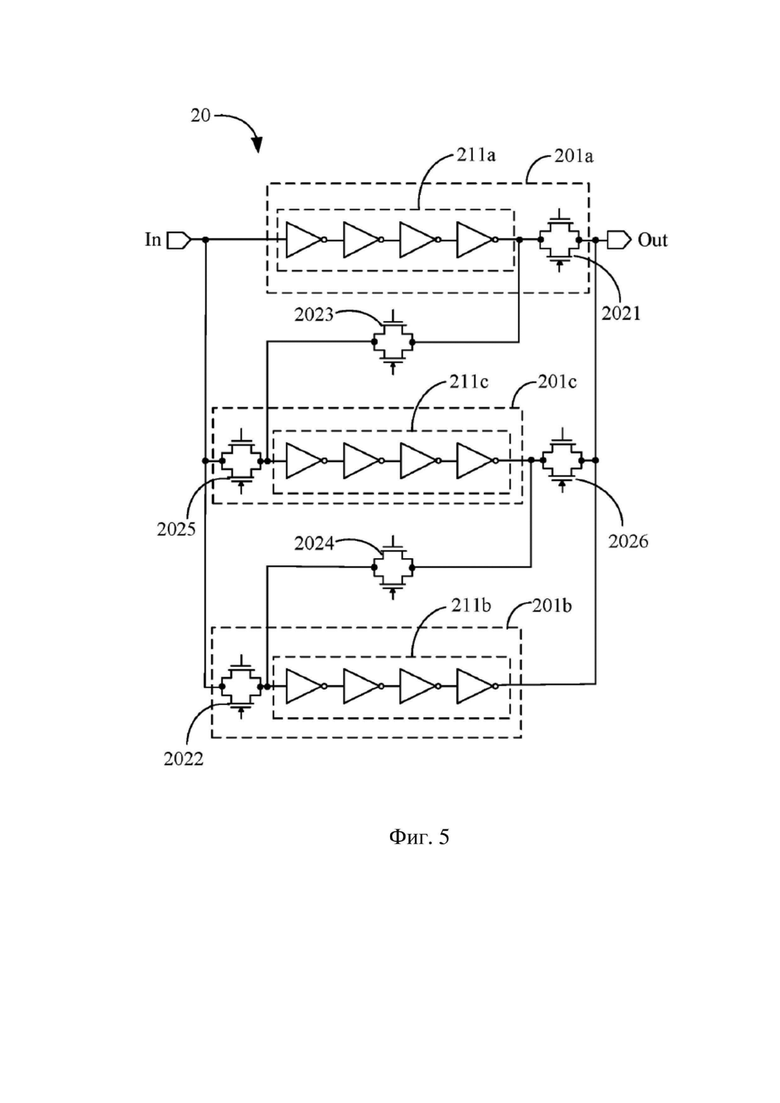

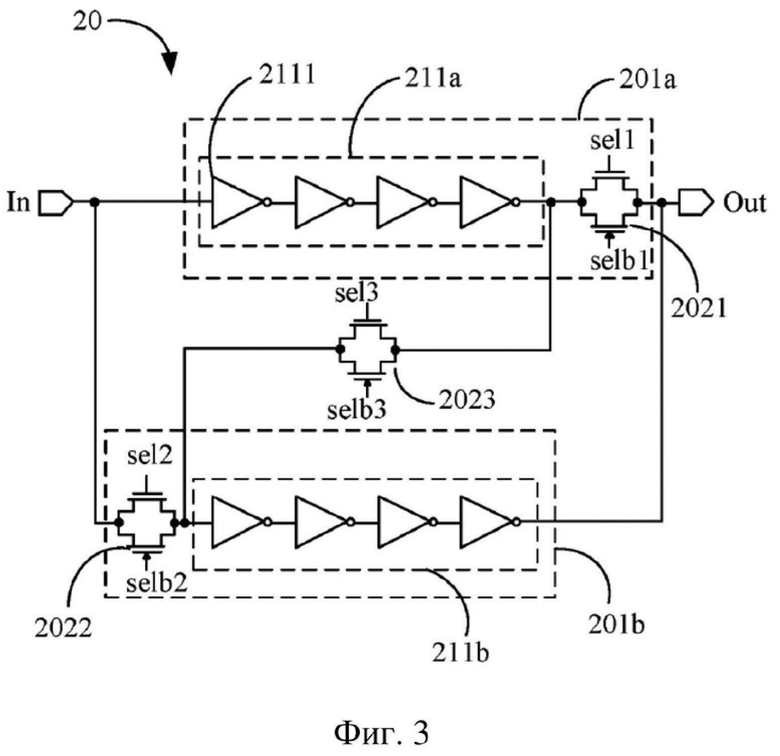

[20] на фиг. 3 представлено схематическое изображение конструкции схемы задержки согласно одному варианту осуществления настоящего раскрытия.

[21] на фиг. 4 представлено схематическое изображение конструкции первого блока задержки, показанного на фиг. 3.

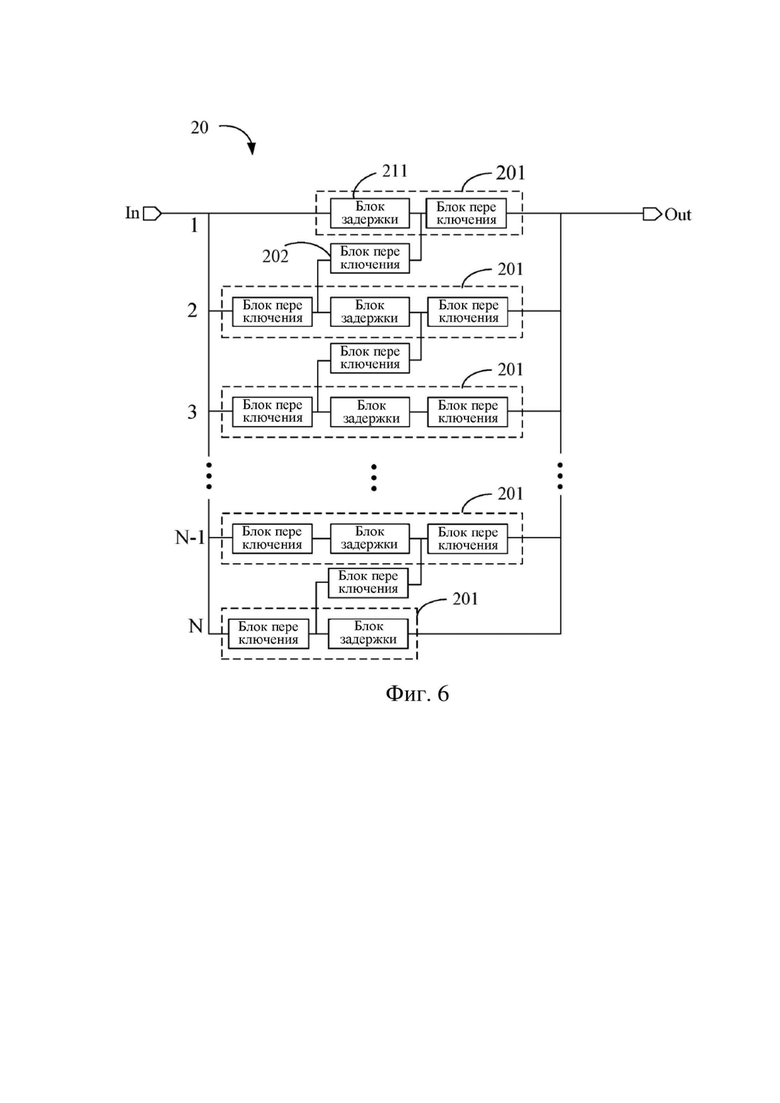

[22] на фиг. 5 представлено схематическое изображение конструкции схемы задержки согласно другому варианту осуществления настоящего раскрытия.

[23] на фиг. 6 представлено схематическое изображение конструкции схемы задержки согласно еще одному варианту осуществления настоящего раскрытия.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[24] Технические решения в вариантах осуществления настоящего раскрытия будут ясно и полно описаны ниже в сочетании с сопроводительными графическими материалами вариантов осуществления настоящего раскрытия. Очевидно, что описанные варианты осуществления представляют собой некоторые, но не все варианты осуществления настоящего раскрытия. На основе вариантов осуществления настоящего раскрытия в объем правовой охраны настоящего раскрытия попадают все другие варианты осуществления, полученные специалистами в данной области техники без приложения каких-либо изобретательских усилий.

[25] Блок-схемы, представленные на сопроводительных графических материалах, являются лишь примерами для описания, но не обязательно включают все содержание или операции/этапы, и операции/этапы не обязательно выполняются в описанном порядке. Например, некоторые операции/этапы могут быть альтернативно разделены, объединены или частично объединены, и поэтому фактический порядок выполнения может меняться в зависимости от реальной ситуации.

[26] Следует понимать, что термины, используемые в этом описании настоящего раскрытия, предназначены только для целей описания конкретных вариантов осуществления и не предназначены для ограничения настоящего раскрытия.

[27] Обратимся к фиг. 1. В связанном уровне техники цепь 100 задержки содержит несколько фазоинверторов 11, соединенных последовательно. Селектор 12 соединен с выходным концом цепи фазоинверторов. Импульсный сигнал, входящий из входного порта In, задерживается с помощью предусмотренной цепи фазоинверторов, и соответствующий импульсный сигнал выводится с помощью селектора 12. Цепь фазоинверторов снабжена несколькими выходными портами, чтобы задержку можно было регулировать.

[28] Например, как показано на фиг. 1, цепь фазоинверторов содержит восемь фазоинверторов 11, соединенных последовательно. Первый выходной порт Out1 расположен на заднем конце цепи фазоинверторов. Второй выходной порт Out2 расположен на среднем конце цепи фазоинверторов. Когда импульсным сигналом управляют для его вывода из первого выходного порта Out1, цепь фазоинверторов выполняет первую обработку с задержкой импульсного сигнала; или когда импульсным сигналом управляют для его вывода из второго выходного порта Out2, цепь фазоинверторов выполняет вторую обработку с задержкой импульсного сигнала. Очевидно, что импульсный сигнал, выходящий из первого выходного порта Out1, проходит через восемь фазоинверторов, а импульсный сигнал, выходящий из второго выходного порта Out2, проходит через четыре фазоинвертора. Поэтому первая задержка больше второй задержки.

[29] Выходные порты предусмотрены в разных положениях на цепи фазоинверторов для управления импульсным сигналом для его вывода из разных портов, чтобы выполнять разную обработку с задержкой импульсного сигнала. Однако в предыдущем случае, несмотря на возможность регулирования задержки, при реализации короткой задержки последующая избыточная часть цепи фазоинверторов не используется соответствующим образом, что приводит к излишней трате ресурсов.

[30] Поэтому для устранения вышеизложенной проблемы в настоящем раскрытии предлагаются схема задержки, схема генерирования импульсов, микросхема и сервер.

[31] Некоторые варианты осуществления настоящего раскрытия будут подробно описаны ниже со ссылкой на сопроводительные графические материалы. Следующие варианты осуществления и признаки в вариантах осуществления могут быть взаимно объединены в случае отсутствия противоречий.

[32] Обратимся к фиг. 2. В настоящем раскрытии предлагается схема 200 генерирования импульсов, содержащая триггер 22 и схему 20 задержки. Триггер 22 использует тактовый импульс Clkin в качестве управляющего сигнала и изменяет статус вывода на основании управляющего сигнала. Схема 20 задержки выполнена с возможностью выполнения обработки с задержкой сигнала, выводимого триггером 22. Схема 20 задержки соединена с блоком 21 управления и выполнена с возможностью приема управляющего сигнала, отправленного блоком 21 управления.

[33] В частности, триггер 22 представляет собой D-триггер. D-триггер содержит входной конец D для сигнала, входной конец Clk для тактового импульса, выходной конец Q для сигнала и конец CDN для сигнала сброса. Входной конец D для сигнала соединен с источником сигнала. Входной конец Clk для тактового импульса выполнен с возможностью приема тактового импульса Clkin. Выходной конец Q для сигнала соединен с входным концом схемы 20 задержки. Конец CDN для сигнала сброса соединен с выходным концом схемы 20 задержки. Когда тактовый импульс Clkin, принятый входным концом Clk для тактового импульса, находится на высоком уровне, D-триггер считывает данные входного конца D для сигнала и передает данные на выходной конец Q для сигнала; или когда тактовый импульс Clkin, принятый входным концом Clk для тактового импульса, находится на низком уровне, D-триггер удерживает данные входного конца D для сигнала и выдает текущие данные на выходной конец Q для сигнала только когда возникает следующий высокий уровень.

[34] Схема 20 задержки принимает импульсный сигнал, выведенный триггером 22, и выполняет соответствующую обработку с задержкой на основании управляющего сигнала, отправленного блоком 21 управления, чтобы выводить импульсный сигнал, полученный после обработки с задержкой.

[35] Обратимся к фиг. 2 и фиг. 3. В некоторых вариантах реализации для описания используется пример, в котором схема 20 задержки содержит две подсхемы задержки.

[36] В частности, схема 20 задержки содержит первую схему 201a задержки, вторую схему 201b задержки и блок 21 управления. Первая схема 201a задержки соединена с второй схемой 201b задержки через модуль переключения. Модуль переключения содержит первый блок 2021 переключения, второй блок 2022 переключения и третий блок 2023 переключения. Модуль переключения соединен с блоком 21 управления, чтобы принимать управляющий сигнал, отправленный блоком 21 управления, и на основании управляющего сигнала определять, следует ли включаться для обеспечения последовательной или параллельной работы первой схемы 201a задержки и второй схемы 201b задержки.

[37] Первая схема 201a задержки содержит первый блок 211a задержки и первый блок 2021 переключения. Вторая схема 201b задержки содержит второй блок 211b задержки и второй блок 2022 переключения. Выходной конец первого блока 211a задержки соединен с первым концом первого блока 2021 переключения. Входной конец первого блока 211a задержки соединен с первым концом второго блока 2022 переключения. Входной конец второго блока 211b задержки соединен с вторым концом второго блока 2022 переключения. Выходной конец второго блока 211b задержки соединен с вторым концом первого блока 2021 переключения. Первый конец третьего блока 2023 переключения соединен с выходным концом первого блока 211a задержки. Второй конец третьего блока 2023 переключения соединен с входным концом второго блока 211b задержки. Первый блок 211a задержки и второй блок 211b задержки выполнены с возможностью выполнения обработки с задержкой принятого импульсного сигнала.

[38] Входной конец первого блока 211a задержки и первый конец второго блока 2022 переключения действуют как входной конец для сигнала всей схемы для приема импульсного сигнала. Выходной конец второго блока 211b задержки и второй конец первого блока 2021 переключения действуют как выходной конец для сигнала для вывода импульсного сигнала, полученного после обработки с задержкой.

[39] Как показано на фиг. 3, в некоторых вариантах реализации каждый из первого блока 2021 переключения, второго блока 2022 переключения и третьего блока 2023 переключения содержит третий конец и четвертый конец. Как третий конец, так и четвертый конец соединены с блоком 21 управления и выполнены с возможностью приема управляющего сигнала, переданного блоком 21 управления, управления включенным/выключенным состоянием первого блока 2021 переключения на основании управляющих сигналов selb1 и sel1, управления включенным/выключенным состоянием второго блока 2022 переключения на основании управляющих сигналов selb2 и sel2 и управления включенным/выключенным состоянием третьего блока 2023 переключения на основании управляющих сигналов selb3 и sel3.

[40] Первый блок 2021 переключения, второй блок 2022 переключения и третий блок 2023 переключения имеют одинаковую конструкцию.

[41] В качестве примера первый блок 2021 переключения содержит первый n-канальный МОП-транзистор и первый p-канальный МОП-транзистор. Исток первого n-канального МОП-транзистора и исток первого p-канального МОП-транзистора соединены друг с другом, действуя как входной конец первого блока 2021 переключения. Сток первого n-канального МОП-транзистора и сток первого p-канального МОП-транзистора соединены друг с другом, действуя как выходной конец первого блока 2021 переключения. Затворы первого n-канального МОП-транзистора и первого p-канального МОП-транзистора соединены с блоком 21 управления как третий конец и четвертый конец. Второй блок 2022 переключения содержит второй n-канальный МОП-транзистор и второй p-канальный МОП-транзистор. Исток второго n-канального МОП-транзистора и исток второго p-канального МОП-транзистора соединены друг с другом, действуя как входной конец второго блока 2022 переключения. Сток второго n-канального МОП-транзистора и сток второго p-канального МОП-транзистора соединены друг с другом, действуя как выходной конец второго блока 2022 переключения. Затворы второго n-канального МОП-транзистора и второго p-канального МОП-транзистора соединены с блоком 21 управления как третий конец и четвертый конец. Третий блок 2023 переключения содержит третий n-канальный МОП-транзистор и третий p-канальный МОП-транзистор. Исток третьего n-канального МОП-транзистора и исток третьего p-канального МОП-транзистора соединены друг с другом, действуя как входной конец третьего блока 2023 переключения. Сток третьего n-канального МОП-транзистора и сток третьего p-канального МОП-транзистора соединены друг с другом, действуя как выходной конец третьего блока 2023 переключения. Затворы третьего n-канального МОП-транзистора и третьего p-канального МОП-транзистора соединены с блоком 21 управления как третий конец и четвертый конец.

[42] Управляющие сигналы, отправленные блоком 21 управления на первый блок 2021 переключения, второй блок 2022 переключения и третий блок 2023 переключения представляют собой сигналы напряжения. Определяют, достигают ли напряжения сигналов напряжения пороговых напряжений блоков переключения, и таким образом осуществляют управление блоками переключения для их включения или не включения.

[43] В качестве примера для описания используется первый блок 2021 переключения. Напряжение сигнала напряжения, входящего в первый блок 2021 переключения, задается изменяющимся в пределах диапазона от -a В до +a В. Когда входное напряжение на затворе первого n-канального МОП-транзистора представляет собой низкое напряжение -a В, то есть sel1=-a В, входное напряжение на затворе первого p-канального МОП-транзистора является высоким напряжением +a В, то есть selb1=+a В. Таким образом, как первый n-канальный МОП-транзистор, так и первый p-канальный МОП-транзистор выключены, то есть первый блок 2021 переключения выключен. Когда входное напряжение на затворе первого n-канального МОП-транзистора представляет собой высокое напряжение +a В, то есть sel1=+a В, входное напряжение на затворе первого p-канального МОП-транзистора является низким напряжением -a В, то есть selb1=-a В. Таким образом, первый n-канальный МОП-транзистор и первый p-канальный МОП-транзистор включены, то есть первый блок 2021 переключения включен.

[44] В некоторых вариантах реализации каждый из первого блока 211a задержки и второго блока 211b задержки содержит множество фазоинверторов 2111, соединенных последовательно. Множество фазоинверторов 2111, соединенных последовательно, образуют две цепи задержки. Можно понять, что длина цепи задержки может быть задана на основании конкретного сценария применения, и это не ограничивается в настоящем документе.

[45] В некоторых вариантах реализации количество фазоинверторов, включенных в первый блок 211a задержки и второй блок 211b задержки, является четным и одинаковым.

[46] Обратимся к фиг. 4. В частности, для описания используется пример, в котором цепь задержки первого блока 211a задержки содержит четыре фазоинвертора, соединенных последовательно. Фазоинвертор 2111 содержит p-канальный МОП-транзистор и n-канальный МОП-транзистор. Исток p-канального МОП-транзистора соединен с источником питания VDD. Затвор p-канального МОП-транзистора и затвор n-канального МОП-транзистора соединены, действуя как входной конец. Сток p-канального МОП-транзистора и сток n-канального МОП-транзистора соединены, действуя как выходной конец. Исток n-канального МОП-транзистора соединен с выводом заземления.

[47] В целом, p-канальный МОП-транзистор используется как нагрузочный транзистор, а n-канальный МОП-транзистор используется как входной транзистор. Такая конфигурация позволяет значительно снизить энергопотребление, поскольку в двух логических состояниях 0 и 1 один из двух транзисторов остается выключенным. Пороговое напряжение p-канального МОП-транзистора составляет VGS(th)P < 0. Пороговое напряжение n-канального МОП-транзистора составляет VGS(th)N > 0. Обычно выдвигается такое требование, чтобы VDD > |VGS(th)P| + VGS(th)N, для обеспечения нормальной работы. VDD представляет собой напряжение питания. Если на входе низкий уровень (например, 0 В), p-канальный МОП-транзистор включен, n-канальный МОП-транзистор выключен, и выходное напряжение приближается к VDD; или если на входе высокий уровень (например, VDD), n-канальный МОП-транзистор включен, p-канальный МОП-транзистор выключен, и выходное напряжение приближается к 0 В.

[48] Фазоинверторы 2111, соединенные последовательно, образуют две цепи задержки, чтобы выполнять обработку с задержкой импульсных сигналов, поступающих в первый блок 211a задержки и второй блок 211b задержки. Количество фазоинверторов 2111, соответственно включенных в первый блок 211a задержки и второй блок 211b задержки, является четным, чтобы гарантировать, что входной импульсный сигнал является таким же, как выходной импульсный сигнал. Кроме того, при обработке импульсного сигнала на основании короткой задержки, две цепи задержки, содержащие одинаковое количество фазоинверторов 2111, соединены параллельно. Таким образом, при выполнении обработки на основе короткой задержки управляющая способность схемы задержки улучшается за счет параллельного соединения между цепями задержки, так что уменьшается флуктуация процесса цепей задержки и достигается надлежащий эффект использования ресурсов.

[49] Флуктуация процесса - это отклонение процесса интегральной схемы, вызванное тем, что в процессе изготовления схемы невозможно точно контролировать технологический параметр устройства, что влияет на точность управления задержкой в схеме задержки. Таким образом, в соответствии со схемой задержки, представленной в настоящем раскрытии, уменьшается флуктуация процесса схемы задержки и повышается точность управления задержкой схемы задержки.

[50] Принцип работы схемы задержки будет подробно описан ниже со ссылкой на предыдущие описания схемы генерирования импульсов, описанной в этом варианте осуществления настоящего раскрытия, и схемы задержки, описанной в этом варианте осуществления. Для простоты описания используется пример, в котором каждый из первого блока 211a задержки и второго блока 211b задержки содержит четыре фазоинвертора, соединенных последовательно.

[51] Когда D-триггер принимает тактовый импульс высокого уровня, данные с входного конца для сигнала передаются на схему задержки как импульсный сигнал, так что схема задержки затем принимает импульсный сигнал.

[52] Когда схеме задержки необходимо выполнить первую обработку с задержкой импульсного сигнала, блок 21 управления отправляет сигнал о выключении на первый блок 2021 переключения и второй блок 2022 переключения, чтобы выключить первый блок 2021 переключения и второй блок 2022 переключения, и отправляет сигнал о включении на третий блок 2023 переключения, чтобы включить третий блок 2023 переключения. В этом случае первый блок 211a задержки и второй блок 211b задержки соединены последовательно. Таким образом, импульсный сигнал, входящий в схему задержки, вводится с входного конца первого блока 211a задержки и выводится из выходного конца первого блока 211a задержки после того, как первый блок 211a задержки выполнит обработку с задержкой импульсного сигнала. Затем импульсный сигнал вводится во входной конец второго блока 211b задержки через третий блок 2023 переключения и выводится из выходного конца второго блока 211b задержки после того, как второй блок 211b задержки выполнит обработку с задержкой импульсного сигнала. Таким образом обработка с задержкой импульсного сигнала завершается. Время задержки импульсного сигнала в каждом из первого блока 211a задержки и второго блока 211b задержки составляет a секунд. Таким образом, общее время задержки импульсного сигнала при первой обработке с задержкой, выполняемой схемой задержки, составляет 2a секунд.

[53] Когда схеме задержки необходимо выполнить вторую обработку с задержкой импульсного сигнала, блок 21 управления отправляет сигнал о включении на первый блок 2021 переключения и второй блок 2022 переключения, чтобы включить первый блок 2021 переключения и второй блок 2022 переключения, и отправляет сигнал о выключении на третий блок 2023 переключения, чтобы выключить третий блок 2023 переключения. В этом случае первый блок 211a задержки и второй блок 211b задержки соединены параллельно. Таким образом, импульсный сигнал, вводимый в схему задержки, вводится с входного конца первого блока 211a задержки и первого конца второго блока 2022 переключения и выводится из второго конца первого блока 2021 переключения и выходного конца второго блока 211b задержки после того, как первый блок 211a задержки и второй блок 211b задержки одновременно выполнят обработку с задержкой импульсного сигнала. Время задержки импульсного сигнала в каждом из первого блока 211a задержки и второго блока 211b задержки составляет a секунд. Таким образом, общее время задержки импульсного сигнала при второй обработке с задержкой, выполняемой схемой задержки, составляет a секунд.

[54] Блок 21 управления управляет включенным/выключенным состоянием каждого блока переключения для дополнительного управления связью с параллельным соединением или последовательным соединением между блоками задержки, чтобы обеспечить возможность регулирования задержки входного импульсного сигнала. Кроме того, когда входной импульсный сигнал обрабатывается на основании короткой задержки, параллельное соединение двух цепей задержки улучшает управляющую способность схемы задержки, то есть уменьшает влияние флуктуации процесса. Более того, надлежащее использование предотвращает излишнюю трату ресурсов, когда требуется короткая задержка.

[55] Обратимся к фиг. 2 и фиг. 5. В некоторых вариантах реализации для описания используется пример, в котором схема 20 задержки содержит три подсхемы задержки.

[56] В частности, схема 20 задержки содержит первую схему 201a задержки, вторую схему 201b задержки, третью схему 201c задержки и блок 21 управления. Первая схема 201a задержки, вторая схема 201b задержки и третья схема 201c задержки соединены друг с другом через модуль переключения. Модуль переключения содержит первый блок 2021 переключения, второй блок 2022 переключения, третий блок 2023 переключения, четвертый блок 2024 переключения, пятый блок 2025 переключения и шестой блок 2026 переключения. Модуль переключения соединен с блоком 21 управления, чтобы принимать управляющий сигнал, отправленный блоком 21 управления, и на основании управляющего сигнала определять, следует ли включаться для обеспечения последовательной или параллельной работы первой схемы 201a задержки, второй схемы 201b задержки и третьей схемы 201c задержки.

[57] Первая схема 201a задержки содержит первый блок 211a задержки и первый блок 2021 переключения. Вторая схема 201b задержки содержит второй блок 211b задержки и второй блок 2022 переключения. Третья схема 201c задержки содержит третий блок 211c задержки, пятый блок 2025 переключения и шестой блок 2026 переключения. Выходной конец первого блока 211a задержки соединен с первым концом первого блока 2021 переключения. Входной конец первого блока 211a задержки соединен с первым концом пятого блока 2025 переключения и первым концом второго блока 2022 переключения. Входной конец третьего блока 211c задержки соединен с вторым концом пятого блока 2025 переключения. Выходной конец третьего блока 211c задержки соединен с первым концом шестого блока 2026 переключения. Второй конец шестого блока 2026 переключения и выходной конец второго блока 211b задержки соединены с вторым концом первого блока 2021 переключения. Входной конец второго блока 211b задержки соединен с вторым концом второго блока 2022 переключения. Первый конец третьего блока 2023 переключения соединен с выходным концом первого блока 211a задержки. Второй конец третьего блока 2023 переключения соединен с входным концом третьего блока 211c задержки. Первый конец четвертого блока 2024 переключения соединен с выходным концом третьего блока 211c задержки. Второй конец четвертого блока 2024 переключения соединен с входным концом второго блока 211b задержки.

[58] Входной конец первого блока 211a задержки, первый конец пятого блока 2025 переключения и первый конец второго блока 2022 переключения действуют как входной конец для сигнала всей схемы для приема импульсного сигнала. Выходной конец второго блока 211b задержки, второй конец первого блока 2021 переключения и второй конец шестого блока 2026 переключения действуют как выходной конец для сигнала для вывода импульсного сигнала, полученного после обработки с задержкой. Первый блок 211a задержки, третий блок 211c задержки и второй блок 211b задержки выполнены с возможностью выполнения обработки с задержкой принятого импульсного сигнала.

[59] Принцип работы схемы задержки будет подробно описан ниже со ссылкой на предыдущие описания схемы генерирования импульсов, описанной в этом варианте осуществления настоящего раскрытия, и схемы 20 задержки, описанной в этом варианте осуществления. Для простоты описания используется пример, в котором каждый из первого блока 211a задержки, второго блока 211b задержки и третьего блока 211c задержки содержит четыре фазоинвертора, соединенных последовательно.

[60] Когда D-триггер принимает тактовый импульс высокого уровня, данные с входного конца для сигнала передаются на схему 20 задержки как импульсный сигнал, так что схема 20 задержки затем принимает импульсный сигнал.

[61] Когда схеме 20 задержки необходимо выполнить первую обработку с задержкой импульсного сигнала, блок 21 управления отправляет сигнал о выключении на первый блок 2021 переключения, пятый блок 2025 переключения, шестой блок 2026 переключения и второй блок 2022 переключения, чтобы выключить первый блок 2021 переключения, пятый блок 2025 переключения, шестой блок 2026 переключения и второй блок 2022 переключения, и отправляет сигнал о включении на третий блок 2023 переключения и четвертый блок 2024 переключения, чтобы включить третий блок 2023 переключения и четвертый блок 2024 переключения. В этом случае первый блок 211a задержки, третий блок 211c задержки и второй блок 211b задержки соединены последовательно. Таким образом, импульсный сигнал, входящий в схему задержки, вводится с входного конца первого блока 211a задержки и выводится из выходного конца первого блока 211a задержки после того, как первый блок 211a задержки выполнит обработку с задержкой импульсного сигнала. Затем импульсный сигнал вводится во входной конец третьего блока 211c задержки через третий блок 2023 переключения и далее выводится из выходного конца третьего блока 211c задержки после того, как третий блок 211c задержки выполнит обработку с задержкой импульсного сигнала. Наконец, импульсный сигнал вводится во входной конец второго блока 211b задержки через четвертый блок 2024 переключения и далее выводится из выходного конца второго блока 211b задержки после того, как второй блок 211b задержки выполнит обработку с задержкой импульсного сигнала. Таким образом обработка с задержкой импульсного сигнала завершается. Время задержки импульсного сигнала в каждом из первого блока 211a задержки, третьего блока 211c задержки и второго блока 211b задержки составляет a секунд. Таким образом, общее время задержки импульсного сигнала при первой обработке с задержкой, выполняемой схемой 20 задержки, составляет 3a секунд.

[62] Когда схеме 20 задержки необходимо выполнить вторую обработку с задержкой импульсного сигнала, блок 21 управления отправляет сигнал о выключении на первый блок 2021 переключения, пятый блок 2025 переключения, второй блок 2022 переключения и четвертый блок 2024 переключения, чтобы выключить первый блок 2021 переключения, пятый блок 2025 переключения, второй блок 2022 переключения и четвертый блок 2024 переключения, и отправляет сигнал о включении на шестой блок 2026 переключения и третий блок 2023 переключения, чтобы включить шестой блок 2026 переключения и третий блок 2023 переключения. В этом случае первый блок 211a задержки и третий блок 211c задержки соединены последовательно, а второй блок 211b задержки выключен. Таким образом, импульсный сигнал, входящий в схему 20 задержки, вводится с входного конца первого блока 211a задержки и выводится из выходного конца первого блока 211a задержки после того, как первый блок 211a задержки выполнит обработку с задержкой импульсного сигнала. Затем импульсный сигнал вводится во входной конец третьего блока 211c задержки через третий блок 2023 переключения и далее выводится из выходного конца второго блока 211c задержки после того, как третий блок 211c задержки выполнит обработку с задержкой импульсного сигнала. Таким образом обработка с задержкой импульсного сигнала завершается. Время задержки импульсного сигнала в каждом из первого блока 211a задержки и третьего блока 211c задержки составляет a секунд. Таким образом, общее время задержки импульсного сигнала при второй обработке с задержкой, выполняемой схемой 20 задержки, составляет 2a секунд.

[63] Альтернативно блок 21 управления может управлять первым блоком 2021 переключения, вторым блоком 2022 переключения, третьим блоком 2023 переключения и шестым блоком 2026 переключения для их выключения, и управлять пятым блоком 2025 переключения и четвертым блоком 2024 переключения для их включения, так что входной импульсный сигнал последовательно проходит через третий блок 211c задержки и второй блок 211b задержки. Таким образом, общее время задержки импульсного сигнала также может составлять 2a секунд. Таким образом, можно понять, что блок 21 управления управляет состоянием каждого блока переключения для изменения пути передачи импульсного сигнала в схеме задержки, чтобы обеспечить возможность регулирования задержки импульсного сигнала.

[64] Когда схеме 20 задержки необходимо выполнить третью обработку с задержкой импульсного сигнала, блок 21 управления отправляет сигнал о включении на первый блок 2021 переключения, пятый блок 2025 переключения, шестой блок 2026 переключения и второй блок 2022 переключения, чтобы включить первый блок 2021 переключения, пятый блок 2025 переключения, шестой блок 2026 переключения и второй блок 2022 переключения, и отправляет сигнал о выключении на третий блок 2023 переключения и четвертый блок 2024 переключения, чтобы выключить третий блок 2023 переключения и четвертый блок 2024 переключения. В этом случае первый блок 211a задержки, третий блок 211c задержки и второй блок 211b задержки соединены параллельно. Таким образом, импульсный сигнал, вводимый в схему задержки, вводится с входного конца первого блока 211a задержки, первого конца пятого блока 2025 переключения и первого конца второго блока 2022 переключения и выводится из второго конца первого блока 2021 переключения, второго конца шестого блока 2026 переключения и выходного конца второго блока 211b задержки после того, как первый блок 211a задержки, третий блок 211c задержки и второй блок 211b задержки одновременно выполнят обработку с задержкой импульсного сигнала. Таким образом обработка с задержкой импульсного сигнала завершается. Время задержки импульсного сигнала в каждом из первого блока 211a задержки, третьего блока 211c задержки и второго блока 211b задержки составляет a секунд. Таким образом, общее время задержки импульсного сигнала при третьей обработке с задержкой, выполняемой схемой 20 задержки, составляет a секунд.

[65] Блок 21 управления управляет включенным/выключенным состоянием каждого блока переключения для дополнительного управления связью с параллельным соединением или последовательным соединением между блоками задержки, чтобы обеспечить возможность регулирования задержки входного импульсного сигнала. Кроме того, когда входной импульсный сигнал обрабатывают на основании короткой задержки, параллельное соединение цепей задержки улучшает управляющую способность схемы задержки, то есть уменьшает влияние флуктуации процесса. Более того, надлежащее использование предотвращает излишнюю трату ресурсов, когда требуется короткая задержка.

[66] Обратимся к фиг. 2 и фиг. 6. В некоторых вариантах реализации для описания используется пример, в котором схема 20 задержки содержит N подсхем задержки. N является целым положительным числом, большим или равным 4.

[67] В частности, схема 20 задержки содержит блок 21 управления и N подсхем 201 задержки. Подсхема 201 задержки выполнена с возможностью выполнения обработки с задержкой входного импульсного сигнала. Блок 21 управления выполнен с возможностью управления соединительной связью между подсхемами 201 задержки.

[68] В некоторых вариантах реализации каждая подсхема 201 задержки содержит по меньшей мере один блок 211 задержки и по меньшей мере один блок переключения. Блок 211 задержки выполнен с возможностью выполнения обработки с задержкой входного импульсного сигнала. Блок переключения выполнен с возможностью управления подсхемой 201 задержки так, чтобы подсоединять или не подсоединять ее.

[69] Две смежные подсхемы 201 задержки соединяются через модуль переключения. Модуль переключения соединен с блоком 21 управления, так что модуль переключения управляется блоком 21 управления для включения или выключения, чтобы обеспечивать последовательную или параллельную работу подсхем 201 задержки.

[70] В качестве примера, как показано на фиг. 6, модуль переключения содержит N блоков 202 переключения. Каждая подсхема 201 задержки снабжена блоком 211 задержки. Блок 211 задержки соединен с по меньшей мере одним из входного конца для сигнала или выходного конца для сигнала через блок 202 переключения модуля переключения. Блоки 211 задержки смежных подсхем 201 задержки соединены через блок 202 переключения. Входной конец первой подсхемы 201 задержки соединен с входным концом для сигнала. Выходной конец N-й подсхемы 201 задержки соединен с выходным концом для сигнала.

[71] Когда смежным подсхемам 201 задержки необходимо работать параллельно, блок 21 управления управляет блоком переключения между смежными подсхемами 201 задержки для его выключения и управляет блоками переключения между соответствующими подсхемами 201 задержки и входным концом для сигнала или выходным концом для сигнала для их включения.

[72] Когда смежным подсхемам 201 задержки необходимо работать последовательно, блок 21 управления управляет блоком переключения между смежными подсхемами 201 задержки для его включения и управляет блоками переключения между соответствующими подсхемами 201 задержки и входным концом для сигнала или выходным концом для сигнала для их выключения.

[73] Блок 21 управления управляет включенным/выключенным состоянием каждого блока переключения для дополнительного управления связью с параллельным соединением или последовательным соединением между блоками задержки, чтобы обеспечить возможность регулирования задержки входного импульсного сигнала. Кроме того, когда входной импульсный сигнал обрабатывают на основании короткой задержки, параллельное соединение цепей задержки улучшает управляющую способность схемы задержки, то есть уменьшает влияние флуктуации процесса. Более того, надлежащее использование предотвращает излишнюю трату ресурсов, когда требуется короткая задержка.

[74] В настоящем раскрытии дополнительное предлагается микросхема. Микросхема содержит схему генерирования импульсов, описанную в любом из представленных выше вариантов осуществления настоящего раскрытия.

[75] Таким образом, соответствующая и конкретная реализация микросхемы в данном варианте осуществления настоящего раскрытия подобна конкретной реализации схемы генерирования импульсов в вариантах осуществления настоящего раскрытия. Более подробные сведения приведены в описаниях схемы генерирования импульсов. Здесь же подробные сведения повторно не описываются.

[76] В настоящем раскрытии дополнительное предлагается сервер. Сервер выполнен с возможностью выполнения обработки данных или вычисления, например, выполнения вычисления для добычи виртуальной цифровой валюты. Сервер содержит плату подключения, плату управления, теплоотвод, плату питания и одну или несколько хэш-плат. Каждая хэш-плата содержит одну или несколько микросхем. Плата управления соединена с хэш-платой через плату подключения. Теплоотвод расположен вокруг хэш-платы. Плата питания выполнена с возможностью подачи питания на плату подключения, плату управления, теплоотвод и хэш-плату.

[77] Следует понимать, что термин «и/или», используемый в данном описании и прилагаемой формуле настоящего раскрытия, указывает любую комбинацию и все возможные комбинации одного или нескольких элементов, перечисленных в ассоциации, и включает их комбинации. Следует отметить, что термин «содержать», «включать» или любой другой их вариант в настоящем документе предназначен для неисключительного включения, так что процесс, способ, изделие или система, содержащие ряд элементов, содержат не только эти элементы, но и другие элементы, не перечисленные явно, или элементы, присущие такому процессу, способу, изделию или системе. В отсутствие дополнительных ограничений элемент, определенный как «содержащий …», не исключает другой такой же элемент в процессе, способе, изделии или системе, содержащих этот элемент.

[78] Порядковые номера представленных выше вариантов осуществления настоящего раскрытия приведены только для описания и не означают более высокого или низкого качества вариантов осуществления. Приведенные выше описания представляют собой просто конкретные варианты осуществления настоящего раскрытия, но не предназначены для ограничения объема правовой охраны настоящего раскрытия. Любая эквивалентная модификация или замена, легко определяемая специалистами в данной области техники в пределах технического объема, раскрытого в настоящем раскрытии, входит в объем правовой охраны настоящего раскрытия. Следовательно, объем правовой охраны настоящего раскрытия определяется объемом правовой охраны формулы изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| МАЛОШУМЯЩИЙ УСИЛИТЕЛЬ И ВСПОМОГАТЕЛЬНАЯ МОНОЛИТНАЯ ИНТЕГРАЛЬНАЯ СХЕМА ДЛЯ ЭТОГО УСИЛИТЕЛЯ | 2006 |

|

RU2435292C2 |

| Схема импульсного преобразователя | 2017 |

|

RU2730176C2 |

| ПЕРЕКЛЮЧАЮЩАЯ СХЕМА | 2016 |

|

RU2645729C1 |

| СХЕМА ПОДАЧИ НАПРЯЖЕНИЯ | 2018 |

|

RU2765106C2 |

| Способ одноциклического управления коррекцией коэффициента мощности | 2023 |

|

RU2808147C1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ | 1991 |

|

RU2010361C1 |

| СХЕМА УПРАВЛЕНИЯ ДЛЯ ЭНЕРГОНЕЗАВИСИМОГО ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1998 |

|

RU2221286C2 |

| ЭЛЕКТРОННАЯ СХЕМА ДЛЯ МНОЖЕСТВА ИНДУКЦИОННЫХ ЭЛЕМЕНТОВ В ГЕНЕРИРУЮЩЕМ АЭРОЗОЛЬ УСТРОЙСТВЕ | 2018 |

|

RU2741651C1 |

| СХЕМА ПИТАНИЯ И УСТРОЙСТВО, СОДЕРЖАЩЕЕ СХЕМУ ПИТАНИЯ | 2007 |

|

RU2427954C2 |

| СПОСОБ И СИСТЕМА ОТБОРА ИОНОВ ДЛЯ МАСС-СПЕКТРОМЕТРА, ИМПУЛЬСНАЯ СХЕМА ВЫСОКОГО НАПРЯЖЕНИЯ И СХЕМА СЕЛЕКЦИИ | 2022 |

|

RU2840338C2 |

Изобретение относится к области технологий интегральных схем. Технический результат заключается в реализации регулирования и управления временем задержки схемы задержки, уменьшая флуктуацию процесса цепей задержки когда импульсный сигнал подвергается обработке с короткой задержкой. Схема задержки содержит блок управления и по меньшей мере две подсхемы задержки. Входные концы подсхем задержки соединены друг с другом и выходные концы подсхем задержки соединены друг с другом. Выходной конец каждой подсхемы задержки соединен с входным концом смежной подсхемы задержки посредством блока переключения, причем каждая подсхема задержки содержит блок задержки, выполненный с возможностью осуществления задержки входного импульсного сигнала, и блок переключения, выполненный с возможностью управления включением подсхемы задержки, и блок управления соединен со всеми блоками переключения и выполнен с возможностью соответственного управления множеством блоков переключения для их включения или выключения, чтобы выполнять соответствующую обработку с задержкой импульсного сигнала. 4 н. и 6 з.п. ф-лы, 6 ил.

1. Схема (20) задержки, выполненная с возможностью выполнения обработки с задержкой входного импульсного сигнала и содержащая:

блок (21) управления и по меньшей мере две подсхемы (201a, 201b, 201c) задержки, причем

входные концы подсхем (201a, 201b, 201c) задержки соединены друг с другом и выполнены с возможностью приема импульсного сигнала; выходные концы подсхем (201a, 201b, 201c) задержки соединены друг с другом и выполнены с возможностью вывода задержанного импульсного сигнала; выходной конец каждой из подсхем (201a, 201b, 201c) задержки соединен с входным концом смежной подсхемы задержки через блок переключения;

каждая подсхема задержки содержит блок задержки и блок переключения, причем блок задержки выполнен с возможностью выполнения обработки с задержкой входного импульсного сигнала, а блок переключения выполнен с возможностью управления подсхемой задержки для ее подсоединения или не подсоединения; и

блок (21) управления соединен со всеми блоками переключения и выполнен с возможностью отдельного управления множеством блоков переключения для их включения или выключения, чтобы выполнять соответствующую обработку с задержкой импульсного сигнала.

2. Схема (20) задержки по п. 1, отличающаяся тем, что подсхемы (201a, 201b, 201c) задержки содержат первую схему (201a) задержки и вторую схему (201b) задержки, причем первая схема (201a) задержки содержит первый блок (211a) задержки и первый блок (2021) переключения, а вторая схема (201b) задержки содержит второй блок (211b) задержки и второй блок (2022) переключения;

выходной конец первого блока (211a) задержки соединен с первым концом первого блока (2021) переключения, входной конец первого блока (211a) задержки соединен с первым концом второго блока (2022) переключения, входной конец второго блока (211b) задержки соединен со вторым концом второго блока (2022) переключения и выходной конец второго блока (211b) задержки соединен со вторым концом первого блока (2021) переключения;

первый конец третьего блока (2023) переключения соединен с выходным концом первого блока (211a) задержки, а второй конец третьего блока (2023) переключения соединен с входным концом второго блока (211b) задержки; и

блок (21) управления соединен с первым блоком (2021) переключения, вторым блоком (2022) переключения и третьим блоком (2023) переключения и выполнен с возможностью управления первым блоком (2021) переключения, вторым блоком (2022) переключения и третьим блоком (2023) переключения для их включения или выключения, чтобы выполнять соответствующую обработку с задержкой импульсного сигнала.

3. Схема (20) задержки по п. 2, отличающаяся тем, что, относительно того, что блок (21) управления выполнен с возможностью управления первым блоком (2021) переключения, вторым блоком (2022) переключения и третьим блоком (2023) переключения для их включения или выключения, чтобы выполнять соответствующую обработку с задержкой импульсного сигнала, блок (21) управления дополнительно выполнен с возможностью:

отправки соответствующего управляющего сигнала на первый блок (2021) переключения, второй блок (2022) переключения и третий блок (2023) переключения; и

когда управляющий сигнал предназначен для управления первым блоком (2021) переключения и вторым (2022) блоком переключения для их выключения и управления третьим блоком (2023) переключения для его включения, первый блок (211a) задержки соединяется со вторым блоком (211b) задержки последовательно и входной импульсный сигнал последовательно проходит через первый блок (211a) задержки и второй блок (211b) задержки, вследствие чего выводится импульсный сигнал, задержанный на первое время задержки; или

когда управляющий сигнал предназначен для управления первым блоком (2021) переключения и вторым блоком (2022) переключения для их включения и управления третьим блоком (2023) переключения для его выключения, первый блок (211a) задержки соединяется со вторым блоком (211b) задержки параллельно и входной импульсный сигнал одновременно проходит через первый блок (211a) задержки и второй блок (211b) задержки, вследствие чего выводится импульсный сигнал, задержанный на второе время задержки, при этом

первое время задержки больше второго времени задержки.

4. Схема (20) задержки по п. 2, отличающаяся тем, что каждый из первого блока (211a) задержки и второго блока (211b) задержки содержит множество фазоинверторов (2111), соединенных последовательно; и

количество фазоинверторов (2111), содержащихся в первом блоке (211a) задержки и втором блоке (211b) задержки, является одинаковым и четным.

5. Схема (20) задержки по п. 4, отличающаяся тем, что фазоинвертор (2111) содержит металлооксидный полупроводниковый с положительными каналами p-канальный МОП-транзистор и металлооксидный полупроводниковый с отрицательными каналами n-канальный МОП-транзистор; исток p-канального МОП-транзистора соединен с источником питания; затвор p-канального МОП-транзистора и затвор n-канального МОП-транзистора соединены, действуя как входной конец; сток p-канального МОП-транзистора и сток n-канального МОП-транзистора соединены, действуя как выходной конец; и исток n-канального МОП-транзистора соединен с выводом заземления.

6. Схема (20) задержки по п. 2, отличающаяся тем, что каждый из первого блока (2021) переключения, второго блока (2022) переключения и третьего блока (2023) переключения содержит третий конец и четвертый конец; и как третий конец, так и четвертый конец соединены с блоком (21) управления и выполнены с возможностью приема управляющего сигнала, переданного блоком (21) управления, для управления состояниями первого блока (2021) переключения, второго блока (2022) переключения и третьего блока (2023) переключения на основании управляющего сигнала, вследствие чего схема (20) задержки выводит импульсный сигнал, задержанный на соответствующее время задержки.

7. Схема (200) генерирования импульсов, содержащая триггер (22) и схему (20) задержки, при этом

входной конец триггера (22) соединен с источником сигнала, выходной конец триггера (22) соединен с входным концом схемы (20) задержки, и триггер (22) выполнен с возможностью вывода соответствующего импульсного сигнала на основании сигнала, отправленного источником сигнала; и

схема (20) задержки представляет собой схему (20) задержки по любому из пп. 1-6.

8. Схема (200) генерирования импульсов по п. 7, отличающаяся тем, что триггер (22) представляет собой триггер данных, D-триггер, входной конец для сигнала D-триггера соединен с источником сигнала, входной конец для тактового импульса D-триггера выполнен с возможностью приема тактового импульса, а выходной конец для сигнала и конец для сигнала сброса D-триггера соединены с входным концом схемы задержки.

9. Микросхема, причем микросхема интегрирована со схемой (200) генерирования импульсов по п. 7 или 8.

10. Сервер, содержащий множество микросхем по п. 9.

| US 7629856 B2, 08.12.2009 | |||

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| CN 107592099 A, 16.01.2018 | |||

| CN 111490758 A, 04.08.2020 | |||

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 2008 |

|

RU2386208C1 |

Авторы

Даты

2024-06-24—Публикация

2022-05-12—Подача