Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств и входных регистров микропроцессорных систем.

Известен адресный формирователь [1] , содержащий входной ключ (выполненный на N- и P-канальных МОП-транзисторах), информационный D-вход которого является адресным входом A адресного формирователя, элемент памяти (выполненный на логических двухвходовых элементах И-НЕ, N- и P-канальных МОП-транзисторах обратной связи и инверторах-формирователях внутренних инверсных входного и выходного адресных сигналов), информационный вход которого соединен с выходом входного ключа, а первый и второй выходы являются соответственно прямым a и инверсным a выходами адресного формирователя, и формирователь инверсного сигнала выбора режима (в источнике приведены его входной BK и выходной BK сигналы), вход которого соединен с прямым управляющим входом E входного ключа (затвор N-канального транзистора) и является входом выбора режима адресного формирователя, а выход - с инверсным управляющим входом E входного ключа (затвор P-канального МОП-транзистора) и с управляющим входом элемента памяти (объединенные входы двухвходовых логических элементов И-НЕ).

Общими для аналога и предлагаемого технического решения являются входной ключ, информационный вход которого является адресным входом адресного формирователя, и элемент памяти, соединенный информационным входом с выходом входного ключа.

Недостатком указанного адресного формирователя является наличие открытого входного ключа в невыбранном режиме, что приводит к протеканию сквозного тока потребления через транзисторы инвертора формирователя внутреннего инверсного входного адресного сигнала, если на адресном входе A третье состояние, или динамического тока потребления, если адресный сигнал переключается на адресном входе A с частотой f, величина которого зависит от частоты переключения f. Данный режим работы адресного формирователя реализуется, когда адресный вход A подсоединен к одному или нескольким формирователям с третьим состоянием, т. е. источниками адресных сигналов служат один или несколько элементов общей системы, разделенных режимами работы во времени (например, Рафикузаман М. Микропроцессоры и проектирование микропроцессорных систем. Мир, 1988, кн. 1, с. 23, рис. 2.3, где источниками адресных сигналов для адресного формирователя памяти служат формирователи с тремя состояниями порта ввода и микропроцессора). В свою очередь наличие тока потребления в схеме вызывает временную потерю работоспособности или полный отказ за счет ужесточения режима работы отдельных элементов и возникновения нежелательных паразитных эффектов, что является прямым снижением надежности схемы адресного формирователя в целом и предъявляет повышенные требования к внешнему источнику питания и системе охлаждения.

Кроме указанного недостатка аналог имеет большее время удержания сигнала выбора режима относительно адресного сигнала за счет необходимости установления адресного сигнала на выходе формирователя внутреннего инверсного входного адресного сигнала до подачи сигнала выбора режима, переводящего адресный формирователь в выбранный режим, требует большего количества элементов для реализации необходимой функции адресного формирователя и имеет различные задержки в цепях восстановления высокого и низкого уровня напряжения на информационном входе элемента памяти (как указано в источнике).

Наиболее близким по технической сущности к изобретению является адресный формирователь [2] , содержащий входной ключ (выполненный на N- и P-канальных МОП-транзисторах), информационный D-вход которого является адресным входом A адресного формирователя, элемент памяти (выполненный на инверторе и N- и P-канальных МОП-транзисторах), информационный вход (вход инвертора) которого соединен с выходом Z-входного ключа, два установочных ключа (выполненных на P- и N-канальных МОП-транзисторах), информационные входы которых соединены с шиной питания, два управляющих ключа (выполненные на N- и P-канальных МОП-транзисторах), информационные входы которых соединены с выходом элемента памяти, два ключа регенерации и восстановления полного уровня напряжения (выполненные на P- и N-канальных МОП-транзисторах), управляющие входы которых соединен с входом элемента памяти, а информационные входы - с шиной питания, формирователь инверсного сигнала выбора режима (в источнике для упрощения описания приведены его входной BK и выходной BK сигналы), вход которого является входом выбора режима адресного формирователя и соединен с прямым управляющим входом E-входного ключа и с управляющими входами вторых установочного и управляющего ключей, а выход соединен с инверсным управляющим входом E-входного ключа и с управляющими входами первых установочного и управляющего ключей, выходной буфферный каскад инверсного адресного сигнала (выполненный в виде цепочки из двух инверторов), вход которого соединен с первым управляющим входом элемента памяти, с выходами первых ключей установочного, управляющего и регенерации и восстановления полного уровня напряжения, а выход F2 является инверсным выходом a адресного формирователя, и выходной буферный каскад прямого адресного сигнала (выполненный на инверторе), вход которого соединен с вторым управляющим входом элемента памяти и с выходами вторых ключей установочного, управляющего и регенерации и восстановления полного уровня напряжения, а выход F1 является прямым выходом a адресного формирователя.

Общими для прототипа и предлагаемого технического решения являются входной ключ, информационный вход которого является адресным входом адресного формирователя, элемент памяти, соединенный информационным входом с выходом входного ключа, и два установочных ключа, соединенных информационными входами с шиной питания.

Недостатком прототипа является наличие открытого входного ключа в невыбранном режиме, что приводит к протеканию сквозного тока потребления через транзисторы инвертора элемента памяти, если на адресном входе A третье состояние, или динамического тока потребления, если адресный сигнал переключается на адресном входе A с частотой f, величина которого зависит от частоты переключения f. Данный режим работы адресного формирователя реализуется, когда адресный вход A подсоединен к одному или нескольким формирователям с третьим состоянием, т. е. источниками адресных сигналов служат один или несколько элементов общей системы, разделенных режимами работы во времени (например, Рафикузаман М. Микропроцессоры и проектирование микропроцессорных систем. Мир, 1988, с. 23, рис. 2.3, где источниками адресных сигналов для адресного формирователя памяти служат формирователи с тремя состояниями порта ввода и микропроцессора). В свою очередь наличие тока потребления в схеме вызывает временную потерю работоспособности или полный отказ за счет ужесточения режима работы отдельных элементов и возникновения нежелательных паразитных эффектов, что является прямым снижением надежности схемы адресного формирователя в целом и предъявляет повышенные требования к внешнему источнику питания и системе охлаждения.

Кроме указанного недостатка прототип имеет большее время удержания сигнала выбора режима относительно адресного сигнала за счет необходимости установления адресного сигнала на выходе элемента памяти до подачи сигнала выбора режима, переводящего адресный формирователь в выбранный режим, и требует большего количества элементов для реализации необходимой функции адресного формирователя.

Поэтому задача создания адресных формирователей, имеющих более высокую надежность и простую реализацию, остается актуальной на сегодняшний день.

Целью изобретения является повышение надежности за счет уменьшения тока потребления в невыбранном режиме.

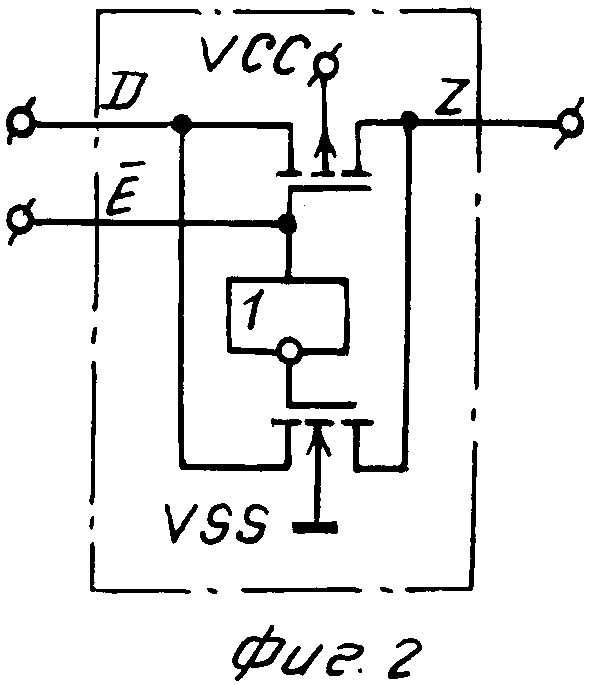

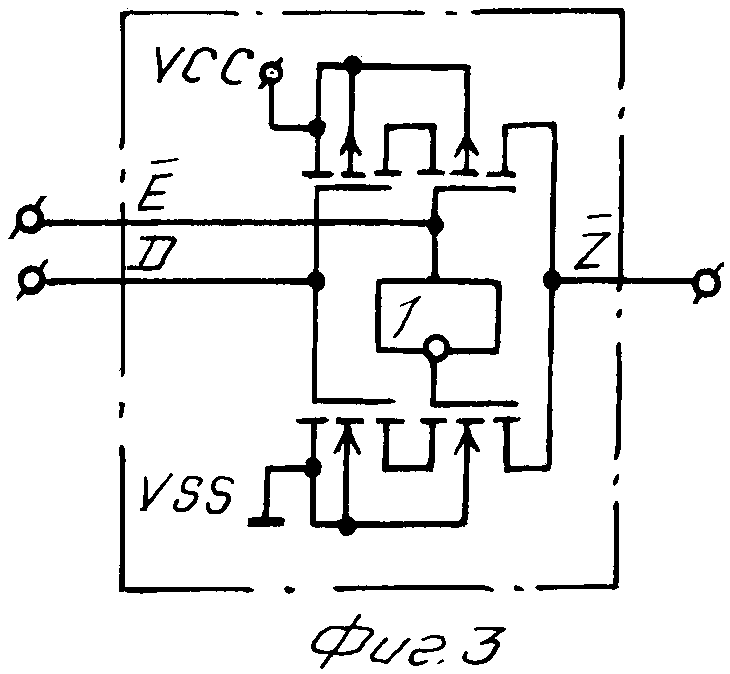

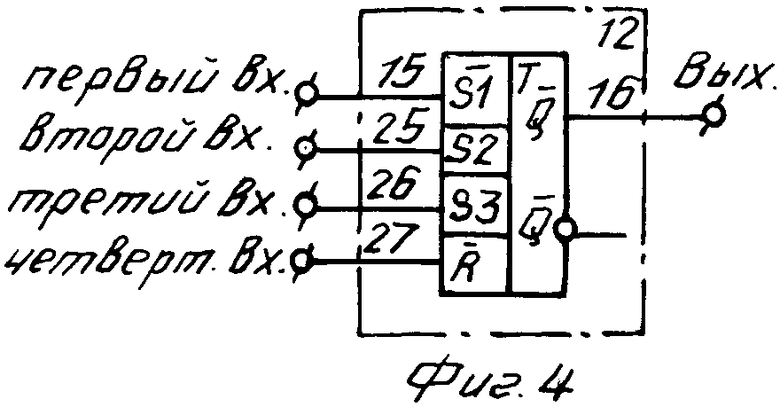

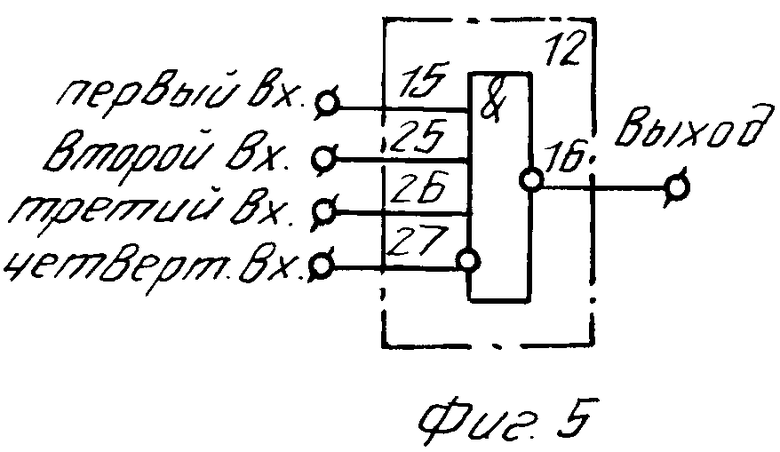

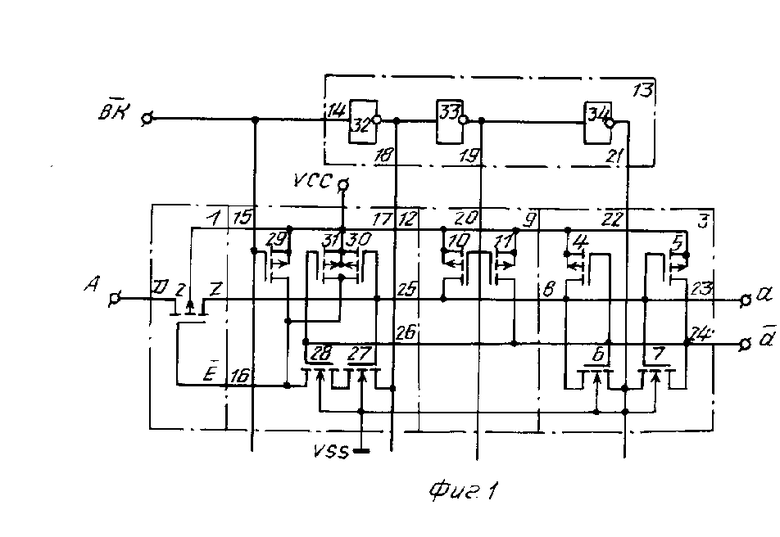

На фиг. 1 изображена схема адресного формирователя; на фиг. 2 и 3 показаны схемы входного ключа; на фиг. 4 и 5 - схемы блока управления; на фиг. 6 и 7 - схемы формирователя сигналов выбора режима.

Адресный формирователь содержит входной ключ 1, выполненный, например, как показано на фиг. 1, на P-канальном МОП-транзисторе 2 или, как показано на фиг. 2, в виде двунаправленного ключа на P-и N-канальных МОП-транзисторах со встроенным инвертором для формирования инверсного управляющего сигнала, или, как показано на фиг. 3, в виде однонаправленного ключа с инверсией входного информационного сигнала на выходе на P- и N-канальных МОП-транзисторах со встроенным инвертором для формирования инверсного управляющего сигнала, информационный D-вход которого является адресным входом А адресного формирователя, элемент 3 памяти, выполненный, например, как показано на фиг. 1, на P-канальных 4, 5 и N-канальных 6, 7 МОП-транзисторах, соединенный информационным входом 8 с выходом Z входного ключа 1, два установочных ключа 9, выполненных, например, как показано на фиг. 1, на P-канальных МОП-транзисторах 10, 11, соединенных информационными входами с шиной питания VCC, блок 12 управления и формирователь 13 сигналов выбора режима, вход 14 которого является входом выбора режима BK адресного формирователя и соединен с первым входом 15 блока 12 управления, выход 16 которого соединен с управляющим входом E входного ключа 1, а четвертый вход 17 - с первым выходом 18 формирователя 13 сигналов выбора режима, второй выход 19 которого соединен с управляющими входами 20 установочных ключей 9, третий выход 21 - с управляющим входом 22 элемента 3 памяти. Первый 23 и второй 24 выходы последнего соединены соответственно с вторым 25 и третьим 26 входами блока 12 управления, с выходами первого (выполненного на транзисторе 10) и второго (выполненного на транзисторе 11) установочных ключей 9 и являются соответственно прямым а и инверсным а выходами адресного формирователя. Блок 12 управления содержит (например, как показано на фиг. 1) первый МОП-транзистор 27 первого типа проводимости (например, как показано на фиг. 1, N-типа), исток которого является четвертым 17, а затвор - вторым 25 входами блок управления, второй МОП-транзистор 28 первого типа проводимости, исток которого соединен со стоком первого МОП-транзистора 27, а затвор и сток являются соответственно третьим входом 26 и выходом 16 блок управления, третий МОП-транзистор 29 второго типа проводимости (например, как показано на фиг. 1, Р-типа), исток которого соединен с шиной питания VCC, сток - со стоком второго МОП-транзистора 28, а затвор является первым входом 15 блока управления, четвертый МОП-транизистор 30 второго типа проводимости, исток которого соединен с шиной питания VCC, сток - со стоком второго МОП-транзистора 28, а затвор - с затвором первого МОП-транзистора 27, и пятый МОП-транзистор 31 второго типа проводимости, исток которого соединен с шиной питания VCС, сток - со стоком, а затвор - с затвором второго МОП-транзистора 28.

Известны схемы, способные в составе предлагаемого адресного формирователя выполнять функцию блока управления (фиг. 4 и 5).

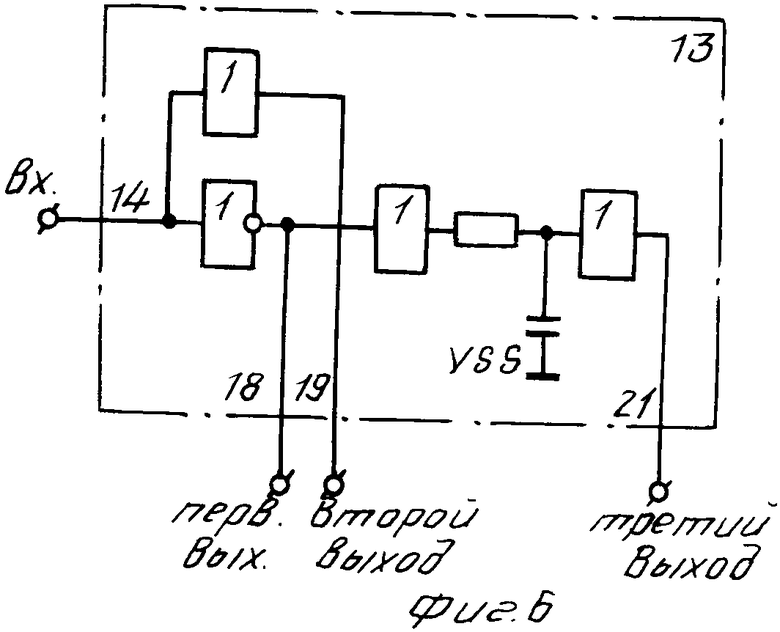

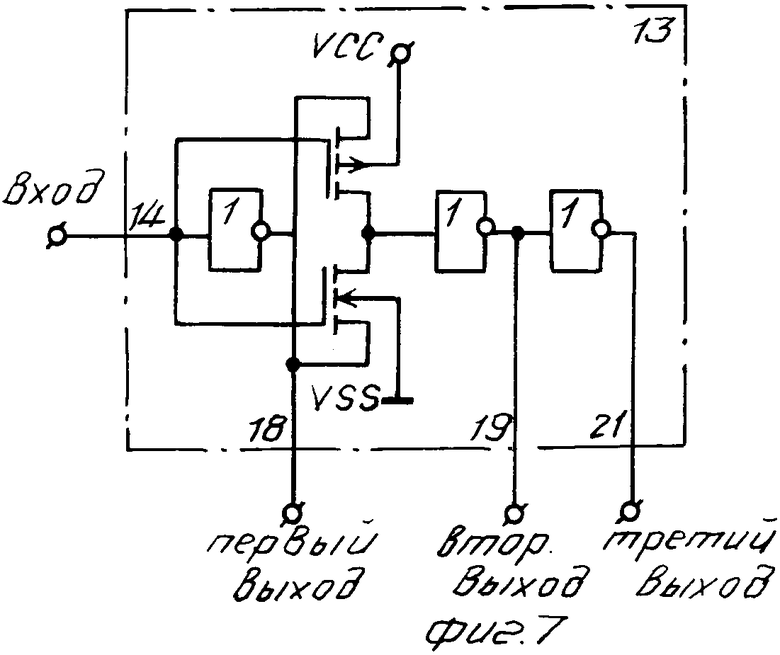

Формирователь 13 сигналов выбора режима содержит повторитель, выполненный, например, как показано на фиг. 1, в виде двух последовательно соединенных инверторов 32 и 33, вход которого является входом 14, а выход - вторым выходом 19 формирователя последовательности сигналов выбора режима, формирователь инверсного сигнала, например, как показано на фиг. 1, реализованный в виде использования функции первого инвертора 32 повторителя, вход которого соединен с входом повторителя, а выход является первым выходом 18 формирователя сигналов выбора режима, и элемент задержки, например, как показано на фиг. 1, реализованный в виде использования внутренней задержки переключения двух последовательно соединенных инверторов 33 и 34, вход которого соединен с выходом формирователя инверсного сигнала, а выход является третьим выходом 21 формирователя сигналов выбора режима.

Возможны другие примеры реализации формирователя сигналов выбора режима (фиг. 6 и 7).

Работает адресный формирователь следующим образом.

В исходном состоянии (невыбранный режим) к входу сигнала выбора режима  приложено напряжение низкого уровня. На первом 18 и третьем 21 выходах формирователя 13 сигналов выбора режима сформировано напряжение высокого уровня, а на втором выходе 19 - низкого. Транзисторы 27 . . . 29 блока 12 управления, 10, 11 установочных ключей 9 и 6, 7 элемента 3 памяти открыты, а транзисторы 30, 31 блока управления и 4, 5 элемента памяти закрыты. На выходах 16 блока управления, первом 23 и втором 24 элемента памяти и прямом а и инверсном

приложено напряжение низкого уровня. На первом 18 и третьем 21 выходах формирователя 13 сигналов выбора режима сформировано напряжение высокого уровня, а на втором выходе 19 - низкого. Транзисторы 27 . . . 29 блока 12 управления, 10, 11 установочных ключей 9 и 6, 7 элемента 3 памяти открыты, а транзисторы 30, 31 блока управления и 4, 5 элемента памяти закрыты. На выходах 16 блока управления, первом 23 и втором 24 элемента памяти и прямом а и инверсном  адресного формирователя установлено напряжение высокого уровня. Входной ключ 1 закрыт по управляющему входу

адресного формирователя установлено напряжение высокого уровня. Входной ключ 1 закрыт по управляющему входу  и внутренние узлы адресного формирователя не доступны для информации, поступающей на адресный вход A.

и внутренние узлы адресного формирователя не доступны для информации, поступающей на адресный вход A.

При переходе адресного формирователя в выбранный режим на вход выбора режима  поступает напряжение высокого уровня, которое передается на первый вход 15 блока 12 управления и на вход 14 формирователя 13 сигналов выбора режима, которым является вход инвертора 32. Напряжение высокого уровня сигнала выбора режима закрывает транзистор 29 блока управления и инвертируется на выходе инвертора 32, являющемся первым выходом 18 формирователя сигналов выбора режима, на напряжение низкого уровня. При этом выход 16 блока 12 управления отключается от шины питания VCC и на него с четвертого входа 17 через открытые транзисторы 27, 28 поступает напряжение низкого уровня первого выхода 18 формирователя сигналов выбора режима, которое открывает входной ключ 1 по управляющему входу

поступает напряжение высокого уровня, которое передается на первый вход 15 блока 12 управления и на вход 14 формирователя 13 сигналов выбора режима, которым является вход инвертора 32. Напряжение высокого уровня сигнала выбора режима закрывает транзистор 29 блока управления и инвертируется на выходе инвертора 32, являющемся первым выходом 18 формирователя сигналов выбора режима, на напряжение низкого уровня. При этом выход 16 блока 12 управления отключается от шины питания VCC и на него с четвертого входа 17 через открытые транзисторы 27, 28 поступает напряжение низкого уровня первого выхода 18 формирователя сигналов выбора режима, которое открывает входной ключ 1 по управляющему входу  для прохождения информации, имеющейся на адресном входе A, к внутренним узлам адресного формирователя.

для прохождения информации, имеющейся на адресном входе A, к внутренним узлам адресного формирователя.

С выхода инвертора 32 формирователя 13 сигналов выбора режима напряжение низкого уровня поступает на вход инвертора 33, инвертируется на его выходе, являющемся вторым выходом 19 формирователя сигналов выбора режима, на напряжение высокого уровня и поступает на вход инвертора 34 и на управляющие входы 20 установочных ключей 9 - затворы транзисторов 10, 11. При этом транзисторы 10, 11 закрываются и отключают первый 23 и второй 24 выходы элементы 3 памяти от шины питания VCC. Одновременно информации адресного сигнала, имеющаяся на адресном входе A, пройдя через открытый входной ключ 1 от D-входа к выходу Z, поступает на информационный вход 8 элемента 3 памяти.

Выходное напряжение высокого уровня инвертора 33 формирователя 13 сигналов выбора режима, поступающее на вход инвертора 34, инвертируется на его выходе, являющемся третьим выходом 21 формирователя сигналов выбора режима, на напряжение низкого уровня, поступает на управляющий вход 22 элемента 3 памяти и тем самым подключает его к источнику напряжения низкого уровня.

Если в выбранном режиме на информационный вход 8 элемента памяти поступает информация адресного сигнала в виде напряжения низкого уровня, то транзистор 7 закрывается, а транзистор 5 открывается и подключает шину питания VCC к второму выходу 24 элемента памяти 3. В то же время на первый выход 23 элемента памяти с управляющего входа 22 через открытый транзистор 6 поступает выходное напряжение низкого уровня третьего выхода формирователя 13 сигналов выбора режима, защелкивая по обратной связи элемент памяти для хранения информации адресного сигнала. Одновременно информация адресного сигнала с первого 23 и второго 24 выходов элемента 3 памяти поступает на соответствующие прямой а и инверсный  выходы адресного формирователя.

выходы адресного формирователя.

Если в выбранном режиме на информационный вход 8 элемента 3 памяти поступает информация адресного сигнала в виде напряжения высокого уровня, то транзистор 7 удерживается в открытом состоянии этим напряжением, в то время как транзистор 6 удерживается в открытом состоянии напряжением на его затворе, сохраняющимся за счет паразитной емкости узла, к которому подсоединен этот затвор. Поэтому через более открытый транзистор 7 емкость этого узла разряжается до напряжения низкого уровня, которое поступает на управляющий вход 22 элемента 3 памяти с третьего выхода 21 формирователя 13 сигналов выбора режима. При этом транзистор 6 элемента 3 памяти закрывается, а транзистор 4 открывается и элемент памяти защелкивается по обратной связи для хранения информации адресного сигнала. Одновременно информация адресного сигнала с первого 23 и второго 24 выходов элемента 3 памяти поступает на соответствующие прямой а и инверсный  выходы адресного формирователя.

выходы адресного формирователя.

Кроме того, напряжение низкого уровня на первом (или втором) выходе 23 (24) элемента 3 памяти одновременно поступает на второй 25 (третий 26) вход блока 12 управления - затворы транзисторов 27, 30 (28, 31). При этом транзистор 27 (28) закрывается и отключает выход 16 блока 12 управления от напряжения низкого уровня первого выхода 18 формирователя 13 сигналов выбора режима, а транзистор 30 (31) открывается и подсоединяет шину питания VCC к выходу 16 блока 12 управления, в результате чего входной ключ 1 закрывается по управляющему входу  и исключает возможность прохождения информации, поступающей на адресный вход А, к внутренним узлам адресного формирователя, а элемент 3 памяти хранит записанную информацию адресного сигнала до возврата адресного формирователя в исходное состояние.

и исключает возможность прохождения информации, поступающей на адресный вход А, к внутренним узлам адресного формирователя, а элемент 3 памяти хранит записанную информацию адресного сигнала до возврата адресного формирователя в исходное состояние.

При возврате адресного формирователя в исходное состояние на вход выбора режима  поступает напряжение низкого уровня, которое подается на первый вход 15 блока 12 управления и на вход 14 формирователя 13 сигналов выбора режима. При этом напряжение низкого уровня сигнала выбора режима открывает транзистор 29 блок 12 управления, подключая ее выход 16 к шине питания VCC, и инвертируется на выходе инвертора 32 формирователя сигналов выбора режима на напряжение высокого уровня, которое передается на первый выход 18 и поступает на четвертый вход 17 блока 12 управления и на вход инвертора 33 формирователя сигналов выбора режима. Выходное напряжение высокого уровня инвертора 32 формирователя 13 сигналов выбора режима инвертируется на выходе инвертора 33 на напряжение низкого уровня, которое передается на второй выход 19 и поступает на управляющие входы установочных ключей 9 - затворы транзисторов 10, 11 и вход инвертора 34 формирователя сигналов выбора режима. При этом транзисторы 10, 11 установочных ключей 9 открываются и подключают шину питания VCC к первому 23 и второму 24 выходам элемента 3 памяти. Выходное напряжение низкого уровня инвертора 33 формирователя 13 сигналов выбора режима инвертируется на выходе инвертора 34 на напряжение высокого уровня, которое передается на третий выход 21 и поступает на управляющий вход 22 элемента 3 памяти. При этом элемент памяти отключается от источника напряжения низкого уровня, которым служит третий выход 21 формирователя 13 сигналов выбора режима, и на его первый 23 и второй 24 выходы через открытые транзисторы 10, 11 установочных ключей 9 поступает напряжение шины питания VCC, в результате чего информация адресного сигналов стирается из элемента 3 памяти и на его первом 23 и втором 24 выходах и соответствующих им выходах адресного формирователя прямом а и инверсном

поступает напряжение низкого уровня, которое подается на первый вход 15 блока 12 управления и на вход 14 формирователя 13 сигналов выбора режима. При этом напряжение низкого уровня сигнала выбора режима открывает транзистор 29 блок 12 управления, подключая ее выход 16 к шине питания VCC, и инвертируется на выходе инвертора 32 формирователя сигналов выбора режима на напряжение высокого уровня, которое передается на первый выход 18 и поступает на четвертый вход 17 блока 12 управления и на вход инвертора 33 формирователя сигналов выбора режима. Выходное напряжение высокого уровня инвертора 32 формирователя 13 сигналов выбора режима инвертируется на выходе инвертора 33 на напряжение низкого уровня, которое передается на второй выход 19 и поступает на управляющие входы установочных ключей 9 - затворы транзисторов 10, 11 и вход инвертора 34 формирователя сигналов выбора режима. При этом транзисторы 10, 11 установочных ключей 9 открываются и подключают шину питания VCC к первому 23 и второму 24 выходам элемента 3 памяти. Выходное напряжение низкого уровня инвертора 33 формирователя 13 сигналов выбора режима инвертируется на выходе инвертора 34 на напряжение высокого уровня, которое передается на третий выход 21 и поступает на управляющий вход 22 элемента 3 памяти. При этом элемент памяти отключается от источника напряжения низкого уровня, которым служит третий выход 21 формирователя 13 сигналов выбора режима, и на его первый 23 и второй 24 выходы через открытые транзисторы 10, 11 установочных ключей 9 поступает напряжение шины питания VCC, в результате чего информация адресного сигналов стирается из элемента 3 памяти и на его первом 23 и втором 24 выходах и соответствующих им выходах адресного формирователя прямом а и инверсном  устанавливается напряжение высокого уровня, которое поступает на второй 25 и третий 26 входы блока 12 управления. Закрытый адресный сигналом транзистор 27 (28) блока управления открывается, а открытый транзистор 30 (31) закрывается. Однако выход 16 блока 12 управления остается подключенным к шине питания VCC через открытый транзистор 29 и входной ключ 1 остается закрытым по управляющему входу

устанавливается напряжение высокого уровня, которое поступает на второй 25 и третий 26 входы блока 12 управления. Закрытый адресный сигналом транзистор 27 (28) блока управления открывается, а открытый транзистор 30 (31) закрывается. Однако выход 16 блока 12 управления остается подключенным к шине питания VCC через открытый транзистор 29 и входной ключ 1 остается закрытым по управляющему входу  , а внутренние узлы адресного формирователя не доступны для информации, поступающей на адресный вход A.

, а внутренние узлы адресного формирователя не доступны для информации, поступающей на адресный вход A.

Таким образом, все элементы адресного формирователя находятся в таком состоянии, что все возможные цепи протекания тока потребления через активные элементы схемы разорваны, а закрытый входной ключ 1 исключает возможность изменения этого состояния информацией, поступающей на адресный вход A, до начала переходных процессов, вызванных появлением сигнала выбора режима, переводящего адресный формирователь в выбранный режим.

Предлагаемый адресный формирователь по сравнению с прототипом имеет более высокую надежность за счет исключения возможности протекания тока потребления в любом статическом режиме через активные элементы схемы при наличии любой информации на адресном входе A, ужесточающего режим работы отдельных элементов схемы адресного формирователя и тем самым приводящего к временной потере работоспособности или полному отказу схемы; представляет более низкие требования к внешнему источнику питания и системе охлаждения за счет отсутствия тока потребления в любом статическом режиме при наличии любой информации на адресном входе А; требует меньшего количества элементов для реализации необходимой функции адресного формирователя; имеет меньшее время удержания сигнала выбора режима относительно адресного сигнала, так как не требует установления адресного сигнала на выходе элемента памяти для появления сигнала выбора режима, переводящего адресный формирователь в выбранный режим.

(56) 1. Кармазинский А. М. Синтез принципиальных схем цифровых элементов на МДП-транзисторах. Радио и связь, 1983, с. 141, рис. 3.21.

2. Там же, с 142, рис. 3.22 а.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "ТОМЬ" | 1992 |

|

RU2010434C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 1990 |

|

RU2010429C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОГО ИЗМЕРЕНИЯ УРОВНЯ | 1992 |

|

RU2010175C1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КООРДИНАТ ГЕОМЕТРИЧЕСКОГО ЦЕНТРА ОБЪЕКТА | 1985 |

|

SU1380590A1 |

| ИОНИЗАЦИОННЫЙ ФИЛЬТР ДЛЯ ОЧИСТКИ ВОЗДУХА | 1992 |

|

RU2009717C1 |

| ДЕШИФРАТОР | 2005 |

|

RU2307405C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЙ КАБЕЛЬНЫХ ЛИНИЙ | 1992 |

|

RU2010253C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств и входных регистров микропроцессорных систем. Изобретение позволяет повысить надежности адресного формирователя за счет уменьшения тока потребления в невыбранном режиме. Адресный формирователь содержит входной ключ 1, информационный D-вход которого является адресным входом A адресного формирователя, блок 12 управления, соединенный своим выходом 16 с управляющим входом E входного ключа 1, элемент 2 памяти, соединенный своим информационным входом 8 с выходом Z входного ключа 1, два установочных ключа 9, соединенных информационными входами с шиной питания VCC, и формирователь 13 сигналов выбора режима, соединенный своим входом 14, который является входом выбора режима  адресного формирователя, с первым входом 15 блока 12 управления, четвертый вход 17 которого соединен с первым выходом 18 формирователя сигналов выбора режима, второй выход 19 которого соединен с управляющими входами 20 установочных ключей 9, а третий выход 21 - с управляющим входом 22 элемента 3 памяти, первый 23 и второй 24 выходы которого соединены соответственно с вторым 25 и третьим 26 входами блока 12 управления, выходами первого (10) и второго (11) установочных ключей 9 и являются соответственно прямым a и инверсным

адресного формирователя, с первым входом 15 блока 12 управления, четвертый вход 17 которого соединен с первым выходом 18 формирователя сигналов выбора режима, второй выход 19 которого соединен с управляющими входами 20 установочных ключей 9, а третий выход 21 - с управляющим входом 22 элемента 3 памяти, первый 23 и второй 24 выходы которого соединены соответственно с вторым 25 и третьим 26 входами блока 12 управления, выходами первого (10) и второго (11) установочных ключей 9 и являются соответственно прямым a и инверсным  выходами адресного формирователя. 2 з. п. ф-лы, 7 ил.

выходами адресного формирователя. 2 з. п. ф-лы, 7 ил.

Авторы

Даты

1994-03-30—Публикация

1991-09-25—Подача