Изобретение касается схемы управления для энергонезависимого полупроводникового запоминающего устройства со схемой преобразователя уровня, которая подает выходное значение и комплементарное этому выходному значению выходное значение на разрядную шину и/или числовую шину полупроводникового запоминающего устройства, и с расположенной между схемой ввода и схемой преобразователя уровня схемой блокировки (latch = схема-защелка), которая промежуточно запоминает подлежащие запоминанию в полупроводниковом запоминающем устройстве данные.

Такая схема управления известна из ЕР 0154379 А2.

Энергонезависимые полупроводниковые запоминающие устройства, такие как, например, флэш-память и электрически стираемое программируемое постоянное запоминающее устройство (EEPROM = ЭСППЗУ), необходимы для занесения или же удаления вводов и вместе с тем данных из отдельных ячеек запоминающего устройства напряжением обычно 15 В. Эти напряжения, существенно превышающие нормальное напряжение питания Vdd (Вольт цифровых данных), которое по порядку величины составляет 5 В, в дальнейшем называются также "высокими напряжениями". В зависимости от режима работы высокие напряжения подаются на числовые шины или разрядные шины или также на числовые шины и разрядные шины полупроводникового запоминающего устройства.

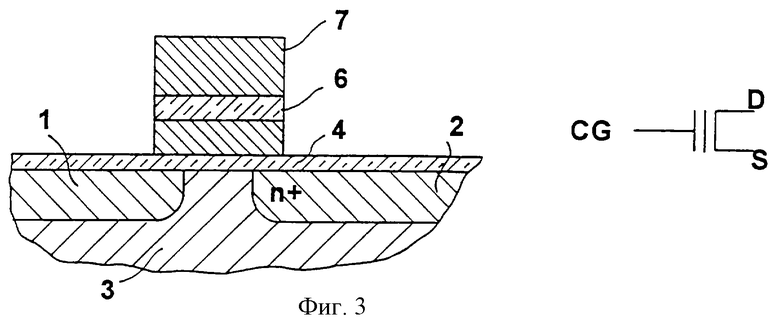

Фиг.3 схематически наглядно показывает структуру так называемой стековой затворной ячейки. Эта стековая затворная ячейка имеет зону истока 1 и зону стока 2 в полупроводниковой подложке 3. Зона истока 1 и зона стока 2 легированы обе примесью n+, в то время как полупроводниковая подложка 3 имеет легирование примесью р. Зона истока 1 и зона стока 2, а также канальная область полупроводниковой подложки 3 между зоной истока 1 и зоной стока 2 снабжены туннельным окисным слоем 4 из, например, окиси кремния. На туннельном окисном слое 4 в области между зоной стока 2 и зоной истока 1 находится плавающий затвор 5 из, например, поликристаллического кремния. На этом плавающем затворе 5 еще расположены промежуточный полидиэлектрик 6 и управляющий электрод 7.

Для стирания и программирования данных при такой стековой затворной ячейке может применяться так называемое "туннелирование Фоулера-Нордхайма" (ФН-туннелирование). При процессе стирания подаются, например, 0 В на зону стока 2 и +15 В на управляющий электрод 7. Тогда электроны из области канала через туннельный окисный слой 4 туннелируют в плавающий затвор 5. При программировании находятся, например, 0 В на управляющем электроде 7 и +15 В на зоне стока 2, что заставляет электроны совершать туннельное движение из плавающего затвора 5 через туннельный окисный слой 4 в зону стока 2. Но также можно для программирования подать, например, -11 В на управляющий электрод 7 и +4 В на зону стока 2. За счет этого также электроны побуждаются совершать туннельное движение из плавающего затвора 5 в зону стока 2.

При программировании с горячими электронами ("hot-e-программирование") подаются на управляющий электрод 7, например, +15 В, на зону стока 2 +5 В и на зону истока 1 0 В. За счет этого электроны перемещаются из зоны стока 2 к зоне истока 1 и одновременно совершают туннельное движение через туннельный окисный слой 4 в плавающий затвор 5.

EEPROM, как известно, может программироваться и стираться побайтно, в то время как флэш-память может программироваться побайтно горячими электронами или ФН-туннелированием и может стираться поблочно ФН-туннелированием.

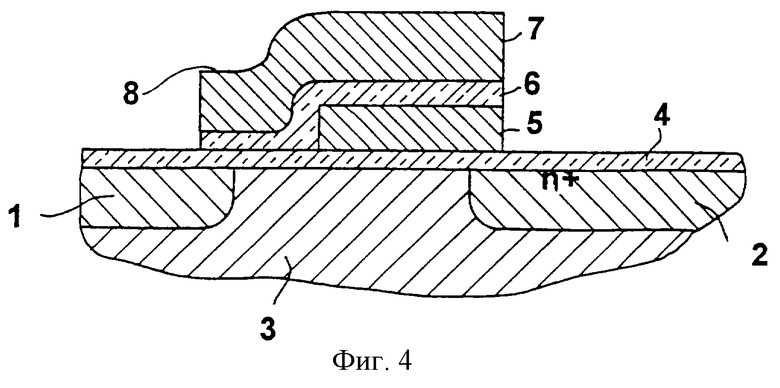

Фиг. 4 показывает в качестве другого типа ячеек памяти так называемую электрически стираемую однотранзисторную ячейку с полупроводниковой подложкой 3, легированной примесью n+ зоной источника 1, легированной примесью n+ зоной стока, туннельным окисным слоем 4, плавающим затвором 5, промежуточным полидиэлектриком 6 и управляющим электродом 7. "Пониженная" часть управляющего электрода 7 обозначается также как последовательный электрод 8, так как повышенный управляющий электрод 7 и последовательный электрод 8 могут рассматриваться как соединенные друг с другом затворы двух включенных последовательно транзисторов n-канальной МОП-структуры.

Показанная на фиг. 3 стековая ячейка воспроизводится представленным на этой фигуре справа символом, причем "CG" означает управляющий электрод 7, "D" - вывод зоны стока 2 и "S" - вывод зоны истока 1.

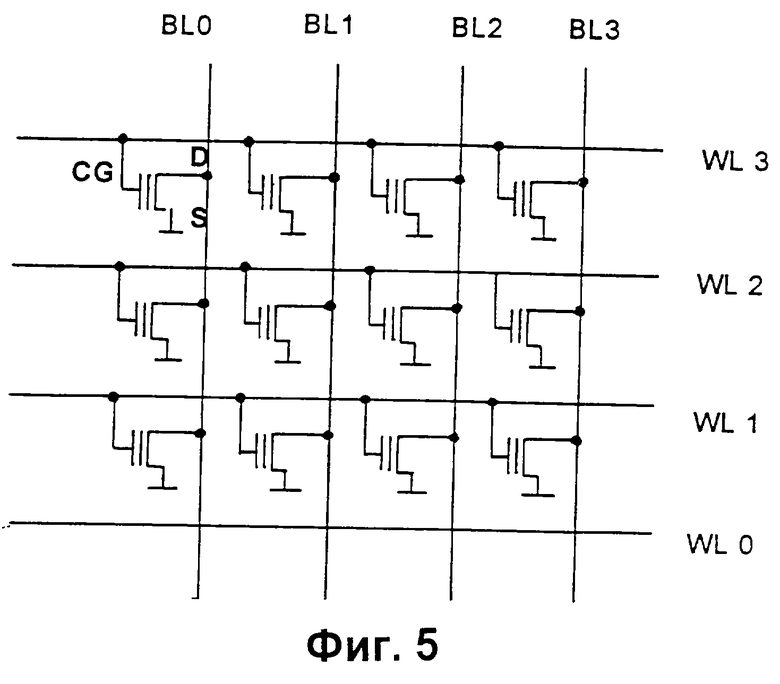

Ячейки памяти показанного на фиг.3 типа могут образовывать полупроводниковое запоминающее устройство с разрядными шинами BL0, BL1, BL2, BL3 и числовыми шинами WL0, WL1, WL2 и WL3, как это схематически показано на фиг.5.

При полупроводниковом запоминающем устройстве высокие напряжения должны подаваться селективно на выбранные числовые шины или же разрядные шины, чтобы стирать или программировать отдельные ячейки памяти. Но кроме полупроводниковых запоминающих устройств должны также коммутироваться специальные регулируемые напряжения с более высокой стабильностью, чем напряжение питания, за счет высоких напряжений, например 15В.

Важным случаем применения является, например, управление разрядными шинами при флэш-памяти с отрицательным напряжением программирования (сравните для этого, например, R. Heinrich, W. Heinrigs, G. Tempel, J. Winnerl, T. Zettler, в Proc. of the International electron device meeting (IEDM), 1993, стр. 445-448). Для достижения постоянных условий программирования здесь, например, напряжение разрядной шины регулируется на 5 В, в то время как на числовые шины подаются -12 В. Также такие регулируемые напряжения, например, 5 В, которые лежат ниже напряжения питания 5,5 В, в дальнейшем понимаются под "высоким напряжением".

Для формирования такого рода управляющих напряжений необходима управляющая схема, которая должна выдавать желаемые напряжения с высокой стабильностью и небольшой занимаемой площадью.

В частности, в US-A-5293561 описана управляющая схема со схемой делителя напряжений для отдельного питания зоны памяти и памяти для устройств переполнения с высокими напряжениями. Эта известная схема управления имеет, в частности, схему преобразователя уровня, которая позволяет подавать выходное значение и комплементарное этому выходному значению выходное значение на полупроводниковое запоминающее устройство.

Но оказалось, что известная схема управления в соответствии с US-A-5293561 мало пригодна для управления разрядными шинами, так как она не позволяет осуществлять промежуточное запоминание данных. Кроме того, известная управляющая схема содержит n-канальные МОП-транзисторы обедненного типа, которые как дополнительные конструктивные элементы обусловливают значительные технологические затраты.

Схема управления в соответствии с европейским патентом ЕР 0154379 А2, выбранным в качестве прототипа заявленного изобретения, напротив, содержит большое число р-канальных МОП транзисторов, которые имеют относительно большую занимаемую площадь и незначительную токовую отдачу.

Поэтому задачей данного изобретения является создание управляющей схемы для энергонезависимого полупроводникового запоминающего устройства, которая может быть реализована с помощью, по возможности, небольшого количества конструктивных элементов на маленькой площади, так что она может сооружаться на самом узком пространстве в координатной сетке матрицы памяти полупроводникового запоминающего устройства и управляющие напряжения могут выдаваться с высокой стабильностью также в высоковольтной области.

Поставленная задача решается тем, что в схеме управления для энергонезависимого полупроводникового запоминающего устройства со схемой преобразования уровня сигнала, напряжения с выходного вывода (D) и дополнительного выходного вывода (DN) которого подают на разрядную шину и/или числовую шину полупроводникового запоминающего устройства, с расположенной между схемой ввода и схемой преобразователя уровня сигнала схемой блокировки (схемой-защелкой), которая промежуточно запоминает подлежащие запоминанию в полупроводниковом запоминающем устройстве данные, согласно изобретению схема ввода состоит из одного, расположенного своим участком исток-сток между входом данных (DATA) и первым, соединенным с управляющим входом схемы преобразователя уровня сигнала выходом данных, первого n-канального МОП транзистора (N1) и схемы из последовательно соединенных второго и третьего n-канальных МОП транзисторов (N2, N3), расположенных между массой и вторым, соединенным с дополнительным к управляющему вводу управляющим вводом схемы преобразователя уровня сигнала, выходом данных, второго и третьего n-канальных МОП транзисторов (N2, N3), причем затвор второго n-канального МОП транзистора (N2) соединен с затвором первого n-канального МОП транзистора (N1) и затвор третьего n-канального МОП транзистора (N3) соединен с истоком или стоком первого n-канального МОП транзистора. Очевидно, что такая схема ввода может применяться также отдельно от управляющей схемы, если сигнал и инвертированный относительно него сигнал должны производиться простыми средствами.

Схема управления в соответствии с изобретением может быть реализована с небольшим количеством конструктивных элементов на небольшой площади, так что она может быть размещена на самом узком пространстве в координатной сетке матрицы памяти полупроводникового запоминающего устройства. Схема ввода построена всего лишь из трех n-канальных МОП транзисторов, так что она может быть реализована особенно просто и выгодно в смысле площади, что имеет высочайшее значение для полупроводниковых запоминающих устройств или же их координатной сетки. Так как здесь не используются р-канальные МОП-транзисторы, схема ввода может быть размещена в общей ванне, что означает дополнительную выгоду по площади. Вследствие более высокой токовой отдачи n-канальных МОП-транзисторов по сравнению с р-канальными МОП-транзисторами, к тому же, вся схема может быть выполнена особенно небольшой.

Схема блокировки в преимущественном способе может состоять из двух антипараллельно (встречно-параллельно) включенных инверторов.

Ниже изобретение подробнее объясняется с помощью чертежей.

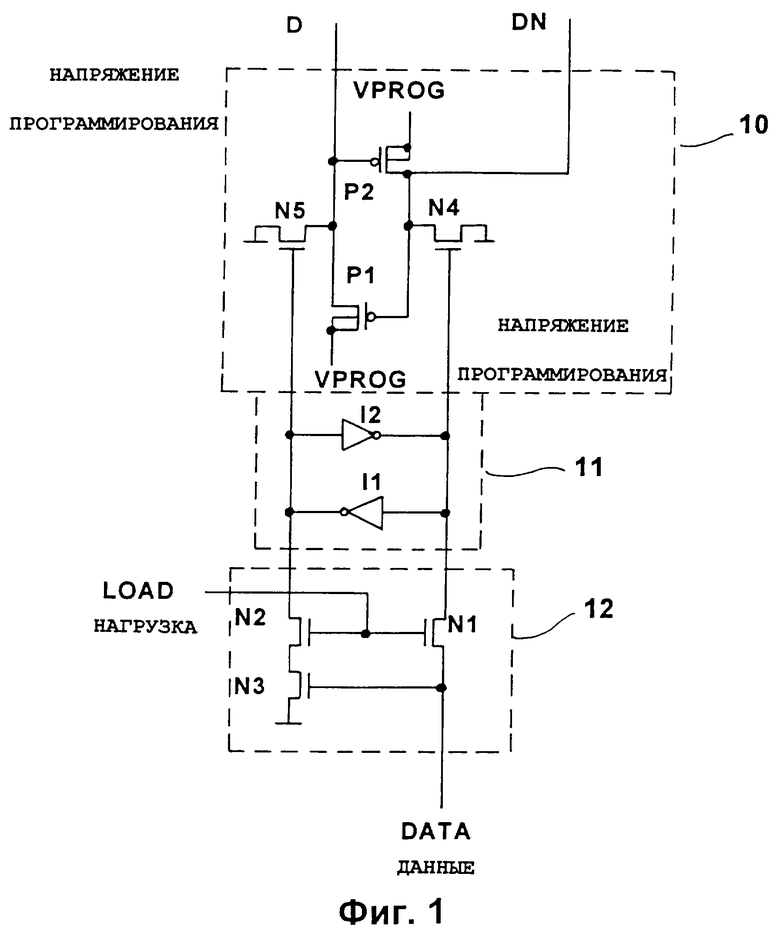

Фиг.1 - функциональная схема управляющей схемы в соответствии с изобретением.

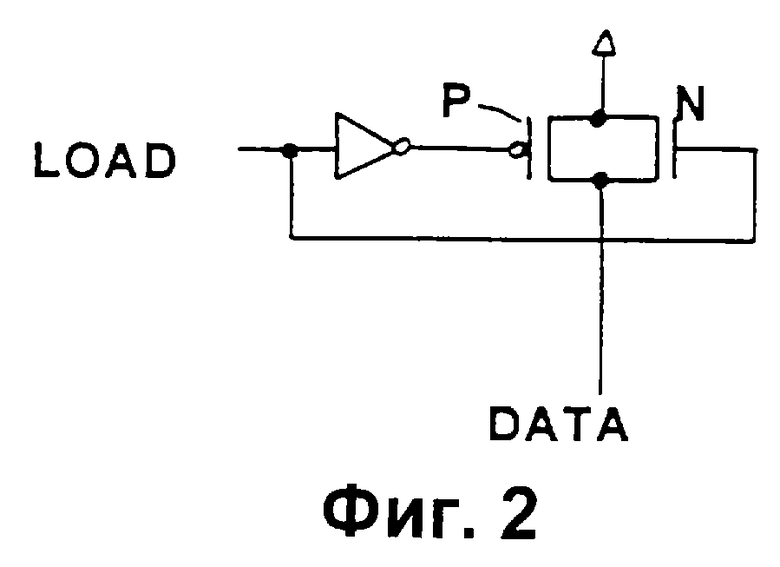

Фиг.2 - передающий КМОП-затвор.

Фиг.3 - вид в разрезе стековой затворной ячейки.

Фиг.4 - вид в разрезе стековой затворной ячейки.

Фиг.5 - матрица ячейки памяти с числовыми и разрядными шинами.

Фиг.3-5 уже были объяснены вначале.

Фиг.1 показывает компоновку схемы управления в соответствии с изобретением. Эта схема управления состоит из схемы преобразователя уровня 10, схемы блокировки (latch) 11 и схемы ввода 12. Схема преобразователя уровня 10 состоит из р-канальных МОП-транзисторов Р1, Р2 и n-канальных МОП-транзисторов N4, N5 и имеет выходные выводы D или же DN, которые соединены с разрядными шинами или же с числовыми шинами полупроводникового запоминающего устройства. Выходные шины D или же DN в зависимости от входного значения "1" или же "0", которое поступает на вход DATA (данные), выдают напряжение VPROG (напряжение программирования) или же 0 В. При этом выходной вывод DN является комплементарным выходному выводу D и выдает 0 В или же напряжение VPROG, если на выходном выводе D имеется напряжение VPROG или же 0 В.

На стоке или же истоке р-канальных МОП-транзисторов Р1 или же Р2 имеется подведенное извне напряжение VPROG, например 15 В. При помощи транзисторов N4, N5, Р1 и Р2 управляется подача этого напряжения VPROG на выходной вывод D или же DN, причем выход DN является комплементарным выходу D, как это уже объяснялось выше.

Схема преобразователя уровня, подобная схеме преобразователя уровня 10, сама по себе известна из уже названного US-A-5 293 561.

Схема преобразователя уровня 10 включена перед схемой блокировки 11, которая состоит из двух антипараллельно расположенных друг к другу инверторов 11 и 12. Перед этой схемой блокировки 11 находится схема ввода 12 из трех n-канальных МОП-транзисторов N1-N3. Подлежащие запоминанию данные, следовательно, например, 5 В для значения данных "1", через вход DATA подводятся к схеме ввода. При этом исток или же сток транзистора N1 соединен со входом DATA, что также справедливо для затвора транзистора N3, который включен последовательно с транзистором N2. Затворы транзисторов N1 и N2 соединены друг с другом и подключены к вводу LOAD (загрузка). Если на вводе LOAD имеются, например, 5 В, то транзисторы N1 и N2 проводят, так что 0 В имеется на левом на фиг.1 входе схемы блокировки 11, в то время как, например, сигнал данных "1" 5 В через транзистор N1 подводится к правому на фиг.1 входу схемы блокировки 11 (уменьшенный на запускающее напряжение транзистора N1).

Управляющая схема в соответствии с изобретением особенно хорошо подходит для данных, которые должны программироваться в энергонезависимое полупроводниковое запоминающее устройство. Эти данные промежуточно запоминаются в схеме блокировки 11 и имеется регулируемое напряжение VPROG для каждой разрядной шины. Схема управления при этом применении предусматривается раздельной для каждой разрядной шины или же числовой шины. Подлежащие программированию данные подаются на входную шину DATA. За счет положительного импульса на вводе LOAD данные затем принимаются в схему блокировки 11. На выходных выводах D и DN схема преобразователя уровня 10 тогда в зависимости от входного значения "1" или же "0" на входном вводе DATA выдает напряжение VPROG или же 0 В. Сигнал на выходном выводе DN при этом является коплементарным сигналу на выходном выводе D и выдает 0 В или же напряжение VPROG, если напряжение на выходном выводе D имеет значение VPROG или же 0 В.

Разумеется, управляющая схема в соответствии с изобретением может применяться на разрядной и/или числовой шине для общего распределения высоких напряжений.

Схема ввода 12 построена всего лишь из трех n-канальных МОП-транзисторов N1, N2 и N3. Ее, таким образом, можно реализовать особенно просто и благоприятно с точки зрения использования поверхности, что имеет высочайшее значение для растровых схем памяти. Так как не применяются р-канальные МОП транзисторы, этот схемный блок может изготавливаться в общей ванне, что означает существенный выигрыш в поверхности. Схема ввода 12 в зависимости от данных ввода переводит правые на фиг.1 узлы схемы блокировки через транзистор N1 (на входе DATA имеется "0") на 0 В или левые узлы через транзисторы N2 и N3 на 0 В.

За счет более высокой токовой отдачи n-канальных МОП-транзисторов по сравнению с р-канальными МОП-транзисторами схема ввода 12 может быть выполнена особенно небольшой. Специально сумма размеров транзисторов N2 и N3 только максимально должна быть такой величины, как размер одного р-канального МОП-транзистора с соответствующим переходным КМОП-затвором (сравни фиг. 2). Для управления схемой ввода 12 далее необходим только один сигнал LOAD. Дополнительный инвертированный сигнал, как само по себе необходимо при переходном КМОП-затворе, не должен применяться.

Схема управления в соответствии с изобретением не нуждается в дополнительном входном инверторе для управления транзисторами N4 и N5, а для этого используется функция инверторов 11 и 12 схемы блокировки. Преимущественная комбинация схемы блокировки 11 со схемой преобразователя уровня 10 экономит, таким образом, конструктивные элементы и поэтому особенно пригодна для применения в критичных к поверхности растровых схемах памяти.

Изобретение относится к схемам управления для энергонезависимого полупроводникового запоминающего устройства и может быть применено в критичных к поверхности растровых схемах памяти. Техническим результатом является возможность выдачи управляющих напряжений с высокой стабильностью даже в высоковольтной области. Устройство содержит схему преобразования уровня сигнала, схему ввода и схему блокировки. 1 з.п. ф-лы, 5 ил.

| 0 |

|

SU154379A1 | |

| RU 94006044 A1, 27.05.1996 | |||

| US 4716312 А, 29.12.1987 | |||

| НАКАПЛИВАЮЩЕЕ УСТРОЙСТВО К УСТАНОВКЕ | 0 |

|

SU208186A1 |

| US 5444396 А, 22.08.1995. | |||

Авторы

Даты

2004-01-10—Публикация

1998-06-08—Подача