ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Изобретение относится к области микроэлектроники. Более конкретно изобретение относится к конструкции модуля оперативной памяти.

УРОВЕНЬ ТЕХНИКИ

Известен модуль оперативной памяти (https://www.jedec.org/category/technology-focus-area/memory-configurations-jesd21-c , дата обращения 12.12.2023), включающий в себя узел хранения данных, выполненный с возможностью предоставления по запросу системной плате, к которой подключен модуль, служебных данных. Такие служебные данные включают в себя данные настроек модуля оперативной памяти, которые именуются также SPD данными (Serial Presence Detect) и включают в себя данные об оптимальных параметрах работы модуля оперативной памяти (например, тайминги, частота и пр.). В известном модуле служебные данные, включая данные настроек модуля оперативной памяти, хранятся на микросхеме электрически стираемого перепрограммируемого ПЗУ EEPROM (Electrically Erasable Programmable Read-Only Memory). В момент загрузки вычислительной системы системная плата обращается к подключенному к ней модулю оперативной памяти, более конкретно, контроллер оперативной памяти системной платы обращается к узлу хранения данных настроек модуля оперативной памяти с запросом о предоставлении данных настроек модуля оперативной памяти, в ответ на который модуль предоставляет соответствующие данные. Взаимодействие контроллера оперативной памяти и узла хранения данных осуществляется по протоколу JEDEC. В известном устройстве в качестве узла хранения данных используется постоянное запоминающее устройство EEPROM. Упомянутое ПЗУ EEPROM устанавливаются на модуль оперативной памяти его производителем, а служебные данные могут записываться на них только с помощью специальных программаторов при крупносерийном производстве. При этом производитель устанавливает запрет на внесение изменений в записанные служебные данные.

Данные настроек модуля оперативной памяти, в частности тайминги, представляют собой значения, рекомендуемые производителем, однако, они не являются единственно возможными для конкретного модуля оперативной памяти. Кроме того, по умолчанию содержащиеся в данных настроек модуля оперативной памяти значения параметров являются оптимальными далеко не для всех случаев применения соответствующих модулей оперативной памяти. Системным интеграторам и производителем серверов предпочтительно иметь возможность задания параметров работы модулей оперативной памяти, содержащихся в данных настроек модуля оперативной памяти, являющихся оптимальными для конкретной стоящей перед ними задачи; например, может потребоваться выбрать иные тайминги или частоту для более высокого быстродействия системы или большей стабильности её работы. При этом, изменение данных настроек модуля оперативной памяти в известном устройстве невозможно без специального программатора. Таким образом, известный модуль оперативной памяти обладает низкой гибкостью настройки параметров его работы.

Для обеспечения большей гибкости настройки параметров разработчиками настоящего решения было принято решение использовать в модуле оперативной памяти узел хранения данных, который включает в себя микроконтроллер и носитель информации, выполненный с возможностью постоянного хранения данных настроек модуля оперативной памяти. При этом микроконтроллер должен быть выполнен с возможностью считывания с носителя информации и оперативного хранения данных настроек модуля оперативной памяти, а также с возможностью передачи оперативно хранящихся данных настроек модуля оперативной памяти в ответ на запрос контроллера оперативной памяти системной платы. Кроме того, микроконтроллер должен быть выполнен с возможностью записи данных настроек модуля оперативной памяти на носитель информации по запросу контроллера оперативной памяти системной платы при условии снятой защиты от записи.

Контроллер оперативной памяти системной платы обменивается информацией с узлом хранения данных оперативной памяти по стандарту Jedec, который предполагает использование шины i2c и протокола Jedec (I2C-bus specification and user manual, опубликовано 01.10.2021).

При решении этой задачи разработчики столкнулись с проблемой недоступности микроконтроллеров, способных передавать данные по протоколу Jedec и обладающих при этом требуемыми возможностями и быстродействием. При этом наиболее подходящими оказались микроконтроллеры, выполненные с возможностью передачи данных по стандарту i2c, которые, однако, по умолчанию не совместимы со стандартом Jedec. Так возникла задача обеспечения возможности реализации вышеупомянутой архитектуры модуля оперативной памяти с использованием микроконтроллера, имеющего возможность передачи данных в соответствии по протоколу i2c, в частности, RISC-V микроконтроллера MIK32 АМУР.

Протокол i2c (https://i2c.info/i2c-bus-specification, дата обращения 16.01.2024) и протокол Jedec (https://www.jedec.org/category/technology-focus-area/memory-configurations-jesd21-c, дата обращения 16.01.2024) не в полной мере совместимы. Шина i2c содержит линию данных (SDA) и линию синхронизации (SCL). В соответствии с протоколом i2c данные передаются в 8-битных пакетах (байтах). Количество байтов не ограничено, при этом за каждым байтом должен следовать бит подтверждения (девятый бит). Девятый бит (бит подтверждения по протоколу i2c) сигнализирует о том, готово ли устройство к переходу к следующему байту. Для всех битов данных, включая бит подтверждения, ведущее устройство должно генерировать тактовые импульсы в линию синхронизации. Если ведомое устройство не подтверждает передачу, это означает, что данных больше нет или оно ещё не готово к передаче.

В соответствии с протоколом Jedec девятый бит используется для передачи данных. В частности, он может использоваться для сообщения адреса страницы, подлежащей чтению, команды управления защитой от записи или информации о состоянии защиты от записи.

Возможным решением при реализации указанной архитектуры могла бы стать программная реализация на микроконтроллере алгоритма передачи данных в соответствии с протоколом Jedec. При программной реализации микроконтроллер должен успевать реагировать на изменения состояний сигналов линии данных (SDA) и линии синхронизации (SCL), и, в случае необходимости, вовремя выдавать логический 0 на линию данных. Программа должна непосредственно управлять состоянием сигнала, направляемого в линию данных. В связи с тем, что микроконтроллер в узле хранения данных является ведомым устройством, он не может влиять на временные параметры обмена, задаваемые ведущим устройством. Ведущее устройство должно соответствовать требованиям стандарта Jedec в части временных параметров обмена (таблица 24 стр. 29 стандарта 21-C, https://www.jedec.org/category/technology-focus-area/memory-configurations-jesd21-c, дата обращения 12.01.2024). Однако, с учётом возможности и необходимости работы на разных скоростях обмена микроконтроллер должен обеспечивать относительно малое время реакции (около 0,6 мкс). Таким образом, программная реализация протокола Jedec предъявляет высокие требования к производительности микроконтроллера.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Задача, стоявшая перед разработчиками раскрытого технического решения, заключалась в создании модуля оперативной памяти с узлом хранения данных на базе микроконтроллера, имеющего возможность передачи данных через интерфейс i2c, который бы обеспечивал бы с одной стороны возможность обмена информацией с контроллером оперативной памяти системной платы по стандарту Jedec, а с другой стороны обеспечивал бы уровень быстродействия, достаточный для корректных запуска и завершения сеансов обмена данными. Иными словами, задачей, стоявшей перед разработчиками настоящего технического решения, было расширение арсенала модулей оперативной памяти.

В ходе решения указанной задачи был создан модуль оперативной памяти, включающий в себя

узел хранения данных, выполненный с возможностью предоставления по запросу системной плате, к которой подключен модуль, данных настроек модуля оперативной памяти.

При этом модуль оперативной памяти отличается тем, что узел хранения данных включает в себя

микроконтроллер, выполненный с возможностью передачи данных по протоколу i2c в качестве ведомого устройства, с возможностью в установленном состоянии модуля оперативной памяти предоставлять системной плате данные настроек модуля оперативной памяти в ответ на запрос контроллера оперативной памяти системной платы по шине i2c, а также с возможностью передачи управляющего сигнала на буферный блок;

буферный блок, соединённый последовательно с линией данных шины i2c и выполненный с возможностью под воздействием управляющего сигнала микроконтроллера переключения в любой один из следующих режимов передачи сигналов: двунаправленный или однонаправленный, причём в однонаправленном режиме буферный блок допускает приём сигналов микроконтроллером и блокирует передачу сигналов микроконтроллером по линии данных.

Технический результат, достигаемый раскрытым решением, заключается в реализации назначения модуля оперативной памяти.

Далее в настоящем описании раскрытое техническое решение будет описано более детально со ссылкой на конкретные варианты осуществления и прилагаемые фигуры чертежей.

КРАТКОЕ ОПИСАНИЕ ПРИЛАГАЕМЫХ ФИГУР ЧЕРТЕЖЕЙ

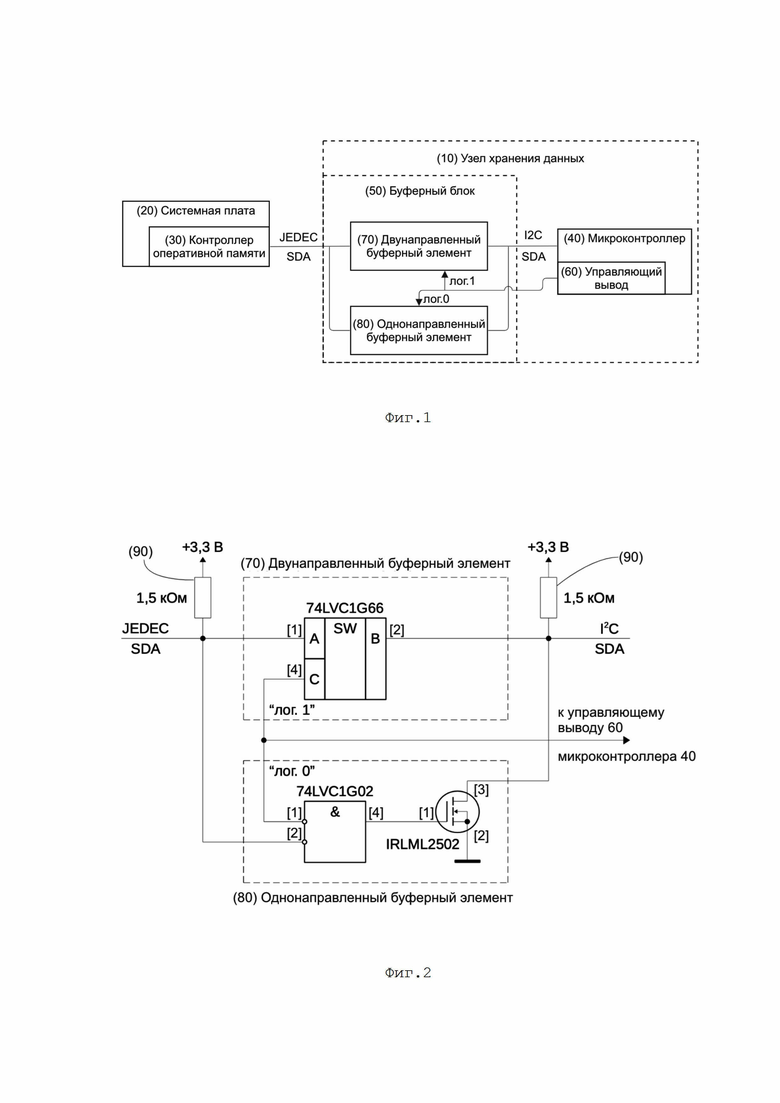

Фиг.1 – функциональная схема подключения микроконтроллера к системной плате. Цифрами в круглых скобках обозначены позиции устройств, участвующих в подключении.

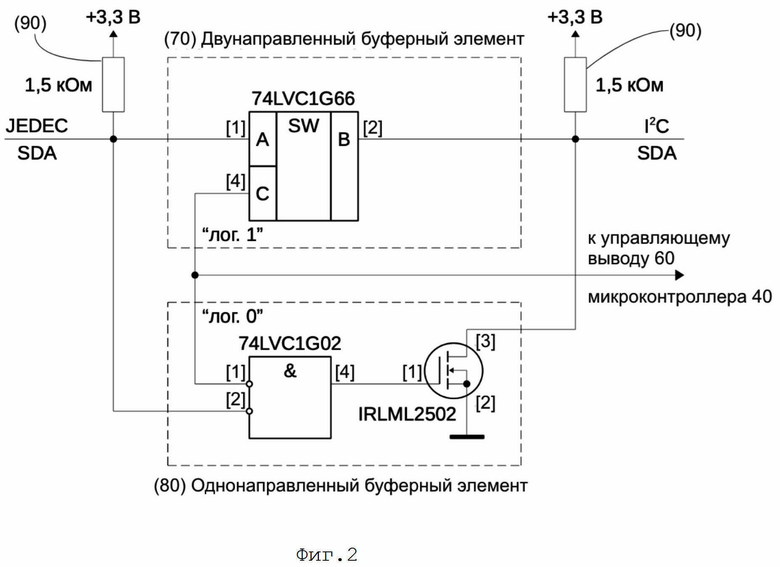

Фиг.2 – схема реализации буферного блока в одном из вариантов осуществления изобретения. Цифрами в квадратных скобках обозначены номера выводов элементов логической схемы.

ВАРИАНТЫ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

В соответствии с раскрытым техническим решением модуль оперативной памяти включает в себя узел 10 хранения данных, выполненный с возможностью предоставления по запросу системной плате 20, к которой подключено устройство, данных настроек модуля оперативной памяти. Данный узел 10 хранения данных в раскрытом решении отличается по своей сути от известного из приведённого выше аналога, но при этом он может быть соединён и взаимодействовать с системной платой 20 известным образом: контроллер 30 оперативной памяти системной платы может быть соединён в качестве ведущего устройства с узлом 10 хранения данных с возможностью передачи данных по шине i2c по протоколу Jedec.

В соответствии с раскрытым техническим решением узел 10 хранения данных включает в себя микроконтроллер 40 и буферный блок 50. При этом микроконтроллер 40 выполнен с возможностью передачи данных по протоколу i2c в качестве ведомого устройства. В качестве такого микроконтроллера 40 узел 10 хранения данных может включать в себя RISC-V микроконтроллер MIK32 АМУР.

Преимуществами RISC-V микроконтроллера MIK32 АМУР являются во-первых, возможность работы по шине i2c в качестве ведомого устройства, что является необходимым для функционирования раскрытого решения; и, во-вторых, RISC-V микроконтроллера MIK32 АМУР выполнен с возможностью задавать не один фиксированный адрес ведомого устройства на шине i2c, а позволяет задать два адреса, один из которых может быть групповым (то есть охватывать сразу группу адресов). Протокол Jedec предполагает специфические команды, которые кодируются с помощью адреса устройства на шине; следовательно, для обеспечения возможности приёма этих команд, микроконтроллер 40 должен быть выполнен с возможностью отклика по меньшей мере по 8 различным адресам ведомого устройства на шине. Наличие группового адреса в RISC-V микроконтроллере MIK32 АМУР обеспечивает такую возможность.

Микроконтроллер 40 в соответствии с раскрытым техническим решением также выполнен с возможностью в установленном состоянии модуля оперативной памяти предоставлять системной плате 20 данные настроек модуля оперативной памяти в ответ на запрос контроллера 30 оперативной памяти системной платы 20 по шине i2c. Под установленным состоянием модуля оперативной памяти следует понимать состояние, в котором модуль оперативной памяти соединён с системной платой 20 с возможностью выполнения своего назначения в рамках вычислительного устройства. В таком состоянии модуль оперативной памяти и, а конкретно узел 10 хранения данных, соединён с возможностью передачи данных по шине i2c с контроллером 30 оперативной памяти системной платы 20. При этом контроллер 30 оперативной памяти системной платы 20 в подавляющем большинстве вычислительных устройств осуществляет связь с узлом хранения данных по протоколу Jedec и шине i2c. Возможность предоставлять системной плате 20 данные настроек модуля оперативной памяти может обеспечиваться среди прочего благодаря наличию у микроконтроллера 40 доступа к данным настроек модуля оперативной памяти. Такой доступ может обеспечиваться, например, благодаря наличию данных настроек модуля оперативной памяти в памяти микроконтроллера 40, либо носителя информации в виде, например, SPI-флэш накопителя, к которому микроконтроллер 40 имеет доступ, например, через SPI интерфейс. В соответствии с протоколом Jedec возможность предоставлять данные осуществляется благодаря тому, что микроконтроллер 40 способен по протоколу Jedec в качестве ведомого устройства предоставлять для считывания данные по запросу от контроллера 30 оперативной памяти системной платы 20, выступающего в качестве ведущего устройства.

В рамках раскрытого технического решения возможность микроконтроллера 40 работать по протоколу Jedec обеспечивается помимо прочего благодаря тому, что узел 10 хранения данных включает в себя буферный блок 50, соединённый последовательно с линией данных (SDA) шины i2c. Последовательное соединение предполагает, что любой сигнал, направляемый по линии данных шины должен пройти через буферный блок 50. При этом буферный блок 50 выполнен с возможностью под воздействием управляющего сигнала микроконтроллера 40 переключаться в любой из следующих режимов передачи сигналов: двунаправленный или однонаправленный, причём в однонаправленном режиме буферный блок 50 допускает приём сигналов микроконтроллером 40 и блокирует передачу сигналов микроконтроллером 40 по линии данных.

Для упомянутого переключения буферного блока 50 под управлением микроконтроллера 40 микроконтроллер 40 выполнен с возможностью передачи управляющего сигнала на буферный блок 50. Для этого управляющий вывод 60 микроконтроллера 40 может быть соединён с буферным блоком 50 с возможностью передачи управляющего сигнала.

В предпочтительном варианте осуществления технического решения буферный блок 50 включает в себя подключенные параллельно друг другу двунаправленный буферный элемент 70 и однонаправленный буферный элемент 80. Параллельное соединение предполагает, что любой сигнал, проходящий через буферный блок 50, должен пройти либо через двунаправленный буферный элемент 70, либо через однонаправленный буферный элемент 80. В этом варианте осуществления двунаправленный буферный элемент 70 выполнен с возможностью блокировки передачи сигналов через него и с возможностью обеспечения передачи сигналов в обоих направлениях линии данных в активном состоянии двунаправленного буферного элемента 70; а однонаправленный буферный элемент 80 выполнен с возможностью обеспечения передачи сигналов только в одном направлении от контроллера 30 оперативной памяти системной платы 20 ведомому устройству в активном состоянии однонаправленного буферного элемента 80. При этом буферный блок 50 может быть выполнен с возможностями при переключении в однонаправленный режим блокировки двунаправленного буферного элемента 70 и активации однонаправленного буферного элемента 80. Кроме того, буферный блок может быть выполнен с возможностью активации двунаправленного буферного элемента 70 при переключении в двунаправленный режим. Также однонаправленный буферный элемент 80 может быть выполнен с возможностью блокировки передачи сигналов через него, при этом буферный блок 50 может быть выполнен с возможностью блокировать однонаправленный буферный элемент 80 при переключении в двунаправленный режим под управлением микроконтроллера 40.

В протоколе i2c после каждого переданного байта приёмник сообщает в шину бит подтверждения (девятый бит): логический 0 (ACK) в случае подтверждения приёма, логическая 1 (NACK) – неподтверждения (например, в случае завершения операции чтения). В микроконтроллер 40, выполненный с возможностью передачи данных по протоколу i2c, заложена такая логика и она не соответствует логике протокола Jedec. В соответствии с протоколом Jedec девятый бит используется для передачи информации. Так, например, в случае, когда ведущее устройство выдаёт команду чтения адреса страницы, ведомое устройство в девятом бите сообщает адрес выбранной страницы: ACK – страница 0, NACK – страница 1. Также в соответствии с протоколом существует восемь команд управления защитой от записи блоков памяти (4 команды, устанавливающие защиту и 4 команды, проверяющие состояние защиты). Если в девятом бите ведомое устройство выдаёт АСК, это означает, что блок памяти не защищён от записи, если выдаётся NACK, это означает, что блок памяти защищён от записи. При записи данных на ведомое устройство (например, в узел хранения данных) ведомое устройство выставляет ACK после байта команды и байта адреса элемента массива; на байт данных выставляется АСК в случае отсутствия защиты от записи (или снятой защиты от записи) и выставляется NACK в случае установленной защиты от записи.

Микроконтроллер 40, выполненный с возможностью передачи данных по протоколу i2c выставляет значения девятого бита в соответствии с протоколом i2c (всегда выставляет – АСК после каждого байта). Для обеспечения совместимости в случае, когда в соответствии с протоколом Jedec ведущее устройство должно получить от микроконтроллера 40 логическую 1 – NACK, необходимо блокировать передачу логический 0 – АСК микроконтроллером 40 в шину.

Управляемый микроконтроллером 40 буферный блок 50 предназначен в первую очередь для обеспечения совместимости упомянутых протоколов передачи данных. Он реализует эту функцию благодаря возможности под управлением микроконтроллера обеспечивать либо двунаправленный, либо однонаправленный от ведущего ведомому устройству режимы передачи сигналов. Преимущественно от ведомого устройства требуется выдавать логический 0 – АСК, буферный блок в этих случаях работает в двунаправленном режиме, пропуская логический 0 – АСК от ведомого устройства (микроконтроллера 40) к ведущему (контроллеру 30 оперативной памяти системной платы 20). В случае необходимости передачи ведомым устройством логической 1 – NACK, микроконтроллер 40 через управляющий вывод 60 направляет управляющий сигнал (в представленном на фигурах чертежей варианте осуществления это логический ноль), блокирующий двунаправленный буферный элемент 70 и разрешающий работу однонаправленного буферного элемента 80 (или активирующий однонаправленный буферный элемент), тем самым переключая линию данных в однонаправленный режим передачи сигналов от ведущего устройства к ведомому устройству. В однонаправленном режиме сигнал ведомого устройства (микроконтроллера 40) не доходит до ведущего устройства. При этом сигнал логической 1 – NACK формируется благодаря наличию в интерфейсе i2c в соответствии с его спецификацией источника тока или «подтягивающего» резистора 90, подключенного к источнику питающего напряжения. В качестве источника питающего напряжения резистора 90 может использоваться источник питания микроконтроллера 40. Предложенная схема с двумя буферными элементами делит линию данных на два сегмента: JEDEC SDA и I2C SDA. Для корректной работы каждого из сегментов шины согласно спецификации I2C устанавливается свой подтягивающий резистор 90 или источник тока. То есть в соответствии со спецификацией стандарта один подтягивающий резистор 90 должен быть подключен к линии данных по отношению к буферному блоку 50 со стороны микроконтроллера 40; второй подтягивающий резистор 90 должен быть подключен к линии данных по отношению к буферному блоку 50 со стороны контроллера 30 оперативной памяти системной платы 20. В некоторых вариантах осуществления изобретения используется подтягивающий резистор, подключенный к источнику питания; в иных вариантах осуществления может быть использовано подключение к источнику тока. Этот принцип с примерами деления на сегменты представлен на рис. 1 стр. 4 и на рис. 43 стр. 52 спецификации I2C I2C-bus specification and user manual, опубликовано 01.10.2021, рисунок 1 на стр. 4, и рисунок 43 на странице 52). Функция подтягивающих резисторов описана в п.3.1.1 на странице 8 спецификации I2C (I2C-bus specification and user manual, опубликовано 01.10.2021): “SDA и SCL - это двунаправленные линии, подключенные к положительному напряжению питания посредством источника тока или подтягивающего резистора (см. Рисунок 3). Когда шина свободна, обе линии находятся в состоянии “ВЫСОКИЙ” (HIGH). Выходные каскады устройств, подключенных к шине, должны иметь открытый сток или открытый коллектор, чтобы выполнять функцию “монтажное ИЛИ”” (перевод авторов). Таким образом, в соответствии со стандартом протокола I2C линия данных шины i2c по умолчанию содержит подтягивающий резистор или источник тока в каждом из сегментов линии данных: между буферным блоком 50 и контроллером 30 оперативной памяти системной платы 20; и между буферным блоком 50 и микроконтроллером 40.

Таким образом, в приведённом варианте осуществления при необходимости выдачи в линию данных логической «1» микроконтроллер 40 через управляющий вывод 60 формирует управляющий сигнал, блокирующий двунаправленный буферный элемент 70 и разрешающий работу однонаправленного буферного элемента 80. В результате этого благодаря наличию подтягивающего резистора в линии данных сегмента шины между буферным блоком 50 и контроллером 30 оперативной памяти системной платы формируется логическая «1».

В качестве двунаправленного буферного элемента в некоторых вариантах осуществления может использоваться логический вентиль (например, 66 элемент 74 серии 74LVC1G66). В качестве однонаправленного буферного элемента может быть использована совокупность вентилей, например 02 вентиль с полевым транзистором (например, IRLML2502) или совокупность вентилей 02 и 06. Необходимо понимать, что буферный блок 40 может иметь иную конструкцию из известных компонентов, обеспечивающих возможность переключения между двунаправленным и однонаправленным от ведущего к ведомому устройству режимами, что не выходит за рамки сущности раскрытого технического решения. В различных вариантах осуществления раскрытого технического решения буферный блок может иметь иные схемные решения. Раскрытая схема с программно-аппаратной реализацией передачи данных по протоколу Jedec с одной стороны позволяет реализовать назначение узла хранения данных и модуля оперативной памяти в целом, а с другой стороны позволяет ослабить требования к производительности микроконтроллера и времени его реакции по сравнению с программной реализацией передачи данных.

Настоящее техническое решение было подробно описано со ссылкой на отдельные варианты его осуществления, однако очевидно, что оно может быть осуществлено в различных вариантах, не выходя за рамки заявленного объёма правовой охраны, определяемого формулой изобретения.

Изобретение относится к модулям оперативной памяти. Технический результат – повышение быстродействия модуля оперативной памяти. Модуль включает в себя узел хранения данных, выполненный с возможностью предоставления по запросу системной плате, к которой подключен модуль, данных настроек модуля оперативной памяти. При этом узел хранения данных включает в себя микроконтроллер, выполненный с возможностью передачи данных по протоколу i2c в качестве ведомого устройства, с возможностью в установленном состоянии модуля оперативной памяти предоставлять системной плате данные настроек модуля оперативной памяти в ответ на запрос контроллера оперативной памяти системной платы по шине i2c, а также с возможностью передачи управляющего сигнала на буферный блок. Буферный блок соединён последовательно с линией данных шины i2c и выполнен с возможностью под воздействием управляющего сигнала микроконтроллера переключения в любой один из следующих режимов передачи сигналов: двунаправленный или однонаправленный, причём в однонаправленном режиме буферный блок допускает приём сигналов микроконтроллером и блокирует передачу сигналов микроконтроллером по линии данных. 7 з.п. ф-лы, 2 ил.

1. Модуль оперативной памяти, включающий в себя

узел хранения данных, выполненный с возможностью предоставления по запросу системной плате, к которой подключен модуль, данных настроек модуля оперативной памяти;

отличающийся тем, что

узел хранения данных включает в себя

микроконтроллер, выполненный с возможностью передачи данных по протоколу i2c в качестве ведомого устройства, с возможностью в установленном состоянии модуля оперативной памяти предоставлять системной плате данные настроек модуля оперативной памяти в ответ на запрос контроллера оперативной памяти системной платы по шине i2c, а также с возможностью передачи управляющего сигнала на буферный блок;

буферный блок, соединённый последовательно с линией данных шины i2c и выполненный с возможностью под воздействием управляющего сигнала микроконтроллера переключения в любой один из следующих режимов передачи сигналов: двунаправленный или однонаправленный, причём в однонаправленном режиме буферный блок допускает приём сигналов микроконтроллером и блокирует передачу сигналов микроконтроллером по линии данных.

2. Модуль оперативной памяти по п. 1, отличающийся тем, что

в качестве микроконтроллера узел хранения данных содержит RISC-V микроконтроллер MIK32 АМУР.

3. Модуль по п. 1, отличающийся тем, что

модуль содержит носитель информации в виде SPI-флэш накопителя;

при этом носитель информации, выполнен с возможностью постоянного хранения данных настроек модуля оперативной памяти;

при этом микроконтроллер выполнен с возможностью считывания с носителя информации и оперативного хранения данных настроек модуля оперативной памяти.

4. Модуль по п. 1, отличающийся тем, что

буферный блок включает в себя подключенные параллельно друг другу двунаправленный буферный элемент и однонаправленный буферный элемент;

при этом

двунаправленный буферный элемент, выполнен с возможностью блокировки передачи сигналов через него и с возможностью обеспечения передачи сигналов в обоих направлениях линии данных;

однонаправленный буферный элемент выполнен с возможностью обеспечения передачи сигналов только в одном направлении от контроллера оперативной памяти системной платы микроконтроллеру.

5. Модуль по п. 1, отличающийся тем, что

линия данных шины i2c содержит подтягивающий резистор или источник тока, в сегменте линии данных между буферным блоком и контроллером оперативной памяти системной платы.

6. Модуль по п. 1, отличающийся тем, что

линия данных шины i2c содержит подтягивающий резистор или источник тока в каждом из сегментов линии данных: между буферным блоком и контроллером оперативной памяти системной платы; и между буферным блоком и микроконтроллером.

7. Модуль по п. 1, отличающийся тем, что

микроконтроллер выполнен с возможностью отклика по шине i2c по по меньшей мере восьми адресам на шине.

8. Модуль по п. 1, отличающийся тем, что

микроконтроллер содержит управляющий вывод, который соединён с буферным блоком с возможностью передачи управляющего сигнала.

| US 10997108 B2, 04.05.2021 | |||

| US 9934148 B2, 03.04.2018 | |||

| US 10671299 B2, 02.06.2020 | |||

| ОБЕСПЕЧЕНИЕ ОЧЕРЕДИ КОМАНД ВО ВСТРОЕННОЙ ПАМЯТИ | 2014 |

|

RU2640652C2 |

Авторы

Даты

2024-07-16—Публикация

2024-02-05—Подача