Изобретение относится к области вычислительной техники и может быть использовано для программной цифровой обработки сигналов в системах радиолокации, гидроакустики и связи.

Из уровня техники известно вычислительное устройство для цифровой обработки сигналов, реализующее функцию быстрого преобразования Фурье (Авторское свидетельство СССР №1295414, МПК: G06F 15/332, опубликовано 07.03.1987 г.). Вычислительное устройство содержит вход управления режимом, блок синхронизации, регистры входных данных, коммутаторы операндов, умножитель, сумматор-вычитатель, выходные коммутаторы и регистры результата.

Недостатком вычислительного устройства является аппаратная реализация только одной функции обработки сигнала.

Известен также программируемый процессор спектральной обработки сигналов (Авторское свидетельство СССР №744603, МПК: G06F 15/34, опубликовано 30.06.1980 г.). Программируемый процессор спектральной обработки сигналов содержит первый и второй блоки регистров, сумматор, блок умножения, блок управления, блок синхронизации, коммутатор, блоки оперативной памяти, блок памяти констант и программ, индексный блок адресации, блок сопряжения внутренних и внешних шин, входы и выходы данных, входы и выходы управления.

Программируемый процессор спектральной обработки сигналов позволяет реализовать различные алгоритмы вычислений спектральных функций, включая быстрое преобразование Фурье (БПФ), однако имеет сравнительно низкое быстродействие, так как операции алгоритма выполняются процессором последовательно в одном потоке обработки.

Наиболее близким к заявляемому техническому решению является процессор цифровой обработки сигналов (Авторское свидетельство СССР №1837320, МПК: G06F 15/332, опубликовано 30.08.1993 г.), выбранный в качестве прототипа. Процессор цифровой обработки сигналов имеет вход обрабатываемого сигнала, вход синхронизации, содержит устройство управления и несколько вычислительных блоков. Каждый вычислительный блок содержит восемь регистров входных отсчетов, коммутатор, блок формирования весовых коэффициентов, два умножителя, два вычислительных модуля и выполняет базовую операцию над отсчетами А и В входного сигнала.

Данный процессор цифровой обработки сигналов имеет сравнительно невысокое быстродействие, ограниченное разбиением потока оцифрованных значений входного сигнала только на два параллельно обрабатываемых потока. Функциональные возможности процессора цифровой обработки сигналов ограничены выполнением несколькими, имеющимися в процессоре вычислительными блоками, только одной программной функции одновременно.

Таким образом, известные программируемые цифровые процессоры не обладают необходимыми характеристиками по обработке сигналов.

Техническим результатом предлагаемого изобретения является расширение функциональных возможностей и повышение производительности программируемого устройства цифровой обработки сигналов.

Технический результат достигается тем, что программируемое устройство цифровой обработки сигналов содержит контроллер шины PCI, первое и второе устройства ввода LVDS, коммутатор каналов ввода-вывода LVDS, первое и второе устройства вывода LVDS, по крайней мере, два вычислительных устройства, буфер ввода данных, буфер вывода данных и буфер обмена PCI для каждого вычислительного устройства, по крайней мере, один буфер обмена вычислительных устройств, а также постоянное запоминающее устройство, первый вход-выход контроллера шины PCI является входом-выходом шины системного магистрального интерфейса CompactPCI, второй вход-выход контроллера шины PCI соединен шиной управления с входом-выходом коммутатора каналов ввода-вывода LVDS и с третьим входом-выходом контроллера шины каждого вычислительного устройства, третий вход-выход контроллера шины PCI соединен шиной обмена данными с первым входом-выходом каждого буфера обмена PCI, входы первого и второго устройств ввода LVDS являются соответственно первым и вторым входами данных программируемого устройства цифровой обработки сигналов, выходы первого и второго устройств ввода LVDS соединены соответственно с первым и вторым входами коммутатора каналов ввода-вывода LVDS, первый и второй выходы коммутатора каналов ввода-вывода LVDS соединены с входами первого и второго устройств вывода LVDS, выходы первого и второго устройств вывода LVDS являются соответственно первым и вторым выходами данных программируемого устройства цифровой обработки сигналов, третий выход коммутатора каналов ввода-вывода LVDS соединен с входом каждого буфера ввода данных, третий вход коммутатора каналов ввода-вывода LVDS соединен с выходом каждого буфера вывода данных, вход первого буфера вывода данных, выход первого буфера ввода данных и второй вход-выход первого буфера обмена PCI соединены первой шиной обмена данными с вторым входом-выходом контроллера шины одного вычислительного устройства, вход второго буфера вывода данных, выход второго буфера ввода данных и второй вход-выход второго буфера обмена PCI соединены второй шиной обмена данными с вторым входом-выходом контроллера шины другого вычислительного устройства, при этом каждое вычислительное устройство содержит, по крайней мере, два цифровых сигнальных процессора, контроллер шины вычислительного устройства и оперативное запоминающее устройство, входы-выходы цифровых сигнальных процессоров, вход-выход оперативного запоминающего устройства, первый вход-выход контроллера шины вычислительного устройства соединены шиной системного магистрального интерфейса вычислительного устройства, первый вход-выход буфера обмена вычислительных устройств соединен с шиной системного магистрального интерфейса одного вычислительного устройства, и второй вход-выход буфера обмена вычислительных устройств соединен с шиной системного магистрального интерфейса другого вычислительного устройства,

Программируемое устройство цифровой обработки сигналов предназначено для обработки радиолокационных сигналов в составе вычислительного комплекса, включающего один или несколько модулей программируемого устройства цифровой обработки сигналов, модуль управляющего процессора, являющийся универсальным процессором обработки данных, один или несколько модулей аналого-цифрового преобразователя, и модуль графического контроллера, обеспечивающий управление отображением информации на видеомониторе.

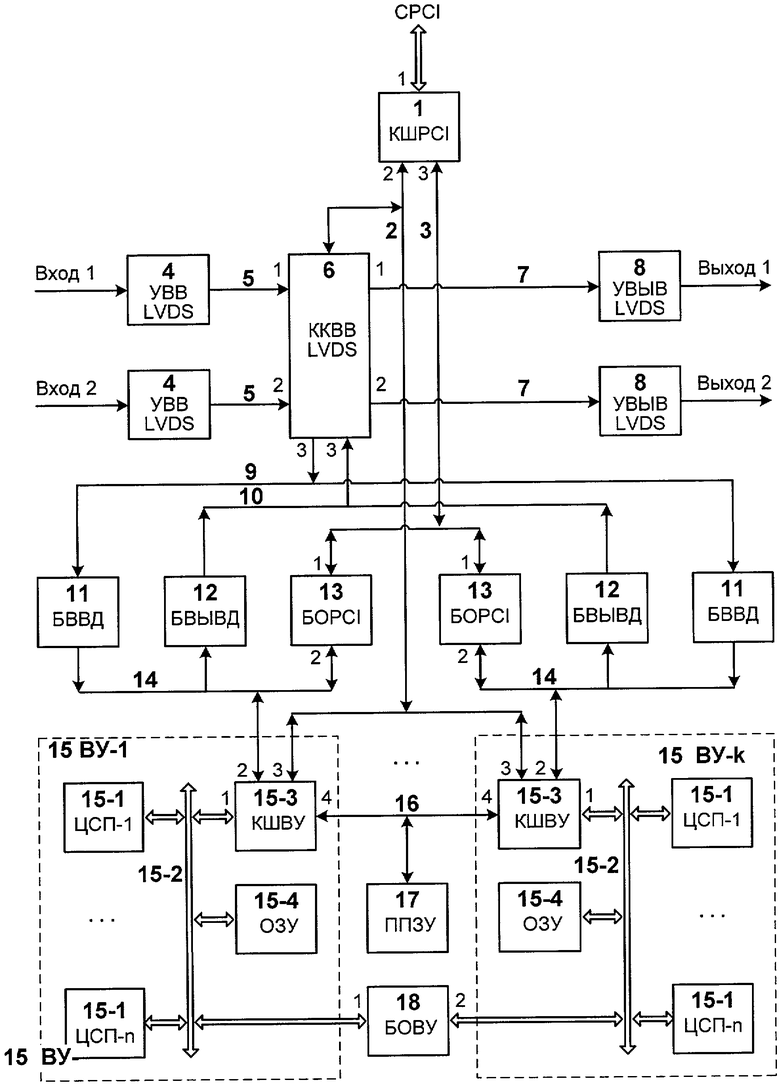

Структурная схема программируемого устройства цифровой обработки сигналов представлена на чертеже, где:

1 - контроллер шины PCI (КШ PCI);

2 - шина управления контроллера шины PCI;

3 - шина обмена контроллера шины PCI с буферами памяти;

4 - устройство ввода LVDS (УВВ LVDS);

5 - шина ввода данных коммутатора каналов ввода-вывода LVDS;

6 - коммутатор каналов ввода-вывода LVDS (KKBB LVDS);

7 - шина вывода данных коммутатора каналов ввода-вывода LVDS;

8 - устройство вывода LVDS (УВЫВ LVDS);

9 - шина вывода данных с ККВВ LVDS на буферы ввода данных;

10 - шина ввода данных с буферов вывода данных на ККВВ LVDS;

11 - буфер ввода данных (БВВД);

12 - буфер вывода данных (БВЫВД);

13 - буфер обмена PCI (БО PCI);

14 - шина обмена данными контроллера шины вычислительного устройства с буферами ввода-вывода;

15 - вычислительное устройство (ВУ-1…ВУ-k);

15-1 - цифровой сигнальный процессор (ЦСП-1…ЦСП-n);

15-2 - шина системного магистрального интерфейса вычислительного устройства;

15-3 - контроллер шины вычислительного устройства (КШВУ);

15-4 - оперативное запоминающее устройство (ОЗУ);

16 - шина обмена данными КШВУ с ППЗУ;

17 - постоянное запоминающее устройство (ППЗУ);

18 - буфер обмена вычислительных устройств (БОВУ).

Программируемое устройство цифровой обработки сигналов содержит контроллер шины PCI (КШ PCI) 1, два устройства ввода LVDS (УВВ LVDS) 4, коммутатор каналов ввода-вывода LVDS (ККВВ LVDS) 6, два устройства вывода LVDS (УВЫВ LVDS) 8, по крайней мере, два вычислительных устройства (ВУ-1…BY-k) 15, буфер ввода данных (БВВД) 11, буфер вывода данных (БВЫВД) 12 и буфер обмена PCI (БО PCI) 13 для каждого вычислительного устройства 15, буфер обмена вычислительных устройств 18 и постоянное запоминающее устройство (ППЗУ) 17.

Каждое вычислительное устройство (ВУ-1…BY-k) 15 содержит, по крайней мере, два цифровых сигнальных процессора (ЦСП-1…ЦСП-n) 15-1, контроллер шины вычислительного устройства (КШВУ) 15-3 и оперативное запоминающее устройство (ОЗУ) 15-4, соединенные шиной системного магистрального интерфейса вычислительного устройства 15-2.

Вход-выход 1 контроллера шины PCI 1 является входом-выходом шины системного магистрального интерфейса CompactPCI (CPCI). Вход-выход 2 контроллера шины PCI 1 соединен шиной управления контроллера шины PCI 2 с входом-выходом управления коммутатора каналов ввода-вывода LVDS бис входом-выходом 3 КШВУ 15-3 каждого вычислительного устройства 15. Вход-выход 3 контроллера шины PCI 1 соединен шиной обмена контроллера шины PCI с буферами памяти 3 с входом-выходом 1 буферов обмена PCI 13.

На входы Вход 1 первого и Вход 2 второго устройств ввода LVDS 4 поступают оцифрованные данные обрабатываемых сигналов с первого и второго каналов ввода LVDS. Выходы первого и второго устройств ввода LVDS 4 соединены шинами ввода данных коммутатора каналов ввода-вывода LVDS 5 с входами 1 и 2 коммутатора каналов ввода-вывода LVDS 6 соответственно. Выход 3 коммутатора каналов ввода-вывода LVDS 6 соединен шиной вывода данных с ККВВ LVDS на буферы ввода данных 9 с входами буферов ввода данных 11. Выходы буферов вывода данных 12 соединены шиной ввода данных с буферов вывода данных на ККВВ LVDS 10 с входом 3 коммутатора каналов ввода-вывода LVDS 6. Выходы 1 и 2 коммутатора каналов ввода-вывода LVDS 6 соединены шинами вывода данных коммутатора каналов ввода-вывода LVDS 7 с входами первого и второго устройств вывода LVDS 8 соответственно. Данные с выходов Выход 1 первого и Выход 2 второго устройств вывода LVDS 8 выдаются на первый и второй каналы вывода LVDS.

Вход-выход 2 КШВУ 15-3 каждого вычислительного устройства 15 соединен шиной обмена данными контроллера шины вычислительного устройства с буферами ввода-вывода 14 с выходом буфера ввода данных 11, входом буфера вывода данных 12 и входом-выходом 2 буфера обмена PCI 13, соответствующих данному вычислительному устройству 15. Вход-выход 4 КШВУ 15-3 каждого вычислительного устройства 15 соединен шиной обмена данными КШВУ с ППЗУ 16 с входом-выходом постоянного запоминающего устройства 17.

Вход-выход 1 буфера обмена вычислительных устройств 18 соединен с шиной системного магистрального интерфейса 15-2 одного вычислительного устройства 15, и вход-выход 2 БОВУ 18 соединен с шиной системного магистрального интерфейса 15-2 другого вычислительного устройства 15.

Интерфейс LVDS (Low Voltage Differential Signaling Interface Std ANSI/TIA/EIA-644) является высокоскоростным последовательным однонаправленным синхронным интерфейсом, осуществляющим соединение от одного передатчика к одному приемнику информации (топология точка-точка) по дифференциальным симметричным линиям. Интерфейс LVDS использует дифференциальные сигналы с уровнями 350 мВ при токе в линии 3,5 мА. Интерфейс LVDS включает одну дифференциальную линию синхронизации и одну или несколько дифференциальных линий передачи данных, скорость передачи по каждой линии данных до 1 Гбит/с.

Интерфейс LVDS используется для ввода в программируемое устройство цифровой обработки сигналов данных оцифрованного сигнала с внешнего устройства аналого-цифрового преобразования и для пересылки данных между программируемыми устройствами цифровой обработки сигналов. Программируемое устройство цифровой обработки сигналов имеет два канала ввода и два канала вывода LVDS, каждый из которых включает одну линию синхронизации и четыре линии передачи данных для повышения пропускной способности канала. Канал ввода или вывода LVDS обеспечивает ввод до 100 миллионов 32-разрядных значений оцифрованных данных в секунду.

Программируемое устройство цифровой обработки сигналов предназначено для использования в составе вычислительного комплекса радиолокационной станции (РЛС) совместно с модулем аналого-цифрового преобразования (АЦП). Дифференциальный метод передачи сигналов по симметричной линии, малое изменение уровней и низкое нарастание напряжения (1 В/нс) сигналов обусловливают малый уровень наводок от интерфейса LVDS и позволяют расширить динамический диапазон АЦП и приемника радиолокационного сигнала.

Устройство ввода LVDS 4 обеспечивает прием данных с канала ввода LVDS. Интерфейс LVDS за один период сигнала в линии синхронизации последовательно пересылает по линии данных кадр, содержащий 10 периодов сигнала данных. Интерфейс LVDS является синхронным интерфейсом и при отсутствии передаваемых данных пересылает по линиям данных канала LVDS специальный кадр синхронизации. УВВ LVDS 4 осуществляет преобразование последовательных кадров в параллельный 10 битный код и выделение из последовательности кадров, включающей кадры синхронизации, кадры, содержащие значащие данные. Из 10 бит кадра, передаваемого по линии данных канала LVDS, 8 младших бит являются значащими битами данных и два старших бита используются для служебных целей. Таким образом, за один период сигнала в линии синхронизации по четырем линиям данных канала LVDS передается 32 бита данных.

Устройство вывода LVDS 8 предназначено для передачи данных в канал вывода LVDS. На вход УВЫВ LVDS 8 поступают 32 разрядные данные, которые разделяются на четыре 8-разрядных элемента данных. Каждый элемент данных дополняется двумя служебными битами для формирования 10-битного кадра. Параллельный 10-битный кадр преобразуется в последовательный кадр и передается в канал вывода LVDS. За один период сигнала в линии синхронизации в каждую из четырех линий данных канала вывода LVDS передается 10 периодов сигнала данных. При отсутствии на входе устройства вывода LVDS 8 данных в канал вывода LVDS предаются специальные кадры синхронизации.

Коммутатор каналов ввода-вывода LVDS 6 обеспечивает коммутацию данных, поступающих с выходов устройств ввода LVDS 4 и подаваемых на входы устройств вывода LVDS 8. Управление коммутатором каналов ввода-вывода LVDS 6 осуществляется по шине управления контроллера шины PCI 2. В зависимости от выбранного режима, коммутатор каналов ввода-вывода LVDS 6 осуществляет следующие подключения:

- данные с выхода устройства ввода LVDS 4 коммутируются на вход буфера ввода данных 11 одного или нескольких вычислительных устройств 15;

- данные с выхода устройства ввода LVDS 4 коммутируются на вход устройства вывода LVDS 8 - режим ретрансляции данных с канала ввода LVDS в канал вывода LVDS;

- данные с выхода одного из буферов вывода данных 12 коммутируются на вход устройства вывода LVDS 8 - режим вывода данных в канал LVDS.

Возможен одновременный ввод данных с обоих устройств ввода LVDS 4 в один буфер ввода данных 11. Также возможна коммутация данных с одного устройства ввода LVDS 4 параллельно на вход буфера ввода данных 11 и на вход устройства вывода LVDS 8. При выводе данных из буфера вывода данных 12 на устройство вывода LVDS 8 ретрансляция данных с канала ввода LVDS через данное устройство вывода LVDS 8 невозможна.

Буфер ввода данных (БВВД) 11 предназначен для буферизации данных, вводимых с первого и второго каналов ввода LVDS, на вычислительное устройство 15. Каждый буфер ввода данных 11 соответствует своему вычислительному устройству 15. Данные на вход буфера ввода данных 11 поступают с выхода 3 коммутатора каналов ввода-вывода LVDS 6. Запись данных в БВВД 11 осуществляется по шине вывода данных с ККВВ LVDS на буферы ввода данных 9 32-разрядными словами с частотой до 100 МГц. Чтение данных с выхода буфера ввода данных 11 выполняется контроллером шины вычислительного устройства 15-3 по шине обмена данными контроллера шины вычислительного устройства с буферами ввода-вывода 14 64-разрядными словами с частотой до 120 МГц.

Буфер ввода данных 11 представляет собой двухпортовое оперативное запоминающее устройство с двумя переключаемыми банками памяти. Размер БВВД 11 определяется из условия накопления в каждом из двух банков памяти буфера данных оцифрованных сигналов, поступающих с двух каналов ввода LVDS за период времени, соответствующий периоду импульса запуска передатчика РЛС. Например, при представлении элемента дальности 32-разрядным значением, максимальном числе элементов дальности в периоде импульса запуска передатчика РЛС, равном 1024, и ввода данных для двух каналов ввода LVDS, размер буфера данных 11 составляет:

32×1024×2=64 Кбит или 8 Кбайт.

При разделении потока входных данных между несколькими вычислительными устройствами 15, размер БВВД 11 для каждого вычислительного устройства может быть уменьшен в соответствующее число раз.

Буфер вывода данных (БВЫВД) 12 предназначен для буферизации данных, выводимых с вычислительного устройства 15 на первый и второй каналы вывода LVDS. Каждый буфер вывода данных 12 соответствует своему вычислительному устройству 15. Данные на вход буфера вывода данных 12 поступают с входа-выхода 2 контроллера шины вычислительного устройства 15-3. Запись данных в БВЫВД 12 выполняется по шине обмена данными контроллера шины вычислительного устройства с буферами ввода-вывода 14 64-разрядными словами с частотой до 120 МГц. Чтение данных с выхода буфера вывода данных 12 осуществляется на вход 3 коммутатора каналов ввода-вывода LVDS 6 по шине ввода данных с буферов вывода данных на ККВВ LVDS 10 32-разрядными словами с частотой до 100 МГц.

Буфер вывода данных 12 представляет собой двухпортовое оперативное запоминающее устройство с двумя переключаемыми банками памяти. Размер буфера вывода данных 12 равен размеру буфера ввода данных 11.

Буфер обмена (БО PCI) 13 предназначен для буферизации данных, пересылаемых между контроллером шины PCI 1 и контроллером шины вычислительного устройства 15-3. Каждый буфер обмена PCI 13 соответствует своему вычислительному устройству 15. Запись и чтение данных с входа-выхода 1 буфера обмена PCI 13 осуществляются по шине обмена контроллера шины PCI с буферами памяти 3 32-разрядными словами с частотой 33 МГц. Запись и чтение данных с входа-выхода 2 БО PCI 13 по шине обмена данными контроллера шины вычислительного устройства с буферами ввода-вывода 14 осуществляются 64-разрядными словами с частотой 120 МГц.

Для обеспечения непрерывного потока данных буфер может иметь организацию двухпортового оперативного запоминающего устройства с двумя переключаемыми банками памяти или буфера FIFO (First Input First Output). Размер буфера обмена PCI 13 определяется из условия минимизации накладных расходов на пересылку данных по шине системного магистрального интерфейса вычислительного устройства 15-2. Пересылка данных по шине системного магистрального интерфейса CompactPCI, имеющей меньшую тактовую частоту и разрядность данных, менее критична по затратам времени.

Шина системного магистрального интерфейса вычислительного устройства 15-2, для используемого типа ЦСП, требует 2 такта для захвата управления шиной, 2 такта, чтобы отдать управление шиной, 5 тактов на пересылку первого и 1 такт на пересылку последующих элементов блока данных. При пяти процентах накладных расходов на передачу управления шиной системного магистрального интерфейса вычислительного устройства 15-2, относительно времени передачи непрерывного блока данных, при передаче 64 бит данных за один такт шины, размер двухбанкового буфера составляет не менее:

2×(2+2+5-1)×64×1/0,05=20480 бит или 2560 байт.

Цифровой сигнальный процессор (ЦСП) 15-1 вычислительного устройства 15 - это микросхема типа ADSP-TS201S фирмы Analog Devices (ADSP-TS201S Data Sheet, Revision В, Analog Devices Inc., 2006). Микросхема ЦСП ADSP-TS201S при частоте синхронизации ядра процессора 600 МГц имеет максимальную производительность: для операций с данными в формате с фиксированной точкой - 4800 MIPS (миллионов операций в секунду) и для операций с данными в формате с плавающей точкой - 3600 MFLOPS (миллионов операций с плавающей точкой в секунду). Объем внутренней памяти ОЗУ микросхемы ADSP-TS201S, используемой для хранения кода программ и обрабатываемых данных составляет 24 Мбит. Внешний порт ADSP-TS201S обеспечивает объединение до 8 микросхем в группу (кластер), посредством шины системного магистрального интерфейса вычислительного устройства 15-2, с передачей управления шиной одному из ЦСП. Во все ЦСП 15-1 может загружаться как одна общая программа, или в каждый ЦСП 15-1 загружаются собственные программы обработки сигнала, ЦСП 15-1 могут вести обработку общих или раздельных данных.

Шина системного магистрального интерфейса вычислительного устройства 15-2 является специализированным системным магистральным параллельным интерфейсом. Шина обеспечивает подключение синхронных статических и динамических устройств памяти и устройств ввода-вывода, а также медленных асинхронных устройств, и поддерживает программный обмен данными, обмен по сигналам прерывания ЦСП и обмен в режиме прямого доступа к памяти. Шина системного магистрального интерфейса вычислительного устройства 15-2 имеет частоту синхронизации 120 МГц и 64-разрядную шину данных, что обеспечивает пиковую производительность передачи данных 960 Мбайт/с.

Оперативное запоминающее устройство (ОЗУ) 15-4 вычислительного устройства 15 предназначено для временного хранения промежуточных данных и результатов вычислений программ ЦСП 15-1. ОЗУ 15-4 является энергозависимым запоминающим устройством с возможностью многократной записи и чтения информации при выполнении программы ЦСП 15-1.

Постоянное запоминающее устройство (ППЗУ) 17 предназначено для хранения программ ЦСП 15-1 и таблиц коэффициентов. ППЗУ 17 выполнено на основе энергонезависимой FLASH-памяти с возможностью многократной записи информации при работе программируемого устройства цифровой обработки сигналов и ее хранения в выключенном состоянии устройства.

Буфер обмена вычислительных устройств (БО ВУ) 18 - есть общая (глобальная) область памяти двух вычислительных устройств 15, отображаемая на адресное пространство шины системного магистрального интерфейса вычислительного устройства 15-2, как локальная память каждого вычислительного устройства 15. Буфер обмена вычислительных устройств 18 реализует наиболее простой и быстрый способ обмена данными между вычислительными устройствами 15, с возможностью непосредственной записи и чтения ЦСП 15-1 каждого вычислительного устройства 15 данных в памяти буфера без дополнительных пересылок. При числе вычислительных устройств 15 более двух, каждая пара вычислительных устройств 15 соединяется со своим буфером обмена вычислительных устройств 18.

Буфер обмена вычислительных устройств 18 является двухпортовым оперативным запоминающим устройством. Объем памяти буфера обмена вычислительных устройств 18 должен быть не менее емкости буфера ввода данных 11 для обеспечения обмена данными вычислительных устройств 15 при обработке сигнала без сжатия входных данных.

Шина управления контроллера шины PCI 2 является синхронной параллельной двунаправленной мультиплексной шиной, по шине осуществляется запись и чтение 32-разрядных данных с частотой 33 МГц регистров программируемого устройства цифровой обработки сигналов, отображаемых на адресное пространство ввода-вывода шины PCI.

Шина обмена контроллера шины PCI с буферами памяти 3 представляет собой синхронную параллельную двунаправленную мультиплексную шину, по шине осуществляется запись и чтение 32-разрядных данных с частотой 33 МГц в память буферов обмена PCI 13, отображаемых на адресное пространство памяти шины PCI.

Шина ввода данных коммутатора каналов ввода-вывода LVDS 5 обеспечивает ввод данных с устройства ввода LVDS 4 на коммутатор каналов ввода-вывода LVDS 6.

Шина вывода данных коммутатора каналов ввода-вывода LVDS 7 обеспечивает вывод данных с коммутатора каналов ввода-вывода LVDS 6 на устройство вывода LVDS 8.

Шина ввода данных коммутатора каналов ввода-вывода LVDS 5 и шина вывода данных коммутатора каналов ввода-вывода LVDS 7 - это синхронные параллельные однонаправленные шины, осуществляющие передачу 32-разрядных данных с частотой до 100 МГц (определяется частотой сигнала в линии синхронизации канала LVDS).

Шина вывода данных с ККВВ LVDS на буферы ввода данных 9 предназначена для записи данных с коммутатора каналов ввода-вывода LVDS 5 в буферы ввода данных 11.

Шина ввода данных с буферов вывода данных на ККВВ LVDS 10 обеспечивает ввод данных на коммутатор каналов ввода-вывода LVDS 6 с буферов вывода данных 12.

Шина вывода данных с ККВВ LVDS на буферы ввода данных 9 и шина ввода данных с буферов вывода данных на ККВВ LVDS 10 являются синхронными параллельными однонаправленными мультиплексными шинами, осуществляющими передачу 32-разрядных данных с частотой до 100 МГц.

Шина обмена данными контроллера шины вычислительного устройства с буферами ввода-вывода 14 является синхронной параллельной двунаправленной мультиплексной шиной, по шине осуществляется запись и чтение 64-разрядных данных с частотой до 120 МГц (определяется частотой синхронизации шины системного магистрального интерфейса вычислительного устройства 15-2). Контроллер шины вычислительного устройства 15-3 обеспечивает по шине обмена данными контроллера шины вычислительного устройства с буферами ввода-вывода 14 запись данных в буфер вывода данных 12, чтение данных из буфера ввода данных 11, а также запись и чтение памяти буфера обмена PCI 13.

Шина обмена данными КШВУ с ПИЗУ 16 обеспечивает запись и чтение контроллером шины вычислительного устройства 15-3 данных постоянного запоминающего устройства 17. Шина обмена данными КШВУ с ППЗУ 16 является двунаправленной мультиплексной шиной. Частота, разрядность данных и сигналы управления шины зависят от конкретного используемого устройства FLASH-памяти.

Контроллер шины PCI (КШ PCI) 1 предназначен для управления обменом данными программируемого устройства цифровой обработки сигналов с шиной системного магистрального интерфейса CompactPCI (CPCI).

Контроллер шины PCI 1 поддерживает обмен данными по шине системного магистрального интерфейса CompactPCI в двух режимах:

- в режиме ведомого устройства шины PCI, под управлением программы, выполняемой модулем управляющего процессора вычислительного комплекса;

- в режиме ведущего устройства или режиме прямого доступа к памяти ведомых устройств на шине системного магистрального интерфейса CompactPCI 12.

В режиме ведомого устройства КШ PCI 1 под управлением управляющего (HOST) процессора вычислительного комплекса обеспечивает запись и чтение данных буфера обмена PCI 13, а также запись-чтение данных регистров коммутатора каналов ввода-вывода LVDS 6 и контроллера шины вычислительного устройства 15-3.

В режиме ведущего устройства КШ PCI 1 осуществляет пересылку данных между буфером обмена PCI 13 и памятью ведомого устройства шины системного магистрального интерфейса CompactPCI, в режиме прямого доступа к памяти, без участия управляющего процессора вычислительного комплекса.

Шина системного магистрального интерфейса CompactPCI (CPCI) является системным магистральным параллельным интерфейсом CompactPCI (CompactPCI Specification PICMG 2.0 D3.0 September 24, 1999). Шина системного магистрального интерфейса Compact PCI имеет тактовую частоту 33 МГц и 32-разрядную шину данных, что обеспечивает пиковую производительность передачи данных 132 Мбайт/с.

Интерфейс CompactPCI использует механический конструктив для промышленных магистрально-модульных систем с возможностью подключения до восьми модулей. Это обеспечивает включение в состав вычислительного комплекса нескольких (до четырех) программируемых устройств цифровой обработки сигналов под управлением модуля управляющего процессора и сопряжение устройств цифровой обработки сигналов с другими модулями, такими, как устройства аналого-цифрового преобразования и модуль графического контроллера.

Предлагаемое программируемое устройство цифровой обработки сигналов выполнено на основе микросхемы ADSP-TS201S фирмы Analog Devices, содержащей два вычислительных ядра, каждое из которых включает умножитель, арифметико-логическое устройство и устройство сдвига, а также содержащей память для хранения программ и данных, устройства ввода-вывода, внутренние шины адреса и данных (Солонина А.И., Улахович Д.А., Яковлев Л.А. Алгоритмы и процессоры цифровой обработки сигналов. - СПб.: БХВ-Петербург, 2001 г., с.60, рис.2.4). Оба вычислительных ядра, как правило, выполняют одну программную функцию одновременно. Цифровой сигнальный процессор ADSP-TS201S поддерживает обработку данных в форматах с фиксированной или плавающей точкой. С цифровым сигнальным процессором поставляется стандартная библиотека программных функций по обработке сигналов и изображений. Кроме того, возможна разработка собственных программных функций с использованием системы команд ADSP-TS201S.

Использование серийно выпускаемых микросхем цифровой обработки сигналов с заданными характеристиками производительности сводит задачу повышения производительности программируемого устройства цифровой обработки сигналов к созданию многопроцессорного вычислительного устройства с распределением и параллельной обработкой входного потока данных оцифрованного сигнала несколькими микросхемами ЦСП.

Программируемое устройство цифровой обработки сигналов работает следующим образом.

В процессе изготовления программируемого устройства цифровой обработки сигналов или при необходимости изменения программы обработки сигналов, код программы под управлением контроллера шины PCI 1 через контроллер шины вычислительного устройства 15-3 одного из вычислительных устройств 15 записывается в постоянное запоминающее устройство 17.

При включении питания или по сигналу начальной установки программируемого устройства цифровой обработки сигналов для каждого вычислительного устройства 15 под управлением контроллера шины вычислительного устройства 15-3 программа переписывается из ППЗУ 17 во внутреннюю память программ микросхем ЦСП 15-1. После завершения копирования ЦСП 15-1 запускает выполнение программы с начального адреса, заданного в коде загруженной программы.

Поступающие с внешнего устройства синхронизации тактовые импульсы ТИ (не показанные на рисунке), период следования которых соответствует неизменному положению антенны радиолокационной станции (РЛС), задают момент начала и время накопления радиолокационной информации.

С модуля аналого-цифрового преобразования на вход устройства ввода LVDS 4 программируемого устройства цифровой обработки сигналов поступают блоки данных обрабатываемого сигнала. Блок данных представляет массив 32-разрядных комплексных значений элементов дальности в текущем периоде импульса запуска передатчика (ИЗП) РЛС. Число блоков данных, соответствующих периоду ИЗП, за период следования тактовых импульсов (ТИ) задает число накоплений значений сигнала для каждого элемента дальности, при неизменном положении антенны РЛС.

Данные с выхода устройства ввода LVDS 4 через коммутатор каналов ввода-вывода LVDS 6 записываются в буферы ввода данных 11. Данные накапливаются в буфере ввода данных 11 в течение текущего периода импульса ИЗП, а в следующем периоде импульса ИЗП пересылаются в режиме прямого доступа к памяти (без пересылки под управлением программы ЦСП 15-1) в оперативное запоминающее устройство 15-4 вычислительного устройства 15 или внутреннюю память данных ЦСП 15-1.

Цифровые сигнальные процессоры 15-1 вычислительных устройств (ВУ-1…BY-k) 15 осуществляют цифровую обработку данных в соответствии с программой обработки сигнала. ЦСП 15-1 выполняет следующие функции обработки сигнала: накопление значений элементов дальности в течение числа периодов ИЗП, соответствующих периоду импульса ТИ, преобразование сигнала из временной в частотную форму представления и обратное преобразование, фильтрацию сигнала в частотной и временной областях, формирование пороговых значений сигнала и выделение целей на фоне помех.

При необходимости объединения данных результатов обработки сигнала нескольких вычислительных устройств 15 данные пересылаются через буфер обмена вычислительных устройств 17. Использование буфера обмена вычислительных устройств 17 позволяет переслать данные между ЦСП 15-1 вычислительных устройств 15 с использованием одной операции записи и одной операции чтения памяти буфера.

После завершения обработки сигнала за текущий период ТИ программируемое устройство цифровой обработки сигналов выдает обработанные данные одним из следующих способов.

При распределенной обработке данных сигнала несколькими программируемыми устройствами цифровой обработки сигналов программируемое устройство цифровой обработки сигналов, выполняющее обработку части каналов дальности, выдает данные на программируемое устройство цифровой обработки сигналов, выполняющее обработку всех элементов дальности одним из двух способов:

- данные с выхода устройства вывода LVDS 8 передающего устройства через один из двух каналов LVDS пересылаются на вход устройства ввода LVDS 4 принимающего устройства;

- данные из буфера обмена PCI 13 передающего устройства пересылаются по шине системного магистрального интерфейса CompactPCI в режиме прямого доступа к памяти (без участия модуля управляющего процессора) в буфер обмена PCI 13 принимающего устройства.

Программируемое устройство цифровой обработки сигналов, обрабатывающее все элементы дальности, пересылает результирующие данные через буфер обмена PCI 13 по шине системного магистрального интерфейса CompactPCI в память модуля управляющего процессора вычислительного комплекса.

Программируемое устройство цифровой обработки сигналов может обрабатывать данные за несколько периодов тактового импульса ТИ, соответствующих числу значений азимута антенны РЛС, с формированием радиолокационного изображения в координатах азимут-дальность, преобразованием его в сектор видеоизображения и выдачей данных под управлением контроллера шины PCI 1 через буфер обмена PCI 13 по шине системного магистрального интерфейса CompactPCI в режиме прямого доступа к памяти в видеопамять модуля графического контроллера вычислительного комплекса.

Расширение функциональных возможностей программируемого устройства цифровой обработки сигналов достигается использованием высокоскоростного последовательного интерфейса LVDS для ввода данных оцифрованных сигналов, наличием двух каналов ввода и двух каналов вывода данных LVDS, с возможностью резервирования одного из каналов ввода и вывода LVDS; параллельной обработкой данных принимаемого сигнала цифровыми сигнальными процессорами нескольких вычислительных устройств, возможностью резервирования, по крайней мере, одного вычислительного устройства; распределенной обработкой данных принимаемого сигнала несколькими ЦСП, возможностью загрузки в каждый ЦСП собственной программы и одновременного выполнения различных программных функций, включая быстрое преобразование Фурье, оптимальную фильтрацию сигнала и обработку изображений; возможностью использования в составе вычислительного комплекса нескольких программируемых устройств цифровой обработки сигналов, соединенных шиной системного магистрального интерфейса CompactPCI, обеспечивающей передачу данных промежуточных вычислений от одного программируемого устройства цифровой обработки сигналов к другому, и передачу результатов вычислений на модуль центрального процессора, и обработанных изображений на модуль графического контроллера вычислительного комплекса.

Повышение производительности программируемого устройства цифровой обработки сигналов обеспечивается вводом данных принимаемых сигналов по высокоскоростному последовательному интерфейсу LVDS; распределением потока принимаемых данных и их обработки между ЦСП нескольких вычислительных устройств; обменом данными через общее пространство памяти буфера обмена вычислительных устройств, при выполнении ЦСП единой программы обработки сигнала; возможностью распределенного выполнения обработки принимаемого сигнала несколькими программируемыми устройствами цифровой обработки сигналов в составе вычислительного комплекса РЛС.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОПРОЦЕССОРНОЕ УСТРОЙСТВО ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ | 2008 |

|

RU2399089C2 |

| УСТРОЙСТВО ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ | 2009 |

|

RU2402807C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2008 |

|

RU2399088C2 |

| ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2007 |

|

RU2344472C1 |

| Высокопроизводительная вычислительная платформа на базе процессоров с разнородной архитектурой | 2016 |

|

RU2635896C1 |

| УСТРОЙСТВО ПЕРВИЧНОЙ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2017 |

|

RU2653293C1 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2013 |

|

RU2547216C1 |

| Сложно-функциональный блок для СБИС типа система на кристалле | 2018 |

|

RU2691886C1 |

| МНОГОУРОВНЕВАЯ МНОГОПРОЦЕССОРНАЯ КОРАБЕЛЬНАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА | 2009 |

|

RU2406125C1 |

Изобретение относится к области вычислительной техники и может быть использовано для программной цифровой обработки сигналов в системах радиолокации, гидроакустики и связи. Технический результат заключается в расширении функциональных возможностей и повышении производительности программируемого устройства цифровой обработки сигналов за счет обеспечения ввода данных принимаемых сигналов по высокоскоростному последовательному интерфейсу LVDS, распределения потока принимаемых данных и их обработки между ЦСП нескольких вычислительных устройств. Устройство содержит соединенные между собой, по крайней мере, два вычислительных устройства, контроллер шины PCI, первое и второе устройства ввода LVDS, коммутатор каналов ввода-вывода LVDS, первое и второе устройства вывода LVDS, буфер ввода данных, буфер вывода данных и буфер обмена PCI для каждого вычислительного устройства, по крайней мере, один буфер обмена вычислительных устройств, а также постоянное запоминающее устройство, при этом вычислительное устройство содержит, по крайней мере, два цифровых сигнальных процессора, контроллер шины вычислительного устройства и оперативное запоминающее устройство. 1 ил.

Программируемое устройство цифровой обработки сигналов, содержащее, по крайней мере, два вычислительных устройства, отличающееся тем, что дополнительно содержит контроллер шины PCI, первое и второе устройства ввода LVDS, коммутатор каналов ввода-вывода LVDS, первое и второе устройства вывода LVDS, буфер ввода данных, буфер вывода данных и буфер обмена PCI для каждого вычислительного устройства, по крайней мере, один буфер обмена вычислительных устройств, а также постоянное запоминающее устройство, при этом вычислительное устройство содержит, по крайней мере, два цифровых сигнальных процессора, контроллер шины вычислительного устройства и оперативное запоминающее устройство, первый вход-выход контроллера шины PCI является входом-выходом шины системного магистрального интерфейса CompactPCI, второй вход-выход контроллера шины PCI соединен двунаправленной шиной управления с входом-выходом коммутатора каналов ввода-вывода LVDS и с третьим входом-выходом контроллера шины каждого вычислительного устройства, третий вход-выход контроллера шины PCI соединен двунаправленной шиной обмена данными с первым входом-выходом каждого буфера обмена PCI, входы первого и второго устройств ввода LVDS являются соответственно первым и вторым входами данных устройства, выходы первого и второго устройств ввода LVDS соединены соответственно с первым и вторым входами коммутатора каналов ввода-вывода LVDS, первый и второй выходы коммутатора каналов ввода-вывода LVDS соединены с входами первого и второго устройств вывода LVDS, выходы первого и второго устройств вывода LVDS являются соответственно первым и вторым выходами данных устройства, третий выход коммутатора каналов ввода-вывода LVDS соединен с входом каждого буфера ввода данных, третий вход коммутатора каналов ввода-вывода LVDS соединен с выходом каждого буфера вывода данных, вход первого буфера вывода данных, выход первого буфера ввода данных, и второй вход-выход первого буфера обмена PCI соединены первой двунаправленной шиной обмена данными со вторым входом-выходом контроллера шины одного вычислительного устройства, вход второго буфера вывода данных, выход второго буфера ввода данных, и второй вход-выход второго буфера обмена PCI соединены второй двунаправленной шиной обмена данными со вторым входом-выходом контроллера шины другого вычислительного устройства, входы-выходы цифровых сигнальных процессоров, вход-выход оперативного запоминающего устройства, первый вход-выход контроллера шины вычислительного устройства соединены шиной системного магистрального интерфейса вычислительного устройства, первый вход-выход буфера обмена вычислительных устройств соединен с шиной системного магистрального интерфейса одного вычислительного устройства, второй вход-выход буфера обмена вычислительных устройств соединен с шиной системного магистрального интерфейса другого вычислительного устройства.

| Процессор цифровой обработки сигналов | 1990 |

|

SU1837320A1 |

| Аппарат для постоянного воздействия на гнойные раны конечностей лекарственными растворами | 1947 |

|

SU72339A1 |

| Способ защиты масла от плесневения и прогоркания | 1949 |

|

SU86332A1 |

| CN 101086729 A, 12.12.2007 | |||

| WO 2005109232 A1, 17.11.2005. | |||

Авторы

Даты

2011-05-20—Публикация

2009-11-18—Подача