Область техники, к которой относится изобретение

Описанные здесь варианты осуществления обычно относятся к межсоединениям. В частности, описанные здесь варианты осуществления обычно относятся к перечислению и/или конфигурации устройств, соединенных межсоединениями.

Краткое описание чертежей

Изобретение может быть наилучшим образом понято при обращении к последующему описанию и сопроводительным чертежам, используемым для пояснения вариантов осуществления изобретения. На чертежах:

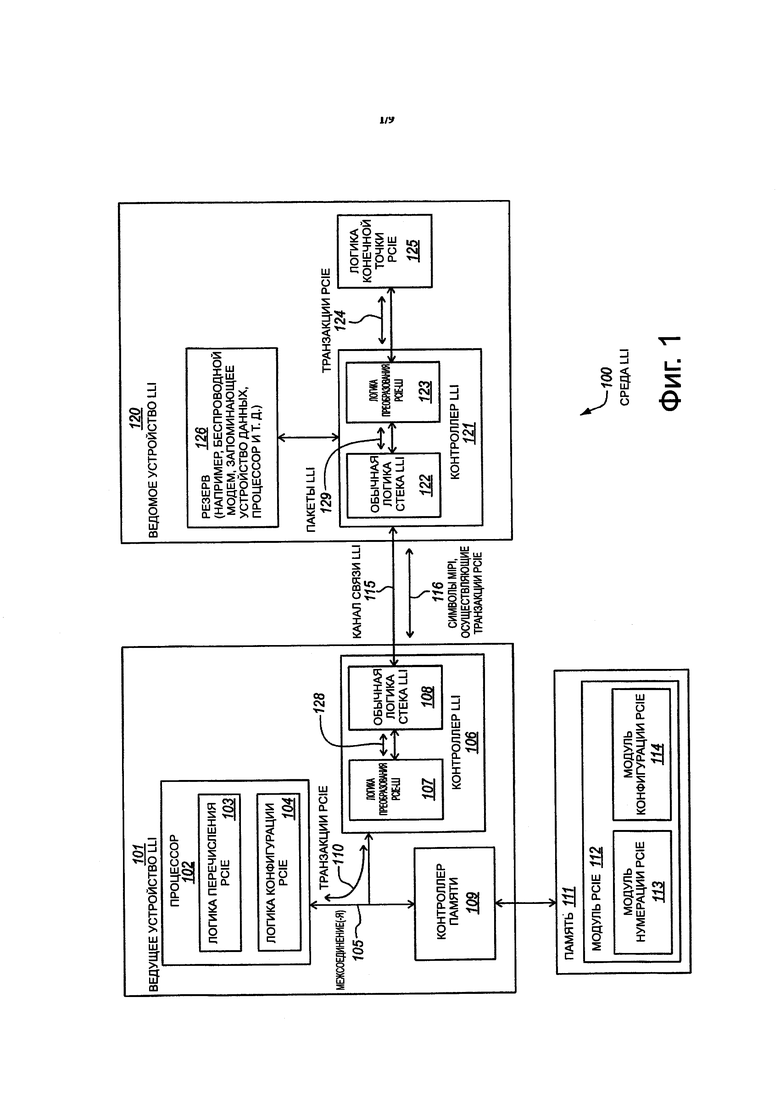

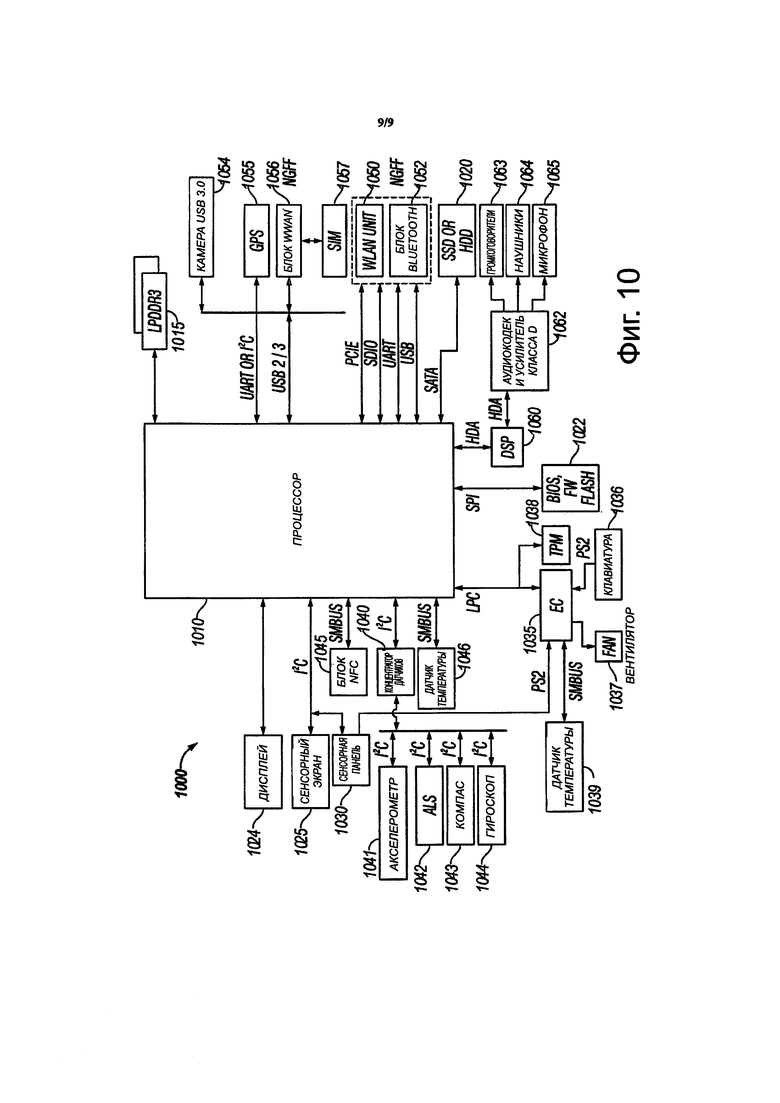

фиг. 1 - блок-схема варианта осуществления среды LLI, содержащей вариант осуществления ведущего устройства LLI, соединенного с вариантом осуществления ведомого устройства LLI посредством канала связи LLI;

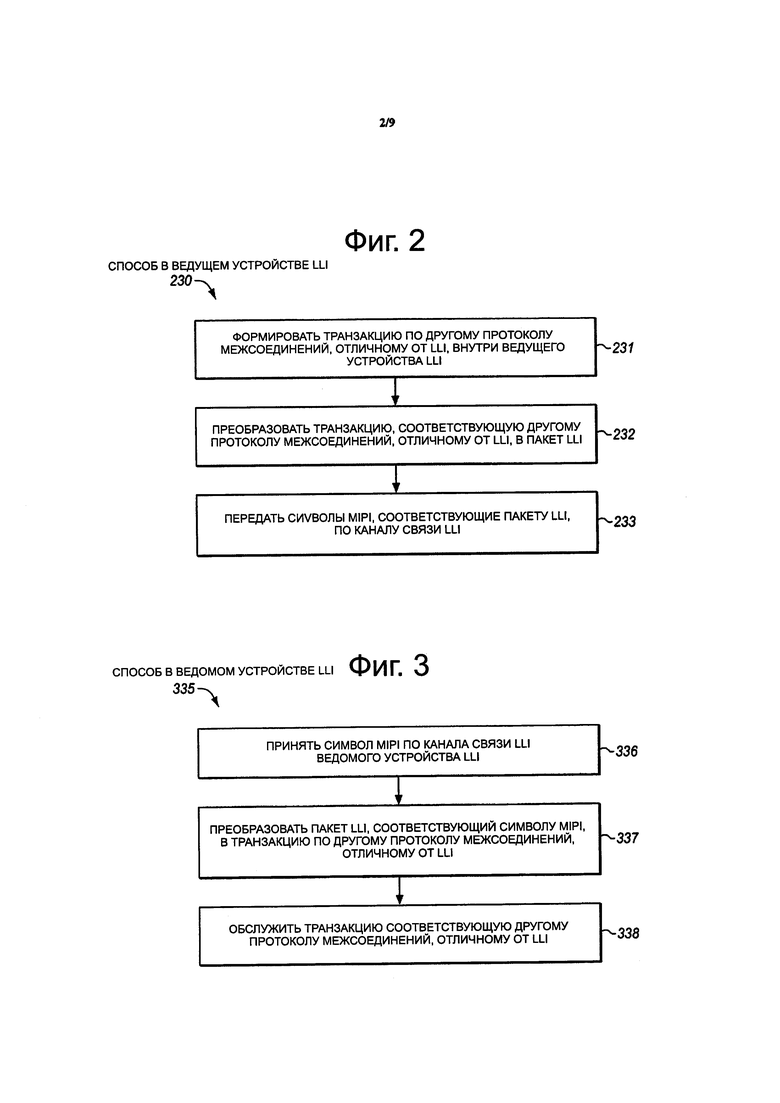

фиг. 2 - блок-схема последовательности выполнения операций варианта осуществления способа, который может выполняться ведущим устройством LLI;

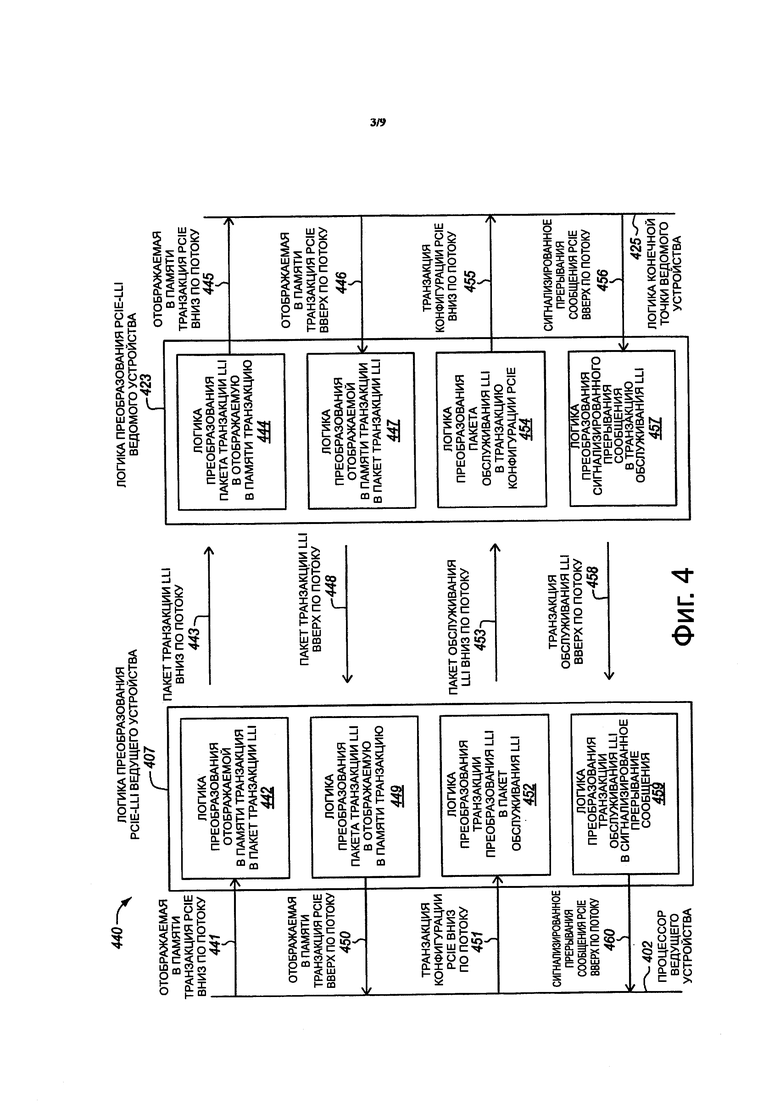

фиг. 3 - блок-схема последовательности выполнения операций варианта осуществления способа, который может выполняться ведомым устройством LLI;

фиг. 4 - блок-схема примерных вариантов осуществления соответствующих преобразований PCIE-LLI;

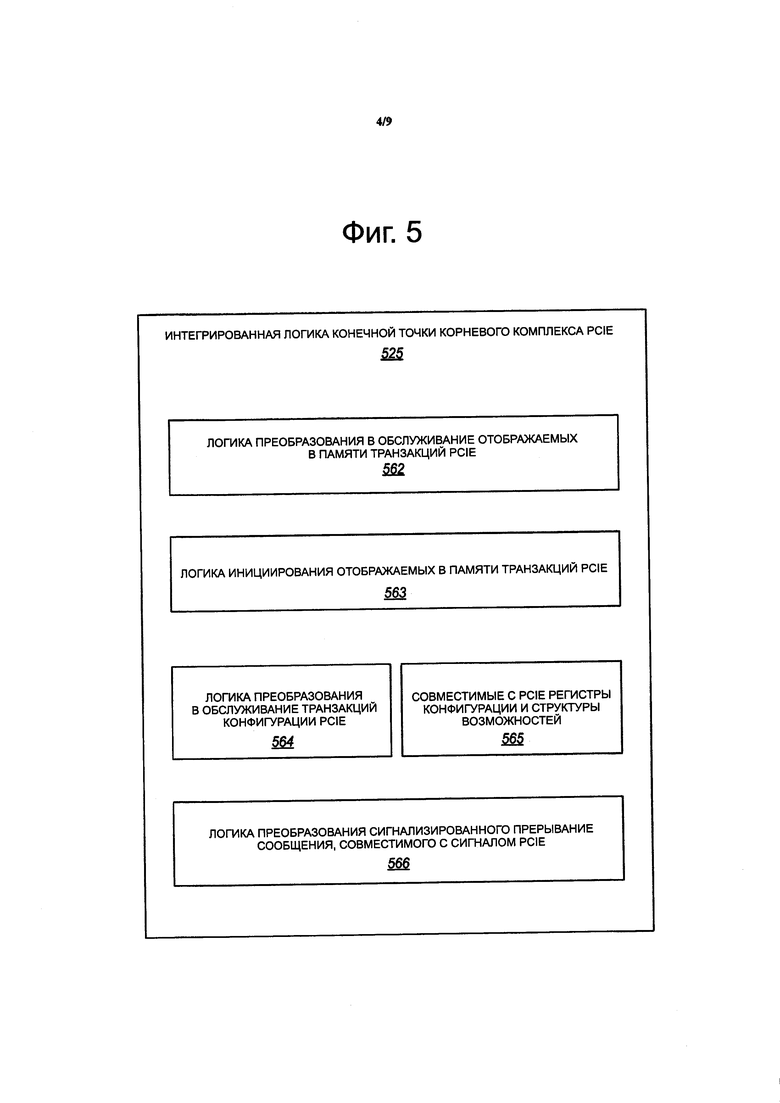

фиг. 5 - блок-схема варианта осуществления интегрированной логики локализации корневого комплекса PCIE;

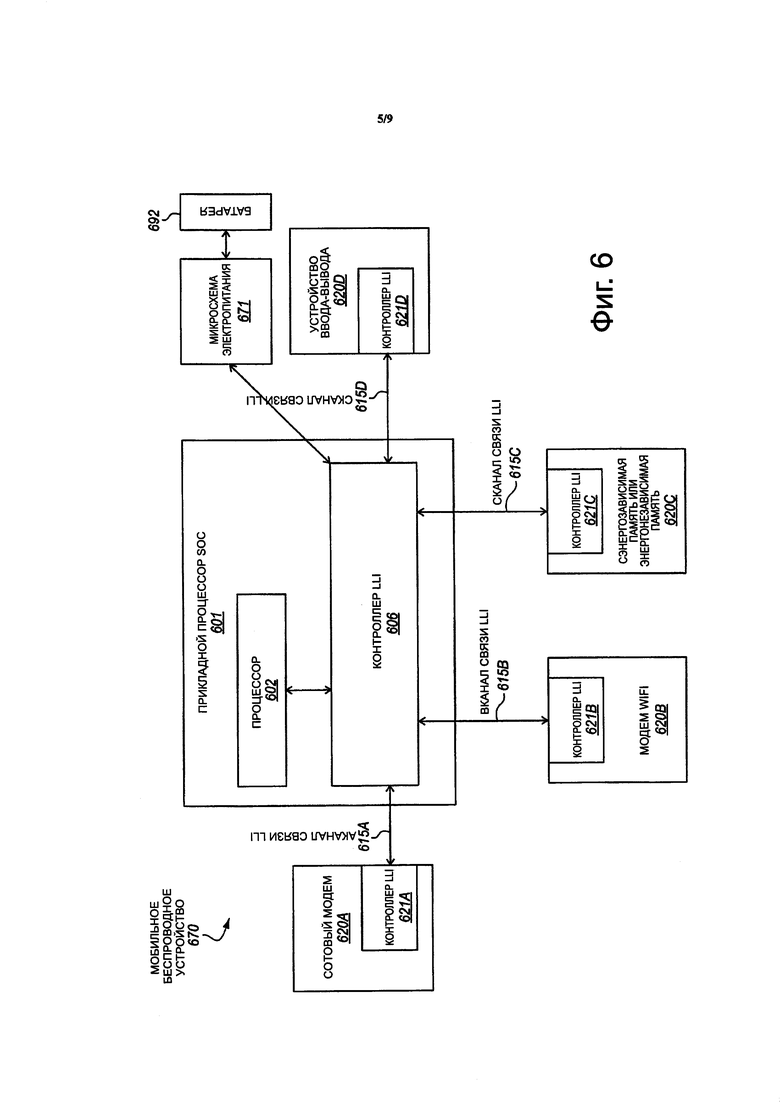

фиг. 6 - блок-схема варианта осуществления мобильного беспроводного устройства, в котором могут присутствовать варианты осуществления изобретения;

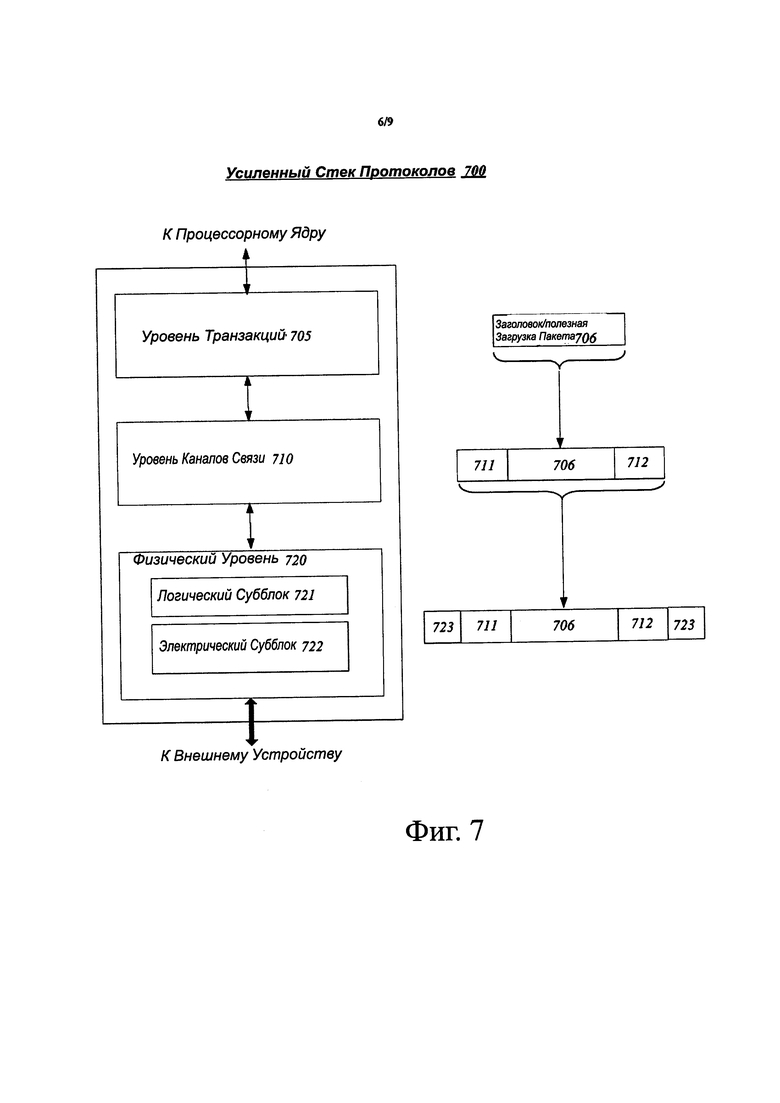

фиг. 7 - вариант осуществления архитектуры межсоединений, совместимой с PCIe, содержащей многоуровневый стек;

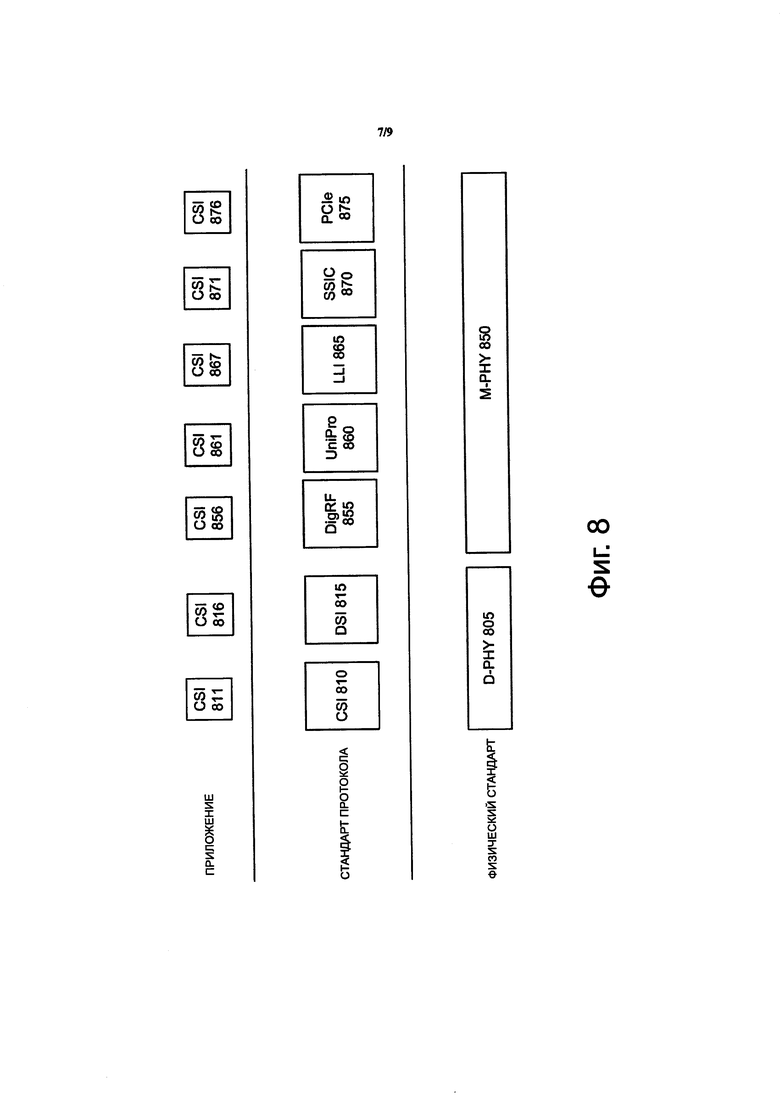

фиг. 8 - вариант осуществления различных протоколов, которые должны передаваться на различных физических уровнях архитектуры межсоединений;

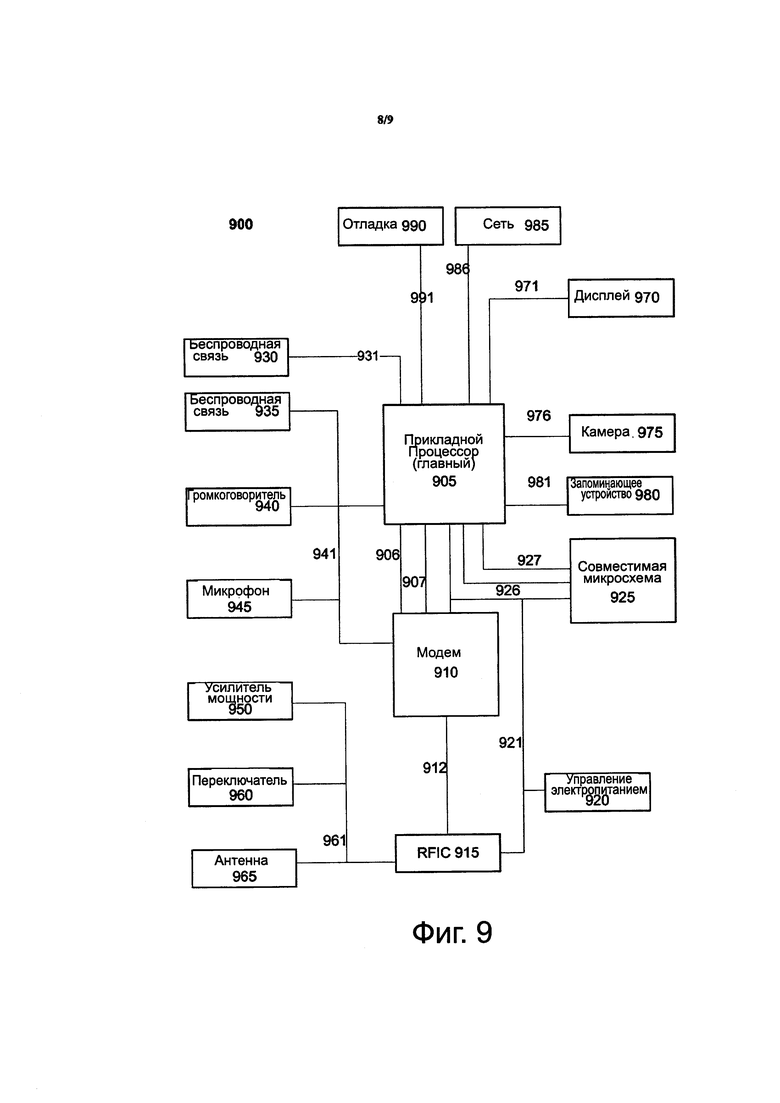

фиг. 9 - вариант осуществления низковольтной компьютерной платформы;

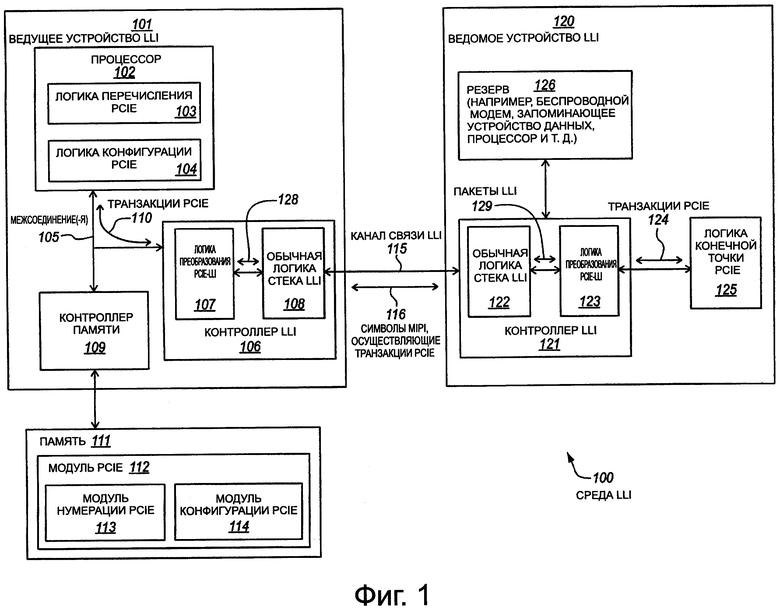

фиг. 10 - вариант осуществления блок-схемы компьютерной системы.

Подробное описание вариантов осуществления

Здесь раскрыты способы, устройства и системы для усиления механизма перечисления и/или конфигурации одного протокола межсоединений для другого протокола межсоединений. В последующем описании изложены многочисленные конкретные подробности (например, конкретные протоколы межсоединений, типы транзакций, типы преобразований транзакций, логические реализации, подробности логического разделения/интеграции, последовательности операций, типы и взаимосвязи системных компонент и т.п.). Однако, следует понимать, что варианты осуществления изобретения могут быть осуществлены на практике без этих конкретных деталей. В других случаях, известные схемы, структуры и технологии не показаны подробно, чтобы не мешать пониманию настоящего описания.

Альянс Mobile Industry Processor Interface (MIPI®) Alliance (Альянс по мобильным промышленным процессорным интерфейсам) является организацией с открытым членством, имеющей цель определения и способствование открытым техническим требованиям для интерфейсов внутри мобильных терминалов. Рабочая группа MIPI по интерфейсам с низкой задержкам (LLI) создала технические требования Альянса MIPI® для интерфейса с низкой задержкой (LLI). Для простоты эта спецификация здесь будет также упоминаться как MIPI LLI или просто LLI.

LLI является интерфейсом с низкой задержкой, разработанным для соединения устройств (например, мобильного устройства или терминала) на уровне межсоединений (например, посредством открытого протокола ядра (Open Core Protocol, ОСР), усовершенствованной архитектуры шины микроконтроллера (Advanced Microcontroller Bus Architecture, AMBA®), и т.д.), используя отображаемые в памяти транзакции. Канал связи LLI является двунаправленным интерфейсом, который позволяет любому из устройств инициировать транзакции. LLI является межсоединением типа "точка-точка", которое позволяет осуществлять связь устройствам на отдельных микросхемах, как если бы устройство, расположенное на удаленной микросхеме, находилось на локальной микросхеме. Спецификация LLI выражается как многоуровневый протокол на уровне транзакций, в котором цели и инициаторы, находящиеся на микросхемах, соединенных LLI, способны обмениваться транзакциями, по существу, без вмешательства программного обеспечения, что помогает добиться низкой задержки. LLI также обычно демонстрирует низкое потребление энергии, которое имеет тенденцию делать LLI пригодным для сотовых телефонов, планшетов и других мобильных устройств с батарейным питанием. Единственным ограничением для LLI является то, что в настоящее время он не имеет достаточного механизма, чтобы перечислять и конфигурировать устройства, присоединенные к звеньям связи LLI.

На фиг. 1 представлена блок-схема варианта осуществления среды 100 LLI, которая содержит вариант осуществления ведущего устройства 101 LLI, связанного с вариантом осуществления ведомого устройства 120 LLI каналом 115 связи LLI. Термины "ведущее устройство" и "ведомое устройство" используются для совместимости с техническими требованиями к LLI. Ведущее устройство может также представлять собой хост-устройство или просто первое устройство, а ведомое устройство может также представлять собой ведомое устройство или просто второе устройство. Ведущее устройство LLI может быть выполнено с возможностью управления ведомым устройством LLI. В некоторых вариантах осуществления ведущее и ведомое устройства LLI могут быть различными микросхемами, матрицей, интегральными схемами или потенциально разными упаковками.

Примеры подходящих ведущих устройств LLI содержат, в частности, микросхемы прикладных процессоров и системы прикладных процессоров на микросхемах (SoCs). Примерами соответствующих ведомых устройств LLI являются, в частности, микросхемы сопроцессоров, микросхемы беспроводных модемов (например, микросхемы сотовых модемов, микросхемы модемов беспроводной локальной сети (WLAN) и т.д.) и микросхемы запоминающего устройства данных (например, микросхемы флэш-памяти), если назвать несколько примеров. Как показано, ведомое устройство LLI может быть беспроводным модемом, устройством хранения данных, сопроцессором или другим ресурсом 126, который используется ведущим устройством LLI. Компоненты ведущего и ведомого устройств LLI могут отображаться в памяти, чтобы облегчить адресацию устройства. Ведущее устройство LLI может быть выполнено с возможностью управления всей картой системной памяти.

Ведущее устройство LLI содержит процессор 102, контроллер 106 LLI и контроллер 109 памяти. Процессор, контроллер LLI и контроллер памяти все связываются вместе друг с другом или как-либо иначе при осуществлении связи друг с другом с помощью одной или более шин или других межсоединений 105. Контроллер памяти связывается или соединяется с памятью 111. Контроллер 106 LLI связывается или соединяется с одним концом канала 115 связи LLI. Контроллер LLI выполнен с возможностью связи ведущего устройства с каналом связи LLI. Ведомое устройство 120 LLI также содержит контроллер 121 LLI, который связывается или соединяется с другим концом канала 115 связи LLI.

В некоторых вариантах осуществления механизм перечисления и/или конфигурации первого протокола межсоединений может быть усилен или использоваться повторно для второго, другого протокола межсоединений. В одном из вариантов второй протокол межсоединений может не иметь присущего ему механизма конфигурации и/или перечисления. В другом варианте второй протокол межсоединений может иметь механизм перечисления и/или конфигурации, но он может быть не настолько хорошим, обширным, всесторонним, хорошо разработанным, хорошо протестированным, гибким или быстрым как механизм первого протокола межсоединений. В еще одном другом варианте второй протокол межсоединений может иметь механизм перечисления и/или конфигурации, но по какой-то другой причине может быть желательным использовать механизм перечисления и/или конфигурации первого протокола (например, потому что он имеет особенность, отсутствующую в другом протоколе, с ним хорошо знакомы или он предпочтителен и т.д.).

Как дополнительно будет описано ниже, в некоторых вариантах осуществления, механизм перечисления и/или конфигурации межсоединения периферийных компонент (Peripheral Component Interconnect, PCI), экспресс-межсоединения периферийных компонент (Peripheral Component Interconnect Express, PCIE) или расширенного межсоединения периферийных компонент (Peripheral Component Interconnect extended, PCI-X) может быть усилен и/или использован повторно для MIPI LLI, хотя объем изобретения этим не ограничивается. В других вариантах осуществления механизм перечисления и/или конфигурации по другому интернет-протоколу, помимо PCI, PCIE или PCI-X, может быть усилен или использоваться повторно для LLI как, например, будущая версия PCI, PCIE, или PCI-X, производная версия PCI, PCIE, или PCI-X, протокол, связанный с PCI, PCIE или PCI-X, протокол, подобный PCI, PCIE или PCI-X, замена PCI, PCIE или PCI-X или протокол, имеющий возможности перечисления и/или конфигурации, сравнимые с PCI, PCIE или PCI-X. Альтернативно, как вариант, могут использоваться другие протоколы с возможностями перечисления и/или конфигурации, такие, как, например, протоколы универсальной последовательной шины (Universal Serial Bus, USB), другие протоколы, производные от USB или связанные с USB, или другие разработанные в будущем протоколы. Термины "протокол на основе межсоединений периферийных компонент", "протокол на основе PCI" и т.п., как они используются здесь, в совокупности упоминаются как PCI, PCIE, PCI-X и другие протоколы на основе PCI или производные от PCI. В других дополнительных вариантах осуществления, механизм перечисления и/или конфигурации PCI, PCI-X, PCIE или какой-либо другой протокол межсоединений, может быть усилен или повторно использоваться для протокола межсоединений, отличного от LLI (например, будущая версия или производный протокол LLI или другой протокол межсоединений, имеющий ограниченные возможности перечисления и/или конфигурации). В других вариантах осуществления вместо LLI могут использоваться протокол Unified Protocol (Unipro), digRF, SuperSpeed Inter-Chip (SSIC), или другие. В приведенных здесь вариантах осуществления PCIE часто используется в качестве примерного протокола, хотя следует понимать, что PCIE может альтернативно быть заменен PCI или PCI-X или USB или другим соответствующим протоколом межсоединений, имеющим механизм перечисления и конфигурации. Кроме того, в описанных ниже вариантах осуществления LLI часто используется в качестве примерного протокола, хотя следует понимать, что LLI может альтернативно быть заменен будущей версией LLI, производным протоколом LLI, протоколом, связанным с LLI, протоколом, подобным LLI или другим протоколом межсоединений, который может получить выгоду от усиления и/или повторного использования возможностей перечисления и конфигурации другого, отличного от них протокола межсоединений.

Обращаясь снова к фиг. 1, память 111 имеет модуль 112 PCIE. Альтернативно, память может иметь модуль другого протокола межсоединений, который отличается от LLI (например, PCI, PCI-X, протокол на основе PCI, USB, и т.д.). В некоторых вариантах осуществления модуль PCIE может быть выполнен с возможностью управления связью через шину PCIE. Шина PCIE не показана и реально это может быть не шина PCIE, как будет объяснено далее. Например, модуль PCIE может содержать драйвер шины PCIE, стек программного обеспечения PCIE или подобные функциональные возможности. В некоторых вариантах осуществления модуль PCIE может содержать по существу стандартный драйвер шины PCIE, стек программного обеспечения PCIE, или по меньшей мере участок в них, достаточный для выполнения перечисления и/или конфигурации, как описано здесь. Различные большие операционные системы обычно содержат стандартные драйверы шины PCIE и/или стеки программного обеспечения PCIE, пригодные для вариантов осуществления.

Стандартные драйверы шины PCIE и/или стеки программного обеспечения PCIE обычно имеют механизм перечисления и конфигурации устройств, подключенных к шинам PCIE. Показанный модуль имеет модуль 113 перечисления PCIE, который полезен для перечисления PCIE, чтобы перечислить одно или более ведомых устройств LLI ведущему устройству LLI. Например, модуль перечисления PCIE может содержать команды, управляющую программу, подпрограммы или процедуры, которые позволяют процессору раскрывать или обнаруживать устройства, присоединенные к шинам PCIE, раскрывать или обнаруживать возможности устройств, присоединенных к шинам PCIE, раскрывать или обнаруживать ресурсы, которые будут использовать устройства, присоединенные к шинам PCIE (например, сколько памяти будут использовать устройства), типы и количества поддерживаемых прерывателей, тип и количество функций в каждом устройстве и т.п. Показанный модуль PCIE также имеет модуль 114 конфигурации PCIE, полезный для конфигурации PCIE. Например, модуль конфигурации PCIE может содержать команды, управляющую программу, подпрограммы или процедуры, которые позволяют процессору конфигурировать устройства, присоединенные к шинам PCIE, например, конфигурируя диапазоны адресов памяти, конфигурируя векторы прерывания, модифицируя регистры конфигурации PCIE и/или структуры возможностей и т.д. Хотя были показаны отдельные модули перечисления и конфигурации PCIE, другие варианты осуществления могут объединять эти модули в единый модуль. В других вариантах осуществления модуль перечисления PCIE может содержаться без модуля конфигурации PCIE или модуль конфигурации PCIE может содержаться без модуля перечисления PCIE.

В некоторых вариантах осуществления модули перечисления 113 PCIE и модули 114 конфигурации PCIE могут быть, по существу, стандартными и могут быть полезны, чтобы выполнять, по существу, стандартные перечисление и конфигурацию. В некоторых вариантах осуществления ведущее устройство 101 LL1 может усиливать или повторно использовать, по существу, стандартные модули перечисления PCIE и/или модули конфигурации PCIE, чтобы выполнять перечисление и/или конфигурацию ведомого устройства 120 LLI 120 по каналу 115 связи LLI. В некоторых вариантах осуществления это может помочь избежать необходимости разрабатывать новые механизмы перечисления и/или конфигурации специально для LLI, что может помочь избежать или, по меньшей мере, сократить время и затраты на разработку. Кроме того, модули перечисление и конфигурации PCIE имеют тенденцию быть хорошо разработанными, протестированными и понятыми. Кроме того, они уже широко доступны через несколько больших операционных систем. Кроме того, PCIE использует стандартизированное механизмы перечисления и конфигурации. Использование таких стандартизированных механизмов может помочь избежать разработки специализированных и/или собственных механизмов перечисления и/или механизмов конфигурации, которые могут иметь тенденцию снижать функциональную совместимость устройства.

Обращаясь опять к фиг. 1, процессор 102 может исполнять команды модуля 113 перечисления PCIE и/или модуля 114 конфигурации PCIE (например, как часть операционной системы, исполняемой на процессоре), которые могут конфигурировать процессор, чтобы иметь модуль/механизм/логику 103 перечисления PCIE и/или модуль/механизм/логику 104 конфигурации PCIE, соответственно. В некоторых вариантах осуществления это может заставить процессор формировать и обеспечивать транзакцию 110, основанную на PCIE или PCI. То есть, процессор может формировать и представлять транзакцию, имеющую протокол межсоединений, отличный от LLI. Модуль/механизм/логика перечисления PCIE и/или модуль/механизм/логика конфигурации PCIE могут обеспечить транзакции 110 на основе PCIE или PCI контроллеру 106 LLI ведущего устройства LLI через одно или более межсоединений 105.

Контроллер LLI содержит вариант осуществления логики 107 преобразования PCIE-LLI, который связан с процессором 102. В другом варианте осуществления логика 107 преобразования PCIE-LLI может быть отдельной от контроллера 106 LLI, но быть связанной с контроллером 106 LLI (например, связанной или логически расположенной между контроллером LLI и процессором). Логика 107 преобразования PCIE-LLI может принимать транзакции 110 PCIE. В некоторых вариантах осуществления логика 107 преобразования PCIE-LLI может быть выполнена с возможностью осуществления преобразований PCIE-LLI и преобразований LLI-PCIE. Альтернативно, логика преобразования PCI-LLI может содержаться для преобразования между PCI (или другим протоколом на основе PCI) и LLI или может содержаться другая логика для преобразования между LLI и другим протоколом межсоединений, помимо LLI. Логика 107 преобразования PCIE-LLI может быть выполнена с возможностью преобразования принятых транзакций 110 PCIE в соответствующие транзакции LLI, пакеты или форматы 128 данных, совместимые с LLI, которые реализуют или представляют транзакции ПО PCIE. В некоторых вариантах осуществления преобразование может содержать отображение разрядов или полей транзакций PCIE в соответствующие биты или поля пакетов LLI или совместимых с LLI форматов данных. Конкретные примеры того, как это может быть сделано, будут описаны здесь далее. Логика преобразования PCIE-LLI может затем обеспечить пакеты LLI или другие форматы 128 данных LLI, совместимые со связанной логикой 108 стеков LLI. В некоторых вариантах осуществления логика стеков LLI может, как вариант, представлять, по существу, стандартный стек LLI, который содержит уровень транзакции, уровень канала передачи данных, уровень адаптера PHY и один или более M-PHY. В некоторых вариантах осуществления логика преобразования PCIE-LLI может быть выполнена с возможностью обеспечения транзакций LLI, которые она формирует на уровне транзакций логики 108 стека LLI. Логика стека LLI может преобразовывать принятые пакеты LLI в соответствующие символы MIPI и затем M-PHY логики 108 стеков LLI и/или контроллер LLI 106 может передавать символы 116 MIPI полученные из пакетов 128 LLI), которые реализуют или представляют транзакции 110 PCIE, по линии 115 связи LLI. Соответственно, в некоторых вариантах осуществления транзакции PCIE, используемые для перечисления и/или конфигурации, могут быть переданы по линии связи LLI как символы MIPI, которые были получены из пакетов LLI.

Ведомое устройство 120 LLI содержит контроллер 121 LLI. Контроллер LLI соединяется с другим противоположным концом канала 115 связи LLI и выполнен с возможностью соединения ведомого устройства LLI с каналом связи LLI. Контроллер 121 LLI содержит логику 122 стека LLI. В некоторых вариантах осуществления логика 122 стека LLI может дополнительно представлять, по существу, стандартный стек LLI, который содержит уровень транзакций, уровень канала передачи данных, уровень адаптера PHY и один или более M-PHY. M-PHY логики 122 стека LLI могут принимать от канала 112 связи LLI символы MIPI (полученные из пакетов 128 LLI), которые осуществляют или представляют транзакции 110 PCIE. Логика 122 стека LLI может обрабатывать символы MIPI и формировать транзакции LLI, пакеты или другие форматы 129 данных, совместимые с LLI. Уровень транзакции логики 122 стека LLI может обеспечивать транзакции LLI или пакеты 129 для варианта осуществления логики 123 преобразования PCIE-LLI. Альтернативно, транзакции LLI или пакеты могут предоставляться для логики преобразования PCI-LLI или для логики, чтобы проводить преобразование между протоколом LLI и другим протоколом межсоединений помимо LLI, отличным от PCI и PCIE.

На чертеже логика 123 преобразования PCIE-LLI является частью контроллера 121 LL1. В другом варианте осуществления логика 123 преобразования PCIE-LLI может быть отдельной от контроллера 121 LLI 121, но связанной с контроллером 121 LLI 121 (например, связанной или логически расположенной между контроллером LLI и вариантом осуществления логики 125 конечной точки PCIE). Логика 123 преобразования PCIE-LLI 123 выполнена с возможностью осуществления преобразований PCIE-LLI и преобразований LLI-PCIE. Альтернативно, другие преобразования на основе PCI или другие преобразования могут быть выполнены как описано здесь в другом месте. Логика преобразования PCIE-LLI может преобразовывать принятые транзакции LLI или пакеты 129, которые реализуют или представляют транзакции PCIE 110, в соответствующие транзакции 124 PCIE. В некоторых вариантах осуществления преобразование может содержать отображение разрядов или полей пакетов LLI, чтобы приспособить соответствующие разряды или поля транзакций PCIE. Конкретные примеры таких преобразований будут дополнительно обсуждены ниже.

Логика 123 преобразования PCIE-LLI связана с вариантом осуществления логики 125 конечной точки PCIE 125. Альтернативно, вместо логика конечной точки PCIE может использоваться логика конечной точки PCI или может использоваться логика конечной точки другого протокола межсоединений, помимо LLI, PCI, и PCIE. Логика 123 преобразования PCIE-LLI может обеспечить транзакции 124 PCIE, она формирует логику 125 конечной точки PCIE. В некоторых вариантах осуществления транзакции 124 PCIE 124, обеспечиваемые для логики конечной точки PCIE, могут быть идентичными или, по меньшей мере, по существу, идентичными транзакциям 110 PCIE, первоначально обеспечиваемым от процессора 101 (например, биты в полях пакета транзакции 124 PCIE могут быть идентичны битам в полях пакета транзакции 110 PCIE). В некоторых вариантах осуществления логики конечной точки PCIE может иметь настолько большую логику PCIE, какой она может быть у нормального устройство PCIE, соединенного с шиной PCIE. Альтернативно, логика конечной точки PCIE может иметь, по меньшей мере, так много логики PCIE, сколько необходимо для поддержания желаемых перечисления и/или конфигурации, требующихся для конкретного варианта осуществления. Для примера, в некоторых вариантах осуществления логика конечной точки PCIE может содержать регистры конфигурации, совместимые с PCIE, (или другие, основанные на PCI) (например, индексные регистры PCIE и т.д.), и структуры возможностей, которые могут быть выполнены с возможностью использования описанных здесь вариантов осуществления. В качестве другого примера, в некоторых вариантах осуществления логика конечной точки PCIE может содержать логику обслуживания/реализации отображаемых в памяти транзакций и/или логику обслуживания/реализации транзакций конфигурации PCIE. В некоторых вариантах осуществления, логика конечной точки PCIE может быть введена в ведомое устройство LLI даже при том, что ведомому устройству LLI не обязательно иметь шины PCIE и/или логика конечной точки PCIE не обязательно должна быть связана с шиной PCIE.

В некоторых вариантах осуществления логика конечной точки PCIE может представить интегрированную логику конечной точки корневого комплекса PCIE. В PCIE ведущее устройство также иногда упоминается как интегрированное устройство корневого комплекса. Удаленное устройство иногда упоминается как конечная точка или конечная точка корневого комплекса. Исторически, в PCI ведущее устройство и удаленное устройство были разными микросхемами, установленными на печатной плате. PCIE также позволяет устройству конечной точки интегрироваться на микросхему или на матрицу с устройством корневого комплекса вместо того, чтобы находиться на отдельной удаленной микросхеме. Такое интегрированное устройство также иногда упоминается в технике как интегрированное устройство конечной точки корневого комплекса. Устройство корневого комплекса и интегрированное устройство конечной точки корневого комплекса интегрируются вместе на микросхеме или на матрице. В случае интегрированной логики конечной точки корневого комплекса PCIE процессор ведущего устройства может даже не знать или не быть осведомленным о вступлении в процесс канала связи LLI, а скорее может осуществлять связь с интегрированным устройством конечной точки корневого комплекса, как если бы оно был интегрирован процессором на микросхему или на матрицу.

В некоторых вариантах осуществления транзакции 110 PCIE и/или транзакции 124 PCIE могут использоваться для перечисления и/или конфигурации ведомого устройства 120 LLI. В случае конфигурации, транзакции 124 PCIE могут быть выполнены с возможностью модификации регистров конфигурации и/или структур возможностей на основе PCIE (или других на основе PCI) ведомого устройства. В некоторых вариантах осуществления, например, в случае некоторого перечисления, транзакции 124 PCIE могут вызывать или приводить в результате к логике конечной точки PCIE, формирующей ответные транзакции 124 PCIE 124 в обратном направлении, которые должны передаваться ведущему устройству LLI. Эти транзакции 124 PCIE могут предоставляться контроллеру 121 LLI ведомым устройством, передаваться логикой стека LLI как символы MIPI по каналу связи 115 связи LLI, приниматься как символы MIPI стеком LLI контроллера 106 LLI ведущего устройства, эффективно переходить на обратное направление к описанному ранее. Логика 123 преобразования PCIE-LLI ведомого устройства может преобразовать пакеты PCIE или транзакции 124 в соответствующие пакеты LLI. Символы 116 MIPI, которые осуществляют или представляют транзакции 124 PCIE, могут передаваться по каналу связи LLL Логика 107 преобразования PCIE-LLI ведущего устройства может преобразовывать пакеты LLI, восстановленные из этих символов MIPI, полученных через канал связи LLI, в соответствующие транзакции 110 PCIE 110. Эти транзакции 110 PCIE могут быть идентичными или, по меньшей мере, по существу, идентичными (например, функционально эквивалентными) первоначально посланным транзакциям 124 PCIE.

На фиг. 2 представлена блок-схема последовательности выполнения операций варианта осуществления способа 230, который может выполняться ведущим устройством LLI. В некоторых вариантах осуществления операции и/или способ, показанные на фиг. 2, могут выполняться ведущим устройством 101 LL1 или внутри ведущего устройства 101 LL1, показанного на фиг. 1. Компоненты, признаки и конкретные необязательные детали, описанные здесь для ведущего устройства 101 LL1, также необязательно применяются к операциям и/или способу 230, которые могут выполняться в вариантах осуществления и/или в рамках ведущего устройства 101 LLI. Альтернативно, операции и/или способ, показанные на фиг. 2, могут выполняться аналогичным и/или полностью другим ведущим устройством LLI, чем то, которое показано на фиг. 1. Кроме того, ведущее устройство LLI, показанное на фиг. 1, может выполнять операции и/или способы точно также, подобно или полностью иначе, чем на фиг. 2.

Способ содержит формирование в блоке 231 транзакции, выполненной по протоколу, отличному от LLI, внутри ведущего устройства LLI. В некоторых вариантах осуществления транзакций может выполняться по протоколу PCI, протоколу PCIE, другому протоколу на основе PCI или другому протоколу, отличному от LLI. В некоторых вариантах осуществления транзакция может быть частью по меньшей мере перечисления ведомого устройства LLI, связанного с каналом связи LLI, или и конфигурации ведомого устройства LLI, связанного с каналом связи LLI.

Способ содержит преобразование в блоке 232 транзакции, которая выполнена по протоколу межсоединений, отличному от LLI, в пакет LLI или транзакцию. В некоторых вариантах осуществления пакет LLI может осуществлять или представлять сформированную транзакцию на основе PCI. В некоторых вариантах осуществления преобразование может содержать отображение битов или полей сформированной транзакции на основе PCI, в соответствующие биты или поля пакета LLI. В некоторых вариантах осуществления пакет LLI может обеспечиваться для уровня транзакций необязательно стандартного стека LLI.

Способ также содержит передачу в блоке 233 символов MIPI, полученных из пакета LLI через канал связи LLI. В некоторых вариантах осуществления символы MIPI могут осуществляться или представляться и могут использоваться, чтобы передавать первоначально сформированную транзакцию на основе PCI или другую транзакцию, выполненную по протоколу межсоединений, отличному от LLI.

На фиг. 3 представлена блок-схема последовательности выполнения операций варианта осуществления способа 335, который может выполняться ведомым устройством LLI. В некоторых вариантах осуществления операции и/или способ, показанные на фиг. 3, могут выполняться ведомым устройством 120 LLI, показанным на фиг. 1, или внутри него. Компоненты, признаки и конкретные необязательные подробности, описанные здесь для ведомого устройства 120 LL1 также необязательно применяются к операциям и/или к способу 335, который в вариантах осуществления может выполняться ведомым устройством 120 LLI или внутри него. Альтернативно, операции и/или способ, показанные на фиг. 3, могут быть выполнены подобным или полностью другим ведомым устройством LLI, чем то, которое показано на фиг. 1, или внутри него. Кроме того, ведомое устройство LLI, показанное на фиг. 1, может выполнить операции и/или способы, такие же, подобные, или полностью отличающиеся от тех, которые показаны на фиг. 2.

Способ содержит прием в блоке 336 символа MIPI, который был получен из пакета LLI, по каналу связи LLI ведомого устройства LLI. В некоторых вариантах осуществления принятый символ MIPI может осуществлять или представлять и может использоваться для передачи транзакции, выполненной по протоколу на основе PCI или другому протоколу межсоединений, отличному от LLI.

Способ содержит в блоке 337 преобразование пакета LLI, который соответствует и/или получен из принятого символа MIPI, в транзакцию, которая имеет другой протокол межсоединений, отличный от LLI. В некоторых вариантах осуществления пакет LLI может быть преобразован в транзакцию по протоколу PCI, по протоколу PCIE или другому протоколу, отличному от LLI. В некоторых вариантах осуществления преобразование может содержать отображение битов или полей пакета LLI в соответствующие биты или поля транзакции.

Способ содержит в блоке 338 обслуживание транзакции, которая выполнена по протоколу межсоединений, отличному от LLI. В некоторых вариантах осуществления транзакция может обслуживаться логикой конечной точки PCI или логикой конечной точки PCIE. В некоторых вариантах осуществления, обслуживание транзакции может выполняться в сочетании по меньшей мере с конфигурированием ведомого устройства LLI или перечислением ведомого устройства LLI ведущему устройству LLI.

На фиг. 2-3 показаны способы, в которых ведущее устройство формирует транзакции и передает символы, представляющие эти транзакции, ведомому устройству. Альтернативно, как упоминалось ранее, рассматриваются также аналоговые обратные способы, в которых ведомое устройство формирует транзакции и передает символы, представляющие эти транзакции, ведущему устройству. В некоторых вариантах осуществления это может делаться, по существу, как описано выше для фиг. 1.

На фиг. 4 представлена блок-схема примерных вариантов осуществления примера соответствующих преобразований 440 PCIE-LLI. Показаны вариант осуществления логики 407 преобразования PCIE-LLI ведущего устройства и вариант осуществления логики 423 преобразования PCIE-LLI ведомого устройства. В некоторых вариантах осуществления логика 407 преобразования PCIE-LLI ведущего устройства и/или логика 423 преобразования PCIE-LLI ведомого устройства, показанные на фиг. 4, соответственно, могут быть введены в ведущее устройство 101 LLI и/или в ведомое устройство 120 LLI, показанные на фиг. 1. Альтернативно, логика 407 преобразования PCIE-LLI ведущего устройства и/или логика 423 преобразования PCIE-LLI ведомого устройства 423, показанных на фиг. 4, соответственно, может быть введена в подобные или разные ведущие и ведомые устройства LLI, отличные от показанных на фиг. 1. Кроме того, ведущее устройство 101 LLI и/или ведомое устройство 120, показанные на фиг. 1, могут быть подобны или отличаться от другой логики преобразования PCIE-LLI, показанной на фиг. 4.

Процессор 402 ведущего устройства может передавать отображаемую в памяти транзакцию 441 в нисходящем потоке дальше в транзакцию, отображаемую в памяти, логике 442 преобразования пакета транзакций LLI логики преобразования PCIE-LLI ведущего устройства. Термин "в нисходящем потоке" используется здесь как относящийся к направлению от ведущего устройства к ведомому устройству. Напротив, термин "в восходящем потоке" используется здесь как относящийся к направлению от ведомого устройства к ведущему устройству. Логика 442 преобразования может быть выполнена с возможностью преобразования отображаемой в памяти транзакции 441 нисходящего потока в соответствующий пакет 443 транзакции LLI нисходящего потока. Пакет 443 транзакции LLI нисходящего потока может передаваться логике 423 преобразования PCIE-LLI ведомого устройства.

Пакет транзакции LLI в логике 444 преобразования отображаемой в памяти транзакции логики преобразования PCIE-LLI ведомого устройства может принимать в нисходящем потоке пакет 443 транзакции LLI. Логика 444 преобразования может быть выполнена с возможностью преобразования пакета 443 транзакции LLI нисходящего потока в соответствующую отображаемую в памяти транзакцию 445 в нисходящем потоке. Отображаемая в памяти транзакция 445 нисходящего потока может передаваться логике 425 конечной точки PCIE ведомого устройства.

Логика 425 конечной точки PCIE ведомого устройства может передавать отображаемую в памяти транзакцию 446 в восходящем потоке в направлении отображаемой в памяти транзакции в логику 447 преобразования пакета транзакции LLI логики преобразования PCIE-LLI ведомого устройства. Логика преобразования 447 может быть выполнена с возможностью преобразования отображаемой в памяти транзакции 446 в восходящем потоке в соответствующий пакет 448 транзакции LLI 448в восходящем потоке. Пакет 448 транзакции LLI в восходящем потоке может быть передан в направлении логики преобразования PCIE-LLI ведущего устройства.

Логика 449 преобразования пакета транзакции LLI в отображаемую в памяти транзакцию логики преобразования PCIE-LLI ведущего устройства может принимать пакет 448 транзакции LLI в восходящем потоке. Логика 449 преобразования может быть выполнена с возможностью преобразования пакета 448 транзакции LLI в восходящем потоке в соответствующую отображаемую в памяти транзакцию 450 в восходящем потоке. Отображаемая в памяти транзакция 450 в восходящем потоке может быть передана процессору 402 ведущего устройства.

Процессор 402 ведущего устройства может передавать в нисходящем потоке транзакцию 451 конфигурации PCIE в направлении транзакции конфигурации PCIE в логику 452 преобразования пакета обслуживания LLI логики преобразования PCIE-LLI ведущего устройства. LLI в настоящий момент не поддерживает транзакции конфигурации. В некоторых вариантах осуществления транзакции конфигурации PCIE могут отображаться в пакеты обслуживания LLI, которые могут передаваться по каналу связи LLI. Логика 452 преобразования может быть выполнена с возможностью преобразования транзакции 451 конфигурации PCIE в нисходящем потоке в соответствующий пакет 453 обслуживания LLI в нисходящем потоке. Пакет 453 обслуживания LLI в нисходящем потоке может быть передан в направлении логики преобразования PCIE-LLI ведомого устройства.

Логика 454 преобразования пакета обслуживания LLI в транзакцию конфигурации PCIE логики преобразования PCIE-LLI ведомого устройства может принять пакет 453 обслуживания LLI в нисходящем потоке. Логика 454 преобразования может быть выполнена с возможностью преобразования пакета 453 обслуживания LLI в нисходящем потоке в соответствующую транзакцию 455 конфигурации PCIE в нисходящем потоке. Транзакция 455 конфигурации PCIE в нисходящем потоке может быть передана в направлении логики 425 конечной точки PCIE ведомого устройства.

Логика 425 конечной точки PCIE ведомого устройства может передавать сообщенное прерывание 456 сообщения в восходящем потоке в направлении сообщенного прерывания сообщения логике 457 преобразования транзакции обслуживания LLI логики преобразования PCIE-LLI ведомого устройства. Логика 457 преобразования может быть выполнена с возможностью преобразования сообщенного прерывания 456 сообщения в восходящем потоке в соответствующий пакет 458 обслуживания LLI в восходящем потоке. Пакет 458 обслуживания LLI в восходящем потоке может быть передан в направлении логики преобразования PCIE-LLI ведущего устройства.

Транзакция обслуживания LLI в логику 459 преобразования сообщенного прерывания сообщения логики преобразования PCIE-LLI ведущего устройства может принять транзакцию 458 обслуживания LLI в восходящем потоке. Логика 459 преобразования может быть выполнена с возможностью преобразования транзакции 458 обслуживания LLI в восходящем потоке в соответствующее сообщенное прерывание 460 сообщения в восходящем потоке. Сообщенное прерывание 460 сообщения в восходящем потоке может быть передано в направлении процессора 402 ведущего устройства.

Чтобы дополнительно проиллюстрировать, как транзакции PCIE могут быть преобразованы в пакеты уровня транзакции LLI, может быть полезным рассмотреть несколько иллюстративных примеров. Отображаемые в памяти считывания и другие отображаемые в памяти транзакции могут не иметь полезной загрузки данных. В таких случаях большинство полей пакета LLI (например, 73-разрядного пакета запроса команды LLI) может быть заполнено, основываясь на соответствующих полях транзакции PCIE (например, 48-разрядный формат заголовка запроса PCIE). Например, поля адреса и длины транзакции PCIE могут отображаться напрямую в соответствующие поля длины и адреса уровня транзакции LLI. Другие поля, такие как поля Requester ID (идентификатор запрашивающей стороны, Tag (тег) и BE, могут устанавливаться статически. Другие поля, такие как атрибуты памяти, могут быть посланы как часть последовательных полей. Теперь рассмотрим отображаемые в памяти записи или другие отображаемые в памяти транзакции, имеющие полезную загрузку данных. Транзакция запроса записи PCIE может быть преобразована в пакет запроса команды LLI как описано непосредственно перед этим. Дополнительно, каждый 64 бита полезной нагрузки данных PCIE могут быть преобразованы в пакет запроса данных записи LLI. Подобный подход может использоваться для реакций считывания. Теперь рассмотрим транзакции конфигурации PCIE. Транзакция конфигурации PCIE (например, 48-разрядная транзакция запроса конфигурации PCIE) может быть преобразована в пакет обслуживания LLI (например, 73-разрядный пакет запроса адреса записи обслуживания LLI). Определенные поля, такие как числовые поля Requester ID, Tag, Bus/Dev/Fn, могут быть установлены статически. Номер регистра может быть послан как часть адреса. Другие поля, если нужно, могут быть посланы как часть неиспользованного адресного поля.

На фиг. 5 представлена блок-схема варианта осуществления интегрированной логики 525 конечной точки корневого комплекса PCIE. В некоторых вариантах осуществления логика 525 конечной точки, показанная на фиг. 5, может вводиться в ведомое устройство 120 LLI, показанное на фиг. 1. Альтернативно, логика 525 конечной точки может быть введена в подобное или совершенно отличное от показанного на фиг. 1 ведомое устройство LLI. Кроме того, ведомое устройство LLI, показанное на фиг. 1, может содержать ту же самую, подобную или полностью отличающуюся логику конечной точки по сравнению с фиг. 5.

Логика конечной точки содержит логику в отображаемых в памяти транзакциях 562 обслуживания PCIE и логику для инициирования отображаемых в памяти транзакций 563 PCIE. Логика конечной точки также содержит логику в транзакциях 564 конфигурации PCIE и регистрах конфигурации, совместимых с PCIE, и структурах 565 возможностей. Логика конечной точки также содержит логику, чтобы сигнализировать о сигнализированных прерываниях 566 сообщений, совместимых с PCIE. В некоторых вариантах осуществления каждая из этих логик может быть подобной, по существу, такой же или такой же логикой в стандартной интегрированной логике конечной точки Root-Complex PCIE. В некоторых вариантах осуществления ведомое устройство LLI, в котором содержится логика конечной точки, может не иметь шины PCIE, и/или логика конечной точки может быть не связана или не осуществлять связь с шиной PCIE, даже если она имеется.

На фиг. 6 представлена блок-схема варианта осуществления мобильного беспроводного устройства 670, в которое могут быть внедрены варианты осуществления изобретения. В различных вариантах осуществления мобильное беспроводное устройство может содержать ноутбук, планшет, смартфон, сотовый телефон, цифровой аудиоплеер, или другое мобильное беспроводное устройство, известное в технике. В некоторых вариантах осуществления ведущее и/или ведомое устройства LLI, показанные на фиг. 1, могут содержаться в мобильном беспроводном устройстве, показанном на фиг. 6. Альтернативно, ведущее и/или ведомое устройства LLI, показанные на фиг. 1, могут содержаться в устройстве, подобном или совершенно отличном от показанного на фиг. 6. Кроме того, устройство, показанное на фиг. 6, может содержать те же самые, подобные, или совершенно другие ведущие и/или ведомые устройства LLI со сравнению с фиг. 1.

Мобильное беспроводное устройство содержит систему прикладного процессора на микросхеме (SoC) 601. SoC имеет процессор 602 и контроллер 606 LLC. SoC может содержать вариант осуществления логики преобразования как раскрыто здесь в другом месте. Сотовый модем 620А, имеющий антенну, имеет также контроллер 621A LLI, связанный с контроллером 606 LLC каналом 615А связи LLI. Модем 620 В WiFi, имеющий антенну, также имеет контроллер 621 В LLI, связанный с контроллером 606 LLC 606 каналом 615 В связи LLI. В некоторых, но не во всех беспроводных устройствах используются дипольные антенны. Энергозависимая или энергонезависимая память 620С имеет контроллер LLI 621С, связанный с контроллером 606 LLC каналом 615С связи LLI. Одним из примеров энергозависимой памяти, содержащимся в некоторых, но не во всех устройствах, является динамическая оперативная память (DRAM). Одним из примеров долговременной памяти, содержащимся в некоторых, но не во всех устройствах, является флэш-память. Устройство 620D ввода/вывода (I/O) имеет контроллер 621D LLI, связанный с контроллером 606 LLC каналом 615D связи. Несколькими примерами соответствующих устройств ввода-вывода являются, в частности, громкоговоритель или другие устройства аудиовыхода, выход на клавиатуру, выход на дисплей, ввод с помощью сенсорного экрана, выход на вибропреобразователь и т.п. Любой сотовый модем, модем WiFi, энергозависимая или энергонезависимая память или устройство ввода/вывода могут содержать варианты осуществления логики преобразования и логики конечной точки, раскрытые здесь в другом месте. Мобильное беспроводное устройство также содержит микросхему 671 электропитания, которая связана с SoC 601. Микросхема электропитания связана с батареей 672, выполненной с возможностью питания мобильного беспроводного устройства.

На фиг. 7 показан вариант осуществления многоуровневого стека протоколов. Многоуровневый стек 700 протоколов содержит любую форму многоуровневого стека связи, такого как стек Quick Path Interconnect (QPI), стек PCie, высокопроизводительный вычислительный стек межсоединений следующего поколения или другой многоуровневый стек. В одном из вариантов осуществления стек 700 протоколов является стеком PCie протоколов, содержащим уровень 705 транзакций, канальный уровень 710 и физический уровень 720. Интерфейс может быть представлен как стек 700 протоколов связи. Представление в виде стека протоколов связи может также упоминаться в отношении модуля или интерфейса, реализующего/содержащего стек протоколов.

PCI Express использует пакеты, чтобы передавать информацию между компонентами. Пакеты формируются на уровне 705 транзакций (Transaction Layer) и на уровне 710 канала передачи данных (Data Link Layer), чтобы переносить информацию от компонента передачи к компоненту приема. По мере того, как передаваемые пакеты проходят через другие уровни, они расширяются с помощью дополнительной информации, необходимой для обработки пакетов на этих уровнях. На приемной стороне происходит обратный процесс и пакеты преобразуются из своего представления на физическом уровне 720 (Physical Layer) в представление на уровне 710 канала передачи данных (Data Link Layer) и, наконец, (для пакетов уровня транзакции, Transaction Layer Packet) в форму, которая может быть обработана на уровне 705 транзакций приемного устройства.

В одном из вариантов осуществления уровень 705 транзакции должен обеспечивать интерфейс между ядром обработки устройства и архитектурой межсоединений, такой как уровень 710 канала передачи данных и физический уровень 720. В этом отношении, первичной ответственностью уровня 705 транзакции является ассемблирование и дизассемблирование пакетов (то есть, пакетов уровня транзакции или TLP). Уровень 705 трансляции обычно руководит управлением потока на кредитной основе для TLP. PCie реализует транзакции разделения, то есть, транзакции с запросом и ответом, разделенными во времени, позволяя каналу связи выполнять другой трафик, в то время, как целевое устройство собирает данные для ответа.

Кроме того, PCie использует управление потоком на кредитной основе. В этой схеме устройство рекламирует начальное количество кредита для каждого из буферов приема на уровне 705 транзакций. Внешнее устройство на противоположном конце канала связи, такое как концентратор 115 контроллера, показанный на фиг. 1, подсчитывает количество кредитов, израсходованных каждым TLP. Транзакция может передаваться, если транзакция не превышает лимит кредита. После приема ответа величина кредита восстанавливается. Преимущество кредитной схемы состоит в том, что задержка возврата кредита не влияет на характеристики при условии, что не достигается лимит кредита.

В одном из вариантов осуществления четыре адресных пространства транзакций содержат адресное пространство конфигурации, адресное пространство памяти, адресное пространство ввода/вывода и адресное пространство сообщения. Транзакции пространства памяти содержат один или больше запросов считывания и запросов записи, чтобы передавать данные в местоположение с отображенной памятью и из него. В одном из варианте осуществления транзакции пространства памяти способны использовать два различных формата адресов, например, формата короткого адреса, такого как 32-разрядный адрес, или формата длинного адреса, такого как 64-разрядный адрес. Транзакции пространства конфигурации используются для доступа к пространству конфигурации устройств PCIe. Транзакции в пространство конфигурации содержат запросы считывания и запросы записи. Транзакции пространства сообщения (или просто сообщения) определяются так, чтобы поддерживать внутриполосную связь между агентами PCIe.

Поэтому, в одном из вариантов осуществления, уровень 705 транзакций ассемблирует заголовок/полезную нагрузку 706 пакета. Формат для текущих заголовков/полезных нагрузок пакета может быть найден в спецификации PCIe на вебсайте спецификаций PCIe.

На фиг. 8 показан вариант осуществления примерного стека протоколов для одного или более интерфейсов, обсуждаемых здесь. Например, межсоединение может содержать физический уровень (PHY), чтобы обеспечить электрическую/физическую связь в то время, как уровни более высокого уровня, такие как уровень протокола, транзакции, приложения или канала связи, могут обеспечить дополнительные функциональные возможности связи. Здесь, MPHY 850 способен к тому, чтобы быть реализованным с множеством различных уровней протоколов, таких как DigRF 855, UniPro 860, LLI 865, SSIC 870 (то ест, 3 протокола USB) или PCIe 875 (то есть Mobile Express). Физический уровень также содержит D-PHY 805. Уровень протоколов также содержит CSI 810 и DSI 815. Уровень приложений также содержит CSI 811, CSI 816, CSI 856, CSI 861, CSI 867, CSI 871 и CSI 876.

На фиг. 9 показан вариант осуществления вычислительной платформы малой мощности. В одном из вариантов осуществления вычислительная платформа 900 малой мощности содержит оборудование пользователя (UE). В некоторых вариантах осуществления UE относится к устройству, которое может использоваться для связи, такому как устройство с возможностью голосовой связи. Примерами UE являются телефон, смартфон, планшет, ультрапортативный ноутбук и маломощный ноутбук. Однако, вычислительная платформа малой мощности может также относиться к любой другой платформе, чтобы получить рабочую точку с пониженной мощностью, такую как планшет, маломощный ноутбук, ультрапереносимый или ультратонкий ноутбук, микросерверный сервер, маломощный настольный компьютер, передающее устройство, приемное устройство или любая другая известная или доступная вычислительная платформа. Показанная платформа изображает множество различных межсоединений, чтобы связывать между собой многочисленные различные устройства. Примерное обсуждение этих межсоединений обеспечивается ниже, чтобы предоставить возможности на реализации и введению раскрытых здесь устройства и способы. Однако, маломощная платформа 900 не требуется, чтобы содержать или реализовывать изображенные межсоединения или устройства. Кроме того, могут содержаться и другие устройства и структуры межсоединений, которые конкретно не показаны.

Начиная с центра чертежа, платформа 900 содержит прикладной процессор 905. Часто он содержит маломощный процессор, который может быть версией конфигурации процессора, описанной здесь или известной в отрасли. Как пример, процессор 900 реализуется как система на одной микросхеме (SoC). В конкретном иллюстративном примере, процессор 900 содержит процессор на основе Intel® Architecture Core™, такой как i3, i5, TI или другой такой процессор, доступный от компании Intel Corporation, Санта-Клара, Калифорния. Однако, следует понимать, что на SoC могут быть интегрированы и другие маломощные процессоры, такие как процессоры доступные от компаний Advanced Micro Devices, Inc. (AMD), Саннивейл, Калифорния, проект на основе MIPS от MIPS Technologies, Inc. Саннивейл, Калифорния, проект на основе ARM, лицензированный от ARM Holdings, Ltd. или ее клиента или их лицензиаты или правообладатели, которые могут вместо них присутствовать в других вариантах осуществления, такие как процессор А5/А6 Apple, процессор Qualcomm Snapdragon или процессор ОМАР TI. Заметим, что по мере того, как процессор и технологии SoC от этих компаний совершенствуются, на SoC могут интегрироваться больше компонентов, показанных как отдельные от главного процессора 900,. В результате, подобные межсоединения (и связанные с ними изобретения) могут использоваться "на кристалле".

В одном из вариантов осуществления прикладной процессор 905 выполняет операционную систему, интерфейс пользователя и приложения. Здесь прикладной процессор 905 часто распознает или связывается с архитектурой набора команд системы команд, Instruction Set Architecture (ISA), так что операционная система, интерфейс пользователя и приложения используют напрямую операции/исполнения операций процессором 905. Он также обычно взаимодействует через интерфейс с датчиками, камерами, дисплеями, микрофонами и запоминающим устройством большой емкости. Некоторые реализации позволяют передать критичную ко времени телекоммуникационную обработку другим компонентам.

Как можно видеть, главный процессор 905 связывается с беспроводным интерфейсом 930, таким как WLAN, WiGig, WirelessHD или другим беспроводным интерфейсом. Здесь используется совместимое межсоединение LLI, SSIC или UniPort, чтобы связать главный процессор 905 и беспроводной интерфейс 930.

LLI поддерживает интерфейс с малой задержкой. LLI обычно позволяет совместное использование памяти двумя устройствами. Двунаправленный интерфейс транспортирует транзакции памяти между двумя устройствами и позволяет устройству получать доступ к локальной памяти другого устройства; часто это делается без вмешательства программного обеспечения, как если бы это было единственное устройство. LLI, в одном варианте осуществления разрешаются три класса трафика, переносящие сигналы по каналу связи, снижая отсчет количества GPIO. Как пример, LLI определяет многоуровневый стек протоколов для передачи или физического уровня (PHY), такого как MPHY, который описывается ниже более подробно.

SSIC относится к сверхскоростной микросхеме SuperSpeed Inter-Chip. SSIC может позволить конструировать высокоскоростные USB-устройств, использующие физический уровень малой мощности. Как пример, используется уровень MPHY, в то время как совместимые протоколы USB 3.0 и программное обеспечение используются помимо MPHY для лучших энергетических показателей.

UniPro описывает многоуровневый стек протоколов с абстракцией физического уровня, обеспечивающей универсальное, с обработкой ошибок, высокоскоростное решение для межсоединения широкого диапазона устройств и компонент: прикладных процессоров, сопроцессоров, модемов и периферийных устройств, а также поддержки различных типов трафика данных, в том числе, сообщений управления, массовой передачи данных и пакетированной потоковой передачи. UniPro может поддерживать использование MPHY или DPHY.

Другие интерфейсы могут также связываться напрямую с главным процессором 905, модулем 990 отладки, сетью 985, дисплеем 970, камерой 975 и запоминающим устройством 980 через другие интерфейсы, которые могут использовать описанные здесь устройства и способы.

Интерфейс 990 отладки и сеть 985 связываются с прикладным процессором 905 через интерфейс 991 отладки, например, PTI, или сетевое соединение, например, интерфейс отладки, который работает через функциональное сетевое соединение 985.

Дисплей 970 содержит один или более дисплеев. В одном из вариантов осуществления дисплей 970 содержит дисплей с одним или более сенсорными датчиками, способными принимать/обнаруживать сенсорный ввод. Здесь дисплей 970 связывается с прикладным процессором 905 через интерфейс дисплея (DSI) 971. DSI 971 определяет протоколы между главным процессором и периферийными устройствами, которые могут использовать физический интерфейс D-PHY. Обычно он принимает пиксельные форматы и определенный набор команд для видеоформатов и сигнализации, такие как Display Pixel Interface 2 (DPI-2) и параметры модуля дисплея управления, такие как Display Command Set (DCS). Как пример, DSI 971 работает на частоте приблизительно от 1,5 ГГб/с на маршрут и до 6 ГГб/с.

Камера 975 в одном из вариантов осуществления содержит датчик изображения, используемый для получения фотоснимков, видеосъемки или того и другого. Камеры передней и задней стороны являются обычными на мобильных устройствах. Двойные камеры могут использоваться для обеспечения поддержки стереоскопии. Как видно на чертеже, камера 975 связывается с прикладным процессором 905 через периферийное межсоединение, такое как CSI 976. CSI 976 определяет интерфейс между периферийным устройством (например, камерой, процессором сигналов изображения) и главным процессором (например, 905, широкополосным прикладным механизмом). В одном из вариантов осуществления передачи данных изображения выполняются через DPHY, однонаправленный дифференциальный последовательный интерфейс с данными и тактовыми сигналами. Управление периферией в варианте осуществления происходит по отдельному обратному каналу, такому как управление камерой. Как пример, скорость CSI может колебаться от 50 Мбит/с до 2 Гбит/с или в любом диапазоне/с любым значением из них.

Запоминающее устройство 980 в одном из примеров содержит энергонезависимую память, используемую прикладным процессором 905 для хранения большого объема информации. Оно может быть основана на флэш-технологии или на магнитном типе хранения, таком как жесткий диск. Здесь запоминающее устройство 980 связывается с процессором 905 посредством межсоединения 981 Universal Flash Storage (UFS). UFS 981 в одном из вариантов осуществления содержит межсоединение, которое адаптируется для маломощных компьютерных платформ питания, таких как мобильные системы. Как пример, оно обеспечивает скорость передачи между 200 и 500 МВ/с (например, 300 МВ/с), используя признаки организации очередей, чтобы увеличить случайные скорости считывания-записи. В одной из реализаций UFS 981 использует физический уровень MPHY и уровень протоколов, такой как UniPro.

Модем 910 часто рекомендуется для модулятора/демодулятора. Модем 910 обычно обеспечивает интерфейс для сотовой связи. При этом используется его способность к передаче с различными типами сетей и различными частотами, в зависимости от того, какой стандарт связи используется. В одном варианте осуществления поддерживаются соединения как для передачи речи, так и данных. Модем 910 связывается с главным процессором 905, используя любое известное межсоединение, такое как одно или более из числа LLI, SSIC, UniPro, Mobile Express и т.д.

В одном из вариантов осуществления шина управления используется для связи управления или интерфейсов данных, таких как беспроводной интерфейс 935, громкоговоритель 940, микрофон 945. Примером такой шины является SLIMbus, гибкий маломощный многоточечный интерфейс, способный поддерживать широкий диапазон аудиорешений и решений для управления. Другие примеры содержат PCM, I2S, I2C, SPI, и UART. Беспроводная связь интерфейс 935 содержит такой интерфейс, как интерфейс по стандарту связи малой дальности между двумя устройствами (например, Bluetooth или NFC), навигационную систему, способную к триангуляции по положению и/или времени (например, GPS), приемник для аналоговых или радиопередач (например, FM Radio) или другой известный беспроводной интерфейс или стандарт. Громкоговоритель-(и) 940 содержит любое устройство для создания звука, такое как электромеханическое устройство, чтобы формировать музыку для телефонных звонков или музыку. Многочисленные громкоговорители могут использоваться для стерео- или многоканального звука. Микрофон 945 часто используется для речевого ввода, такого как разговор во время вызова.

Радиочастотная интегральная схема (RFIC) 915 должна выполнять аналоговую обработку, такую как обработка радиосигналов, например, усиление, преобразование частоты, фильтрация и цифровое преобразование. Как показано на чертеже, RFIC 915 связывается с модемом 910 через интерфейс 912. В одном из вариантов осуществления, интерфейс 912 содержит двунаправленный, высокоскоростной интерфейс (например. DigRF), который поддерживает такие стандарты связи, как LTE, 3GPP, EGPRS, UMTS, HSPA+, и TD-SCDMA. В качестве конкретного примера, DigRF использует ориентированный на кадры протокол, основанный на физическом уровне M-PHY. DigRF обычно упоминается как удобный для RF, с малой задержкой, маломощный, с оптимизированным количеством выводом, который в настоящее время работает со скоростью между 1,5 и 3 Гбит/с на маршрут и может выполнен с множеством маршрутов, таких как 4 маршрута.

Интерфейс 961 (например, интерфейс RF-управления) содержит гибкую шину для поддержки простых и сложных устройств. Как конкретный пример, интерфейс 961 содержит гибкую двухпроводную последовательную шину, предназначенную для управления компонентами RF Front- End. Одно устройство управления шиной может записывать и считывать данные во множество устройств, такие как усилитель 950 мощности для усиления мощности RF-сигнала, датчики, для приема сигналов от датчиков, модуль(и) 960 переключателя для переключения путей прохождения RF-сигнала в зависимости от режима сети, и блоки 965 настройки антенны для компенсации плохих условий распространения радиоволн или улучшения полосы пропускания. Интерфейс 961 в одном из вариантов осуществления имеет функцию группового запуска для критичных ко времени событий и низкой EMI.

Управление 920 электропитанием используется для обеспечения всех различных компонент в мобильном устройстве 900 управляемым напряжением электропитания, таким как уменьшающееся напряжение или увеличивающееся напряжение, чтобы повысить эффективность компонент в мобильном устройстве. В одном из вариантов осуществления оно также управляет и контролирует заряд батареи и остающуюся энергию. Интерфейс батареи может быть использован между управлением 920 электропитанием и батареей. Как пример, интерфейс батареи содержит однопроводное соединение между мобильным терминалом и смарт/дешевыми батареями.

На фиг. 10 представлена блок-схема компонент, существующих в компьютерной системе в соответствии с вариантом осуществления настоящего изобретения. Как показано на фиг. 10, система 1000 содержит любую комбинацию компонент. Эти компоненты могут быть реализованы как интегральные схемы (IC), их части, дискретные электронные устройства или другие модули, логика, аппаратурные средства, программное обеспечение, встроенное микропрограммное обеспечение или их комбинации, адаптированные в компьютерной системе, или как компоненты, иным способом введенные внутрь шасси компьютерной системы. Заметим также, что блок-схема, показанная на фиг. 10, предназначена показывать вид верхнего уровня многих компонент компьютерной системы. Однако, следует понимать, что некоторые из показанных компонент могут отсутствовать могут присутствовать дополнительные компоненты и в других реализациях может иметься другое расположение показанных компонент. В результате, изобретение, описанное выше, может быть реализовано на любом участке одного или более межсоединений, показанных или описанных ниже.

Как видно на фиг. 10, процессор 1010 в одном из вариантов осуществления содержит микропроцессор, многоядерный процессор, многопоточный процессор, процессор с ультранизким напряжением, встроенный процессор или другой известный элемент обработки. В показанной реализации процессор 1010 действует как основной процессорный блок и центральный концентратор для связи с множеством различных компонент системы 1000. Как пример, процессор 1000 реализуется как система на микросхемах (SoC). Как конкретный пояснительный пример, процессор 1010 содержит процессор Intel® на основе Architecture Core™, такой как i3, i5, i7 или другой такой процессор, доступный от Intel Corporation, Санта-Клара, Калифорния. Однако, следует понимать, что в других вариантах осуществления вместо таких процессоров, как процессор Apple А5/А6, процессор Qualcomm Snapdragon или процессор TI ОМАР могут присутствовать другие низковольтные процессоры, такие как доступные от Advanced Micro Devices, Inc. (AMD), Саннивейл, Калифорнии, проект на основе MIPS от MIPS Technologies, Inc. Саннивейл, Калифорния, проект на основе ARM проект, лицензированный от компании ARM Holdings, Ltd или ее потребителя. Заметим, что многие из заказных версий таких процессоров модифицируются и различаются; однако, они могут поддерживать или распознать набор конкретных команд, который выполняет определенные алгоритмы, как указано лицензиаром процессора. Здесь, микроархитектурная реализация может меняться, но архитектурная функция процессора является обычно совместима. Определенные подробности в отношении архитектуры и работы процессора 1010 в одной из реализаций будут обсуждены далее ниже, чтобы обеспечить пояснительный пример.

Процессор 1010 в одном из вариантов осуществления осуществляет связь с системной памятью 1015. Это иллюстративный пример, который в варианте осуществления может быть реализован через множество устройств памяти, чтобы обеспечить заданный объем системной памяти. В качестве примеров, память может соответствовать низковольтной, с двойной скоростью данных конструкции (LPDDR) Совместного Технического Совета по электронным устройствам, Joint Electron Devices Engineering Council (JEDEC), по текущему стандарту LPDDR2 согласно JEDEC JESD 209-2E (опубликовано в апреле 2009 г.) или следующему поколению стандарта LPDDR, который будут упоминаться как LPDDR3 или LPDDR4 с расширениями LPDDR2 для увеличения полосы пропускания. В различных реализациях индивидуальные устройства памяти могут иметь различные типы пакетов, такие как одиночный матричный пакет (SDP), двойной матричный пакет (DDP) или четверной матричный пакет (Q17P). Эти устройства в некоторых вариантах осуществления напрямую паяются на системную плату, чтобы обеспечить более низкое решение для профиля, в то время как в других вариантах осуществления устройства конфигурируются как один или более модулей памяти, которые поочередно связываются с системной платой данным соединителем. И конечно, возможны другие реализации памяти, такие как другие типы модулей памяти, например, модули памяти с двухрядным расположением выводов (DIMM) различных вариантов, в том числе, в частности, microDIMM, MiniDIMM. В конкретном иллюстративном варианте осуществления размер памяти составляет от 2 Гбайт до 16 Гбайт, и может быть выполнен как пакет DDR3LM или LPDDR2 или память LPDDR3, которая паяется на системную плату через шаровую сеточную матрицу (BGA).

Чтобы обеспечить постоянное хранение информации, такой как данные, приложения, одна или более операционных систем и т.д, запоминающее устройство 1020 большой емкости может быть также связано с процессором 1010. В различных вариантах осуществления, чтобы обеспечить более тонкую и легкую конструкцию системы, а также повысить чувствительность системы, это запоминающее устройство большой емкости может быть реализовано через SSD. Однако, в других вариантах осуществления запоминающее устройство большой емкости может быть реализовано, в первую очередь, используя жесткий диск (HDD) с малым объемом хранения SSD, чтобы действовать в качестве кэша SSD, позволяющего долговременное хранение состояния контекста и другой такой информации во время события выключения электропитания, так чтобы при повторном включении могло происходить быстрое включение деятельности системы. Также, как показано на фиг. 10, устройство 1022 флэш-памяти может быть связано с процессором 1010, например, через последовательный периферийный интерфейс (SPI). Это флэш-устройство может обеспечивать долговременное хранение системного программного обеспечения, в том числе, основного программного обеспечения ввода/вывода (BIOS), а также другого встроенного микропрограммного обеспечения системы.

В различных вариантах осуществления системное запоминающее устройство большой емкости реализуется только одним SSD или как диск, оптический или другой диск с кэшем SSD. В некоторых вариантах осуществления запоминающее устройство большой емкости реализуется как SSD или как HDD наряду с модулем восстанавливаемого кэша (RST). В различных реализациях HDD обеспечивает хранение объема хранения 320 ГВ - 4 ТБ и выше, в то время как кэш RST реализуется с SSD, имеющим емкость 24 ГБ - 256 ГБ. Заметим, что такой кэш SSD может быть выполнен как кэш единого уровня (SLC) или опция многоуровневого кэша (MLC), чтобы обеспечить соответствующий уровень чувствительности. В опции только с SSD модуль может быть помещен в различных местах, таких как в mSATA или слоте NGFF. Как пример, у SSD имеет емкость в пределах от 120 ГБ - 1 ТБ.

В пределах системы 1000 могут присутствовать различные устройства ввода-вывода (I/O). В варианте осуществления на фиг. 10 специально показан дисплей 1024, который может быть жидкокристаллическим дисплеем высокой четкости или светодиодной панелью (LED), выполненной внутри участка крышки шасси. Эта панель дисплея может также обеспечивать сенсорный экран 1025, например, выполненный поверх панели дисплея так, что посредством взаимодействия пользователя с этим сенсорным экраном, могут обеспечиваться вводы данных пользователем для системы, чтобы позволить желаемые операции, например, в отношении отображения информации, доступа к информации и т.д. В одном из вариантов осуществления, дисплей 1024 может быть связан с процессором 1010 через межсоединение дисплея, которое может быть реализовано как высокопроизводительное графическое межсоединение. Сенсорный экран 1025 может быть связан с процессором 1010 через другое межсоединение, которое в варианте осуществления может быть межсоединением I2C. Как дополнительно показано на фиг. 10, вдобавок к сенсорному экрану 1025 может также осуществляться ввод данных пользователем посредством касания сенсорной панели 1030, которая может быть выполнена внутри шасси и может также быть связана с тем же самым межсоединением I2C, что и сенсорный экран 1025.

В различных вариантах осуществления дисплей может иметь различные размеры экрана, например, 11,6 дюйма или 13,3 дюйма, и может иметь формат 16:9, и по меньшей мере 300 нит яркости. Также дисплей может иметь разрешающую способность полной высокой четкости (HD) (по меньшей мере 1920×1080 пикселей), быть совместимым со встроенным портом дисплея (eDP), и быть панелью с низкой потребляемой энергией с самообновлением панели.

Что касается возможностей сенсорного экрана, то система может обеспечивать мультисенсорную панель дисплея, обладающую мультисенсорной способностью и рассчитанной по меньшей мере на 5 пальцев. И в некоторых вариантах осуществления дисплей может быть пригоден для 10 пальцев. В одном варианте осуществления сенсорный экран располагается внутри защищенного от повреждений и царапин стекла и обладает покрытием (например, Gorilla GlassTM или Gorilla Glass 2ТМ) для низкого трения, чтобы уменьшить "горение пальца" и избежать "пропуска пальца". Чтобы обеспечить улучшенное ощущение касания и чувствительность, сенсорная панель, в некоторых реализациях имеет мультисенсорные функциональные возможности, такие как менее чем 2 кадра (30 Гц) на статический просмотр во время изменения масштаба защемления, и функциональная возможность одного касания с менее чем 1 см на кадр (30 Гц) за 200 мс (задержка на пальце до указателя). Дисплей в некоторых реализациях поддерживает стекло по краям с минимальным перекосом экрана, которое также заделан заподлицо с поверхностью панели, и ограниченная интерференция ввода-вывода при использовании мультикасания.

Для целей перцепционных вычислений и других целей в системе могут присутствовать различные датчики, которые могут быть связаны с процессором 1010 различными способами. Определенные инерционные датчики и датчики среды могут связываться с процессором 1010 через концентратор 1040 датчиков, например, через межсоединение I2C. В варианте осуществления, показанном на фиг. 10, эти датчики могут содержать акселерометр 1041, датчик 1042 окружающего света (ALS), компас 1043 и гироскоп 1044. Другие датчики окружающей среды могут содержать один или более температурных датчиков 1046, которые в некоторых вариантах осуществления связываются с процессором 1010 через шину системного управления (SMBus).

Например, в отношении управления электропитанием/проблемы срока службы работы, основываясь, по меньшей мере, на части информации от датчика окружающего света, определяют условия окружающего света в месте расположения платформы и, соответственно, управляют интенсивностью свечения дисплея. Таким образом, электроэнергия, расходуемая при работе дисплея, в определенных условиях освещения снижается.

В варианте осуществления операционная система (ОС) может быть операционной системой Microsoft® Windows® 8, которая реализует функцию Connected Standby, (также упоминаемое здесь как Win8 CS). Connected Standby Windows 8 или другая ОС, имеющая подобное состояние, может обеспечивать через платформу, как описано здесь, очень низкое электропитание в неактивном режиме, чтобы позволить приложениям остаться подключенными, например, к местоположению, основанному на облаке, при очень низком потреблении энергии. Платформа может поддерживать 3 состояния электропитания, а именно, экран включен (нормальное); Connected Standby (как значение по умолчанию "выключенное состояние"); и отключение (нулевое потребление электропитания). Таким образом, в состоянии Connected Standby платформа логически включена (при минимальном уровне потребляемой мощности) даже при том, что экран выключен. В такой платформе управление электропитанием может быть сделано прозрачным для приложений и поддержать постоянную связь, в частности, благодаря технологии выгрузки, чтобы позволить выполнять работу компоненту с самым низким потреблением энергии.

Также, на фиг. 10 видно, что различные периферийные устройства могут связываться с процессором 1010 через межсоединение с малым количеством выводов (LPC). В показанном варианте осуществления различные компоненты могут связываться через встроенный контроллер 1035. Такие компоненты могут содержать клавиатуру 1036 (например, связанный через интерфейс PS2), вентилятор 1037 и температурный датчик 1039. В некоторых вариантах осуществления сенсорная панель 1030 может также связываться с ЕС 1035 через интерфейс PS2. Кроме того, защитный процессор, такой как проверенный модуль платформы (ТРМ) 1038 в соответствии с версией 1.2 спецификации ТРМ Trusted Computing Group (TCG), датированной 2 октября 2003 г., может также связываться с процессором 1010 через это межсоединение LPC. Однако, следует понимать, что объем настоящего изобретения не ограничивается в этом отношении и безопасная обработка и хранение безопасной информации могут осуществляться в другом защищенном месте, таком как статическая оперативная память (SRAM) в сопроцессоре безопасности, или как зашифрованные блобы данных, которые расшифровываются, только когда защищаются режимом безопасного включения (SE) процессора.

В конкретной реализации периферийные порты могут содержать соединитель медиаинтерфейса высокой четкости (HDMI) (который может иметь другие факторы формы, такие как полный размер, мини- или микро); один или более портов USB, таких как полноразмерные внешние порты в соответствии со спецификацией версии 3.0 универсальной последовательной шины, Universal Serial Bus Revision 3.0 Specification, (ноябрь 2008 г. , из которых по меньшей мере один подает энергию для заряда USB-устройств (таких как смартфоны), когда система находится в состоянии Connected Standby и включена в настенную сетевую розетку переменного тока. Кроме того, могут быть обеспечены один или более портов ThunderboltTM. Другие порты могут содержать внешне доступное устройство считывания с перфокарт, такое как полномасштабное устройство считывания с перфокарт SDXC и/или считыватель SIM-карты для WW AN (например, 8-миконтактное устройство считывания с перфокарт). Для аудио может присутствовать 3.5-миллиметровый разъем с возможностью подключения громкоговорителя и микрофона в стереорежиме (например, комбинационная функциональность), с поддержкой обнаружения разъема (например, наушники только поддерживают только микрофон, встроенный в крышку, или наушники с микрофоном в кабеле). В некоторых вариантах осуществления этот разъем может быть с переключением выполнения задач между стереонаушниками и вводом от стереомикрофона. Кроме того, может обеспечиваться разъем питания для связи с адаптером переменного тока (АС).

Система 1000 может связываться с внешними устройствами множеством способов, в том числе, беспроводным. В варианте осуществления, показанном на фиг. 10, присутствуют различные беспроводные модули, каждый из которых может соответствовать радиомодулю, выполненному с возможностью связи по конкретному протоколу беспроводной связи. Один из способов радиосвязи на малой дальности, такой как связь в ближнем поле, может осуществляться через блок 1045 связи в ближнем поле (NFC), который может осуществлять связь в одном их вариантов осуществления с процессором 1010 через SMBus. Заметим, что через этот блок 1045 NFC могут осуществлять связь устройства, находящиеся в непосредственной близости друг от друга. Например, пользователь может позволить системе 1000 связываться с другим (например) мобильным устройством, таким как смартфон пользователя, адаптируя двух устройства вместе в тесной связи и позволяя передавать информацию, такую как идентификационная информация, информация о платежах, данные, такие как данные изображения и так дальше. Беспроводная передача мощности также может выполняться, используя систему NFC.

Используя описанный здесь блок NFC, пользователи могут подталкивать устройства друг к другу и располагать устройства друг около друга для функций связи в ближнем поле (таких как связь в ближнем поле и беспроводная передача энергии (WPT)), усиливая связь между обмотками одного или более таких устройств. Более конкретно, варианты осуществления предоставляют устройства, сформированные и расположенные стратегически, имеющие ферритовые материалы, чтобы обеспечить лучшую связь катушек. Каждая катушка имеет индуктивность связанную с ней, которая может быть выбрана в сочетании с резистивными, емкостными и другими признаками системы, чтобы выбрать общую резонансную частоту для системы.

Как дополнительно видно на фиг. 10, дополнительные беспроводные блоки могут содержать другие беспроводные механизмы связи малой дальности, в том числе блок 1050 WLAN и блок 1052 Bluetooth. Используя блок 1050 WLAN 1050, может быть реализована связь по Wi-Fi™ в соответствии с заданным стандартом Института инженеров по электронике и радиотехнике (IEEE) 802.11, в то время как связь малой дальности может осуществляться через модуль 1052 Bluetooth по протоколу Bluetooth. Эти блоки могут осуществлять связь с процессором 1010, например, через канал связи USB или канал связи универсального асинхронного приемопередатчика (UART). Или эти блоки могут связываться с процессором 1010 через межсоединение согласно протоколу Peripheral Component Interconnect Express™ (PCIe™), например, в соответствии с версией 3.0 PCI ExpressTM Specification Base Specification (опубликованной 17 января 2007 г. ), или другому такому протоколу, такому как стандарт последовательного ввода/вывода данных (SDIO). Конечно, фактическое физическое соединение между этими периферийными устройствами, которое может быть выполнено с помощью одной или более расширительными платами, может с помощью соединителей NGFF адаптироваться к системной плате.

Кроме того, передача сообщений в области широкополосной беспроводной зоны, например, в соответствии с протоколом сотовой связи или другой беспроводной широкополосной области, может осуществляться через блок 1506 WWAN, который, в свою очередь, может связываться с модулем 1057 идентификации абонента (SIM). Кроме того, чтобы разрешить прием и использование информации о расположении, может также присутствовать модуль 1955 GPS. Заметим, что в варианте осуществления, показанном на фиг. 10, блок 1056 WWAN и интегрированное устройство получения, такое как модуль 1054 камеры, могут передавать по данному протоколу USB, такому как USB 2,0 или 3,0, канал связи или протокол I2C или UART. И снова, фактическое физическое соединение этих блоков может осуществляться через адаптацию расширительной платы NGFF к соединителю NGFF, выполненному на системной плате.

В конкретном варианте осуществления функциональные возможности беспроводной связи могут обеспечивать модальность, например, с решением WiFiTM 80211ac (например, расширительная плата, которая обратно совместима с IEEE 802.11labgn) с поддержкой Windows CS8. Эта карта может быть конфигурирована во внутреннем слоте (например, через адаптер NGFF). Дополнительный модуль может обеспечивать возможности Bluetooth (например, Bluetooth 4.0 с совместимостью обратно) а также функциональные возможности Intel® Wireless Display. Кроме того, поддержка NFC может быть предоставляться через отдельное устройство или мультифункциональное устройство и может быть расположена, как пример, на переднем правом участке шасси для легкости доступа. Еще один дополнительный модуль может быть устройством WWAN, которое может оказать поддержку для 3G/4G/LTE и GPS. Этот модуль может быть реализован во внутреннем слоте (например, NGFF). Поддержка интегрированной антенны может быть предоставлена WiFi™, Bluetooth, WWAN, NFC и GPS, позволяя осуществлять бесшовный переход от WiFi™ к WWAN для радиоканала, передавать беспроводные гигабайты (WiGig) в соответствии со спецификацией Wireless Gigabit Specification (июль 2010 г.) и наоборот.