Изобретение относится к технике дискретного регулирования фазового сдвига и может использоваться для измерительных, связных и управляющих систем с частотной и фазовой модуляцией, в том числе в квантовых стандартах частоты, эталонах единиц времени и частоты, компараторах частотных.

Для цифрового регулирования фазы импульсов обычно применяются устройства, принцип действия которых основан на пересчете импульсов опорного генератора. К таким устройствам относится цифровой управляемый фазовращатель по патенту РФ на полезную модель №757, в котором п-фазный генератор задает минимальную разность фаз. Недостаток такого устройства заключается в том, что такой генератор трудно выполнить высокостабильным и широкодиапазонным, так как сдвиг фаз обеспечивается инверторами с аналоговыми линиями задержки, которые должны быть перестраиваемые в зависимости от рабочей частоты.

В качестве ближайшего аналога (прототипа) предлагаемого технического решения принят цифровой фазовращатель по патенту RU № 2173933, который содержит опорный мультифазный генератор импульсов, через делитель частоты и регистр сдвига связанный с группой информационных входов первого мультиплексора. Мультиплексор и выходной первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ под управлением старших разрядов цифрового кода фазы осуществляют с шагом фазовый сдвиг. Вторые мультиплексор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ осуществляют фазовый сдвиг тактовых импульсов, а вместе с ними и выходных сигналов с шагом в соответствии с содержанием младших разрядов цифрового кода фазы.

Недостатком устройства-прототипа является сложность выполнения мультифазного генератора импульсов (задающего сдвиг фаз) особенно в широком диапазоне частот. Так как известная формула, связывающая частоту ω=dϕ/dt, где ϕ - текущая фаза; t - текущее время, полагает, что на разных частотах значение одинаковых отрезков времени вызывает различное значение текущей фазы (разности фазы между начальным и настоящим значением). Поэтому в этом генераторе импульсов требуется точно подстраивать задержку для калибровки шага установки фазы.

Технической задачей предлагаемого технического решения является повышение точности установки разности фаз цифрового фазовращателя в широком диапазоне частот при упрощении выполнения генератора импульсов.

Сущность технического решения задачи заключается в том, что цифровой фазовращатель, включающий генератор импульсов, выходной регистр, мультиплексор и блок управляющей логики, входы которого являются первой и второй (старших - первых и младших - вторых) группой входов цифровых кодов фазы цифрового фазовращателя, адресные входы мультиплексора являются входами цифровых кодов фазы со второй группы выходов блока управляющей логики, согласно заявляемому он дополнительно содержит, последовательно соединенные m-разрядный аналого-цифровой преобразователь (АЦП), вход которого является входом устройства исследуемого сигнала, демультиплексор организацией (m*n) m-разрядов на n-строк, (число n равно отношению периода входного сигнала к периоду сигнала генератора импульсов), оперативное запоминающее устройство организацией (m*n) разрядов, m-разрядный регистр с n-строками, (n-1) вычитателей кодов, подключенных к выходам регистра построчно с перекрытием, (n-1) делителей кодов, [k *(n-1)] цифровых логических ключей (элементов ИЛИ-НЕ) и [k* (n-1)] m-разрядных сумматоров, где k - число ступеней младших управляющих входных кодов, причем, в каждом (n-1) разряде сумматоры включены последовательно выходами ко вторым входам последующего k-сумматора, вторые входы первого сумматора подключены к соответствующему (n-1) выходу m-разрядного регистра с n строками, а выходы последних k-сумматоров подключены соответственно к (n-1) входам мультиплексора, и частотомер (частотомер-периодомер, определяющий количество строк n в демультиплексоре и ОЗУ), первый вход которого соединен с входом устройства, а группа его выходов подключена к третьей группе входов блока управляющей логики, выход генератора импульсов подключен соответственно к тактовому входу АЦП, к тактовому входу частотомера, к тактовому входу выходного регистра и тактовому входу m-разрядного регистра с n-строками, группа вторых и третьих выходов блока управляющей логики подключены ко вторым и третьим входам ОЗУ, четвертые выходы подключены к входам соответствующих цифровых логических ключей, пятая группа выходов блока управляющей логики подключена к управляющим входам демультиплексора, при этом первые входы выходного регистра соединены с выходами мультиплексора, а выход регистра служит выходом цифрового фазовращателя.

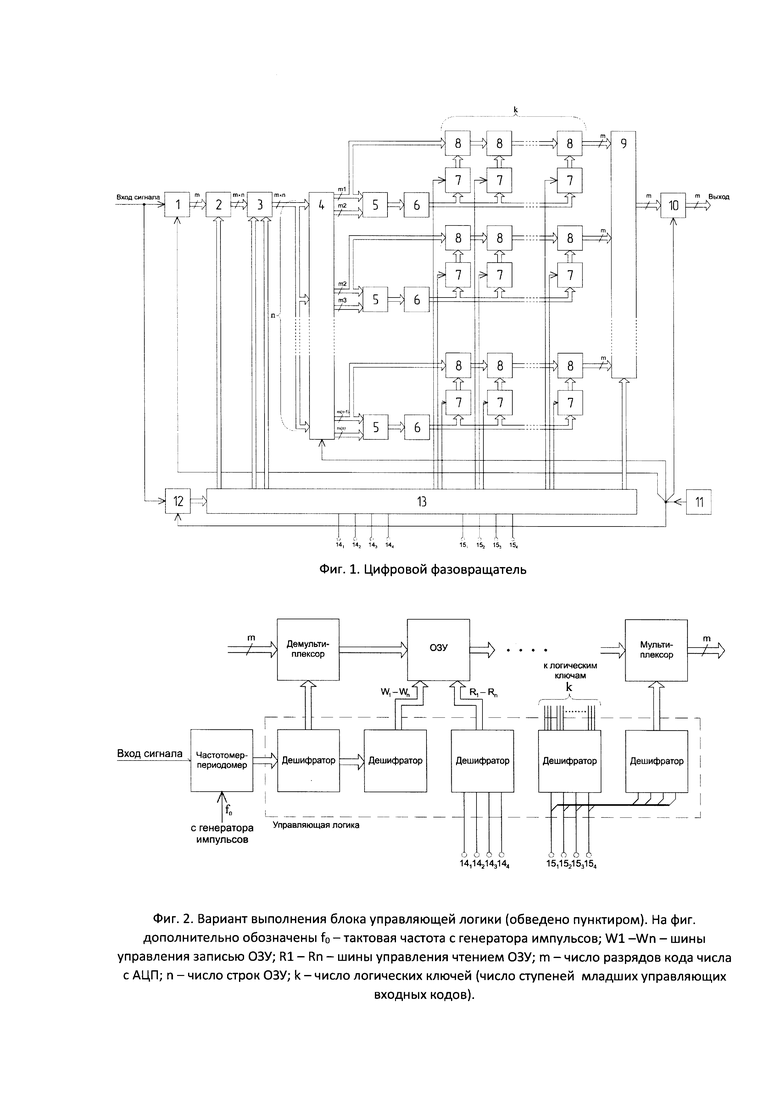

Техническое решение поясняется структурной схемой цифрового фазовращателя (фиг. 1), где обозначено: 1 - аналого-цифровой преобразователь (АЦП); 2 - демультиплексор; 3 - оперативное запоминающее устройство (ОЗУ); 4 - m-разрядный регистр с n-строками; 5-вычитатели кодов; 6 - делитель кодов; 7 - цифровые логические ключи; 8 - сумматоры кодов; 9 - мультиплексор; 10 - параллельный (выходной) регистр; 11 - опорный генератор импульсов; 12 - частотомер-периодомер; 13 - блок управляющей логики; 14 - старшие (первые) управляющие коды фазы цифрового фазовращателя; 15 - младшие (вторые) управляющие коды фазы цифрового фазовращателя, 16 - преобразователей кодов - дешифраторы.

На фиг. 2 представлена схема взаимодействия блока управляющей логики 13 в цифровом фазовращателе. Она состоит из нескольких преобразователей кодов - дешифраторов 16, которые нужны для преобразования и управления демультиплексором, ОЗУ, логическими ключами и мультиплексором, имеющих различную логическую структуру управления.

Для изготовления предлагаемого цифрового фазовращателя требуются известные технические средства [1, 2]. Так, сумматоры 8 и вычитатели 5 кодов могут быть выполнены на микросхемах 1533ИМ3, 1533ИМ6; аналого-цифровой преобразователь 1 на микросхемах MDRA1A16FI, 1113ПВ1; мультиплексор 9 на микросхемах 1533КП2, 1561КП1; демультиплексор 2 на микросхеме CD4556BE; ОЗУ 3 - на микросхемах 565РУ5, 555ИР26; регистр 4 на микросхеме 1533ИР9; управляющая логика 14. 15 и цифровые логические ключи 7 на микросхемах 1533ЛЕ5, 1533ЛА3-1533ЛА12, 555ИД3. Все эти узлы проще и технологичнее выполнить на ПЛИС, в которых есть готовые библиотеки элементов [3]. В качестве генератора 11 импульсов можно использовать кварцевую стабилизацию частоты и одновременно обеспечить широкий диапазон перестройки частоты. Частотомер-периодомер 12 выполняется по классической схеме.

Цифровой фазовращатель (фиг. 1) включает последовательно соединенные m-разрядный АЦП 1 (вход которого является входом устройства), демультиплексор 2 и ОЗУ 3, m-разрядный регистр с n-строками 4, тактовый вход которого соединен с генератором 11 сигналов, выходы которого подключены соответственно к (n-1) цепочкам в каждом разряде из последовательно соединенных вычитателей 5 кодов, делителей 6 кодов, выходы которых подключены к первым входам [k *(n-1)] цифровых логических ключей 7 (элементов ИЛИ-НЕ), выходы каждого из которых подключены к входам [k*(n-l)] m-разрядных сумматоров 8, причем, в каждом (n-1) разряде сумматоры 8 включены последовательно выходами ко вторым входам соответствующего последующего k-сумматора 8k, вторые входы первого сумматора 81 подключены к соответствующему (n-1) выходу m-разрядного регистра с n-строками 4, а выходы последних k-сумматоров 8k подключены соответственно к (n-1) входам мультиплексора 9, выходы которого соединены с соответствующими входами параллельного (выходного) регистра 10, тактовый вход которого подключен к генератору 11 импульсов, а группа выходов служит выходом цифрового фазовращателя. Генератор 11 импульсов также подключен к тактовому входу АЦП 1, к тактовому входу частотомера 12, первый вход которого соединен с входом устройства. Блок управляющей логики 13, входы которого присоединены к соответствующим входным зажимам 14 старших разрядов цифровых кодов фазы, к соответствующим входным зажимам 15 младших разрядов цифровых кодов фазы и к выходу частотомера 12. Управляющие выходы блока управляющей логики 13 соединены соответственно с адресными входами цифровых логических ключей 7 и с адресными входами демультиплексора 2 и мультиплексора 9. Частотомер 12 является частотомером-периодомером, т.е. измерителем периода входного сигнала, а именно отношение тактовой частоты к входной или периода входного сигнала к периоду тактовой частоты генератора импульсов. Если использовать просто частотомер, тогда потом управляющая логика должна "переворачивать" значение выходного кода частотомера. Чтобы этого не делать - проще частотомером-периодомером измерять сразу период входной частоты относительно тактового сигнала генератора импульсов.

Работа цифрового фазовращателя осуществляется следующим образом. По каждому такту сигнала генератора импульсов 11 записываются последовательно в каждую строку ОЗУ 3 значения кода входной частоты, вычисленное с помощью АЦП 1. Количество занятых строк ОЗУ 3 зависит от входной частоты и определяется частотомером-периодомером 12. С каждым тактом опорной частоты генератора 11 сигналов значения кода входной частоты в ОЗУ 3 перезаписывается (обновляются) в каждую следующую строку n. Выборка кода на выход цифрового фазовращателя в m-разрядный регистр с n-строками 4 осуществляется последовательно тактовым сигналом в соответствии с первым управляющим кодом 14, поданным на вход блока управляющей логики 13. При нулевом значении этого кода в m-разрядный регистр с n-строками 4 перезаписывается тот же код, который записывается в строку ОЗУ 3. При изменении первого управляющего кода переключается входным кодом управляющая логика для считывания в m-разрядный регистр 4 с n-строками предыдущего или наоборот, последующего значения кода из ОЗУ 3. Таким образом, при периодическом входном сигнале может осуществляться сдвиг кода фазы как назад, так и вперед, в зависимости от кода управляющей логики на одну или несколько строк. Затем, происходит нахождение промежуточных значений разности кода двух соседних выборок каждой ступени и выполняются вычисления по формуле:

(Fi - Fi+1) /k *v + Fi;

где k - число ступеней младших управляющих входных кодов 15, v - число, равное выборке требуемой ступени управляющей логикой; Fi, Fi+1 - коды двух соседних промежуточных чисел. Вычитатель 5 производит получение разности соседних кодов, записанных в ОЗУ 3, эта разность делится на к. Если младшие управляющие коды 15 не нулевые, этот вычисленный код шага последовательно добавляется или не добавляется (в зависимости от состояния открытого или закрытого цифрового логического ключа 7) на шаг ступени в каждом k - том сумматоре 8 и код нужного количества шагов v суммируется с минимальным входным кодом Fi, для подачи на каждый вход мультиплексора 9 цифрового фазовращателя.

Например, в диапазоне входных частот 1-30 МГц, при числе ступеней интерполирования k=8, точность установки фазы повышается в 8 раз - в наихудшем случае - вместо двух ступеней при тактовой частоте 60 МГц - будет восемь, и дискретность установки разности фаз вместо 180 градусов будет 22 градуса. А в начале диапазона - при входной частоте, равной 1 МГц, дискретность вместо 60 будет 479. Что соответствует вместо 6 градусов шагу 0,75 градусов.

Таким образом, для создания меток отсчета фазы не требуется использовать мультифазный генератор импульсов. Тактирование устройства проходит синхронно одним генератором импульсов каждый такт. Используется только один выход генератора импульсов. Этим обеспечивается высокая стабильность фазы. При этом повышается точность установки разности фаз цифрового фазовращателя за счет повышения дискретности в широком диапазоне частот.

Литература

1. Б.Г. Федорков, В.А. Телец Микросхемы ЦАП и АЦП,

функционирование, параметры, применение. М.: Энергоатомиздат, 1990.

2. В.Л. Шило Популярные цифровые микросхемы: Справочник, 2е изд., испр. - Челябинск; Металлургия, Челябинское отд., 1989.

3. М. Клайв Проектирование на ПЛИС. Архитектура, средства и методы. Издательский дом «Додека-XXI», 2007 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Устройство для измерения динамической погрешности аналого-цифровых преобразователей | 1984 |

|

SU1221749A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396721C1 |

| Многоканальное устройство для измерения температуры | 1990 |

|

SU1791731A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ МНОГОЛУЧЕВЫХ РАДИОСИГНАЛОВ | 1992 |

|

RU2042195C1 |

| Устройство для зондирования ионосферы | 1990 |

|

SU1742762A1 |

Изобретение предназначено для прецизионных измерений относительной разности фаз и может быть использовано в измерителях и калибраторах фаз для эталонов единиц времени и частоты, в квантовых водородных генераторах и квантовых дискриминаторах стандартов частоты. Цифровой фазовращатель состоит из включенных последовательно АЦП, демультиплексора, ОЗУ, регистра, (n-1) каналов, состоящих из вычитателей, делителей кодов, цифровых логических ключей, сумматоров, мультиплексора и регистра, включенных последовательно, а также частотомера-периодомера, опорного генератора и блока управляющей логики, причем вторые входы первых сумматоров подключены к соответствующим выходам регистра, (n-1) каналов, сумматоры включены выходами ко вторым входам следующих, а последние сумматоры подключены к соответствующим входам мультиплексора. На тактовые входы АЦП, регистров и частотомера-периодомера подан тактовый сигнал с генератора импульсов, а управляющие коды поданы через блок управляющей логики на демультиплексор, ОЗУ, мультиплексор и цифровые логические ключи. Технический результат заключается в повышении точности установки разности фаз в широком диапазоне частот. 2 ил.

Цифровой фазовращатель, включающий генератор импульсов, выходной регистр, мультиплексор и блок управляющей логики, входы которого являются первой и второй группой входов цифровых кодов фазы цифрового фазовращателя, адресные входы мультиплексора являются входами цифровых кодов фазы с первой группы выходов блока управляющей логики, отличающийся тем, что он содержит последовательно соединенные m-разрядный АЦП, вход которого является входом устройства исследуемого сигнала, демультиплексор организацией (m*n) m-разрядов на n-строк, оперативное запоминающее устройство организацией (m*n) разрядов, m-разрядный регистр с n-строками, (n-1) вычитателей кодов, подключенных к выходам регистра построчно с перекрытием, (n-1) делителей кодов, [k *(n-1)] цифровых логических ключей и [k*(n-1)] m-разрядных сумматоров, где k - число ступеней младших управляющих входных кодов, причем в каждом (n-1) разряде сумматоры включены последовательно выходами ко вторым входам последующего k-сумматора, вторые входы первого сумматора подключены к соответствующему (n-1) выходу m-разрядного регистра с n строками, а выходы последних k-сумматоров подключены соответственно к (n-1) входам мультиплексора, и частотомер, первый вход которого соединен с входом устройства, а группа его выходов подключена к третьей группе входов блока управляющей логики, выход генератора импульсов подключен соответственно к тактовому входу АЦП, к тактовому входу частотомера, к тактовому входу выходного регистра и тактовому входу m-разрядного регистра с n-строками, группа вторых и третьих выходов блока управляющей логики подключены ко вторым и третьим входам ОЗУ, четвертые выходы подключены к входам соответствующих цифровых логических ключей, пятая группа выходов блока управляющей логики подключена к управляющим входам демультиплексора, при этом первые входы выходного регистра соединены с выходами мультиплексора, а выход регистра служит выходом цифрового фазовращателя.

| ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ | 2000 |

|

RU2173933C1 |

| ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ СО СВЕРХШИРОКОЙ ПОЛОСОЙ ПРОПУСКАНИЯ | 2016 |

|

RU2664776C1 |

| CN 202339906 U, 18.07.2012 | |||

| WO 2012168926 A2, 13.12.2012. | |||

Авторы

Даты

2024-07-23—Публикация

2024-03-05—Подача