Изобретение относится к автомати- к.е и вычислительной технике, предназ- начено для цифроаналогового преоб- разования двух цифровых сигналов и может быть использовано в цифровых стереофонических устройствах воспро изведения звука, в системах связи с импульсно-кодовой модуляцией.

Цель изобретения - повышение быстродействия и улучшение устройства цифроаналогового преобразования.

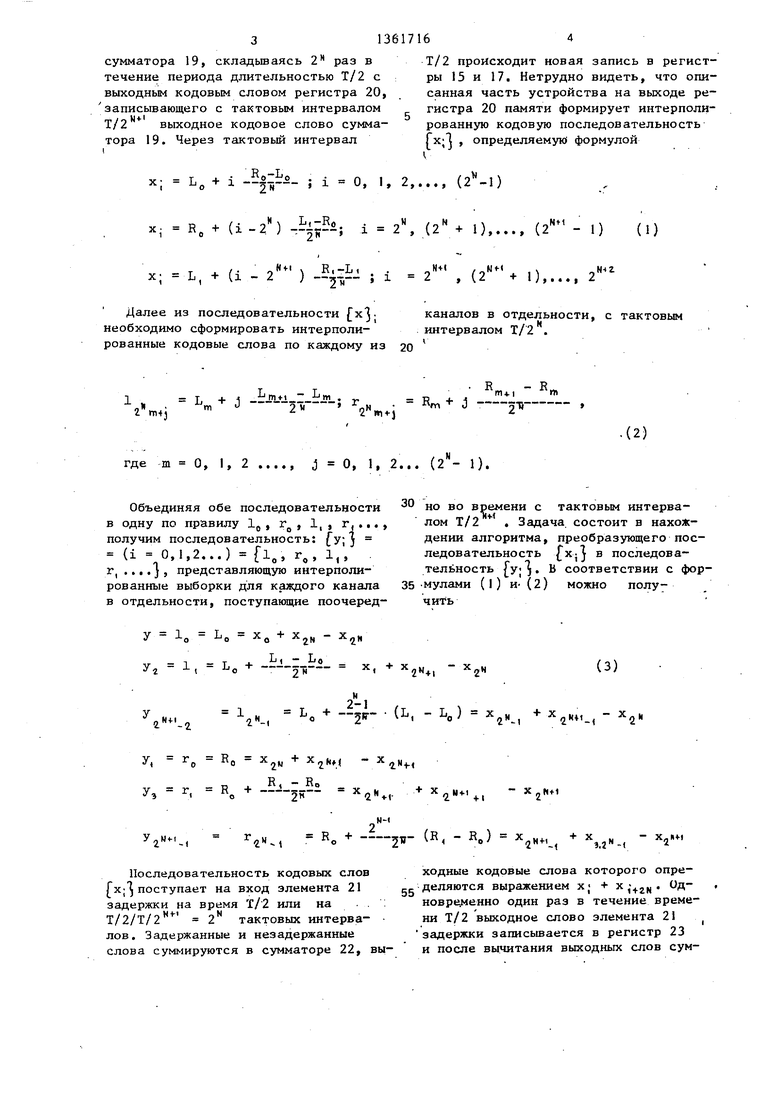

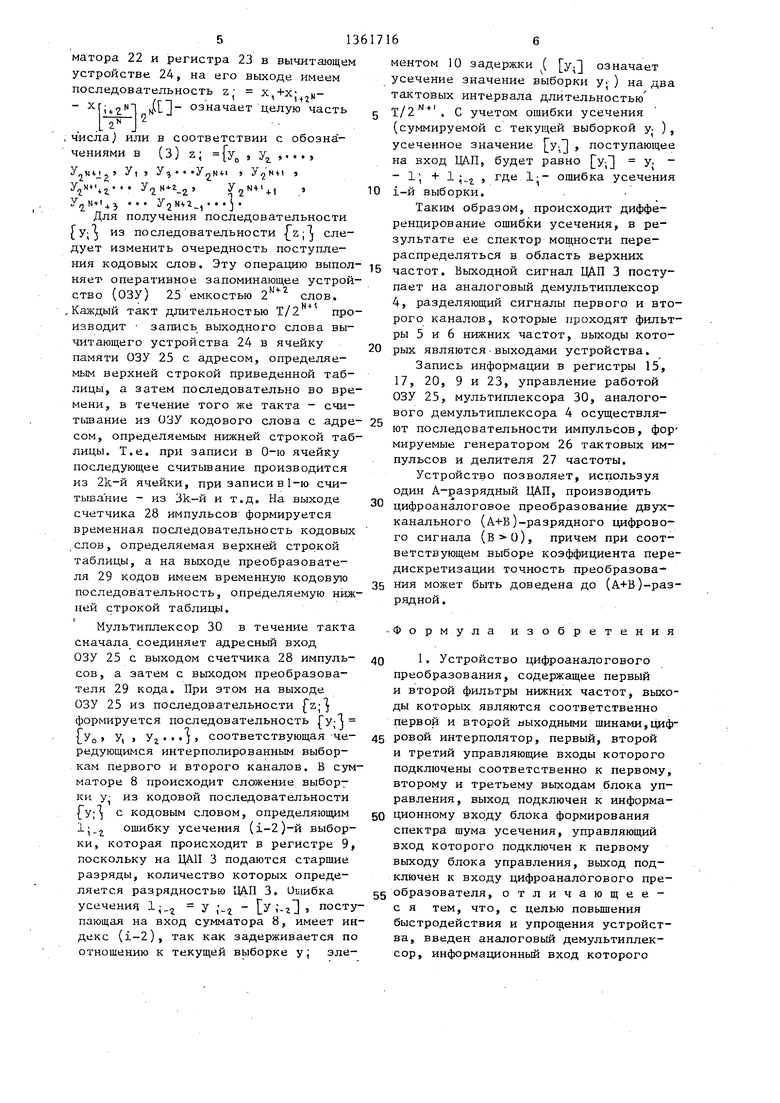

На фиг.1 приведена функциональ - ная схема устройства цифроаналогово- го преобразования; на фиг. 2 функциональная схема цифрового интерпо лятора; на фиг. 3 - функциональная схема блока управления.

Устройство цифроаналогового пре- образования (фиг.1) содержит цифро- вой интерполятор 1, блок 2 формирования спектра шума усечения, цифро- аналоговый преобразователь (ЦДП) 3, аналоговый демультиплексор 4, первый и второй фильтры 5 и 6 нижних частот, блок 7 управления. Блок 2 мо™ жет быть выполнен на сумматоре 8, регистре У, элементе 10 задержки, информационный вход цифрового интерполятора 1 является входной шиной 11, блок 7 имеет первый, второй и третий выходы 12-14.

Цифровой интерполятор 1 (фиг.2) выполнен на первом ре.гистре 15, первом вычитающем устройстве 16, втором регистре 17, делителе 18 кода, первом сумматоре 19, третьем регистре 20, элементе 21 задержки, втором сумматоре 22, четвертом регистре 23,втором вычитающем устройстве 24, оперативном запоминающем устройстве 25.

Блок 7 управления (фиг.З) выполне на генераторе 26 тактовых импульсов.

Вход 2k . 3k 2k+l 3k-H 3k-l 4k-1 0 k...

Такой преобразователь кода можно реализовать различно, например, на основе постоянного запоминающего устройства или в виде логического комбинационного устройства.

Пусть на вход устройства цифро- аналогового преобразования последовательно во времени через тактовьй интервал 1/2 поступают кодовые слова

- з-

13617162

делителе 27 частоты, счетчике 28 Htt пульсов, преобразователе 29 кода, мультиплексоре 30.

5

Устройство работает следующим образом.

В основу работы устройства положено выполнение цифровой интерполяции по линейному закону между двумя соседними выборками без локального разделения.

Для иллюстрации работы устройства примем коэффициент передискрети- зации К-2 , где N - целое положительное число. При этом коэффициент деления в делителе 18 кода равен 2, что реализуется для цифровых двоичных слов сдвигом кодового слова на N разрядов в.сторону младших разря- дов, а величины задержек в элементах 21 и 10 задержки соответственно рав- - ны Т/2 и 1/2, где Т - интервал дискретизации -выборок входной кодовой последовательности для каждого канат ла. Генератор 26 тактовых импульсов генерирует последовательность.с частотой f /Т, а делитель 27 частоты выполнен с коэффициентом деления, равным 2 , т.е. частоты следования импульсов на его выходе 2/Т. Счетчик 28 импульсов - (М+2)-разрядг ный, т.е. считает импульсы от О до (2 -1),после чего сбрасывается в нулевое состояние и происходит новый 5 цикл счета. Лреобразователь 29 двоичного кода осуществляет преобразование входного (Ы+2)-разрядного двоичного числа в вькодное (К+2)-разряд- ное число в соответствии.с таблицей, в которой k 2 (для сокращения записи числа представлены в десятич0

5

0

ной, а не в двоичной форме).

k-1 2k-1

5

первого L и второго R каналов. Одновременно с записью текущего кодового слова в регистр 15 происходит запись разности предыдущего слова, хранящегося в том же регистре с предыдущего такта, и выходного кодового слова сумматора 19 в регистр 17. Полученное слово делится на 2 в делителе 18 кода, поступает на первый вход

313617164

сумматора 19, складьшаясь 2 раз вТ/2 происходит новая запись в регисттечение периода длительностью 1/2 сры 15 и 17. Нетрудно видеть, что опивыходным кодовым словом регистра 20,санная часть устройства на выходе ре записывающего с тактовым интерваломгистра 20 памяти формирует интерполиТ/2 выходное кодовое слово сумма-рованную кодовую последовательность

тора 19. Через тактовый интервалГх; , определяемую формулой

k

х; Ь„ + i ; i О, I, 2,..., ()

X. К„ + (1-2.) 1 2 ( 1),..., ( 1) (1)

, т . /. , N R.-L, . . ,н ,,н«- . .4 „мчг х; - L, + U - / ; -ji- 2 +1;,...,2

Далее из последовательности каналов в отдельности, с тактовым необходимо сформировать интерполи- интервалом Т/2, рованные кодовые слова по каждому из 20

т т m rtl

г -т+з Rn,+ j --p ,

.(2) где m 0, 1,2 ...., j 0, 1, 2... ( 1).

Объединяя обе последовательности но во времени с тактовым интерва- в одну по правилу 1 , г , 1, , г, ... , лом Т/2 . Задача состоит в нахож- получим последовательность: f у; } дении алгоритма, преобразующего пос- (i 0,1,2...) fl, r,, 1,, . ледовательность fx; в последова- г, ....}, представляющую интерполи- тельность {у;j. В соответствии с форрованные выборки для каждого канала35 -мулами (|) и- (2) можно полу- в отдельности, поступающие поочеред- чить

У 1о Хо + XjN -

Уг 1, Ь„ + -Ь - Ь X, + X N - X н(3)

-- ° - 0 ««и , - 2

У, I D 0 Xj, + - х,ц

R R

УЭ . RO 24,- - г

2

( , RO - 2TI- (R - RO) 4H+, - .jN., - Xj

Последовательность кодовых слов ходные кодовые слова которого опре- х; поступает на вход элемента 21 gg деляются выражением х; + х , . Од- задержки на время Т/2 или на . . ; новре1менно один раз в течение време- 1/2/1/2 2 тактовых интерва- ни Т/2 выходное слово элемента 21 лов. Задержанные и незадержанные задержки записьшается в регистр 23 слова суммируются в сумматоре 22, вы- и после вычитания выходных слов сум51361716

матора 22 и регистра 23 в вычитающем устройстве 24, на его выходе имеем последовательность z; х +х

- хг

fi + 2. l означает целую часть

Г

, числа j или в соответствии с обозна - чениями в (3) Z; у„ , у,, ,.. . , У УЗ

УО

+ 1

+ 1

- ..

,,-..J .

Для получения последовательности

из последовательности следует изменить очередность поступленяет оперативное запоминающее устройство (ОЗУ) 25 емкостью 2 слов. ,Каждый такт длительностью Т/2 проментом 10 задержки ( у. означает усечение значение выборки у;) на два i42M тактовых интервала длительностью 5 . С учетом ошибки усечения

(суммируемой с текущей выборкой у. ), усеченное значение у- , поступающее на вход ЦАП, будет равно у; у. - - 1; + 1. , где - ошибка усечения 10 i-й выборки.

Таким образом, происходит дифференцирование ошибки усечения, в результате ее спектор мощности перераспределяться в область верхних ния кодовых слов. Эту операцию выпол- ,5 астот. Выходной сигнал ЦАП 3 поступает на аналоговый демультиплексор 4, разделяющий сигналы первого и второго каналов, которые проходят фильт- изводит запись, выходного слова вы- частот, вьпсоды кото- читающего устройства 24 в ячейку зо рых являютсявыходами устройства, памяти ОЗУ 25 с адресом, определяемым верхней строкой приведенной таблицы, а затем последовательно во времени, в течение того же такта - счи- тьшание из ОЗУ кодового слова с адре- 25 сом, определяемым нижней строкой таблицы. Т.е. при записи в 0-ю ячеййу последующее считывание производится из 2К-й ячейки, при записи в 1-ю считывание - из ЗК-й и т.д. На выходе счетчика 28 импульсов формируется временная последовательность кодовых слов, определяемая верхней строкой таблицы, а на выходе преобразователя 29 Кодов имеем временную кодовую

Запись информации в регистры 15, 17, 20, 9 и 23, управление работой ОЗУ 25, мультиплексора 30, аналогового демультиплексора 4 осуществляют последовательности импульсов, фор- мируемые генератором 26 тактовых импульсов и делителя 27 частоты.

Устройство позволяет, используя один А-разрядный ЦАП, производить

цифроаналоговое преобразование двух- канального (А+в)-разрядного цифрового сигнала (), причем при соответствующем выборе коэффициента передискретизации точность преобразовав

35 ния может быть доведена до ()-разпоследовательность, определяемую нижней строкой таблицы.

Мультиплексор 30 в течение такта сначала соединяет адресный вход ОЗУ 25 с выходом счетчика 28 импульсов, а затем с выходом преобразователя 29 кода. При этом на выходе ОЗУ 25 из последовательности fz; формируется последовательность

35 ния может быть доведена до ()-раз

рядной.

Формула изобретения

40 1 Устройство цифроаналогового преобразования, содержащее первый и второй фильтры нижних частот, выхо ды которых являются соответственно первой и второй выходными шинами,циф

У| Уг«« соответствующая че- 45 ровой интерполятор, первый, второй редующимся интерполированным выбор- и третий управляющие входы которого кам первого и второго каналов. В сум- подключены соответственно к первому.

маторе 8 происходит сложение выборки у из кодовой последовательности с кодовым СЛОВОМ, определяющим ошибку усечения (1-2)-й выборки, которая происходит в регистре 9, поскольку на ЦАП 3 подаются старшие разряды, количество которых определяется разрядностью ЦАП 3. Ошибка усечения 1;. у ; - поступающая на вход сумматора 8, имеет индекс (i-2), так как задерживается по отношению к текущей выборке yj элепает на аналоговый демультиплексор 4, разделяющий сигналы первого и второго каналов, которые проходят фильт- частот, вьпсоды кото- рых являютсявыходами устройства,

Запись информации в регистры 15, 17, 20, 9 и 23, управление работой ОЗУ 25, мультиплексора 30, аналогового демультиплексора 4 осуществляют последовательности импульсов, фор- мируемые генератором 26 тактовых импульсов и делителя 27 частоты.

Устройство позволяет, используя один А-разрядный ЦАП, производить

цифроаналоговое преобразование двух- канального (А+в)-разрядного цифрового сигнала (), причем при соответствующем выборе коэффициента передискретизации точность преобразовав

ния может быть доведена до ()-разрядной.

Формула изобретения

1 Устройство цифроаналогового преобразования, содержащее первый и второй фильтры нижних частот, выходы которых являются соответственно первой и второй выходными шинами,цифровой интерполятор, первый, второй и третий управляющие входы которого подключены соответственно к первому.

второму и третьему выходам блока управления , выход подключен к информационному входу блока формирования спектра шума усечения, управляющий вход которого подключен к первому выходу блока управления, выход подключен к входу цифроаналогового преобразователя, отличающее- с я тем, что, с целью повышения быстродействия и упрощения устройства, введен аналоговый демультиплексор, информационный вход которого

подключен к выходу цифроаналогового преобразователя, первый и второй выходы подключены соответственно к входам первого и второго фильтров нижних частот, управляющий вход подключен .к первому выходу блока управления, при этом информационный вход цифрового интерполятора является входной шиной.

2. Устройство по П.1, от л и - чающееся тем, что цифровой интерполятор выполнен на первом,втором, третьем и четвертом регистрах,, первом и втором вычитающих устройст- вах, делителе кода, первом и втором сумматорах, элементе задержки, оперативном запоминающем устройстве, выход которого является выходом цифрового интерполятора, адресный вход является третьим управляющим входом цифрового интерполятора, вход записи- чтения объединен с управляющим входом третьего регистра и является первым управляющим входом цифрового ин ерполятора, информационный вход оперативного запоминающего устройства подключен к выходу второго вычитающего устройства, вход уменьшаемого которого подключен к выходу второго сумма- тора, вход вычитаемого подключен к выходу четвертого регистра, управляющий вход четвертого регистра объединен с управляющими входами первого и второго регистров и является вторым управляющим входом цифрового интерполятора, информационный вход объединен с первым входом второго сумматора и подключен к выходу элемента задержки, вход которого объединен с вторым входом второго сумматора и первым входом первого сумматора и подключен к второму выходу третьего регистра, информационный вход которого объединен с входом вычитаемого первого вычитающего устройства и подключен к выходу первого сумматора, второй вход которого подключен к Зы- ходу делителя кода, вход которого подключен к выходу второго регистра, информационный вход которого подключен к выходу первого вычитающего устройства, вход уменьшаемого которого подключен к выходу первого регистра, информационный, вход которого является информационным входом цифрового интерполятора.

3. Устройство по П.1, отличающееся тем, что блок управления выполнен на генераторе тактовых импульсов, делителе частоты, счетчике импульсов, преобразователе кода и мультиплексоре, выход которого является третьим выходом блока уп-. равления, первый вход подключен к выходу преобразоваЧ-еля кода, второй вход объединен с входом преобразователя кода и подключен к выходу счетчика импульсов, вход которого объединен с входом делителя частоты, подключен к выходу генератора тактовых импульсов и является первым выходом блока управления, выход делителя частоты является вторым выходом блока управления.

Ik 12

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь случайных сигналов | 1990 |

|

SU1732419A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1300542A1 |

| Статистический анализатор | 1989 |

|

SU1695328A1 |

| Формирователь повторяющихся частотно-модулированных сигналов | 1988 |

|

SU1555806A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221755A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326494C1 |

Изобретение относится к автоматике и вычислительной технике, предназначено для дифроаналогового преобразования двух цифровых сигналов и может быть использовано в цифровых стереофонических устройствах воспроизведения звука, в системах связи с импульсно-кодовой модуляцией. Цель - повьпиение быстродействия и упрощение устройства. Устройство содержит циф ровой интерполятор 1, блок 2 формирования спектра шума усечения, цифро- аналоговый преобразователь 3, аналоговый демультиплексор 4, первый и второй фильтры 5,6 нижних частот, блок 7 упр.авления. Блок 2 может быть выполнен на сумматоре 8, регистре 9, элементе 10 задержки. Цель достигается за счет выполнения цифровой интерполяции по линейному закону между двумя соседними выборками без пока- нального разделения. 2 з,п, ф-лы, 3 ил,, 1 табл. (О 11 : 35

Редактор Е.Папп

Составитель В.Першиков

Техред М.Дидык Корректор В.Гирняк

Заказ 6303/56 Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб,,

Производственно полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Гнатек Ю.Р, Справочник по цифро- аналоговым и | |||

| аналогоцифровым: преобразователям | |||

| - М.: Радио и связь, 1982, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Госдхард и др | |||

| Цифроаналоговое преобразование в проигрывателе Компакт Диск | |||

| - Philips | |||

| Tech | |||

| Rev., 1982, т.40, , с | |||

| Способ прикрепления барашков к рогулькам мокрых ватеров | 1922 |

|

SU174A1 |

Авторы

Даты

1987-12-23—Публикация

1985-04-02—Подача