1

Изобретение относится к измерительной технике и может быть использовано в сетевых измерительных системах и локальных контрольно-измерительных сетях при испытаниях быстродействующих и высокоточных аналого-цифровых преобразователей (АЦП).

Цель изобретения - повышение точности.

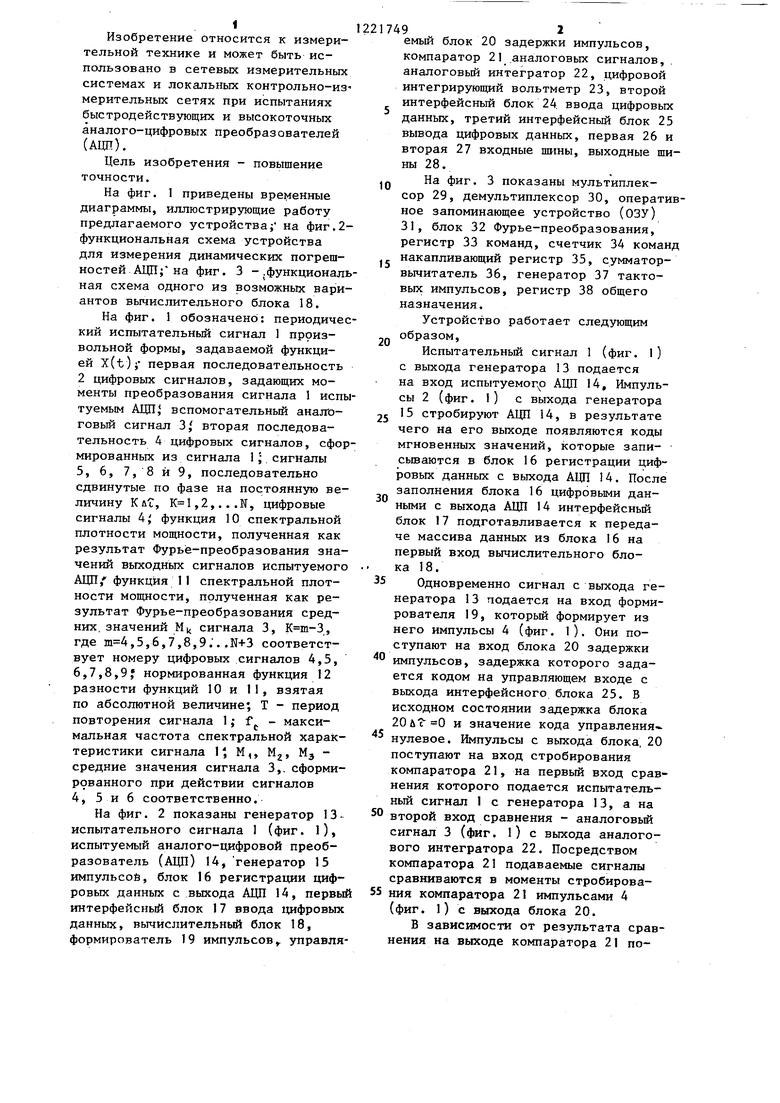

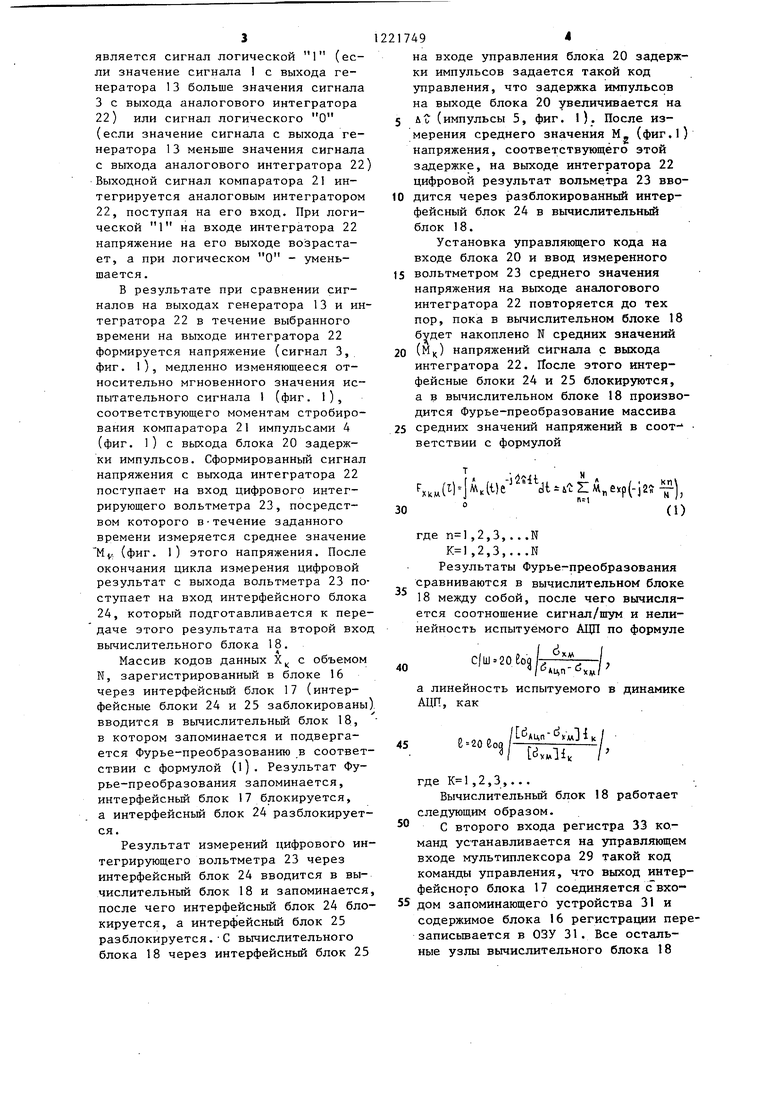

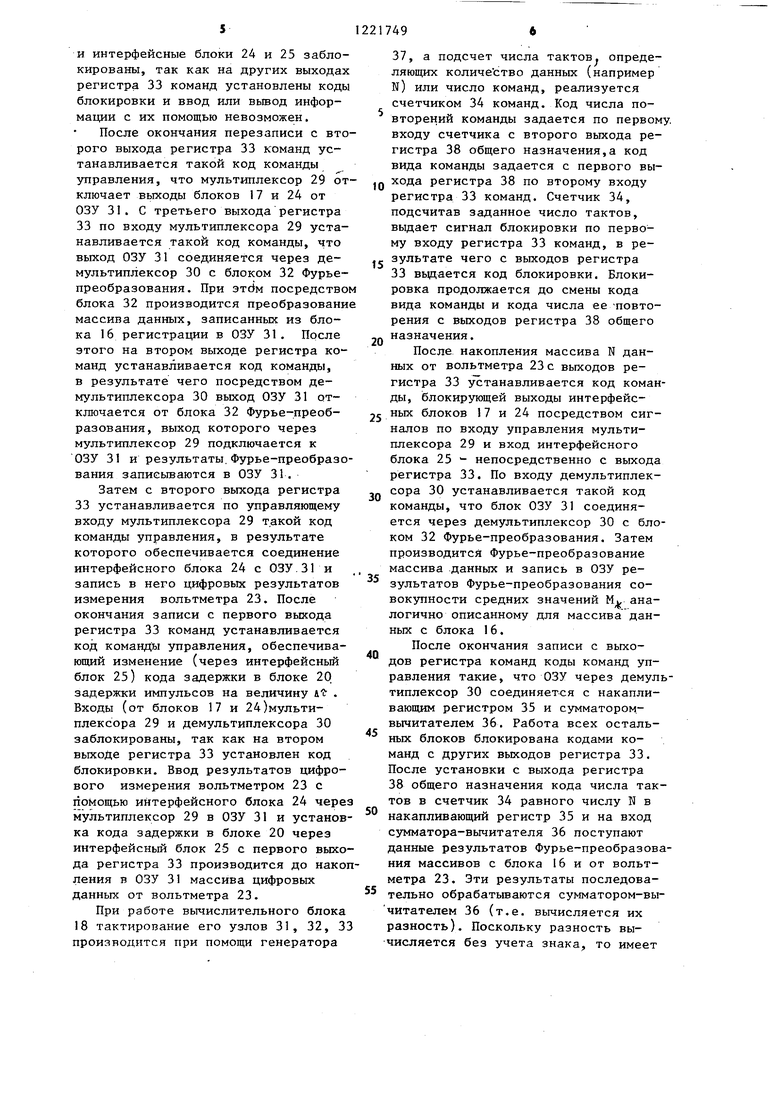

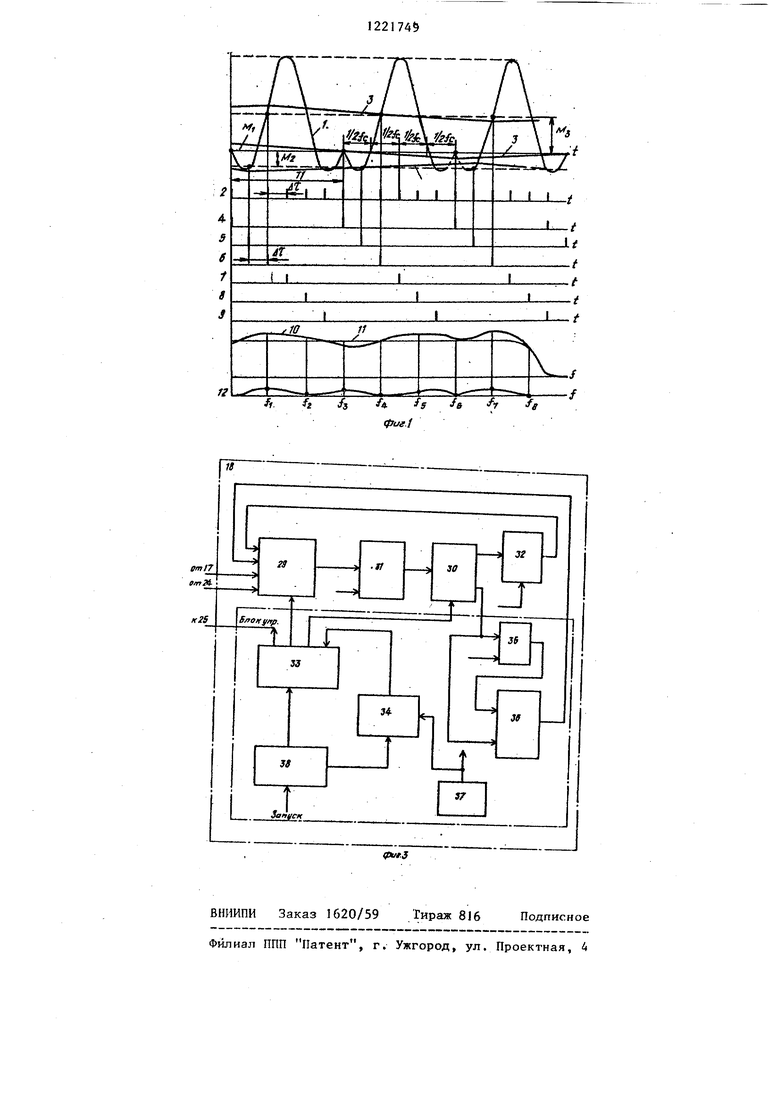

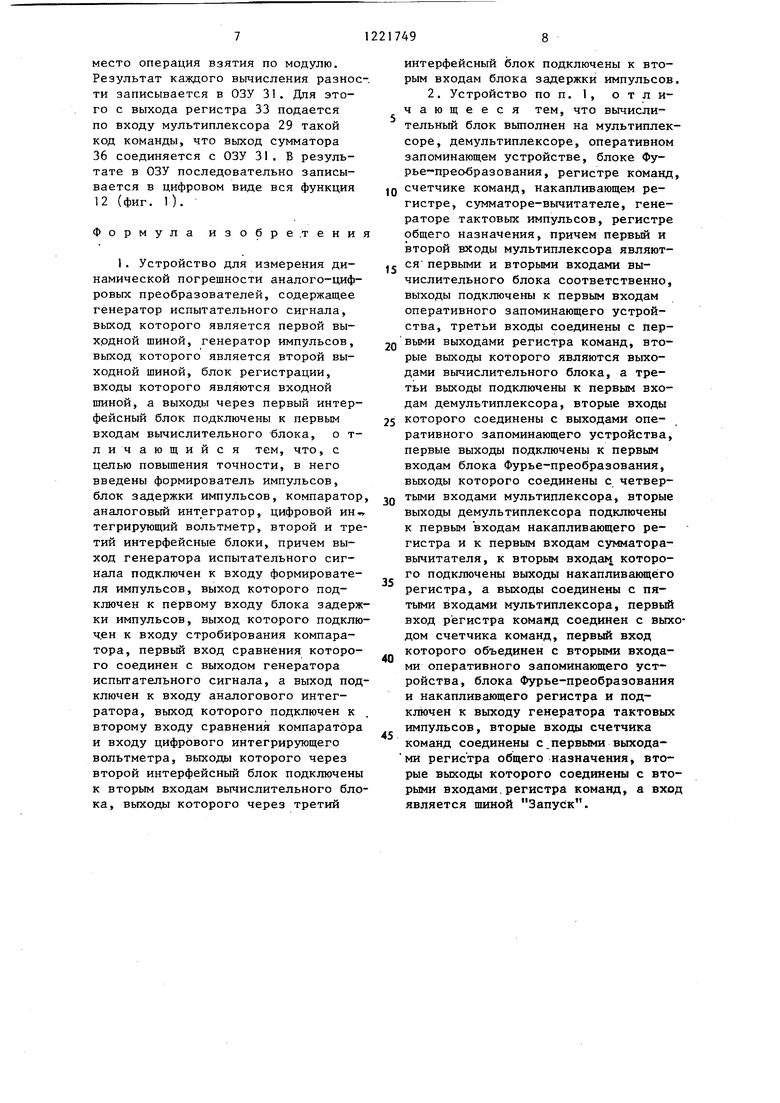

На фиг. I приведены временные диаграммы, иллюстрирующие работу предлагаемого устройства; на фиг.2- функциональная схема устройства для измерения динамических погрешностей АЦП; на фиг. 3 -.функциональная схема одного из возможных вариантов вычислительного блока 18.

На фиг. 1 обозначено: периодический испытательный сигнал 1 произвольной формы, задаваемой функцией X(t)i первая последовательность 2 цифровых сигналов, задающих моменты преобразования сигнала I испытуемым АЦП вспомогательный аналоговый сигнал 3, вторая последовательность 4 цифровых сигналов, сформированных из сигнала 1) сигналы 5, 6, 7, 8 и 9, последовательно сдвинутые по фазе на постоянную величину К дТ, ,2,...N, цифровые сигналы 4 функция 10 спектральной плотности мощности, полученная как результат Фурье-преобразования значений выходных сигналов испытуемого АЦП, функция 11 спектральной плотности мощности, полученная как результат Фурье-преобразования средних, значений Мц сигнала 3, , где ,5,6,7,8,9.. ,N+3 соответствует номеру цифровых сигналов 4,5, 6,7,8,9 нормированная функция 12 разности функций 10 и 11, взятая по абсолютной величине; Т - период повторения сигнала 1 , f - максимальная частота спектральной характеристики сигнала 1, М,, М, Мд - средние значения сигнала 3,, сформированного при действии сигналов 4, 5 и 6 соответственно.

На фиг. 2 показаны генератор 13- испытательного сигнала 1 (фиг. 1), испытуемый аналого-цифровой преобразователь (АЦП) 14, генератор 15 импульсой, блок 16 регистрации цифровых данных с выхода АЦП 14, первь интерфер сный блок 17 ввода цифровых данных, вычислительный блок 18, формирователь 19 импульсов,, управля15

17492

емый блок 20 задержки импульсов,

компаратор 21 аналоговых сигналов, аналоговый интегратор 22, цифровой интегрирующий вольтметр 23, второй интерфейсный блок 24, ввода цифровьпс данных, третий интерфейсный блок 25 вывода цифровых данньк, первая 26 и вторая 27 входные шшы, выходные шины 28.

.Q На фиг. 3 показаны мультиплексор 29, демультиплексор 30, оператиное запоминающее устройство (ОЗУ) 31, блок 32 Фурье-преобразования, регистр 33 команд, счетчик 34 коман накапливающий регистр 35, сумматор- вычитатель 36, генератор 37 тактовых импульсов, регистр 38 общего назначения.

Устройство работает следующим

20 образом.

Испытательный сигнал 1 (фиг. I) с выхода генератора 13 подается на вход испытуемог о АЦП 14, Импульсы 2 (фиг. 1) с выхода генератора

25 15 стробируют АЦП 14, в результате чего на его выходе появляются коды мгновенных значений, которые запи- сьшаются в блок 16 регистрации цифровых данных с выхода АЦП I4. После заполнения блока 16 цифровыми данными с выхода АЦП 14 интерфейсный блок 17 подготавливается к передаче массива данных из блока 16 на первый вход вычислительного блока 18.

35 Одновременно сигнал с выхода генератора 13 подается на вход формирователя 19, который формирует из него импульсы 4 (фиг. 1). Они поступают на вход блока 20 задержки

импульсов, задержка которого задается кодом на управляющем входе с выхода интерфейсного, блока 25. В исходном состоянии задержка блока 20л с 0 и значение кода управления

нулевое. Импульсы с выхода блока, 20 поступают на вход стробирования компаратора 21, на первый вход сравнения которого подается испытательный сигнал 1 с генератора 13, а на

50 второй вход сравнения - аналоговый сигнал 3 (фиг. О с выхода аналогового интегратора 22. Посредством компаратора 21 подаваемые сигналы сравниваются в моменты стробирова55 НИН компаратора 21 импульсами 4 (фиг. 1) с выхода блока 20.

В зависимости от результата сравнения на выходе компаратора 21 по30

3

является сигнал логической 1 (если значение сигнала 1 с выхода генератора 13 больше значения сигнала 3 с выхода аналогового интегратора 22) или сигнал логического О (если значение сигнала с выхода генератора 13 меньше значения сигнала с выхода аналогового интегратора 22 Выходной сигнал компаратора 21 интегрируется аналоговым интегратором 22, поступая на его вход. При логической 1 на входе интегратора 22 напряжение на его выходе возрастает, а при логическом О - уменьшается .

В результате при сравнении сигналов на выходах генератора 13 и интегратора 22 в течение выбранного времени на выходе интегратора 22 формируется напряжение (сигнал 3, фиг. l), медленно изменяющееся относительно мгновенного значения испытательного сигнала 1 (фиг. 1), соответствующего моментам стробиро- вания компаратора 21 импульсами 4 (фиг. 1) с выхода блока 20 задержки импульсов. Сформированный сигнал напряжения с выхода интегратора 22 поступает на вход цифрового интег- рирующего вольтметра 23, посредством которого в-течение заданного времени измеряется среднее значение M,. (фиг. 1) этого напряжения. После окончания цикла измерения цифровой результат с выхода вольтметра 23 поступает на вход интерфейсного блока 24, который подготавливается к передаче этого результата на второй вхо вычислительного блока 18.

4

Массив кодов данных Х. с объемом N, зарегистрированный в блоке 16 через интерфейсный блок 17 (интерфейсные блоки 24 и 25 заблокированы вводится в вычислительный блок 18, в котором запоминается и подвергается Фурье-преобразованию в соответствии с формулой (l). Результат Фурье-преобразования запоминается, интерфейсный блок 17 блокируется, а интерфейсный блок 24 разблокируется.

Результат измерений цифрового интегрирующего вольтметра 23 через интерфейсный блок 24 вводится в вычислительный блок 18 и запоминается после чего интерфейсньш блок 24 блокируется, а интерфейсный блок 25 разблокируется.-С вычислительного блока 18 через интерфейсный блок 25

21749Л

на входе управления блока 20 задержки импульсов задается такой код управления, что задержка импульсов на выходе блока 20 увеличивается на

5 if (импульсы 5, фиг. ). После измерения среднего значения М. (фиг.1) напряжения, соответствующего этой задержке, на выходе интегратора 22 цифровой результат вольметра 23 вво10 дится через разблокированный интерфейсный блок 24 в вычислительный блок 18.

Установка управляющего кода на входе блока 20 и ввод измеренного

15 вольтметром 23 среднего значения напряжения на выходе аналогового интегратора 22 повторяется до тех пор, пока в вычислительном блоке 18 будет накоплено N средних значений

20 (Мц) напряжений сигнала с выхода интегратора 22. После зтого интерфейсные блоки 24 и 25 блокируются, а в вычислительном блоке 18 производится Фурье-преобразование массива

25 средних значений напряжений в соот- ветствии с формулой

XkW

(1)|мД1).2:м„ехр(-12),

(1)

35

где n,2,3,...N ,2,3,...N

Результаты Фурье-преобразования сравниваются в вычислительном блоке 18 между собой, после чего вычисляется соотношение сигнал/шум и нелинейность испытуемого АЦП по формуле

. ., .-/. О / АЦп- у /

а линейность испытуемого в динамике

АЦП, как

45

civMlf,

где ,2,3,...

Вычислительный блок 18 работает следующим образом.

С второго входа регистра 33 команд устанавливается на управляющем входе мультиплексора 29 такой код команды управления, что выход интерфейсного блока 17 соединяется с вхо55 дом запоминающего устройства 31 и содержимое блока 16 регистрации пере записьшается в ОЗУ 31. Все остальные узлы вычислительного блока 18

и интерфейсные блоки 24 и 25 заблокированы, так как на других выходах регистра 33 команд установлены коды блокировки и ввод или вьгоод информации с их помощью невозможен.

После окончания перезаписи с второго выхода регистра 33 команд устанавливается такой код команды управления, что мультиплексор 29 отключает выходы блоков 17 и 24 от ОЗУ 31. С третьего выхода регистра 33 по входу мультиплексора 29 устанавливается такой код команды, что выход ОЗУ 31 соединяется через де- мультиплексор 30 с блоком 32 Фурье- преобразования. При этЬм посредством блока 32 производится преобразование массива данных, записанных из блока 16 регистрации в ОЗУ 31. После этого на втором выходе регистра команд устанавливается код команды, в результате чего посредством де- мультиплексора 30 выход ОЗУ 31 отключается от блока 32 Фурье-преобразования, выход которого через мультиплексор 29 подключается к ОЗУ 31 и результаты.Фурье-преобразования записьгоаются в ОЗУ 31.

Затем с второго выхода регистра 33 устанавливается по управляющему входу мультиплексора 29 такой код команды управления, в результате которого обеспечивается соединение интерфейсного блока 24 с ОЗУ.31 и запись в него цифровых результатов измерения вольтметра 23. После окончания записи с первого выхода регистра 33 команд устанавливается код команды управления, обеспечивающий изменение (через интерфейсный блок 25) кода задержки в блоке 2Q задержки импульсов на величину Af . Входы (от блоков 17 и 24)мульти- плексора 29 и демультиплексора 30 заблокированы, так как на втором выходе регистра 33 установлен код блокировки. Ввод результатов цифрового измерения вольтметром 23 с помощью интерфейсного блока 24 через мультиплексор 29 в ОЗУ 31 и установка кода задержки в блоке 20 через интерфейсный блок 25 с первого выхода регистра 33 производится до накопления в ОЗУ 31 массива цифровых данных от вольтметра 23.

При работе вьиислительного блока 18 тактирование его узлов 31, 32, 33 производится при помощи генератора

0

37, а подсчет числа тактов определяющих количе ство данных (например N) или число команд, реализуется счетчиком 34 команд. Код числа повторений команды задается по первому, входу счетчика с второго выхода регистра 38 общего назначения,а код вида команды задается с первого вы- JQ хода регистра 38 по второму входу регистра 33 команд. Счетчик 34, подсчитав заданное число тактов, вьщает сигнал блокировки по первому входу регистра 33 команд, в ре- г зультате чего с выходов регистра 33 вьщается код блокировки. Блокировка продолжается до смены кода вида команды и кода числа ее повторения с выходов регистра 38 общего назначения.

После накопления массива N данных от вольтметра 23 с выходов регистра 33 устанавливается код команды, блокирующей выходы интерфейс5 ных блоков 17 и 24 посредством сигналов по входу управления мультиплексора 29 и вход интерфейсного блока 25 непосредственно с выхода регистра 33. По входу демультиплекQ сора 30 устанавливается такой код команды, что блок ОЗУ 31 соединяется через демультиплексор 30 с блоком 32 Фурье-преобразования. Затем производится Фурье-преобразование массива данных и запись в ОЗУ результатов Фурье-преобразования совокупности средних значений М аналогично описанному для массива данных с блока 16.

После окончания записи с выходов регистра команд коды команд управления такие, что ОЗУ через демультиплексор 30 соединяет-ся с накапливающим регистром 35 и сумматором- вычитателем 36. Работа всех остальных блоков блокирована кодами команд с других выходов регистра 33. После установки с выхода регистра 38 общего назначения кода числа тактов в счетчик 34 равного числу И в

накапливающий регистр 35 и на вход сумматора-вьтитателя 36 поступают данные результатов Фурье-преобразования массивов с блока 16 и от вольтметра 23. Эти результаты последовательно обрабатываются сумматором-вы- читателем 36 (т.е. вычисляется их разность). Поскольку разность вычисляется без учета знака, то имеет

5

место операция взятия по модулю. Результат каждого вычисления разности записывается в ОЗУ 31. Для этого с выхода регистра 33 подается по входу мультиплексора 29 такой код команды, что выход сумматора 36 соединяется с ОЗУ 31. В результате в ОЗУ последовательно записывается в цифровом виде вся функция 12 (фиг. 1 ).

Формула изобретени

1. Устройство для измерения динамической погрешности аналого-цифровых преобразователей, содержащее генератор испытательного сигнала, выход которого является первой вы- хрдной шиной, генератор импульсов, выход которого является второй выходной шиной, блок регистрации, входы которого являются входной шиной, а выходы через первый интерфейсный блок подключены к первым входам вычислительного блока, о т- ли чающийся тем, что, с целью повышения точности, в него введены формирователь импульсов, блок задержки импульсов, компаратор аналоговый интегратор, цифровой ин., тегрирующий вольтметр, второй и третий интерфейсные блоки, причем выход генератора испытательного сигнала подключен к входу формирователя импульсов, выход которого подключен к первому входу блока задержки импульсов, выход которого подключен к входу стробирования компаратора, первый вход сравнения которого соединен с выходом генератора испытательного сигнала, а выход подключен к входу аналогового интегратора, выход которого подключен к второму входу сравнения компаратора и входу цифрового интегрирующего вольтметра, выходы которого через второй интерфейсный блок подключены к вторым входам вычислительного блока, выходы которого через третий

o

5

0

5

0

5

0

5

интерфейсный блок подключены к вторым входам блока задержки импульсов. 2. Устройство по п. 1, отличающееся тем, что вычислительный блок выполнен на мультиплексоре, демультиплексоре, оперативном запоминающем устройстве, блоке Фурье-преобразования, регистре команд, счетчике команд, накапливающем регистре, сумматоре-вычитателе, генераторе тактовых импульсов, регистре общего назначения, причем первый и второй входы мультиплексора являются первыми и вторыми входами вычислительного блока соответственно, выходы подключены к первым входам оперативного запоминающего устройства, третьи входы соединены с пер выми выходами регистра команд, вторые выходы которого являются выходами вычислительного блока, а третьи выходы подключены к первым входам демультиплексора, вторые входы которого соединены с выходами оперативного запоминающего устройства, первые выходы подключены к первым входам блока Фурье-преобразования, выходы которого соединены с четвертыми входами мультиплексора, вторые выходы демультиплексора подключены к первым входам накапливающего регистра и к первым входам сумматора- вычитателя, к вторым входам которого подключены выходы накапливающего регистра, а выходы соединены с пятыми входами мультиплексора, первый вход регистра команд соединен с выходом счетчика команд, первый вход которого объединен с вторыми входами оперативного запоминающего устройства, блока Фурье-преобразования и накапливающего регистра и подключен к выходу генератора тактовых импульсов, вторые входы счетчика команд соединены с.первыми выхода ми регистра общего назначения, вторые выходы которого соединены с вторыми входами.регистра команд, а вход является шиной Запуск.

гг

.Y

Запуск

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| Цифроаналоговая система сбора и обработки информации | 1986 |

|

SU1363271A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2256937C1 |

| СИСТЕМА КАЛИБРОВКИ УСТРОЙСТВА ИЗМЕРЕНИЯ И КОНТРОЛЯ ВИБРАЦИИ, УПРАВЛЯЕМОГО МИКРОПРОЦЕССОРОМ | 2006 |

|

RU2313773C1 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1561075A1 |

Изобретение относится к измерительной технике и может быть использовано в сетевых измерительных системах и локальных контрольно-измерительных сетях при испытаниях быстродействующих и высокоточных аналого-цифровых преобразователей (АЦП). Изобретение позволяет повысить точность за счет того, что в устройство, содержащее генератор 13 испытательного сигнала, генератор 15 импульсов, блок 16 регистрации, первьй интерфейсный блок 17, вычислительный блок 18, введены формирователь 19 импульсов, блок 20 задержки импульсов, компаратор 21, аналоговый интегратор 22, цифровой интегрирующий вольтметр 23, второй 24 и третий 25 интерфейсные блоки, что, в свою очередь, позволило более четко вычислить основные параметры, характеризующие дийами- ческие характеристики АЦП. 1 з.п. ф-лы, 3 ил. Q 9 (Л с

| Способ измерения динамической погрешности аналого-цифровых преобразователей и устройство для его реализации | 1981 |

|

SU999154A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Test a/d converters digitally, electronic Design 25 | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

Авторы

Даты

1986-03-30—Публикация

1984-03-19—Подача