Изобретение относится к области автоматики и измерительной техники и может быть использовано в системах контроля телевизионных устройств.

Цель изобретения - повышение точности формирования телевизионного сигнала.

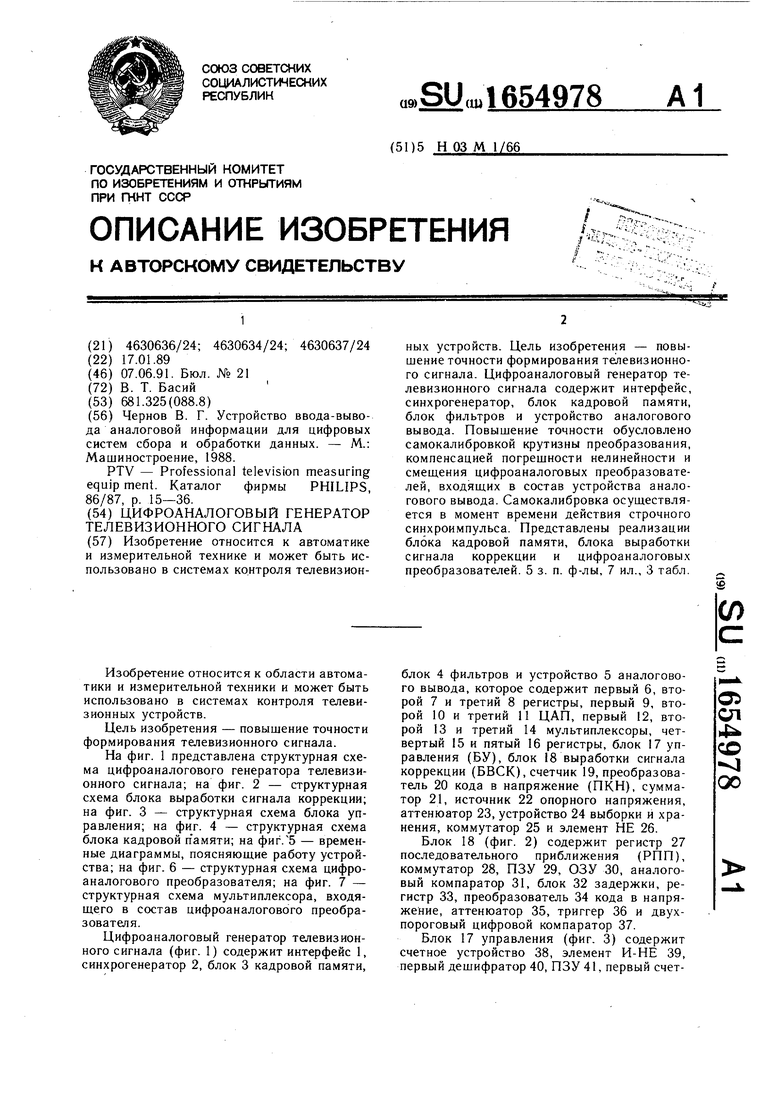

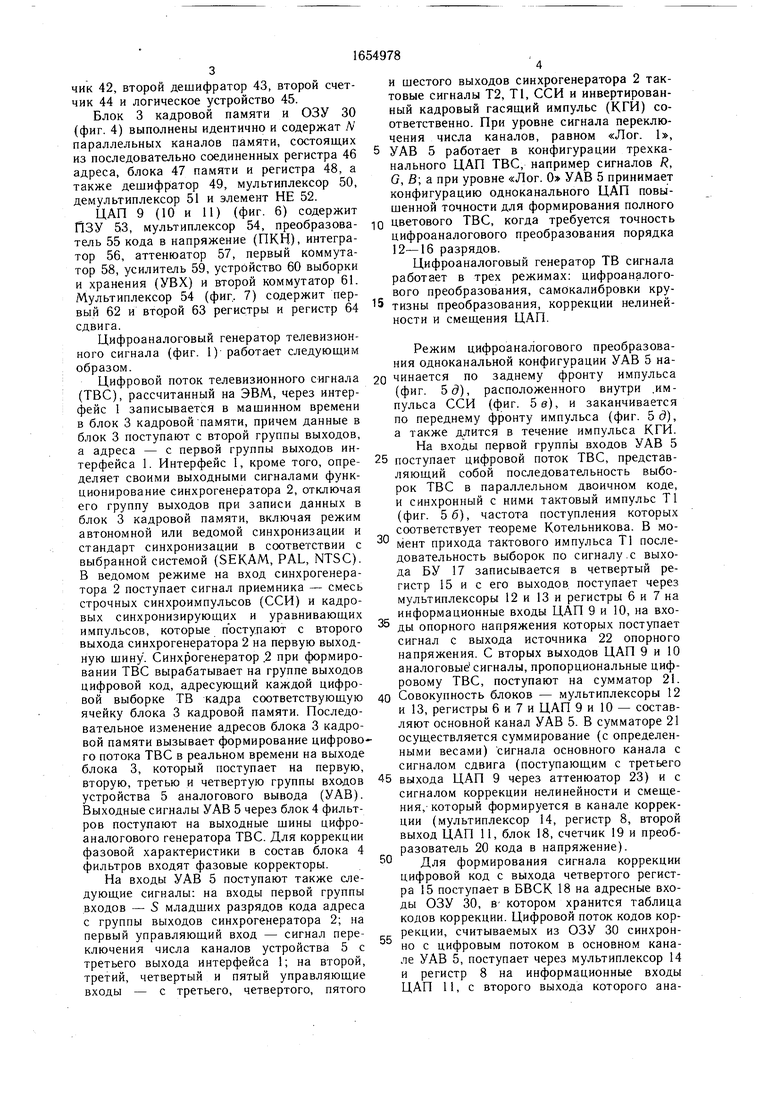

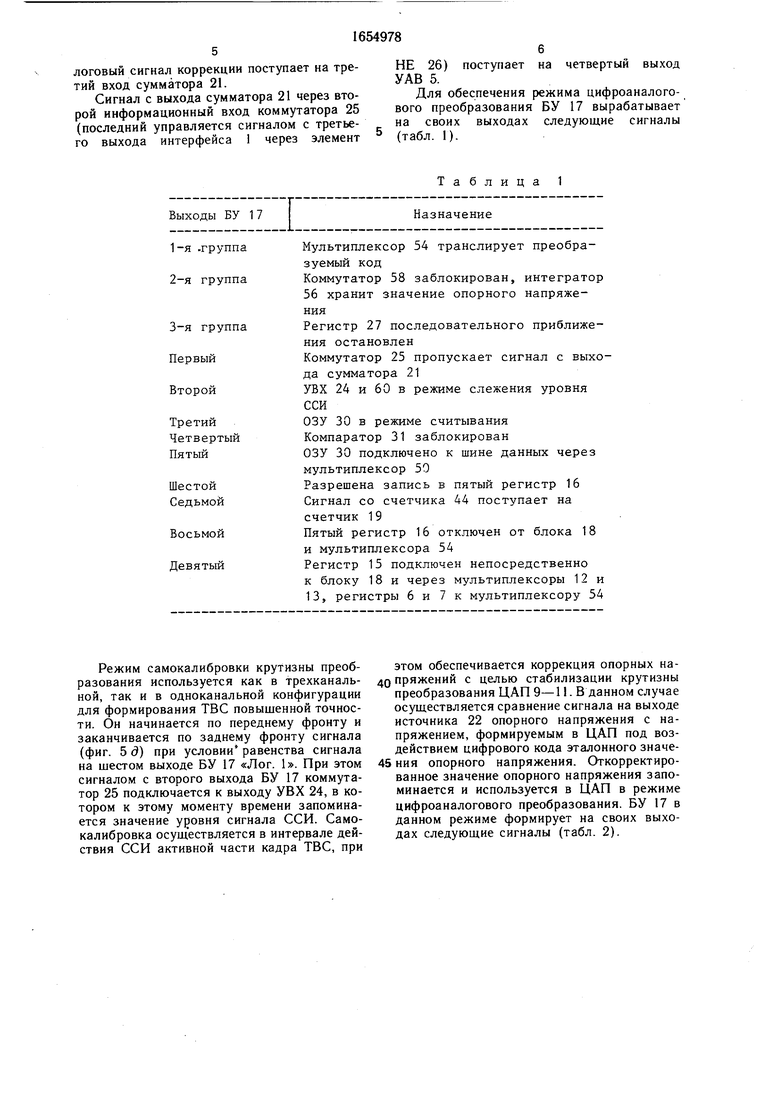

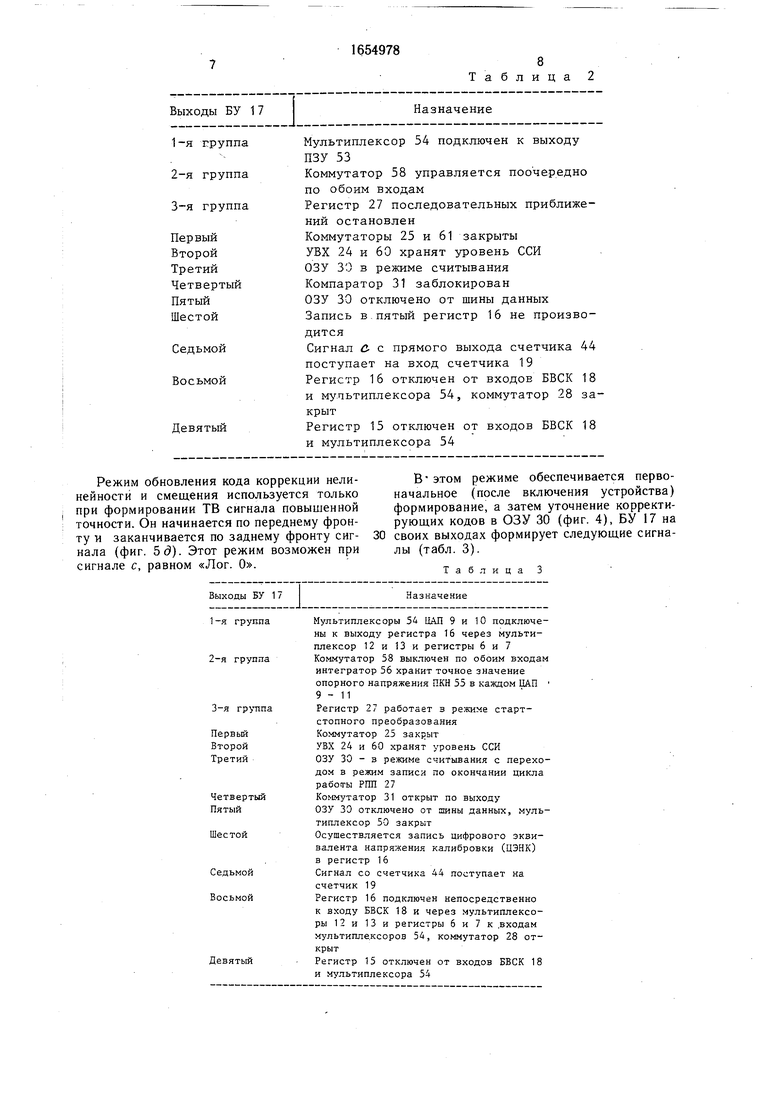

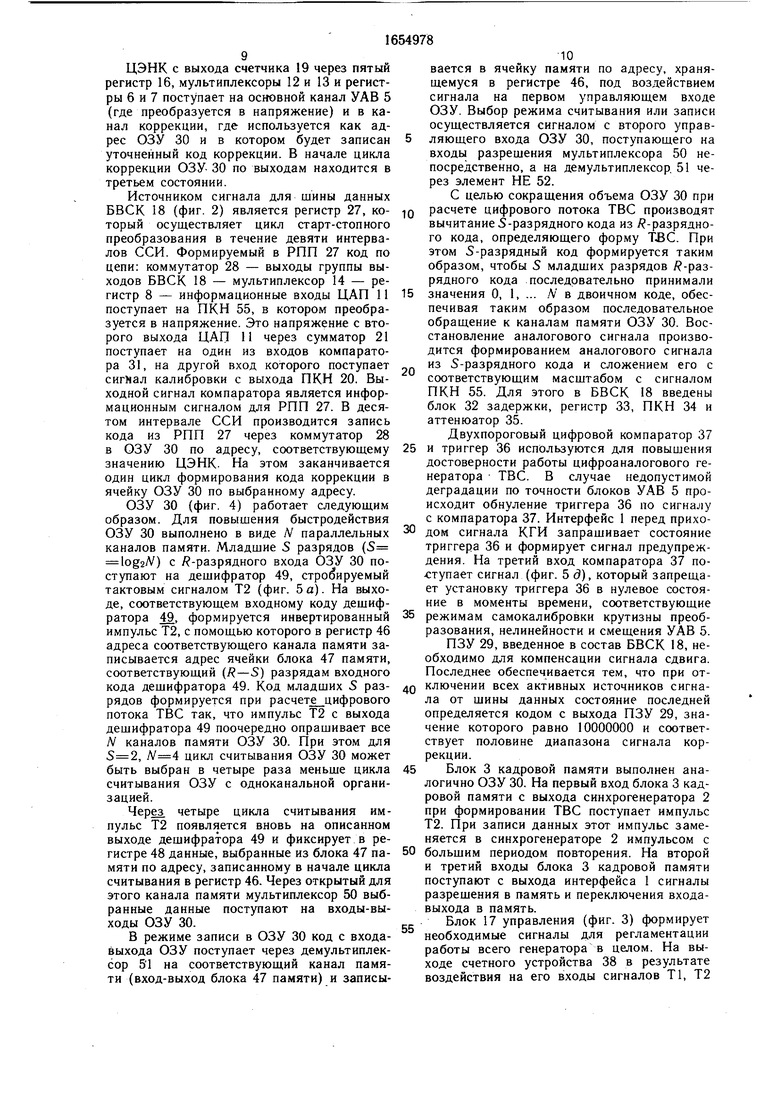

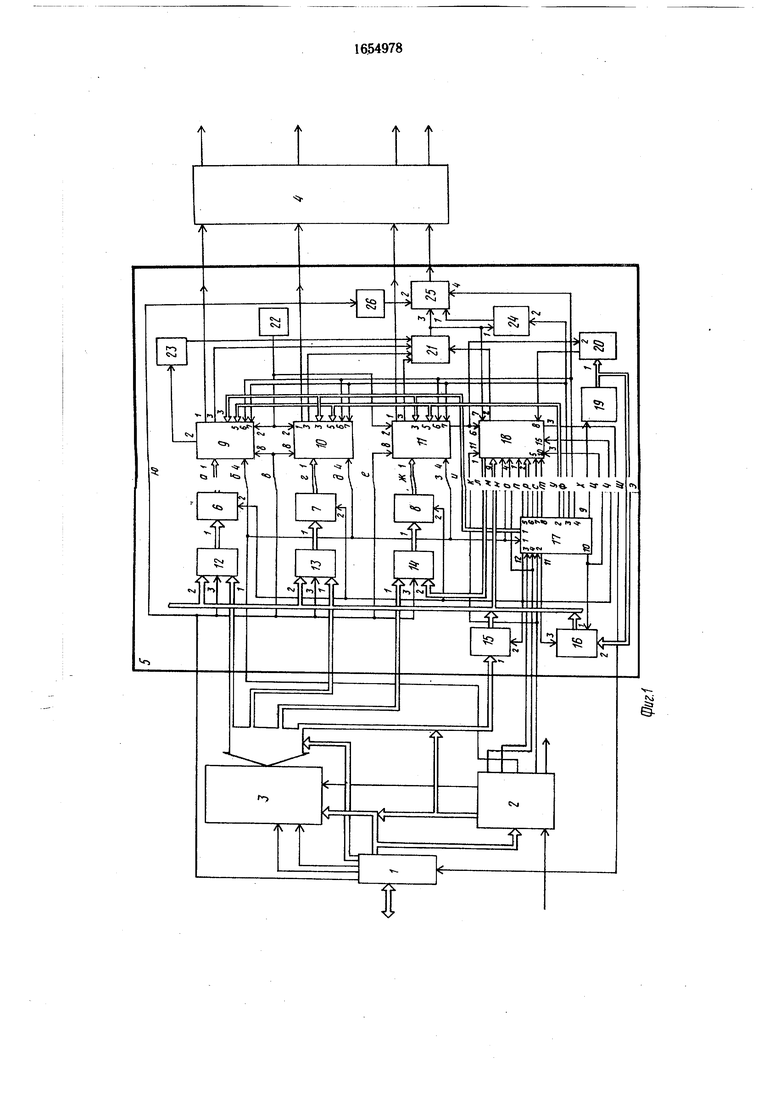

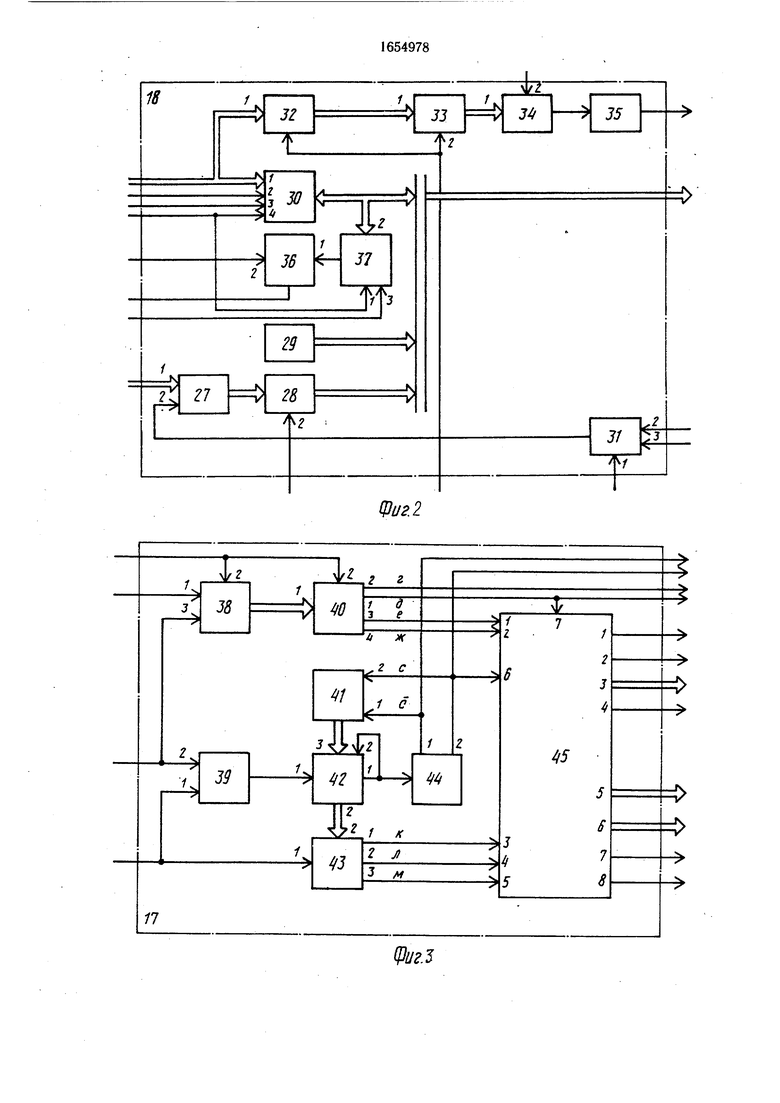

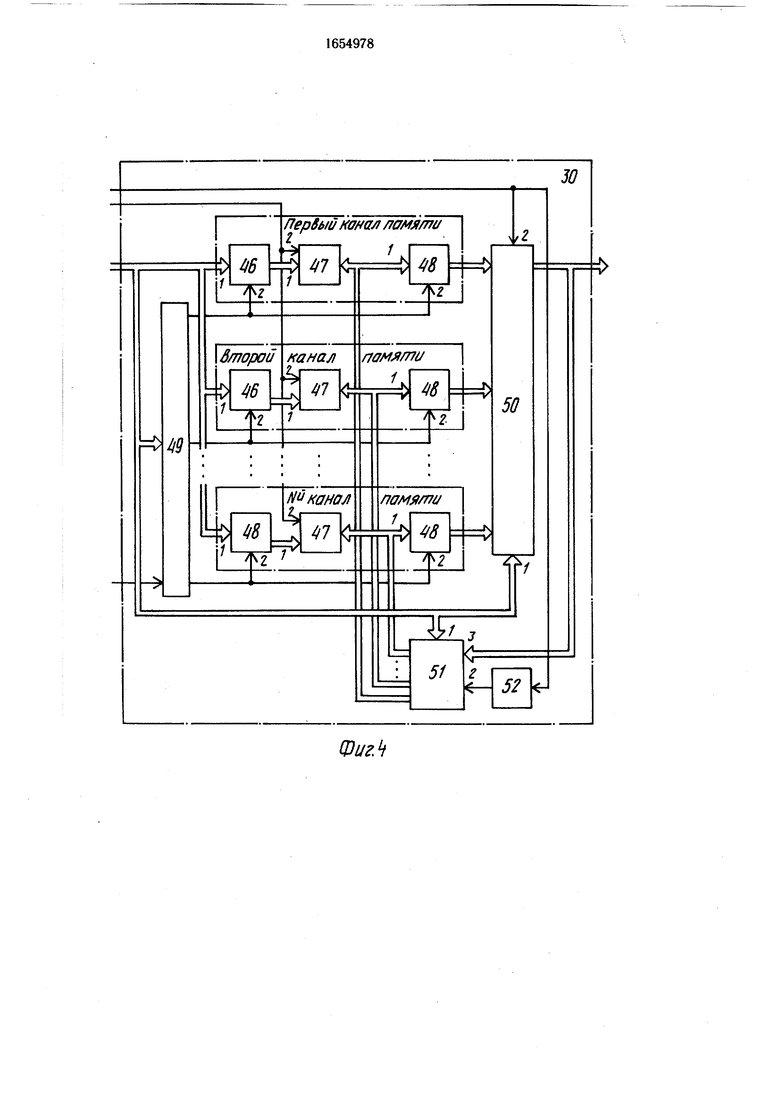

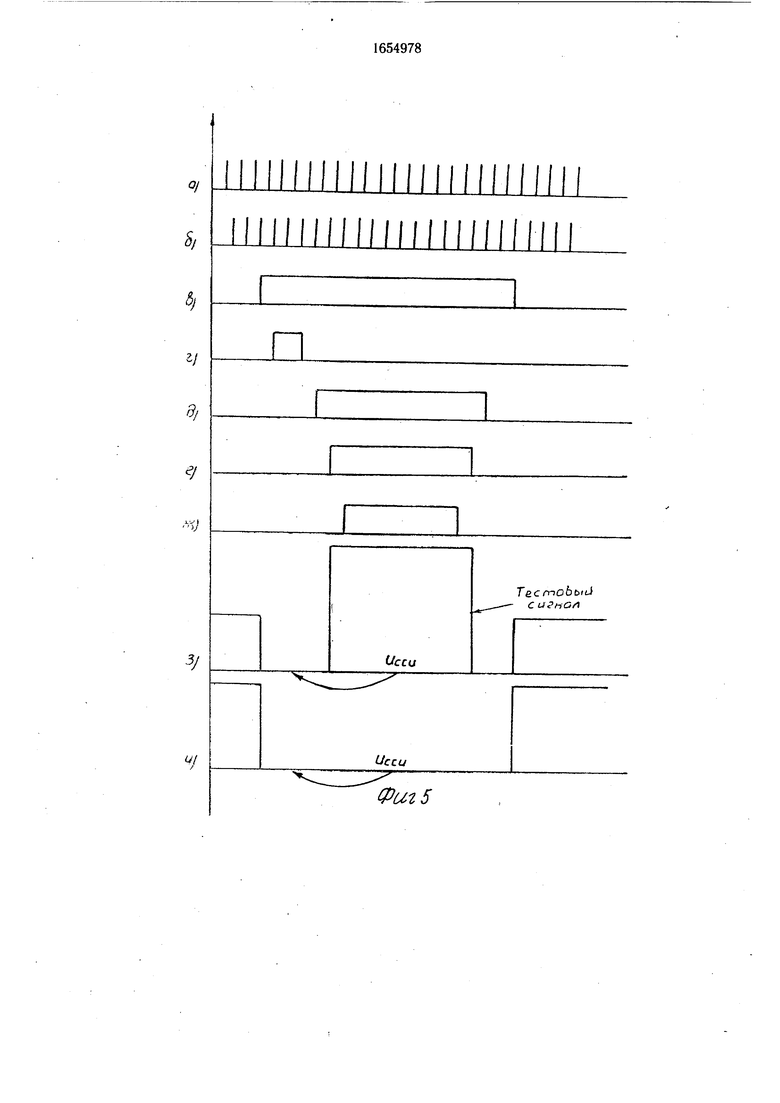

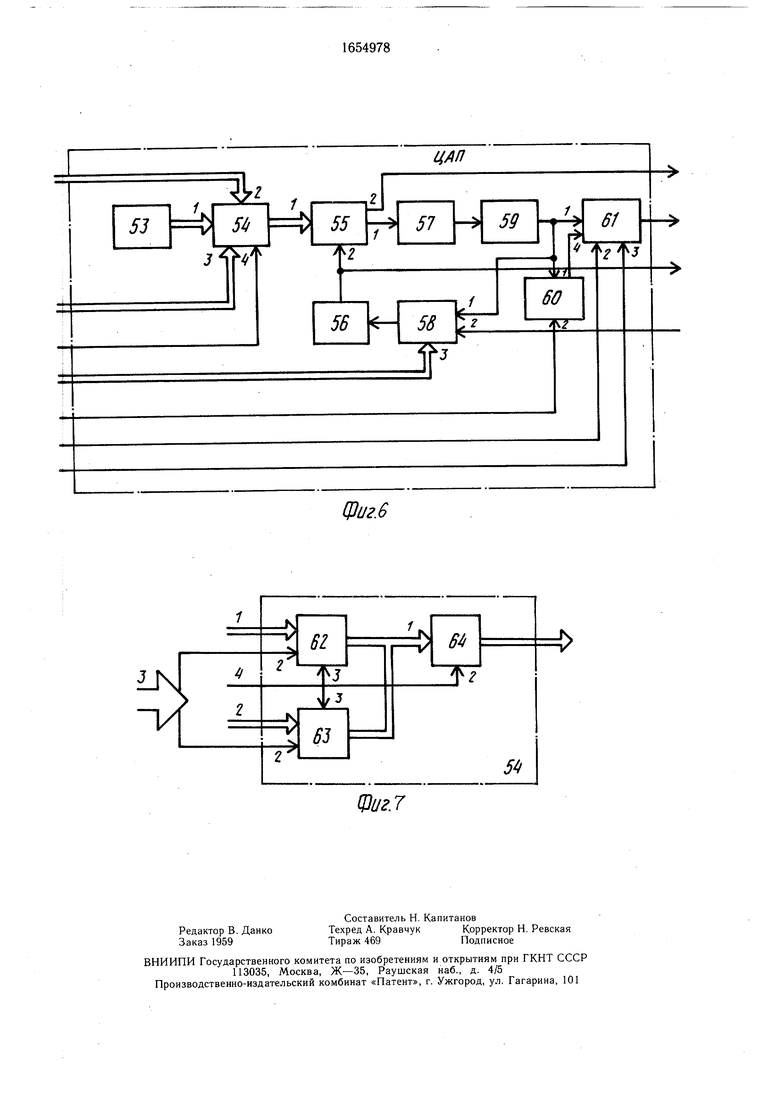

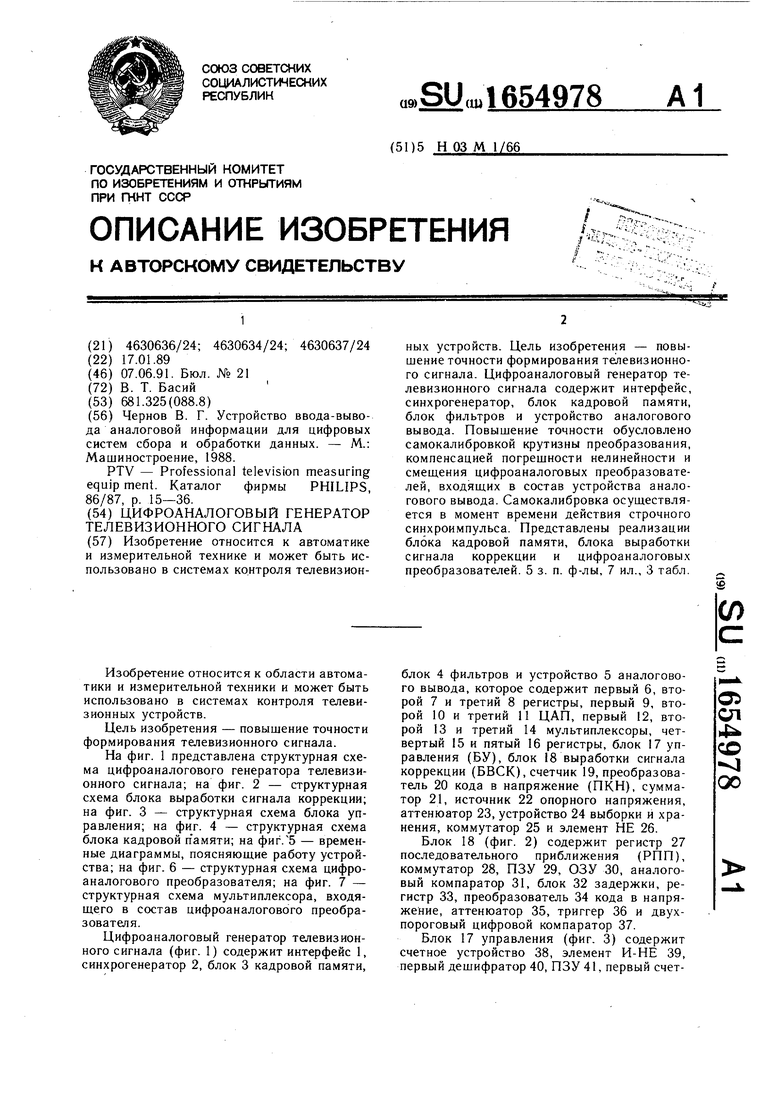

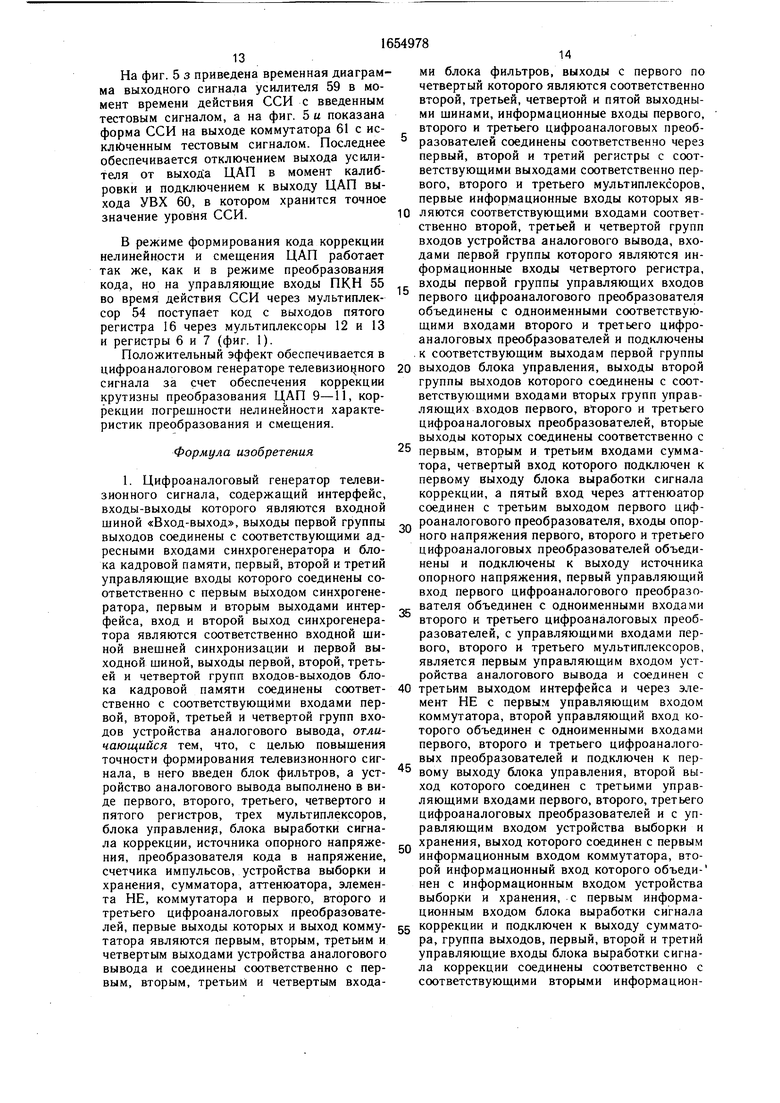

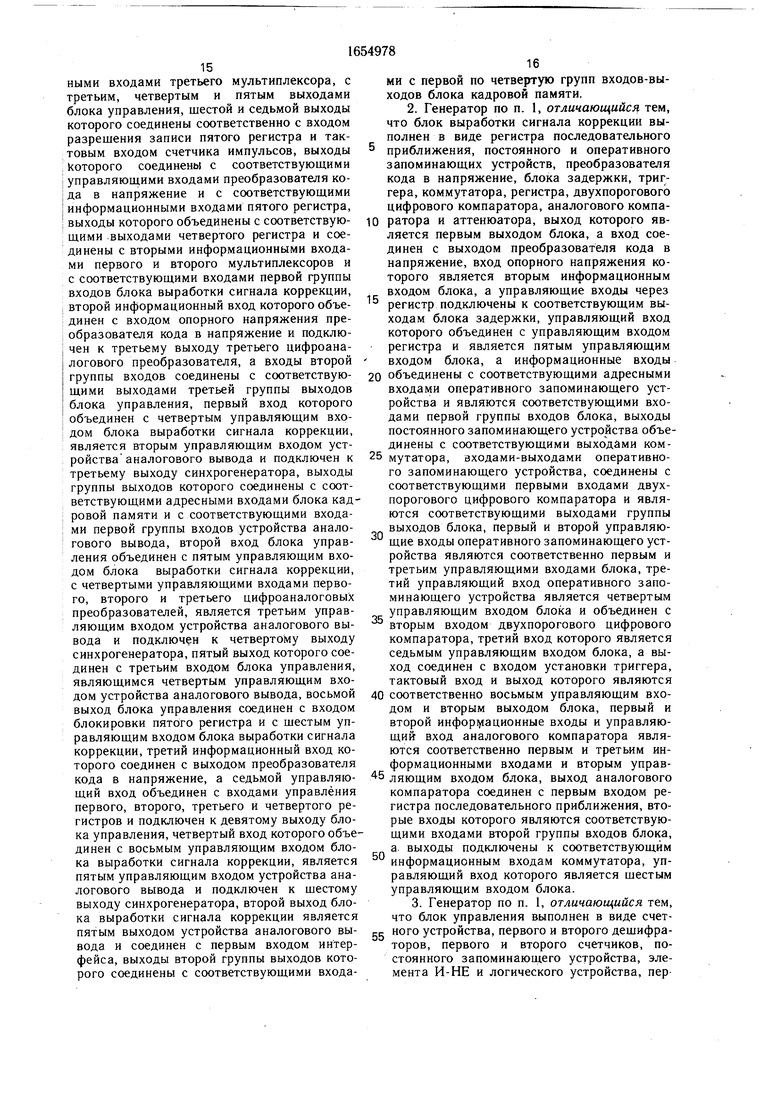

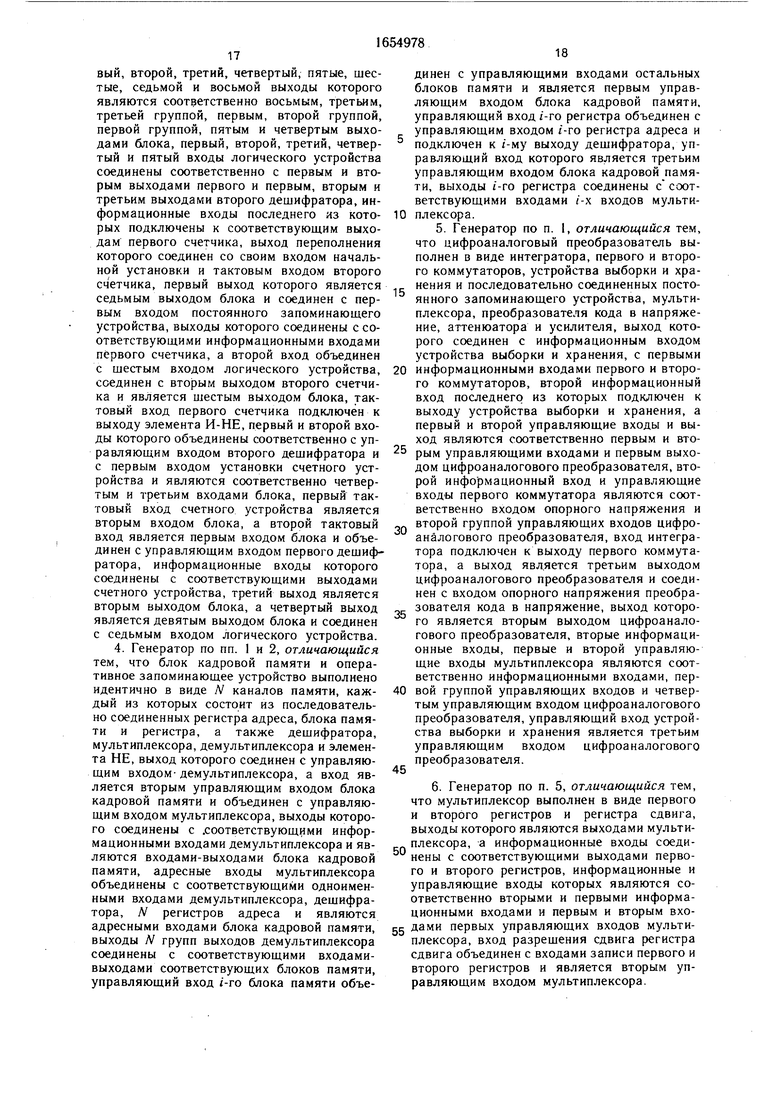

На фиг. 1 представлена структурная схема цифроаналогового генератора телевизионного сигнала; на фиг. 2 - структурная схема блока выработки сигнала коррекции; на фиг. 3 - структурная схема блока управления; на фиг. 4 - структурная схема блока кадровой памяти; на фиг.5 - временные диаграммы, поясняющие работу устройства; на фиг. 6 - структурная схема цифро- аналогового преобразователя; на фиг. 7 - структурная схема мультиплексора, входящего в состав цифроаналогового преобразователя.

Цифроаналоговый генератор телевизионного сигнала (фиг. 1) содержит интерфейс 1, синхрогенератор 2, блок 3 кадровой памяти,

блок 4 фильтров и устройство 5 аналогового вывода, которое содержит первый 6, второй 7 и третий 8 регистры, первый 9, второй 10 и третий 11 ЦАП, первый 12, второй 13 и третий 14 мультиплексоры, четвертый 15 и пятый 16 регистры, блок 17 управления (БУ), блок 18 выработки сигнала коррекции (БВСК), счетчик 19, преобразователь 20 кода в напряжение (ПКН), сумматор 21, источник 22 опорного напряжения, аттенюатор 23, устройство 24 выборки и хранения, коммутатор 25 и элемент НЕ 26.

Блок 18 (фиг. 2) содержит регистр 27 последовательного приближения (РПП), коммутатор 28, ПЗУ 29, ОЗУ 30, аналоговый компаратор 31, блок 32 задержки, регистр 33, преобразователь 34 кода в напряжение, аттенюатор 35, триггер 36 и двух- пороговый цифровой компаратор 37.

Блок 17 управления (фиг. 3) содержит счетное устройство 38, элемент И-НЕ 39, первый дешифратор 40, ПЗУ 41, первый счетCD

сд

со 1

00

чик 42, второй дешифратор 43, второй счетчик 44 и логическое устройство 45.

Блок 3 кадровой памяти и ОЗУ 30 (фиг. 4) выполнены идентично и содержат N параллельных каналов памяти, состоящих из последовательно соединенных регистра 46 адреса, блока 47 памяти и регистра 48, а также дешифратор 49, мультиплексор 50, демультиплексор 51 и элемент НЕ 52.

ЦАП 9 (10 и 11) (фиг. 6) содержит ПЗУ 53, мультиплексор 54, преобразователь 55 кода в напряжение (ПК.Н), интегратор 56, аттенюатор 57, первый коммутатор 58, усилитель 59, устройство 60 выборки и хранения (УВХ) и второй коммутатор 61. Мультиплексор 54 (фиг. 7) содержит пери шестого выходов синхрогенератора 2 тактовые сигналы Т2, Т1, ССИ и инвертированный кадровый гасящий импульс (КГИ) соответственно. При уровне сигнала переключения числа каналов, равном «Лог. 1,

5 УАВ 5 работает в конфигурации трехка- нального ЦАП ТВС, например сигналов R, G, В; а при уровне «Лог. О УАВ 5 принимает конфигурацию одноканального ЦАП повышенной точности для формирования полного

10 цветового ТВС, когда требуется точность цифроаналогового преобразования порядка 12-16 разрядов.

Цифроаналоговый генератор ТВ сигнала работает в трех режимах: цифроаналогового преобразования, самокалибровки крувый 62 и второй 63 регистры и регистр 64 15 тизны преобразования, коррекции нелиней- сдвига.ности и смещения ЦАП.

Цифроаналоговый генератор телевизионного сигнала (фиг. 1) работает следующим образом.

Цифровой поток телевизионного сигнала (ТВС), рассчитанный на ЭВМ, через интерфейс 1 записывается в машинном времени в блок 3 кадровой памяти, причем данные в

Режим цифроаналогового преобразования одноканальной конфигурации УАВ 5 на- 20 чинается по заднему фронту импульса (фиг. 5д), расположенного внутри .импульса ССИ (фиг. 5 а), и заканчивается по переднему фронту импульса (фиг. 5д),

блок 3 поступают с второй группы выходов, а адреса - с первой группы выходов ина также длится в течение импульса КГИ. На входы первой группы входов УАВ 5

терфейса 1. Интерфейс 1, кроме того, опре- 25 поступает цифровой поток ТВС, представделяет своими выходными сигналами функционирование синхрогенератора 2, отключая его группу выходов при записи данных в блок 3 кадровой памяти, включая режим автономной или ведомой синхронизации и стандарт синхронизации в соответствии с выбранной системой (SEK.AM, PAL, NTSC). В ведомом режиме на вход синхрогенератора 2 поступает сигнал приемника - смесь строчных синхроимпульсов (ССИ) и кадровых синхронизирующих и уравнивающих импульсов, которые поступают с второго выхода синхрогенератора 2 на первую выходную шину. Синхрогенератор 2 при формировании ТВС вырабатывает на группе выходов цифровой код, адресующий каждой цифро30

35

ляющий собой последовательность выборок ТВС в параллельном двоичном коде, и синхронный с ними тактовый импульс Т1 (фиг. 56), частота поступления которых соответствует теореме Котельникова. В момент прихода тактового импульса Т1 последовательность выборок по сигналу с выхода БУ 17 записывается в четвертый регистр 15 и с его выходов поступает через мультиплексоры 12 и 13 и регистры 6 и 7 на информационные входы ЦАП 9 и 10, на входы опорного напряжения которых поступает сигнал с выхода источника 22 опорного напряжения. С вторых выходов ЦАП 9 и 10 аналоговые сигналы, пропорциональные цифровому ТВС, поступают на сумматор 21.

вой выборке ТВ кадра соответствующую 40 Совокупность блоков - мультиплексоры 12 ячейку блока 3 кадровой памяти. Последо-и 13, регистры 6 и 7 и ЦАП 9 и 10 - составвательное изменение адресов блока 3 кадро- ляют основной канал УАВ 5. В сумматоре 21 вой памяти вызывает формирование цифрово- осуществляется суммирование (с определенго потока ТВС в реальном времени на выходе блока 3, который поступает на первую,

ными весами) сигнала основного канала с сигналом сдвига (поступающим с третьего

вторую, третью и четвертую группы входов 45 выхода ЦАП 9 через аттенюатор 23) и с

устройства 5 аналогового вывода (УАВ). Выходные сигналы УАВ 5 через блок 4 фильтров поступают на выходные шины цифро- аналогового генератора ТВС. Для коррекции фазовой характеристики в состав блока 4 фильтров входят фазовые корректоры.

На входы УАВ 5 поступают также следующие сигналы: на входы первой группы входов - S младших разрядов кода адреса с группы выходов синхрогенератора 2; на первый управляющий вход - сигнал переключения числа каналов устройства 5 с третьего выхода интерфейса 1; на второй, третий, четвертый и пятый управляющие входы - с третьего, четвертого, пятого

50

55

сигналом коррекции нелинейности и смещения, который формируется в канале коррекции (мультиплексор 14, регистр 8, второй выход ЦАП 11, блок 18, счетчик 19 и преобразователь 20 кода в напряжение).

Для формирования сигнала коррекции цифровой код с выхода четвертого регистра 15 поступает в БВСК 18 на адресные входы ОЗУ 30, в- котором хранится таблица кодов коррекции. Цифровой поток кодов коррекции, считываемых из ОЗУ 30 синхронно с цифровым потоком в основном канале УАВ 5, поступает через мультиплексор 14 и регистр 8 на информационные входы ЦАП 11, с второго выхода которого анаи шестого выходов синхрогенератора 2 тактовые сигналы Т2, Т1, ССИ и инвертированный кадровый гасящий импульс (КГИ) соответственно. При уровне сигнала переключения числа каналов, равном «Лог. 1,

УАВ 5 работает в конфигурации трехка- нального ЦАП ТВС, например сигналов R, G, В; а при уровне «Лог. О УАВ 5 принимает конфигурацию одноканального ЦАП повышенной точности для формирования полного

цветового ТВС, когда требуется точность цифроаналогового преобразования порядка 12-16 разрядов.

Цифроаналоговый генератор ТВ сигнала работает в трех режимах: цифроаналогоРежим цифроаналогового преобразования одноканальной конфигурации УАВ 5 на- чинается по заднему фронту импульса (фиг. 5д), расположенного внутри .импульса ССИ (фиг. 5 а), и заканчивается по переднему фронту импульса (фиг. 5д),

а также длится в течение импульса КГИ. На входы первой группы входов УАВ 5

поступает цифровой поток ТВС, представпоступает цифровой поток ТВС, представ

ляющий собой последовательность выборок ТВС в параллельном двоичном коде, и синхронный с ними тактовый импульс Т1 (фиг. 56), частота поступления которых соответствует теореме Котельникова. В момент прихода тактового импульса Т1 последовательность выборок по сигналу с выхода БУ 17 записывается в четвертый регистр 15 и с его выходов поступает через мультиплексоры 12 и 13 и регистры 6 и 7 на информационные входы ЦАП 9 и 10, на входы опорного напряжения которых поступает сигнал с выхода источника 22 опорного напряжения. С вторых выходов ЦАП 9 и 10 аналоговые сигналы, пропорциональные цифровому ТВС, поступают на сумматор 21.

Совокупность блоков - мультиплексоры 12 и 13, регистры 6 и 7 и ЦАП 9 и 10 - состав ляют основной канал УАВ 5. В сумматоре 21 осуществляется суммирование (с определенными весами) сигнала основного канала с сигналом сдвига (поступающим с третьего

выхода ЦАП 9 через аттенюатор 23) и с

выхода ЦАП 9 через аттенюатор 23) и с

сигналом коррекции нелинейности и смещения, который формируется в канале коррекции (мультиплексор 14, регистр 8, второй выход ЦАП 11, блок 18, счетчик 19 и преобразователь 20 кода в напряжение).

Для формирования сигнала коррекции цифровой код с выхода четвертого регистра 15 поступает в БВСК 18 на адресные входы ОЗУ 30, в- котором хранится таблица кодов коррекции. Цифровой поток кодов коррекции, считываемых из ОЗУ 30 синхронно с цифровым потоком в основном канале УАВ 5, поступает через мультиплексор 14 и регистр 8 на информационные входы ЦАП 11, с второго выхода которого аналотовый сигнал коррекции поступает на третий вход сумматора 21.

Сигнал с выхода сумматора 21 через второй информационный вход коммутатора 25 (последний управляется сигналом с третьего выхода интерфейса 1 через элемент

6 на

четвертый выход

НЕ 26) поступает УАВ 5.

Для обеспечения режима цифроаналого- вого преобразования БУ 17 вырабатывает на своих выходах следующие сигналы (табл. 1).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Устройство для ввода и вывода изображений объектов | 1990 |

|

SU1829045A1 |

| УСТРОЙСТВО И СПОСОБ ОТОБРАЖЕНИЯ ТЕЛЕВИЗИОННОЙ ВИДЕОИНФОРМАЦИИ НА ЭКРАНЕ КОМПЬЮТЕРНОГО МОНИТОРА | 2011 |

|

RU2464725C1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ПОСЛЕДОВАТЕЛЬНОСТИ КАДРОВ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ | 1993 |

|

RU2066929C1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1501134A1 |

| Устройство формирования телевизионного изображения с перемещением управляемого фрагмента | 1988 |

|

SU1644171A1 |

| Устройство для ввода и вывода цветной графической информации | 1985 |

|

SU1315964A1 |

Изобретение относится к автоматике и измерительной технике и может быть использовано в системах контроля телевизионных устройств. Цель изобретения - повышение точности формирования телевизионного сигнала. Цифроаналоговый генератор телевизионного сигнала содержит интерфейс, синхрогенератор, блок кадровой памяти, блок фильтров и устройство аналогового вывода. Повышение точности обусловлено самокалибровкой крутизны преобразования, компенсацией погрешности нелинейности и смещения цифроаналоговых преобразователей, входящих в состав устройства аналогового вывода. Самокалибровка осуществляется в момент времени действия строчного синхроимпульса. Представлены реализации блока кадровой памяти, блока выработки сигнала коррекции и цифроаналоговых преобразователей. 5 з. п. ф-лы, 7 ил., 3 табл.

У 17 па па

па

й

Назначение

Мультиплексор 54 транслирует преобразуемый код

Коммутатор 58 заблокирован, интегратор 56 хранит значение опорного напряжения

Регистр 27 последовательного приближения остановлен

Коммутатор 25 пропускает сигнал с выхода сумматора 21

УВХ 24 и 60 в режиме слежения уровня С СИ

ОЗУ 30 в режиме считывания Компаратор 31 заблокирован ОЗУ 30 подключено к шине данных через мультиплексор 50

Разрешена запись в пятый регистр 16 Сигнал со счетчика 44 поступает на счетчик 19

Пятый регистр 16 отключен от блока 18 и мультиплексора 54

Регистр 15 подключен непосредственно к блоку 18 и через мультиплексоры 12 и 13, регистры 6 и 7 к мультиплексору 54

Режим самокалибровки крутизны преобразования используется как в трехканаль- ной, так и в одноканальной конфигурации для формирования ТВС повышенной точности. Он начинается по переднему фронту и заканчивается по заднему фронту сигнала (фиг. 5 д) при условии равенства сигнала на шестом выходе БУ 17 «Лог. 1. При этом сигналом с второго выхода БУ 17 коммутатор 25 подключается к выходу УВХ 24, в котором к этому моменту времени запоминается значение уровня сигнала ССИ. Самокалибровка осуществляется в интервале действия ССИ активной части кадра ТВС, при

Таблица 1

Назначение

этом обеспечивается коррекция опорных на- 40 пряжений с целью стабилизации крутизны преобразования ЦАП 9-11. В данном случае осуществляется сравнение сигнала на выходе источника 22 опорного напряжения с напряжением, формируемым в ЦАП под воздействием цифрового кода эталонного значе- 45 ния опорного напряжения. Откорректированное значение опорного напряжения запоминается и используется в ЦАП в режиме цифроаналогового преобразования. БУ 17 в данном режиме формирует на своих выходах следующие сигналы (табл. 2).

Режим обновления кода коррекции нели-В этом режиме обеспечивается первонейности и смещения используется тольконачальное (после включения устройства)

при формировании ТВ сигнала повышеннойформирование, а затем уточнение корректиточности. Он начинается по переднему фрон-рующих кодов в ОЗУ 30 (фиг. 4), БУ 17 на ту и заканчивается по заднему фронту сиг- 30 своих выходах формирует следующие сигнанала (фиг. 5д). Этот режим возможен прилы (табл. 3). сигнале с, равном «Лог. О.т а б л и ц а 3

Выходы БУ 17

Мультиплексоры 54 ЦДЛ 9 и 10 подключены к выходу регистра 16 через мультиплексор 12 и 13 и регистры 6 и 7

Коммутатор 58 выключен по обоим входам интегратор 56 хранит точное значение опорного напряжения ПКН 55 в каждом ЦАП 9-11

Регистр 27 работает з режиме старт- стопного преобразования

Коммутатор 25 закрыт

УВХ 24 и 60 хранят уровень ССИ

ОЗУ 30 - в режиме считывания с переходом в режим записи по окончании цикла работы РГШ 27

Коммутатор 31 открыт по выходу

ОЗУ 30 отключено от шины данных, мультиплексор 50 закрыт

Осуществляется запись цифрового эквивалента напряжения калибровки (ЦЭНК) в регистр 16

Сигнал со счетчика 44 поступает на счетчик 19

Регистр 16 подключен непосредственно к входу БВСК 18 и через мультиплексоры 1 2 и 1 3 и регистры 6 и 7 к входам мультиплексоров 54, коммутатор 28 открыт

Регистр 15 отключен от входов БВСК 18 и мультиплексора 54

Назначение

ЦЭНК с выхода счетчика 19 через пятый регистр 16, мультиплексоры 12 и 13 и регистры 6 и 7 поступает на основной канал УАВ 5 (где преобразуется в напряжение) и в канал коррекции, где используется как адрес ОЗУ 30 и в котором будет записан уточненный код коррекции. В начале цикла коррекции ОЗУ- 30 по выходам находится в третьем состоянии.

Источником сигнала для шины данных БВСК 18 (фиг. 2) является регистр 27, который осуществляет цикл старт-стопного преобразования в течение девяти интервалов ССИ. Формируемый в РПП 27 код по цепи: коммутатор 28 - выходы группы выходов БВСК 18 - мультиплексор 14 - регистр 8 - информационные входы ЦАП 11 поступает на ПКН 55, в котором преобразуется в напряжение. Это напряжение с второго выхода ЦАП 11 через сумматор 21 поступает на один из входов компаратора 31, на другой вход которого поступает сигнал калибровки с выхода ПКН 20. Выходной сигнал компаратора является информационным сигналом для РПП 27. В десятом интервале ССИ производится запись кода из РПП 27 через коммутатор 28 в ОЗУ 30 по адресу, соответствующему значению ЦЭНК. На этом заканчивается один цикл формирования кода коррекции в ячейку ОЗУ 30 по выбранному адресу.

ОЗУ 30 (фиг. 4) работает следующим образом. Для повышения быстродействия ОЗУ 30 выполнено в виде N параллельных каналов памяти. Младшие 5 разрядов (S log2jV) с / -разрядного входа ОЗУ 30 поступают на дешифратор 49, строб ируемый тактовым сигналом Т2 (фиг. 5 а). На выходе, соответствующем входному коду дешифратора 49. формируется инвертированный импульс Т2, с помощью которого в регистр 46 адреса соответствующего канала памяти записывается адрес ячейки блока 47 памяти, соответствующий (R-S) разрядам входного кода дешифратора 49. Код младших 5 разрядов формируется при расчете цифрового потока ТВС так, что импульс Т2 с выхода дешифратора 49 поочередно опрашивает все N каналов памяти ОЗУ 30. При этом для , цикл считывания ОЗУ 30 может быть выбран в четыре раза меньше цикла считывания ОЗУ с одноканальной организацией.

Через, четыре цикла считывания импульс Т2 появляется вновь на описанном выходе дешифратора 49 и фиксирует в регистре 48 данные, выбранные из блока 47 памяти по адресу, записанному в начале цикла считывания в регистр 46. Через открытый для этого канала памяти мультиплексор 50 выбранные данные поступают на входы-выходы ОЗУ 30.

В режиме записи в ОЗУ 30 код с входа- выхода ОЗУ поступает через демультиплек- сор 51 на соответствующий канал памяти (вход-выход блока 47 памяти) и записы10

0

вается в ячейку памяти по адресу, хранящемуся в регистре 46, под воздействием сигнала на первом управляющем входе ОЗУ. Выбор режима считывания или записи осуществляется сигналом с второго управ- ляющего входа ОЗУ 30, поступающего на входы разрешения мультиплексора 50 непосредственно, а на демультиплексор 51 через элемент НЕ 52.

С целью сокращения объема ОЗУ 30 при расчете цифрового потока ТВС производят вычитание 5-разрядного кода из / -разрядно- го кода, определяющего форму ТБС. При этом 5-разрядный код формируется таким образом, чтобы 5 младших разрядов R-раз- рядного кода последовательно принимали значения О, 1, ... N в двоичном коде, обеспечивая таким образом последовательное обращение к каналам памяти ОЗУ 30. Восстановление аналогового сигнала производится формированием аналогового сигнала из 5-разрядного кода и сложением его с соответствующим масштабом с сигналом ПКН 55. Для этого в БВСК 18 введены блок 32 задержки, регистр 33, ПКН 34 и аттенюатор 35.

Двухпороговый цифровой компаратор 37 5 и триггер 36 используются для повышения достоверности работы цифроаналогового генератора ТВС. В случае недопустимой деградации по точности блоков УАВ 5 происходит обнуление триггера 36 по сигналу с компаратора 37. Интерфейс 1 перед прихо- 0 дом сигнала КГИ запрашивает состояние триггера 36 и формирует сигнал предупреждения. На третий вход компаратора 37 поступает сигнал (фиг. 5 д), который запрещает установку триггера 36 в нулевое состояние в моменты времени, соответствующие 5 режимам самокалибровки крутизны преобразования, нелинейности и смещения УАВ 5. ПЗУ 29, введенное в состав БВСК 18, необходимо для компенсации сигнала сдвига. Последнее обеспечивается тем, что при от- 0 ключении всех активных источников сигнала от шины данных состояние последней определяется кодом с выхода ПЗУ 29, значение которого равно 10000000 и соответствует половине диапазона сигнала коррекции.

5 Блок 3 кадровой памяти выполнен аналогично ОЗУ 30. На первый вход блока 3 кадровой памяти с выхода синхрогенератора 2 при формировании ТВС поступает импульс Т2. При записи данных этот импульс заменяется в синхрогенераторе 2 импульсом с 0 большим периодом повторения. На второй и третий входы блока 3 кадровой памяти поступают с выхода интерфейса 1 сигналы разрешения в память и переключения входа- выхода в память.

Блок 17 управления (фиг. 3) формирует необходимые сигналы для регламентации работы всего генератора в целом. На выходе счетного устройства 38 в результате воздействия на его входы сигналов Tl, T2

5

11

и ССИ формируется двоичная последовательность кодов, синхронная с тактом Т1, длительность которой превышает длительность сигнала ССИ.

Первый дешифратор 40 путем дешифрации кодов с выхода счетного устройства 38 с использованием сигнала Т2 (фиг. 5 а) формирует на своих выходах импульсные сигналы г, д, е, ж (фиг. 5 г, д, е, ж). Логическое устройство 45 путем логической обработки сигналов е, ж, а также сигналов с, к, л, м с выходов второго счетчика 44 и второго дешифратора 43 формирует остальные выходные сигналы блока 17 управления

Логическое устройство 45 реализуется по следующему алгоритму:

Вых. 1.: сДдВых. 2:

Вых. 3: с./ е/ мВых. 4:

сЛжЛ(мул)

Вых. 5: сДжЛк-Вых. 6: дV (еДс)

с/ ж/ лсДе,

Вых. 7: с /кЛдВых. 8: ()Лд

где V. Л - символы логических операций ИЛИ и И соответственно.

Сигнал (фиг. 5 в) с выхода элемента И-НЕ 39 поступает на тактовый вход первого (реверсивного) счетчика 42, работающего в режиме вычитания с загрузкой кода предустановки с выхода ПЗУ 41. Для этого импульс заема, возникающий при совпадении нулевого состояния на всех выходах первого счетчика 42 с выходным сигналом элемента И-НЕ 39 подается на вход загрузки входного кода с выхода ПЗУ 41. Последний под воздействием сигналов с первого и второго выходов второго счетчика 44, поступающих на его адресный вход, обеспечивает на своих выходах следующие коды: при с код ПЗУ 1000 (число 8), а при с 0 код ПЗУ 1001 (число 9). Второй дешифратор 43, стробируемый сигналом КТИ, формирует на своих выходах (при с 0) сигналы: м - состояние счетчика 42 соответствует числу 9 (одна ТВ строка); л - состояние счетчика 42 соответствует числам 8, ... 2,1 (восемь ТВ строк), к - состояние счетчика 42 соответствует числу 0 (одна ТВ строка). Эти сигналы совместно с сигналом с ис- пользуются в логическом устройстве 45 для формирования соответствующих сигналов.

ЦАП 9 (10, 11) (фиг. 6) работает следующим образом. В режиме преобразования кода цифровой код ТВС, поступающий на второй информационный вход мультиплексора 54, записывается в регистр 62 (фиг. 7) тактовым импульсом Т1. При этом выходы регистра 63 отключены от входов регистра 64 сдвига. Преобразуемый код формируется на выходах регистра 64 сдвига после несколь- ких импульсов Т1, чем осуществляется выравнивание времени задержки прохождения сигналов по различным цепям УАВ 5. Код

12

О

0

5 0 5 о 5

0 5

с выхода регистра 64 сдвига поступает на управляющие входы ПКН 55, в котором осуществляется его преобразование в аналоговый сигнал. В качестве опорного напряжения для ПКН 55 используется сигнал, запомненный в интеграторе 56 в процессе калибровки. Выход коммутатора 58 в этом режиме отключен от обоих своих входов. В качестве выходного сигнала ЦАП в одно- канальной конфигурации используется второй выход ПКН 55, а в трехканальной конфигурации - второй выход второго коммутатора 61, один из входов которого через усилитель 59 и аттенюатор 57 подключен к первому выходу ПКН 55. Сигнал с выхода интегратора 56 первого ЦАП 9 используется также для формирования сигнала сдвига, необходимого для обеспечения однополяр- ности сигнала коррекции. Сигнал с выхода интегратора 56 третьего ЦАП 11 используется в качестве опорного напряжения для ПКН 20 УАВ 5 и для ПКН 34 БВСК 18.

В режиме самокалибровки ЦАП используется код эталонного значения опорного напряжения, записанный в ПЗУ 53. Этот код заносится в регистр 63 мультиплексора 54 и через регистр 64 сдвига поступает на управляющие входы ПКН 55 (выходы регистра 62 в этом режиме отключены от входов регистра 64 сдвига). Калибровка уровня опор ного напряжения ПКН 55 осуществляется замыканием контура отрицательной обратной связи, состоящего из ПКН 55, аттенюатора 57, усилителя 59, первого коммутатора 58 и интегратора 56. В начале действия ССИ выход второго коммутатора 61 соединяется с выходом УВХ 60, который переводится в режим хранения значения уровня ССИ. Калибровка значения опорного напряжения ПКН 55 осуществляется путем подключения к входу интегратора 56 либо сигнала с выхода усилителя 59, либо сигнала от источника 22 опорного напряжения (фиг. 1). Соотношение времен интегрирования выходных напряжений усилителя 59 и источника 22 опорного напряжения обеспечивается таким управлением, при котором выходной сигнал усилителя 59 подключен к входу интегратора 56 в течение восьми импульсов вида (фиг. 5е), а выход источника 22 опорного напряжения - в течение одного такого импульса. Указанная коммутация осуществляется с помощью первого коммутатора 58.

В случае равенства амплитуды тестового сигнала на выходе усилителя 59 одной восьмой от напряжения источника 22 интегратора 56 по окончании цикла коррекции не изменяет своего выходного напряжения. В противном случае, в результате действия отрицательной обратной связи обеспечивается коррекция выходного напряжения интегратора 56 (т. е. опорного напряжения ПКН 55) и, следовательно, корректируется крутизна преобразования ПКН 55.

13

На фиг. 5 з приведена временная диаграмма выходного сигнала усилителя 59 в момент времени действия ССИ с введенным тестовым сигналом, а на фиг. 5 и показана форма ССИ на выходе коммутатора 61 с ис- ключенным тестовым сигналом. Последнее обеспечивается отключением выхода усилителя от выхода ЦАП в момент калибровки и подключением к выходу ЦАП выхода УВХ 60, в котором хранится точное значение уровня ССИ.

ми блока фильтров, выходы с первого по четвертый которого являются соответственно второй, третьей, четвертой и пятой выходными шинами, информационные входы первого, второго и третьего цифроаналоговых преобразователей соединены соответственно через первый, второй и третий регистры с соответствующими выходами соответственно первого, второго и третьего мультиплексоров, первые информационные входы которых яв- 10 ляются соответствующими входами соответственно второй, третьей и четвертой групп входов устройства аналогового вывода, входами первой группы которого являются информационные входы четвертого регистра,

В режиме формирования кода коррекции

нелинейности и смещения ЦАП работает

так же, как и в режиме преобразования

кода, но на управляющие входы ПКН 55 входы первой группы управляющих входов

во время действия ССИ через мультиплек- первого цифроаналогозого преобразователя

объединены с одноименными соответствующими входами второго и третьего цифро- аналоговых преобразователей и подключены

к соответствующим выходам первой группы

сор 54 поступает код с выходов пятого

регистра 16 через мультиплексоры 12 и 13

и регистры 6 и 7 (фиг. 1).

Положительный эффект обеспечивается в

цифроаналоговом генераторе телевизионного 20 выходов блока управления, выходы второй

сигнала за счет обеспечения коррекции группы выходов которого соединены с соответствующими входами вторых групп управляющих входов первого, второго и третьего цифроаналоговых преобразователей, вторые выходы которых соединены соответственно с

крутизны преобразования ЦАП 9-11, коррекции погрешности нелинейности характеристик преобразования и смещения.

Формула изобретения

25

первым, вторым и третьим входами сумматора, четвертый вход которого подключен к первому выходу блока выработки сигнала коррекции, а пятый вход через аттенюатор соединен с третьим выходом первого цифшиной «Вход-выход, выходы первой группы „ роаналогового преобразователя, входы опорвыходов соединены с соответствующими адресными входами синхрогенератора и блока кадровой памяти, первый, второй и третий управляющие входы которого соединены соответственно с первым выходом синхрогененого напряжения первого, второго и третьего цифроаналоговых преобразователей объединены и подключены к выходу источника опорного напряжения, первый управляющий вход первого цифроаналогового преобразоразователей, с управляющими входами первого, второго и третьего мультиплексоров, является первым управляющим входом устройства аналогового вывода и соединен с

ратора, первым и вторым выходами интер- вателя объединен с одноименными входами фейса, вход и второй выход синхрогенера- второго и третьего цифроаналоговых преоб- тора являются соответственно входной шиной внешней синхронизации и первой выходной шиной, выходы первой, второй, третьей и четвертой групп входов-выходов блока кадровой памяти соединены соответ- 40 третьим выходом интерфейса и через эле- ственно с соответствующими входами пер- мент НЕ с первым управляющим входом вой, второй, третьей и четвертой групп вхо- коммутатора, второй управляющий вход кодов устройства аналогового вывода, отли- торого объединен с одноименными входами чающийся тем, что, с целью повышения первого, второго и третьего цифроаналого- точности формирования телевизионного сиг- вых преобразователей и подключен к пер- нала, в него введен блок фильтров, а уст- 5 ВОму выходу блока управления, второй вы- ройство аналогового вывода выполнено в ви- ход которого соединен с третьими управляющими входами первого, второго, третьего цифроаналоговых преобразователей и с управляющим входом устройства выборки и

де первого, второго, третьего, четвертого и пятого регистров, трех мультиплексоров, блока управления, блока выработки сигнала коррекции, источника опорного напряже- п хранения, выход которого соединен с первым

ния, преобразователя кода в напряжение, счетчика импульсов, устройства выборки и хранения, сумматора, аттенюатора, элемента НЕ, коммутатора и первого, второго и третьего цифроаналоговых преобразоватеинформационным входом коммутатора, второй информационный вход которого объединен с информационным входом устройства выборки и хранения, с первым информационным входом блока выработки сигнала

леи, первые выходы которых и выход комму-55 коррекции и подключен к выходу сумматотатора являются первым, вторым, третьим ира, группа выходов, первый, второй и третий

четвертым выходами устройства аналоговогоуправляющие входы блока выработки сигнавывода и соединены соответственно с пер-ла коррекции соединены соответственно с

вым, вторым, третьим и четвертым входа-соответствующими вторыми информацион1654978

14

ми блока фильтров, выходы с первого по четвертый которого являются соответственно второй, третьей, четвертой и пятой выходными шинами, информационные входы первого, второго и третьего цифроаналоговых преобразователей соединены соответственно через первый, второй и третий регистры с соответствующими выходами соответственно первого, второго и третьего мультиплексоров, первые информационные входы которых яв- ляются соответствующими входами соответственно второй, третьей и четвертой групп входов устройства аналогового вывода, входами первой группы которого являются информационные входы четвертого регистра,

входы первой группы управляющих входов

к соответствующим выходам первой группы

выходов блока управления, выходы второй

группы выходов которого соединены с соответствующими входами вторых групп управляющих входов первого, второго и третьего цифроаналоговых преобразователей, вторые выходы которых соединены соответственно с

первым, вторым и третьим входами сумматора, четвертый вход которого подключен к первому выходу блока выработки сигнала коррекции, а пятый вход через аттенюатор соединен с третьим выходом первого цифроаналогового преобразователя, входы опорного напряжения первого, второго и третьего цифроаналоговых преобразователей объединены и подключены к выходу источника опорного напряжения, первый управляющий вход первого цифроаналогового преобразоразователей, с управляющими входами первого, второго и третьего мультиплексоров, является первым управляющим входом устройства аналогового вывода и соединен с

вателя объединен с одноименными входами второго и третьего цифроаналоговых преоб- третьим выходом интерфейса и через эле- мент НЕ с первым управляющим входом коммутатора, второй управляющий вход которого объединен с одноименными входами первого, второго и третьего цифроаналого- вых преобразователей и подключен к пер- ВОму выходу блока управления, второй вы- ход которого соединен с третьими управляющими входами первого, второго, третьего цифроаналоговых преобразователей и с управляющим входом устройства выборки и

хранения, выход которого соединен с первым

информационным входом коммутатора, второй информационный вход которого объеди нен с информационным входом устройства выборки и хранения, с первым информационным входом блока выработки сигнала

ными входами третьего мультиплексора, с третьим, четвертым и пятым выходами блока управления, шестой и седьмой выходы которого соединены соответственно с входом разрешения записи пятого регистра и тактовым входом счетчика импульсов, выходы Которого соединены с соответствующими управляющими входами преобразователя кода в напряжение и с соответствующими информационными входами пятого регистра, выходы которого объединены с соответствующими выходами четвертого регистра и соединены с вторыми информационными входами первого и второго мультиплексоров и с соответствующими входами первой группы входов блока выработки сигнала коррекции, второй информационный вход которого объединен с входом опорного напряжения преобразователя кода в напряжение и подключен к третьему выходу третьего цифроана- логового преобразователя, а входы второй группы входов соединены с соответствующими выходами третьей группы выходов блока управления, первый вход которого объединен с четвертым управляющим входом блока выработки сигнала коррекции, является вторым управляющим входом устройства аналогового вывода и подключен к третьему выходу синхрогенератора, выходы группы выходов которого соединены с соответствующими адресными входами блока кадровой памяти и с соответствующими входами первой группы входов устройства аналогового вывода, второй вход блока управления объединен с пятым управляющим входом блока выработки сигнала коррекции, с четвертыми управляющими входами первого, второго и третьего цифроаналоговых преобразователей, является третьим управляющим входом устройства аналогового вывода и подключен к четвертому выходу синхрогенератора, пятый выход которого соединен с третьим входом блока управления, являющимся четвертым управляющим входом устройства аналогового вывода, восьмой выход блока управления соединен с входом блокировки пятого регистра и с шестым управляющим входом блока выработки сигнала коррекции, третий информационный вход которого соединен с выходом преобразователя кода в напряжение, а седьмой управляющий вход объединен с входами управления первого, второго, третьего и четвертого регистров и подключен к девятому выходу блока управления, четвертый вход которого объединен с восьмым управляющим входом блока выработки сигнала коррекции, является пятым управляющим входом устройства аналогового вывода и подключен к шестому выходу синхрогенератора, второй выход блока выработки сигнала коррекции является пятым выходом устройства аналогового вывода и соединен с первым входом интерфейса, выходы второй группы выходов которого соединены с соответствующими входа

0

5

0

5

0

5

0

5

ми с первой по четвертую групп входов-выходов блока кадровой памяти.

вый, второй, третий, четвертый, пятые, шестые, седьмой и восьмой выходы которого являются соответственно восьмым, третьим, третьей группой, первым, второй группой, первой группой, пятым и четвертым выходами блока, первый, второй, третий, четвертый и пятый входы логического устройства соединены соответственно с первым и вторым выходами первого и первым, вторым и третьим выходами второго дешифратора, информационные входы последнего из которых подключены к соответствующим выходам первого счетчика, выход переполнения которого соединен со своим входом начальной установки и тактовым входом второго счетчика, первый выход которого является седьмым выходом блока и соединен с первым входом постоянного запоминающего устройства, выходы которого соединены с соответствующими информационными входами первого счетчика, а второй вход объединен с шестым входом логического устройства, соединен с вторым выходом второго счетчика и является шестым выходом блока, тактовый вход первого счетчика подключен к выходу элемента И-НЕ, первый и второй входы которого объединены соответственно с управляющим входом второго дешифратора и с первым входом установки счетного устройства и являются соответственно четвертым и третьим входами блока, первый тактовый вход счетного устройства является вторым входом блока, а второй тактовый вход является первым входом блока и объединен с управляющим входом первого дешифратора, информационные входы которого соединены с соответствующими выходами счетного устройства, третий выход является вторым выходом блока, а четвертый выход является девятым выходом блока и соединен с седьмым входом логического устройства. 4. Генератор по пп. 1 и 2, отличающийся тем, что блок кадровой памяти и оперативное запоминающее устройство выполнено идентично в виде N каналов памяти, каждый из которых состоит из последовательно соединенных регистра адреса, блока памяти и регистра, а также дешифратора, мультиплексора, демультиплексора и элемента НЕ, выход которого соединен с управляющим входом- демультиплексора, а вход является вторым управляющим входом блока кадровой памяти и объединен с управляющим входом мультиплексора, выходы которого соединены с .соответствующими информационными входами демультиплексора и являются входами-выходами блока кадровой памяти, адресные входы мультиплексора объединены с соответствующими одноименными входами демультиплексора, дешифратора, N регистров адреса и являются адресными входами блока кадровой памяти, выходы N групп выходов демультиплексора соединены с соответствующими входами- выходами соответствующих блоков памяти, управляющий вход /-го блока памяти объе

5

динен с управляющими входами остальных блоков памяти и является первым управляющим входом блока кадровой памяти, управляющий ВХОД/-ГО регистра объединен с управляющим входом /-го регистра адреса и подключен к /-му выходу дешифратора, управляющий вход которого является третьим управляющим входом блока кадровой памяти, выходы /-го регистра соединены с соответствующими входами i-x входов мульти- 0 плексора.

0 информационными входами первого и второго коммутаторов, второй информационный вход последнего из которых подключен к выходу устройства выборки и хранения, а первый и второй управляющие входы и выход являются соответственно первым и вторым управляющими входами и первым выходом цифроаналогового преобразователя, второй информационный вход и управляющие входы первого коммутатора являются соответственно входом опорного напряжения и второй группой управляющих входов цифро- аналогового преобразователя, вход интегратора подключен к выходу первого коммутатора, а выход является третьим выходом цифроаналогового преобразователя и соединен с входом опорного напряжения преобразователя кода в напряжение, выход которого является вторым выходом цифроаналогового преобразователя, вторые информационные входы, первые и второй управляющие входы мультиплексора являются соответственно информационными входами, первой группой управляющих входов и четвертым управляющим входом цифроаналогового преобразователя, управляющий вход устройства выборки и хранения является третьим управляющим входом цифроаналогового

преобразователя. 5

0

5

0

Щи г. 2

Фиг.1

b

i/

И6

Ч.

f-M

f

т

/

Первый канал яамя/яи 1

47

Ь

г

второй

канал

fet

7

I

Лмканал

л

С

г

памяти 1

Ф

7vf

яамя/mi

о

W I 7

iko

О/

s/

&J

ц

9/

3

)

3/

41

И

Tec rnobbtd сигнал

С/сса

Uccu

Фиг 5

Щиг.В

| Чернов В | |||

| Г | |||

| Устройство ввода-вывода аналоговой информации для цифровых систем сбора и обработки данных | |||

| - М.: Машиностроение, 1988 | |||

| PTV - Professional television measuring equip ment | |||

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1991-06-07—Публикация

1989-01-17—Подача