Предлагаемое изобретение относится к области перспективной элементной базы нейроморфной электроники и может быть использовано в качестве синаптического элемента при интегральной реализации нейронных сетей.

Функциональным аналогом заявляемого изобретения является интегральный электронный синапс на основе комплементарных структур «металл - окисел - полупроводник» (КМОП) [Sahibia Kaur Vohra, Sherin A. Thomas, Mahendra Sakare, and Devarshi Mrinal Das. CMOS Circuit Implementation of Spiking Neural Network for Pattern Recognition Using On-chip Unsupervised STDP Learning // arXiv:2204.04430v1, eess.IV, 2022, https://arxiv.org/pdf/2204.04430.pdf, 2011, с. 3, фиг. 4], содержащий первый и второй интеграторы с утечкой на основе параллельных RC-цепей, преобразователь «напряжение-ток» на основе операционного усилителя, первый и второй электронные ключи, подключающие первый и второй интеграторы к напряжению питания при поступлении управляющих импульсов на первый и второй управляющие входы, третий, четвертый, пятый, шестой и седьмой электронные ключи, подключающие преобразователь «напряжение-ток» на основе операционного усилителя при поступлении управляющих импульсов на первый и второй управляющие входы, преобразователь «напряжение-проводимость» на основе конденсатора и МОП-транзистора с электронной проводимостью, причем затвор МОП-транзистора соединен с одним из контактов конденсатора, благодаря чему напряжение на конденсаторе определяет уровень проводимости канала МОП-транзистора (синаптический вес), восьмой электронный ключ, соединяющий конденсатор преобразователя «напряжение-проводимость» с выходом преобразователя «напряжение-ток» на основе операционного усилителя в режиме перестройки синаптических весов (в режиме обучения нейронной сети) и отключающий конденсатор преобразователя «напряжение-проводимость» от выхода преобразователя «напряжение-ток» на основе операционного усилителя в основном режиме работы нейронной сети с неизменными синаптическими весами (в inference-режиме).

Недостатками данного технического решения являются изменение напряжения на конденсаторе в inference-режиме, обусловленное токами утечки, и соответствующее нежелательное изменение проводимости канала МОП-транзистора (деградация во времени синаптического веса), нелинейность передаточной характеристики интегрального электронного синапса (нелинейная зависимость проводимости канала МОП-транзистора от числа управляющих импульсов), необходимость использования операционного усилителя, характеризующегося повышенным (по сравнению с логическими КМОП-элементами) энергопотреблением вследствие протекания сквозного тока.

Аналогом заявляемого изобретения является интегральный гибридный КМОП-мемристивный синапс [H. Aziza, H. Bazzi, J. Postel-Pellerin, P. Canet, M. Moreau, et al.. An Augmented OxRAM Synapse for Spiking Neural Network (SNN) Circuits. 2019 14th International Conference on Design & Technology of Integrated Systems In Nanoscale Era (DTIS), Apr 2019, Mykonos, France. 10.1109/DTIS.2019.8735057. hal-02306907, с. 4, фиг. 8], содержащий металлооксидную мемристивную структуру, МОП-транзисторы с электронной проводимостью каналов, сдвиговый регистр, причем количество МОП-транзисторов с электронной проводимостью каналов M и разрядность сдвигового регистра R (число триггеров в регистре) равна числу уровней проводимости интегрального электронного синапса N, стоковые контакты всех МОП-транзисторов с электронной проводимостью каналов соединены с первым контактом металлооксидной мемристивной структуры, истоковые контакты всех МОП-транзисторов с электронной проводимостью каналов соединены с выходной линией электронного синапса, второй контакт металлооксидной мемристивной структуры и вход тактовых импульсов сдвигового регистра соединены со входной линией электронного синапса, на входную линию данных сдвигового регистра подается постоянный уровень логической единицы, выходная линия данных i-го разряда сдвигового регистра соединена с затвором соответствующего i-го МОП-транзистора с электронной проводимостью каналов, где i=1, 2,…, N, а N - число уровней проводимости интегрального электронного синапса.

Недостатками данного интегрального гибридного КМОП-мемристивного синапса являются сравнительно большая площадь, занимаемая интегральным электронным синапсом на кристалле, обусловленная тем, что количество МОП-транзисторов с электронной проводимостью каналов и разрядность сдвигового регистра (число триггеров в регистре) равны числу уровней проводимости интегрального электронного синапса (64 - 512 для реальных нейронных сетей), нелинейность передаточной характеристики и наличие разброса параметров «от прибора к прибору» и «от цикла к циклу», обусловленные нелинейностью и разбросом параметров мемристивных структур.

Наиболее близким по технической сущности к заявляемому изобретению (прототипом) является интегральный электронный КМОП синапс с цифровым управлением [Asghar, M.S.; Arslan, S.; Kim, H. A Low-Power Spiking Neural Network Chip Based on a Compact LIF Neuron and Binary Exponential Charge Injector Synapse Circuits. Sensors 2021, 21, 4462. https://doi.org/10.3390/s21134462, с. 8, фиг. 4], содержащий МОП-транзисторы с дырочной проводимостью каналов, определяющие синаптический вес, количество которых M равно логарифму по основанию 2 от числа уровней проводимости N интегрального электронного синапса (M=log2N), причем значения ширины каналов Wi МОП-транзисторов, определяющих синаптический вес, связаны между собой соотношением Wi=2Wi-1, где i - порядковый номер МОП-транзистора (i=0,1,…,M-1); M ключевых МОП-транзисторов с дырочной проводимостью каналов; M КМОП инверторов на основе комплементарных пар МОП-транзисторов с электронной и дырочной проводимостью, контакты затворов которых соединены и образуют входную линию КМОП-инвертора, а контакты стоков которых соединены и образуют выходную линию КМОП-инвертора, причем все ключевые МОП-транзисторы с дырочной проводимостью имеют одинаковые параметры каналов, контакт стока i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, соединен с контактом истока i-го ключевого МОП-транзистора с дырочной проводимостью канала для всех i=0,1,…,M-1, контакты стоков всех ключевых МОП-транзисторов с дырочной проводимостью канала соединены с выходной линией электронного синапса, контакты затворов всех МОП-транзисторов, определяющих синаптический вес, соединены с линией постоянного напряжения смещения, определяющего проводимости каналов МОП-транзисторов, определяющих синаптический вес, входные линии всех КМОП инверторов соединены со входной линией электронного синапса, выходная линия i-го КМОП инвертора соединена с контактом затвора i-го ключевого МОП-транзистора с дырочной проводимостью канала для всех i=0,1,…,M-1, контакты истоков МОП-транзисторов с дырочной проводимостью комплементарных пар всех КМОП-инверторов соединены с линией питания, контакты истоков МОП-транзисторов с электронной проводимостью комплементарных пар КМОП инверторов образуют M-разрядную цифровую управляющую шину электронного синапса.

Признаками прототипа, совпадающими с существенными признаками заявляемого изобретения, являются МОП-транзисторы с дырочной проводимостью каналов, определяющие синаптический вес, количество которых M равно логарифму по основанию 2 от числа уровней проводимости N интегрального электронного синапса (M=log2N), причем значения ширины каналов Wi МОП-транзисторов, определяющих синаптический вес, связаны между собой соотношением Wi=2Wi-1, где i - порядковый номер МОП-транзистора, определяющего синаптический вес (i=0,1,…,M-1); M ключевых МОП-транзисторов с дырочной проводимостью каналов.

Недостатками прототипа являются:

- необходимость использования отдельного КМОП-инвертора для управления каждым из M ключевых МОП-транзисторов, что приводит к увеличению площади, занимаемой электронным синапсом на кристалле, увеличению входной емкости электронного синапса (поскольку входная линия электронного синапса соединена со входными линиями всех M КМОП-инверторов) и, как следствие, к повышению потребляемой мощности;

- одинаковые параметры каналов (в частности, ширина каналов) ключевых МОП-транзисторы с дырочной проводимостью, что приводит, с одной стороны, к увеличению площади, занимаемой ключевыми транзисторами на кристалле, (для ключевых транзисторов, соединенных с МОП-транзисторами, определяющими синаптический вес, с наименьшими значениями ширины каналов), а с другой стороны, к увеличению погрешности установки уровня проводимости (синаптического «веса») (для ключевых транзисторов, соединенных с МОП-транзисторами, определяющими синаптический вес, с наибольшими значениями ширины каналов).

Задачей предлагаемого изобретения является создание интегрального электронного КМОП синапса, обеспечивающего достижение технического результата: уменьшения площади, занимаемой электронным синапсом на кристалле, уменьшения входной емкости электронного синапса, снижения потребляемой мощности и уменьшения погрешности установки уровня проводимости электронного синапса (синаптического «веса»).

Для достижения необходимого технического результата в интегральный электронный КМОП синапс, содержащий МОП-транзисторы с дырочной проводимостью каналов, определяющие синаптический вес, количество которых M равно логарифму по основанию 2 от числа уровней проводимости N интегрального электронного синапса (M=log2N), причем значения ширины каналов Wi МОП-транзисторов, определяющих синаптический вес, связаны между собой соотношением Wi=2Wi-1, где i - порядковый номер МОП-транзистора (i=0,1,…,M-1); M ключевых МОП-транзисторов с дырочной проводимостью каналов, введен КМОП-инвертор на основе комплементарной пары МОП-транзисторов с электронной и дырочной проводимостью, контакты затворов которых соединены и образуют входную линию электронного синапса, а контакты стоков соединены и образуют выходную линию КМОП-инвертора, причем ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью канала равна ширине канала i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i=0,1,…,M-1, контакт истока МОП-транзистора с дырочной проводимостью КМОП-инвертора и контакты истоков всех ключевых МОП-транзисторов с дырочной проводимостью каналов соединены с линией питания, контакт истока МОП-транзистора с электронной проводимостью КМОП-инвертора соединен с линией постоянного напряжения смещения, контакт стока i-го ключевого МОП-транзистора с дырочной проводимостью канала соединен с контактом истока i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i=0,1,…,M-1, контакты затворов всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией КМОП-инвертора, контакты стоков всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией электронного синапса, контакты затворов всех ключевых МОП-транзисторов с дырочной проводимостью каналов образуют M-разрядную цифровую управляющую шину электронного синапса.

Введение КМОП-инвертора, входная линия которого является входной линией электронного синапса, а выходная линия соединена с контактами затворов всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, равенство ширины канала i-го ключевого МОП-транзистора ширине канала i-го МОП-транзистора, определяющего синаптический вес, для всех i=0,1,…,M-1, соединение контактов истоков всех ключевых МОП-транзисторов с линией питания, соединение контакта истока МОП-транзистора с электронной проводимостью КМОП-инвертора с линией постоянного напряжения смещения, соединение контакта стока i-го ключевого МОП-транзистора с контактом истока i-го МОП-транзистора, определяющего синаптический вес, для всех i=0,1,…,M-1, соединение контактов стоков всех МОП-транзисторов, определяющих синаптический вес, с выходной линией электронного синапса, а также то, что M-разрядная цифровая управляющая шина электронного синапса образована контактами затворов ключевых МОП-транзисторов, обеспечило уменьшение числа МОП-транзисторов, приходящихся на один разряд цифровой управляющей шины в 2 раза (по сравнению с прототипом) при уменьшении площади, занимаемой каждым ключевым МОП-транзистором на кристалле, уменьшение в M раз числа затворов NG, соединенных со входной линией электронного синапса (в прототипе NG = 2M, в предлагаемом электронном КМОП синапсе NG = 2 при любом числе разрядов M цифровой управляющей шины), благодаря чему получен положительный эффект, заключающийся в уменьшении площади, занимаемой электронным синапсом на кристалле, уменьшении входной емкости электронного синапса, снижении потребляемой мощности (поскольку потребляемая мощность прямо пропорциональна входной емкости при заданной частоте следования входных импульсов) и уменьшении погрешности установки уровня проводимости электронного синапса.

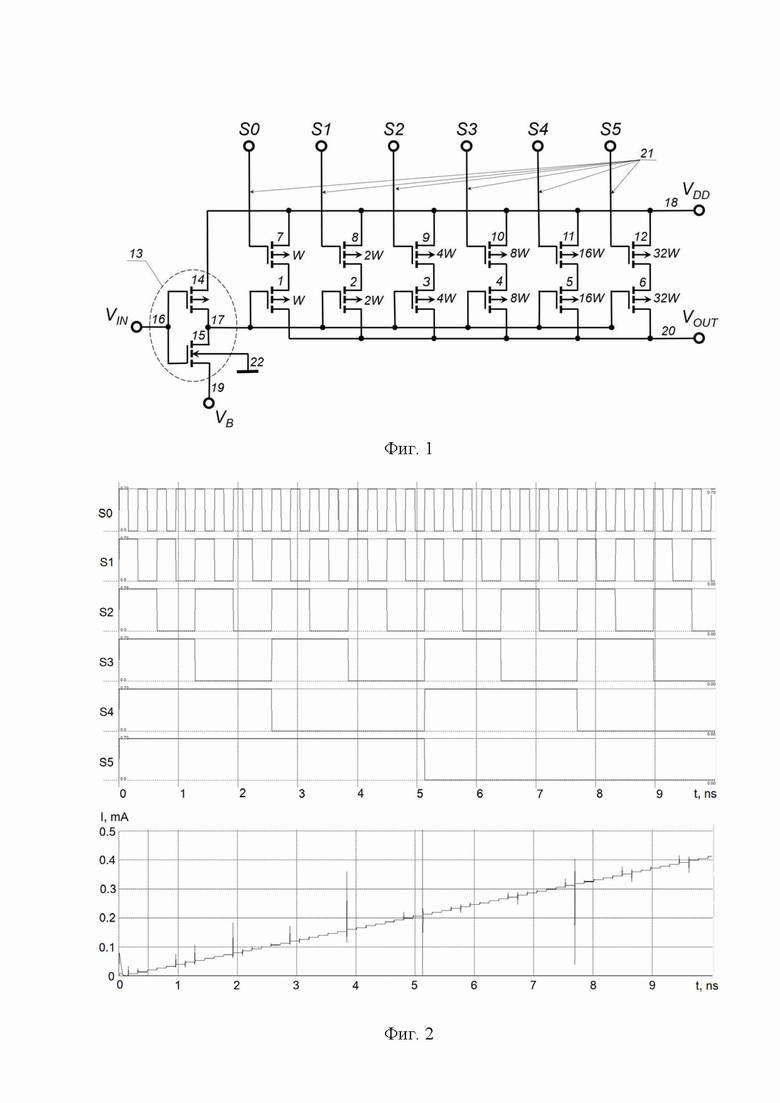

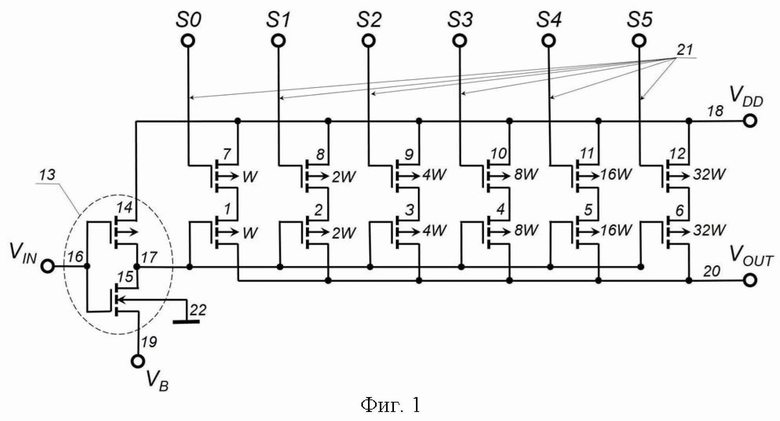

На фиг. 1 приведена схема электрическая принципиальная предлагаемого интегрального электронного КМОП синапса (на примере для количества M МОП-транзисторов, определяющих синаптический вес, M=log264=6). На фиг. 2 приведены временные диаграммы предлагаемого интегрального электронного КМОП синапса.

Интегральный электронный КМОП синапс (фиг.1) содержит МОП-транзисторы 1 - 6 с дырочной проводимостью каналов, определяющие синаптический вес, ключевые МОП-транзисторы 7 - 12 с дырочной проводимостью каналов, КМОП-инвертор 13 на основе комплементарной пары МОП-транзистора 14 с дырочной проводимостью и МОП-транзистора с электронной проводимостью 15 со входной линией 16 и выходной линией 17, линию питания 18 VDD, линию 19 постоянного напряжения смещения VB, выходную линию 20 электронного синапса VOUT, цифровую управляющую шину 21 электронного синапса S5 - S0 (S5 - старший разряд, S0 - младший разряд), образованную контактами затворов ключевых МОП-транзисторов 7 - 12 с дырочной проводимостью каналов, линию 22 нулевого потенциала VSS.

Контакты затворов МОП-транзистора 14 с дырочной проводимостью и МОП-транзистора 15 с электронной проводимостью соединены со входной линией 16 КМОП-инвертора 13, являющейся входной линией VIN электронного синапса. Контакты стоков МОП-транзистора 14 с дырочной проводимостью и МОП-транзистора 15 с электронной проводимостью соединены и образуют выходную линию 17 КМОП-инвертора 13. Контакт истока МОП-транзистора 14 с дырочной проводимостью КМОП-инвертора 13 и контакты истоков ключевых МОП-транзисторов 7 - 12 с дырочной проводимостью каналов соединены с линией питания 18 VDD. Контакт истока МОП-транзистора 15 с электронной проводимостью КМОП-инвертора 13 соединен с линией 19 постоянного напряжения смещения VB. Контакт подложки МОП-транзистора 15 с электронной проводимостью КМОП-инвертора 13 соединен с линией 22 нулевого потенциала VSS. Контакты затворов МОП-транзисторов 1 - 6 с дырочной проводимостью каналов соединены с выходной линией 17 КМОП-инвертора 13. Контакты стоков МОП-транзисторов 1 - 6 с дырочной проводимостью каналов соединены с выходной линией 20 электронного синапса VOUT.

Количество M МОП-транзисторов 1 - 6 с дырочной проводимостью каналов, определяющих синаптический вес, равно логарифму по основанию 2 от числа уровней проводимости N интегрального электронного синапса (на фиг. 1 M=log264=6), причем значения ширины каналов Wi МОП-транзисторов 1 - 6 связаны между собой соотношением Wi=2Wi-1, где i - порядковый номер МОП-транзистора (i=0,1,…,M-1), ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью равна ширине канала i-го МОП-транзистора с дырочной проводимостью, определяющего синаптический вес, для всех i=0,1,…,M-1, контакт стока i-го ключевого МОП-транзистора с дырочной проводимостью канала соединен с контактом истока i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i=0,1,…,M-1.

Работает устройство следующим образом.

При подаче напряжения питания VDD на линию питания 18, напряжения смещения VB на линию постоянного напряжения смещения 19, соединенную с истоком МОП-транзистора 15 с электронной проводимостью канала КМОП-инвертора 13, относительно линии 22 нулевого потенциала VSS, и действующем низком уровне логического нуля VIN на входной линии 16 электронного синапса, соединенной с контактами затворов МОП-транзистора 14 с дырочной проводимостью канала и МОП-транзистора 15 с электронной проводимостью канала КМОП-инвертора 13, МОП-транзистор 14 с дырочной проводимостью канала открывается, а МОП-транзистор 15 с электронной проводимостью канала закрывается, в результате чего на выходной линии 17 КМОП-инвертора 13, соединенной со стоками комплементарных МОП-транзисторов 14 и 15 и с затворами МОП-транзисторов 1 - 6 с дырочной проводимостью каналов, определяющих синаптический вес, устанавливается высокий уровень напряжения, близкий к напряжению питания VDD, в результате чего все МОП-транзисторы 1 - 6 с дырочной проводимостью каналов закрываются, и выходная линия 20 VOUT электронного синапса переводится в высокоимпедансное Z-состояние вне зависимости от цифрового кода на управляющей цифровой шине 21 S5 - S0 и состояний ключевых МОП-транзисторов 7 - 12 с дырочной проводимостью каналов.

При поступлении на входную линию 16 электронного синапса входного импульса VIN с амплитудой AIN, определяемой (относительно линии 22 нулевого потенциала VSS) выражением AIN=VB+VDD, и длительностью tIN и действующем цифровом коде S5 - S0 на управляющей цифровой шине 21 (активный уровень логического нуля), МОП-транзистор 14 с дырочной проводимостью канала КМОП-инвертора 13 закрывается, а МОП-транзистор 15 с электронной проводимостью канала КМОП-инвертора 13 открывается, в результате чего на выходной линии 17 КМОП-инвертора 13, соединенной со стоками комплементарных МОП-транзисторов 14 и 15 и с затворами МОП-транзисторов 1 - 6 с дырочной проводимостью каналов, в интервале времени tIN устанавливается низкий уровень напряжения, близкий к напряжению смещения VB, в результате чего все МОП-транзисторы 1 - 6 с дырочной проводимостью каналов открываются до уровней проводимости каналов, приближенно определяемых выражением (1):

GWi≈μpC0Wi/L(VDD/2-|V0|-VB), i=0, 1,…, M-1, (1)

где GWi - проводимость канала i-го МОП-транзистора;

Wi - ширина канала i-го МОП-транзистора;

L - длина каналов МОП-транзисторов;

C 0 - удельная емкость диэлектрика затворов МОП-транзисторов;

μp - подвижность носителей заряда (дырок) в каналах МОП-транзисторов;

V 0 - пороговое напряжение МОП-транзисторов;

VDD - напряжение питания;

VB - напряжение смещения;

M - число транзисторов, определяющих синаптический вес.

Поскольку значения ширины каналов Wi МОП-транзисторов 1 - 6 связаны между собой соотношением Wi=2Wi-1, где i - порядковый номер МОП-транзистора (i=0,1,…,M-1), то, в соответствии с выражением (1), проводимости GWi МОП-транзисторов 1 - 6 будут связаны аналогичным образом GWi=2GWi-1 с возможностью пропорционального изменения всех уровней проводимости GWi напряжением смещения VB.

При этом действующий цифровой код S5 - S0 на управляющей цифровой шине 21 установит каждый из ключевых МОП-транзисторов 7 - 12 с дырочной проводимостью каналов в открытое состояние (при уровне логического нуля на разряде управляющей цифровой шины 21, соединенной с контактом затвора данного ключевого МОП-транзистора) или в закрытое состояние (при уровне логической единицы на разряде управляющей цифровой шины 21, соединенной с контактом затвора данного ключевого МОП-транзистора). Через открытые каналы ключевых МОП-транзисторов 7 - 12 истоки соответствующих МОП-транзисторов 1 - 6, определяющих синаптический вес, подключатся к линии питания 18 параллельно друг другу, в результате чего суммарная проводимость электронного синапса будет определяться выражением (2):

G= GW0S0 + GW1S1 + GW2S2 + … + GWM-1SM-1 =

= GW0S020 + GW0S121 + GW0S222 + … + GW0SM-12M-1, (2)

где S0 - SM-1 принимают значения 0 или 1 в соответствии с цифровым кодом на управляющей шине.

Сопротивления каналов ключевых МОП-транзисторов 7 - 12, соединенных последовательно с каналами МОП-транзисторов 1 - 6, будут вносить погрешность в устанавливаемые в соответствии с выражением (2) значения проводимости электронного синапса. С целью минимизации данной погрешности (и одновременно занимаемой площади, емкости и энергопотребления) ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью канала равна ширине канала i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i=0,1,…,M-1, то есть значения ширины каналов Wi ключевых МОП-транзисторов 7 - 12 связаны между собой соотношением Wi=2Wi-1, так же, как значения ширины каналов МОП-транзисторов 1 - 6. При этом суммарная проводимость ключевых МОП-транзисторов 7 - 12 пропорциональна цифровому коду S5 - S0 на управляющей цифровой шине 21, аналогично суммарной проводимости МОП-транзисторов 1 - 6.

Таким образом, интегральный электронный КМОП синапс разработан и реализован как аналоговый синаптический функциональный элемент с цифровым управлением проводимостью (с прямым преобразованием «цифровой код - уровень проводимости»), используемый для интегральной аппаратной реализации нейронных сетей.

В соответствии с временными диаграммами на фиг. 2, полученными в результате схемотехнического моделирования топологической реализации предлагаемого интегрального электронного КМОП синапса по технологии с проектной нормой 50 нм, при поступлении на входную линию 16 электронного синапса входного импульса VIN, проводимость электронного синапса G (и пропорциональный ей ток I в выходной линии 20 электронного синапса) будут определяться кодом S5-S0 на цифровой управляющей шине 21 в соответствии с выражением (2) и напряжением смещения VB на линии 19 в соответствии с выражением (1).

Положительный эффект, заключающийся в уменьшении площади, занимаемой электронным синапсом на кристалле, уменьшении входной емкости электронного синапса, снижении потребляемой мощности и уменьшении погрешности установки уровня проводимости электронного синапса, получен за счет введения перечисленных выше новых признаков, не определяется конкретной технологией реализации устройства и обеспечивает возможность и эффективность использования предложенного интегрального электронного КМОП синапса в интегральных устройствах нейроморфной электроники.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный электронный синаптический КМОП-элемент | 2024 |

|

RU2836650C1 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

| Многоканальный коммутатор | 1982 |

|

SU1078616A1 |

| Многоканальный коммутатор | 1989 |

|

SU1723667A1 |

| Многоканальный коммутатор | 1989 |

|

SU1644373A1 |

| ЕМКОСТНАЯ МОП ДИОДНАЯ ЯЧЕЙКА ФОТОПРИЕМНИКА-ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2014 |

|

RU2583955C1 |

| КМОП-ТРАНЗИСТОР С ВЕРТИКАЛЬНЫМИ КАНАЛАМИ И ОБЩИМ ЗАТВОРОМ | 2012 |

|

RU2504865C1 |

| Триггер на КМОП транзисторах | 1980 |

|

SU921052A1 |

| СПОСОБ ФОРМИРОВАНИЯ ЭЛЕКТРОПРОВОДЯЩИХ И/ИЛИ ПОЛУПРОВОДНИКОВЫХ ТРЕХМЕРНЫХ СТРУКТУР, СПОСОБ УНИЧТОЖЕНИЯ ЭТИХ СТРУКТУР И ГЕНЕРАТОР/МОДУЛЯТОР ЭЛЕКТРИЧЕСКОГО ПОЛЯ ДЛЯ ИСПОЛЬЗОВАНИЯ В СПОСОБЕ ФОРМИРОВАНИЯ | 1999 |

|

RU2210834C2 |

| Способ изготовления КМОП-структур | 2015 |

|

RU2665584C2 |

Изобретение относится к области перспективной элементной базы нейроморфной электроники. Интегральный электронный КМОП синапс, содержащий МОП-транзисторы с дырочной проводимостью каналов, определяющие синаптический вес, количество которых M=log2N, где N - число уровней проводимости интегрального электронного синапса, причем значения ширины каналов Wi МОП-транзисторов, определяющих синаптический вес, связаны между собой соотношением Wi=2Wi-1, где i - порядковый номер МОП-транзистора (i=0, 1,…, M-1); M ключевых МОП-транзисторов с дырочной проводимостью каналов. В устройство введен КМОП-инвертор на основе комплементарной пары МОП-транзисторов с электронной и дырочной проводимостью, контакты затворов которых соединены и образуют входную линию электронного синапса, а контакты стоков соединены и образуют выходную линию КМОП-инвертора. Ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью канала равна ширине канала i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i=0, 1,…, M-1, контакт истока МОП-транзистора с дырочной проводимостью КМОП-инвертора и контакты истоков всех ключевых МОП-транзисторов с дырочной проводимостью каналов соединены с линией питания. Контакт истока МОП-транзистора с электронной проводимостью КМОП-инвертора соединен с линией постоянного напряжения смещения, контакт стока i-го ключевого МОП-транзистора с дырочной проводимостью канала соединен с контактом истока i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i=0, 1,…, M-1, контакты затворов всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией КМОП-инвертора. Контакты стоков всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией электронного синапса, контакты затворов всех ключевых МОП-транзисторов с дырочной проводимостью каналов образуют M-разрядную цифровую управляющую шину электронного синапса. Изобретение обеспечивает возможность уменьшения площади, занимаемой электронным синапсом на кристалле, уменьшения входной емкости электронного синапса, снижения потребляемой мощности и уменьшения погрешности установки уровня проводимости электронного синапса. 2 ил.

Интегральный электронный КМОП синапс, содержащий МОП-транзисторы с дырочной проводимостью каналов, определяющие синаптический вес, количество которых M = log2N, где N – число уровней проводимости интегрального электронного синапса, причем значения ширины каналов Wi МОП-транзисторов, определяющих синаптический вес, связаны между собой соотношением Wi = 2Wi-1, где i – порядковый номер МОП-транзистора (i = 0, 1,…, M-1); M ключевых МОП-транзисторов с дырочной проводимостью каналов, отличающийся тем, что в него введен КМОП-инвертор на основе комплементарной пары МОП-транзисторов с электронной и дырочной проводимостью, контакты затворов которых соединены и образуют входную линию электронного синапса, а контакты стоков соединены и образуют выходную линию КМОП-инвертора, причем ширина канала i-го ключевого МОП-транзистора с дырочной проводимостью канала равна ширине канала i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i = 0, 1,…, M-1, контакт истока МОП-транзистора с дырочной проводимостью КМОП-инвертора и контакты истоков всех ключевых МОП-транзисторов с дырочной проводимостью каналов соединены с линией питания, контакт истока МОП-транзистора с электронной проводимостью КМОП-инвертора соединен с линией постоянного напряжения смещения, контакт стока i-го ключевого МОП-транзистора с дырочной проводимостью канала соединен с контактом истока i-го МОП-транзистора с дырочной проводимостью канала, определяющего синаптический вес, для всех i = 0, 1,…, M-1, контакты затворов всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией КМОП-инвертора, контакты стоков всех МОП-транзисторов с дырочной проводимостью каналов, определяющих синаптический вес, соединены с выходной линией электронного синапса, контакты затворов всех ключевых МОП-транзисторов с дырочной проводимостью каналов образуют M-разрядную цифровую управляющую шину электронного синапса.

| Asghar, M.S | |||

| et al., Low-Power Spiking Neural Network Chip Based on a Compact LIF Neuron and Binary Exponential Charge Injector Synapse Circuits | |||

| Способ регенерирования сульфо-кислот, употребленных при гидролизе жиров | 1924 |

|

SU2021A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| H | |||

| Aziza et al | |||

| An Augmented OxRAM Synapse for Spiking Neural Network (SNN) Circuits | |||

| Станок для придания концам круглых радиаторных трубок шестигранного сечения | 1924 |

|

SU2019A1 |

Авторы

Даты

2023-12-05—Публикация

2023-07-27—Подача