Устройство сбоеустойчивого разряда самосинхронного регистра хранения относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных регистровых и вычислительных устройств, систем цифровой обработки информации.

Известно устройство разряда самосинхронного регистра хранения с нулевым спейсером в составе параллельного регистра [1, рис. 11.2], содержащий два элемента И-ИЛИ-НЕ. Недостатки данного устройства - отсутствие хранения информации в спейсере (фазе гашения) и низкая сбоеустойчивость по отношению к анти-спейсерному состоянию входов в рабочей фазе.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является устройство разряда самосинхронного регистра хранения [2, рис. 8(a)], содержащее два гистерезисных триггера (Г-триггера, в зарубежной технической литературе известного как С-элемент) и индикаторный элемент 2ИЛИ-НЕ.

Недостаток прототипа - «залипание» его информационного выхода в состоянии анти-спейсера, инверсного по отношению к спейсеру, при логическом сбое, порождающем анти-спейсер на информационных входах разряда регистра, которое препятствует возврату разряда самосинхронного регистра хранения в корректное рабочее состояние по окончании логического сбоя.

Задача, решаемая заявляемым изобретением, заключается в повышении сбоеустойчивости устройства разряда самосинхронного регистра хранения за счет встраивания в Г-триггер (С-элемент) дополнительного транзистора типа «металл-окисел-полупроводник» (МОП) с каналом р- или n-типа проводимости, управляемого инверсным выходом другого Г-триггера (С-элемента) этого же разряда регистра хранения, и использования элемента «равнозначность» или «неравнозначность» в качестве индикаторного элемента разряда регистра хранения.

В дальнейшем будем называть Г-триггер С-элементом.

Решение поставленной задачи достигается тем, что в разряде самосинхронного регистра хранения, содержащем два С-элемента, индикаторный элемент, парафазный информационный вход, вход управления, парафазный информационный выход и индикаторный выход, причем первые входы первого и второго С-элемента подключены соответственно к прямому и инверсному компонентам парафазного входа, вторые входы первого и второго С-элемента соединены с входом управления, выход первого С-элемента подключен к прямому компоненту парафазного выхода и первому входу индикаторного элемента, выход второго С-элемента подключен к инверсному компоненту парафазного выхода и второму входу индикаторного элемента, выход которого соединен с индикаторным выходом разряда регистра хранения, каждый С-элемент содержит, по меньшей мере, четыре р-МОП транзистора и четыре n-МОП транзистора, два входа и один выход, причем первый вход подключен к затворам первых транзисторов р- и n-типа, второй вход подключен к затворам вторых транзисторов р- и n-типа, исток второго транзистора р-типа соединен с шиной питания, а его сток - с истоком первого транзистора р-типа, сток которого подключен к стоку первого транзистора n-типа, затворам третьих транзисторов р- и n-типа и стокам четвертых транзисторов р- и n-типа, исток второго транзистора n-типа соединен с шиной земли, а его сток - с истоком первого транзистора n-типа, истоки третьего и четвертого транзисторов р-типа подключены к шине питания, истоки третьего и четвертого транзисторов n-типа подключены к шине земли, стоки третьих транзисторов р- и n-типа соединены с выходом С-элемента и затворами четвертых транзисторов р- и n-типа, введены третий вход и инверсный выход в каждый С-элемент, причем третий вход первого С-элемента подключен к инверсному выходу второго С-элемента, третий вход второго С-элемента соединен с инверсным выходом первого С-элемента, а индикаторный элемент реализован самосинхронным двухвходовым элементом «равнозначность» или «неравнозначность».

Предлагаемое устройство сбоеустойчивого разряда самосинхронного регистра хранения обладает существенными признаками, отличающими его от прототипа и находящимися в причинно-следственной связи с достигаемым техническим результатом. Действительно, использование трехвходовых Г-триггеров в составе разряда регистра хранения известно, например, в [3, Fig. 3], где третьи входы обоих С-элементов подключены к поразрядному индикаторному выходу предшествующей самосинхронной схемы. Но это не обеспечивает иммунности разряда регистра хранения к состоянию анти-спейсера входных сигналов. Именно подключение третьего входа каждого С-элемента к инверсному выходу другого С-элемента этого же разряда регистра хранения позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны из уровня техники, устройство может считаться имеющим существенные отличия.

Понятие "парафазный", используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя составляющими - парой переменных {X, ХВ}, которые в активной фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние - спейсерное (нерабочее состояние или состояние гашения). Если в качестве спейсерного используется состояние {1,1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0,0}, то - парафазный сигнал с нулевым спейсером. Спейсерное состояние - статическое состояние, переключение в которое в самосинхронной схемотехнике должно фиксироваться индикатором окончания переходного процесса, в данном случае - окончания переключения в спейсерное состояние.

Второй способ предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние: {1,1} или {0,0}, - называемое транзитным состоянием.

В материалах данной заявки речь идет об устройстве разряда самосинхронного регистра хранения, информационные вход и выход которого являются парафазным сигналом с любым типом спейсера, в дальнейшем - просто парафазным сигналом. Таким образом, отличительная особенность заявляемого устройства состоит в возможности реализации с его помощью обоих выше указанных типов спейсера парафазного сигнала.

На Фиг. 1 представлена схема устройства сбоеустойчивого разряда регистра хранения, содержащая два С-элемента 1-2, индикаторный элемент 3, прямой 4 и инверсный 5 компоненты информационного парафазного входа, вход управления 6, прямой 7 и инверсный 8 компоненты информационного парафазного выхода и индикаторный выход 9, прямой 4 и инверсный 5 компоненты информационного парафазного входа подключены к первым входам первого 1 и второго 2 С-элементов соответственно, вход управления 6 подключен ко вторым входам первого 1 и второго 2 С-элементов, третий вход первого С-элемента 1 подключен к инверсному выходу второго С-элемента 2, третий вход второго С-элемента 2 соединен с инверсным выходом первого С-элемента 1, прямой выход первого С-элемента 1 подключен к прямому компоненту 7 парафазного информационного выхода и первому входу индикаторного элемента 3, прямой выход второго С-элемента 2 соединен с инверсным компонентом 8 парафазного информационного выхода и вторым входом индикаторного элемента 3, выход индикаторного элемента 3 подключен к индикаторному выходу 9 триггера.

Для обеспечения самосинхронности устройства разряда регистра хранения его индикаторный элемент должен быть монотонным, т.е. не содержать внутренних инверторов. Монотонный элемент "равнозначность" реализуется, например, схемой [4, рис. 3.11(a)].

Сбоеустойчивый С-элемент с тремя входами и двумя выходами, использованный в устройстве сбоеустойчивого разряда регистра хранения, может строиться на основе полустатического [5, Fig. 1(c)] или статического [5, Fig. 1(a)] варианта исполнения стандартного С-элемента. В оба варианта добавляется дополнительный МОП транзистор, тип канала и способ включения которого зависят от типа спейсера информационного входа разряда регистра хранения.

Сбоеустойчивость полустатического С-элемента в составе устройства сбоеустойчивого разряда регистра хранения с нулевым спейсером информационных парафазных входа и выхода достигается тем, что в стандартный полустатический С-элемент, содержащий, по меньшей мере, четыре р-МОП транзистора и четыре n-МОП транзистора, два входа, один выход, шину питания и шину земли, причем первый вход подключен к затворам первых транзисторов р- и n-типа, второй вход подключен к затворам вторых транзисторов р- и n-типа, исток второго транзистора р-типа соединен с шиной питания, а его сток - с истоком первого транзистора р-типа, сток которого подключен к стоку первого транзистора n-типа, затворам третьих транзисторов р- и n-типа и стокам четвертых транзисторов р- и n-типа, исток второго транзистора n-типа соединен с шиной земли, а его сток - с истоком первого транзистора n-типа, истоки третьего и четвертого транзисторов р-типа подключены к шине питания, истоки третьего и четвертого транзисторов n-типа подключены к шине земли, стоки третьих транзисторов р- и n-типа соединены с выходом С-элемента и затворами четвертых транзисторов р- и n-типа, введены третий вход, второй (инверсный) выход и пятый транзистор р-типа, затвор которого подключен к третьему входу, исток - к шине питания, а сток - к истоку первого транзистора р-типа, инверсный выход соединен с затворами третьих транзисторов р- и n-типа.

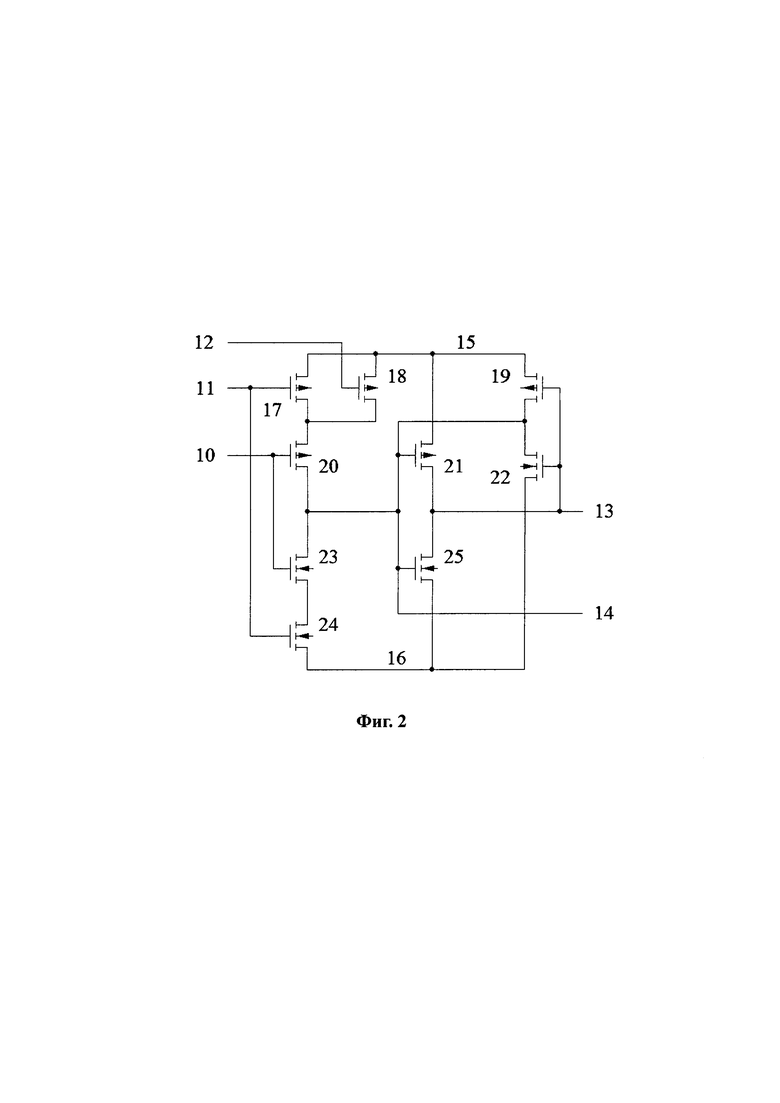

На Фиг. 2 представлена схема полустатического С-элемента в составе устройства сбоеустойчивого разряда регистра хранения с нулевым спейсером информационных парафазных входа и выхода, содержащая три входа 10-12, прямой 13 и инверсный 14 выходы, шину питания 15, шину земли 16, пять р-МОП транзисторов 17-21 и четыре n-МОП транзистора 22-25, первый вход 10 подключен к затворам транзисторов 20 и 23, второй вход 11 подключен к затворам транзисторов 17 и 24, исток транзистора 17 соединен с шиной питания, а его сток - с истоком транзистора 20, сток которого подключен к стоку транзистора 23, затворам транзисторов 21 и 25 и стокам транзисторов 19 и 22, исток транзистора 24 соединен с шиной земли, а его сток - с истоком транзистора 23, истоки транзисторов 19 и 21 подключены к шине питания, истоки транзисторов 22 и 25 подключены к шине земли, стоки транзисторов 21 и 25 соединены с прямым выходом 13 и затворами транзисторов 19 и 22, затвор транзистора 18 подключен к третьему входу 12, его исток - к шине питания, а сток - к истоку транзистора 20, инверсный выход 14 соединен с затворами транзисторов 21 и 25.

С-элемент на Фиг. 2 является полустатическим, так как успешно работает только при определенном соотношении между размерами транзисторов 19 и 22 "слабого" инвертора и транзисторов остальной части С-элемента. Однако представленный на Фиг. 2 принцип сбоеустойчивой модификации С-элемента за счет добавления МОП-транзистора р-типа может быть использован и в статическом С-элементе.

В этом случае решение задачи повышения сбоеустойчивости устройства разряда самосинхронного регистра хранения с нулевым спейсером достигается тем, что в статический С-элемент, используемый в устройстве сбоеустойчивого разряда регистра и содержащий шесть р-МОП транзисторов и шесть n-МОП транзисторов, два входа с нулевым спейсером, один выход, шину питания и шину земли, причем первый вход подключен к затворам вторых и четвертых транзисторов р- и n-типа, второй вход подключен к затворам первых и третьих транзисторов р- и n-типа, исток первого транзистора р-типа соединен с шиной питания, а его сток - с истоком второго транзистора р-типа, сток которого подключен к стоку второго транзистора n-типа, затворам шестых транзисторов р- и n-типа и стокам пятых транзисторов р- и n-типа, исток первого транзистора n-типа соединен с шиной земли, а его сток - с истоком второго транзистора n-типа, истоки третьего и четвертого транзисторов р-типа подключены к шине питания, а их стоки соединены с истоком пятого транзистора р-типа, исток шестого транзистора р-типа соединен с шиной питания, а его сток подключен к стоку шестого транзистора n-типа, выходу С-элемента и затворам пятых транзисторов р- и n-типа, истоки третьего и четвертого транзисторов n-типа подключены к шине земли, а их стоки соединены с истоком пятого транзистора n-типа, исток шестого транзистора n-типа соединен с шиной земли, введены третий вход, второй (инверсный) выход и седьмой транзистор р-типа, затвор которого подключен к третьему входу, исток - к шине питания, а сток - к стоку первого транзистора р-типа, инверсный выход соединен с затворами шестых транзисторов р- и n-типа.

В составе устройства сбоеустойчивого разряда самосинхронного регистра хранения статический С-элемент подключается идентично полустатическому С-элементу в соответствии со схемой на Фиг. 1.

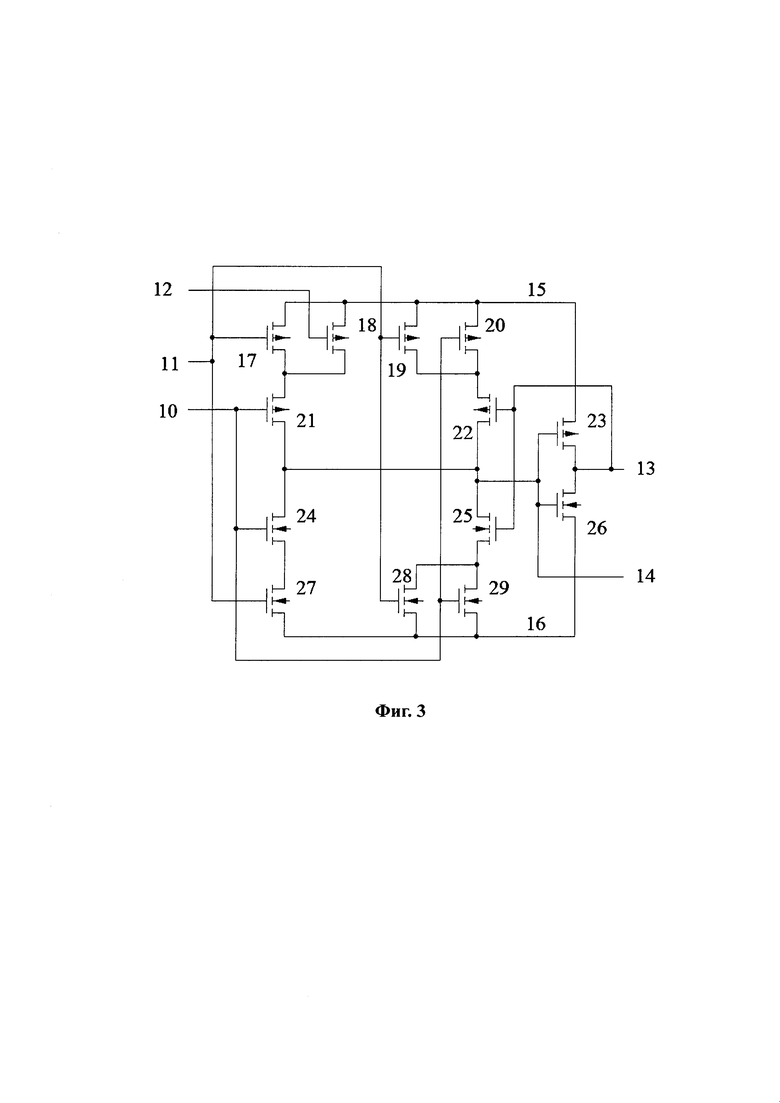

На Фиг. 3 представлена схема сбоеустойчивого статического С-элемента, используемая в составе устройства сбоеустойчивого разряда самосинхронного регистра хранения с нулевым спейсером и содержащая три входа 10-12, прямой 13 и инверсный 14 выходы, шину питания 15, шину земли 16, семь р-МОП транзисторов 17-23 и шесть n-МОП транзисторов 24-29, первый вход 10 подключен к затворам транзисторов 20, 21, 24 и 29, второй вход 11 подключен к затворам транзисторов 17, 19, 27 и 28, истоки транзисторов 17-20 и 23 соединены с шиной питания 15, стоки транзисторов 17 и 18 соединены с истоком транзистора 21, сток которого подключен к стоку транзистора 24, затворам транзисторов 23 и 26 и стокам транзисторов 22 и 25, истоки транзисторов 26-29 соединены с шиной земли 16, сток транзистора 27 соединен с истоком транзистора 24, исток транзистора 22 подключен к стокам транзисторов 19 и 20, исток транзистора 25 подключен к стокам транзисторов 28 и 29, стоки транзисторов 23 и 26 соединены с прямым выходом 13 и затворами транзисторов 22 и 25, затвор транзистора 18 подключен к третьему входу 12, инверсный выход 14 соединен с затворами транзисторов 23 и 26.

Схема устройства сбоеустойчивого разряда самосинхронного регистра хранения на Фиг. 1 с парафазным информационным входом с нулевым спейсером работает следующим образом. Будем обозначать входы и выходы схемы буквами I и О соответственно и индексом, совпадающим с их нумерацией на Фиг. 1. Пусть схема находится в одном из рабочих состояний, например, I4=0, I5=1, и вход управления I6 высоким уровнем разрешает запись в разряд регистра хранения рабочего состояния (I6=1). При появлении на входе разряда кратковременного анти-спейсера I4=I5=1 из-за логического сбоя в предшествующей комбинационной части, на выходах разряда регистра хранения тоже появится анти-спейсер O7=O8=1, а на инверсных выходах С-элементов 1 и 2 появится уровень логического нуля, который откроет р-транзисторы 18 в обоих сбоеустойчивых С-элементах разряда регистра хранения. Это еще не приведет к каким-либо переключениям С-элементов 1 и 2, так как транзистор 20 в полустатическом С-элементе (Фиг. 2) и транзистор 21 в статическом С-элементе (Фиг. 3) закрыты. Индикаторный элемент "равнозначность" 3 проиндицирует анти-спейсер на выходе разряда регистра хранения как спейсер (O9=1), запретит источнику информационного входа регистра переключать информационный вход в спейсер I4=I5=0, и запретит источнику сигнала управления переключать его в спейсер I6=0. По окончании логического сбоя информационный вход разряда регистра хранения вернется в исходное рабочее состояние I4=0, I5=1, транзистор 20 (Фиг. 2) в полустатическом С-элементе 1 (или транзистор 21 в статическом С-элементе 1 (Фиг. 3)) откроется, транзистор 23 (Фиг. 2) в полустатическом С-элементе 1 (или транзистор 24 в статическом С-элементе 1 (Фиг. 3)) закроется и инверсный выход С-элемента 1 перейдет в высокий уровень (логическую единицу), поскольку в полустатическом С-элементе размеры КМОП транзисторов 19 и 22 на Фиг. 2 выбираются достаточно маленькими, чтобы не мешать переключению инвертора на транзисторах 21 и 25 в инверсное состояние. (Инвертор на транзисторах 19 и 22 является "слабым". Он нужен для поддержки уровня напряжения на входе "сильного" инвертора на транзисторах 21 и 25, когда входы разряда регистра хранения не обеспечивают прямое подключение затворов транзисторов 21 и 25 к шине питания или земли.)

В результате парафазный информационный выход разряда регистра хранения переключится в рабочее состояние О7=0, O8=1 и индикаторный элемент 3 подтвердит низким уровнем своего выхода 9 переключение разряда регистра хранения в рабочее состояние. Таким образом, логический сбой оказывается замаскированным и не приводит к критической ошибке в работе схемы.

Особенности данной схемы по сравнению с прототипом следующие.

С-элементы, составляющие основу устройства сбоеустойчивого разряда регистра хранения с нулевым спейсером, имеют третий вход и второй (инверсный) выход, причем третий вход одного статического или полустатического С-элемента подключен к инверсному выходу другого С-элемента разряда регистра, а сам С-элемент имеет дополнительный р-МОП транзистор, затвор которого подключен к третьему входу С-элемента. Использование элемента «равнозначность» в качестве формирователя индикаторного выхода разряда регистра хранения, обеспечивает восприятие запрещенного анти-спейсерного состояния входного парафазного сигнала, возникшего из-за логического сбоя, как спейсерного, предотвращая хранение и передачу его как некорректного рабочего состояния. Дополнительный р-МОП транзистор в схеме С-элемента обеспечивает самостоятельное переключение устройства сбоеустойчивого разряда регистра хранения из анти-спейсера в корректное рабочее состояние после окончания логического сбоя.

Логический элемент «неравнозначность» в качестве индикаторного элемента устройства сбоеустойчивого разряда самосинхронного регистра хранения работает аналогично элементу «равнозначность», но с инверсными значениями выхода, соответствующими рабочей и спейсерной фазе устройства сбоеустойчивого разряда регистра хранения.

Таким образом, предлагаемое устройство обеспечивает повышение сбоеустойчивости устройства разряда самосинхронного регистра хранения с нулевым спейсером за счет индикации его состояния, противоположного спейсеру, как спейсерного и самостоятельного переключения разряда регистра из этого сбойного состояния в корректное рабочее состояние после окончания логического сбоя. Цель изобретения достигнута.

Аналогичный прием повышения сбоеустойчивости может быть использован в устройстве разряда регистра хранения с единичным спейсером информационного входа. В этом случае устройство разряда регистра хранения также реализуется схемой на Фиг. 1, а схемы сбоеустойчивых С-элементов претерпевают изменения, направленные на самолечение нулевого анти-спейсера на информационном выходе разряда регистра.

Сбоеустойчивость полустатического С-элемента в составе устройства сбоеустойчивого разряда самосинхронного регистра хранения с единичным спейсером информационных парафазных входа и выхода достигается тем, что в стандартный полустатический С-элемент, содержащий четыре р-МОП транзистора и четыре n-МОП транзистора, два входа и один выход с единичным спейсером, шину питания и шину земли, причем первый вход подключен к затворам первых транзисторов р- и n-типа, второй вход подключен к затворам вторых транзисторов р- и n-типа, исток второго транзистора р-типа соединен с шиной питания, а его сток - с истоком первого транзистора р-типа, сток которого подключен к стоку первого транзистора n-типа, затворам третьих транзисторов р- и n-типа и стокам четвертых транзисторов р- и n-типа, исток второго транзистора n-типа соединен с шиной земли, а его сток - с истоком первого транзистора n-типа, истоки третьего и четвертого транзисторов р-типа подключены к шине питания, истоки третьего и четвертого транзисторов n-типа подключены к шине земли, стоки третьих транзисторов р- и n-типа соединены с выходом С-элемента и затворами четвертых транзисторов р- и n-типа, введены третий вход, второй (инверсный) выход и пятый транзистор n-типа, затвор которого подключен к третьему входу, исток - к шине земли, а сток - к истоку первого транзистора n-типа, инверсный выход соединен с затворами третьих транзисторов р- и n-типа.

На Фиг. 4 представлена схема полустатического С-элемента в составе устройства сбоеустойчивого разряда самосинхронного регистра хранения с единичным спейсером информационных парафазных входа и выхода, содержащая три входа 10-12, прямой 13 и инверсный 14 выходы, шину питания 15, шину земли 16, четыре р-МОП транзистора 17, 19-21 и пять n-МОП транзисторов 18, 22-25, первый вход 10 подключен к затворам транзисторов 20 и 23, второй вход 11 подключен к затворам транзисторов 17 и 24, исток транзистора 17 соединен с шиной питания, а его сток - с истоком транзистора 20, сток которого подключен к стоку транзистора 23, затворам транзисторов 21 и 25 и стокам транзисторов 19 и 22, исток транзистора 24 соединен с шиной земли, а его сток - с истоком транзистора 23, истоки транзисторов 19 и 21 подключены к шине питания, истоки транзисторов 22 и 25 подключены к шине земли, стоки транзисторов 21 и 25 соединены с прямым выходом 13 и затворами транзисторов 19 и 22, затвор транзистора 18 подключен к третьему входу 12, его исток - к шине земли, а сток - к истоку транзистора 23, инверсный выход 14 соединен с затворами транзисторов 21 и 25.

С-элемент на Фиг. 4 является полустатическим, так как успешно работает только при определенном соотношении между размерами транзисторов 19 и 22 "слабого" инвертора и размерами транзисторов остальной части С-элемента. Однако представленный на Фиг. 4 принцип модификации С-элемента за счет добавления МОП-транзистора n-типа может быть использован и в статическом С-элементе для повышения сбоеустойчивости разряда регистра хранения с единичным спейсером.

В этом случае решение задачи повышения сбоеустойчивости устройства разряда самосинхронного регистра хранения с единичным спейсером достигается тем, что в статический С-элемент, используемый в устройстве разряда регистра и содержащий шесть р-МОП транзисторов и шесть n-МОП транзисторов, два входа и один выход с единичным спейсером, шину питания и шину земли, причем первый вход подключен к затворам вторых и четвертых транзисторов р- и n-типа, второй вход подключен к затворам первых и третьих транзисторов р- и n-типа, исток первого транзистора р-типа соединен с шиной питания, а его сток - с истоком второго транзистора р-типа, сток которого подключен к стоку второго транзистора n-типа, затворам шестых транзисторов р- и n-типа и стокам пятых транзисторов р- и n-типа, исток первого транзистора n-типа соединен с шиной земли, а его сток - с истоком второго транзистора n-типа, истоки третьего и четвертого транзисторов р-типа подключены к шине питания, а их стоки соединены с истоком пятого транзистора р-типа, исток шестого транзистора р-типа соединен с шиной питания, а его сток подключен к стоку шестого транзистора n-типа, выходу С-элемента и затворам пятых транзисторов р- и n-типа, истоки третьего и четвертого транзисторов n-типа подключены к шине земли, а их стоки соединены с истоком пятого транзистора n-типа, исток шестого транзистора n-типа соединен с шиной земли, введены третий вход, второй (инверсный) выход и седьмой транзистор n-типа, затвор которого подключен к третьему входу, исток - к шине земли, а сток - к стоку первого транзистора n-типа, инверсный выход соединен с затворами шестых транзисторов р- и n-типа.

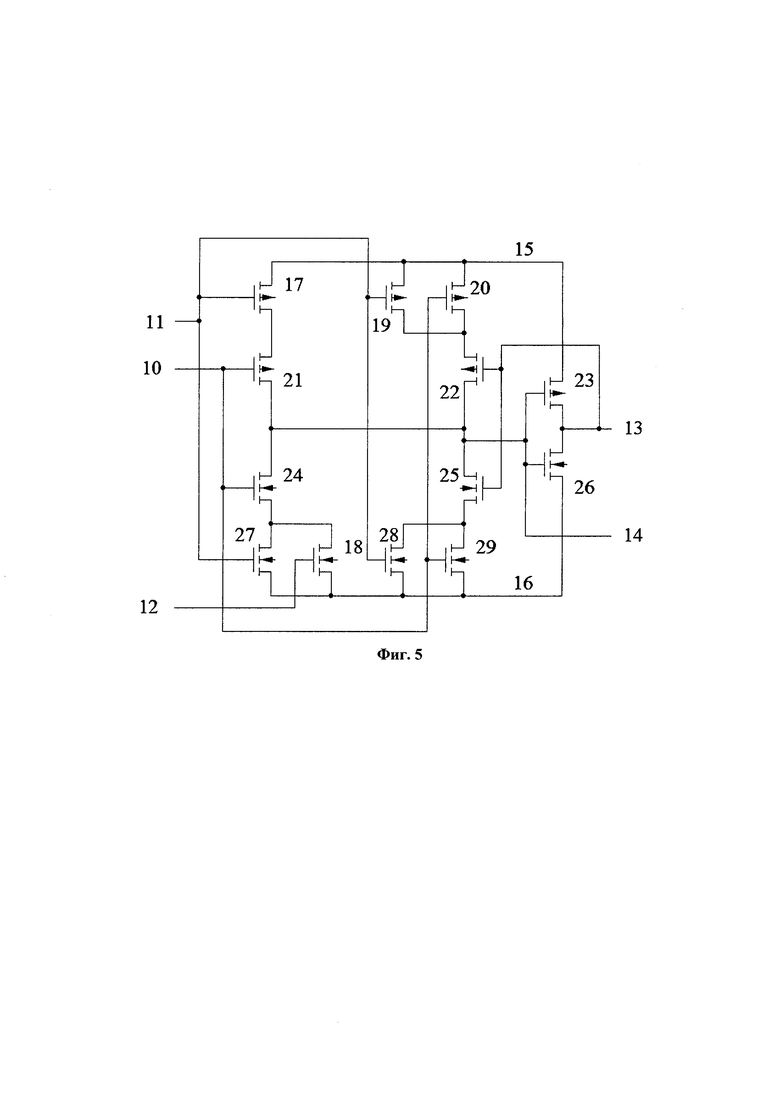

На Фиг. 5 представлена схема сбоеустойчивого статического С-элемента, используемая в составе сбоеустойчивого устройства разряда самосинхронного регистра хранения с единичным спейсером информационных парафазных входа и выхода и содержащая три входа 10-12, прямой 13 и инверсный 14 выходы, шину питания 15, шину земли 16, шесть р-МОП транзисторов 17, 19-23 и семь n-МОП транзисторов 18, 24-29, первый вход 10 подключен к затворам транзисторов 20, 21, 24 и 29, второй вход 11 подключен к затворам транзисторов 17, 19, 27 и 28, истоки транзисторов 17, 19-20 и 23 соединены с шиной питания 15, сток транзистора 17 соединен с истоком транзистора 21, сток которого подключен к стоку транзистора 24, затворам транзисторов 23 и 26 и стокам транзисторов 22 и 25, истоки транзисторов 18, 26-29 соединены с шиной земли 16, стоки транзисторов 18 и 27 соединены с истоком транзистора 24, исток транзистора 22 подключен к стокам транзисторов 19 и 20, исток транзистора 25 подключен к стокам транзисторов 28 и 29, стоки транзисторов 23 и 26 соединены с прямым выходом 13 и затворами транзисторов 22 и 25, затвор транзистора 18 подключен к третьему входу 12, инверсный выход 14 соединен с затворами транзисторов 23 и 26.

Схема устройства сбоеустойчивого разряда самосинхронного регистра хранения на Фиг. 1 с парафазным информационным входом с единичным спейсером работает следующим образом. Пусть схема находится в одном из рабочих состояний, например, I4=0, I5=1, и вход управления I6 низким уровнем разрешает запись в разряд регистра хранения рабочего состояния (I6=0). При появлении на входе разряда кратковременного анти-спейсера I4=I5=0 из-за логического сбоя в предшествующей комбинационной части, на выходах разряда регистра тоже появится анти-спейсер O7=O8=0, а на инверсных выходах С-элементов 1 и 2 появится уровень логической единицы, который откроет n-транзисторы 18 в обоих сбоеустойчивых С-элементах разряда регистра хранения. Это еще не приведет к каким-либо переключениям С-элементов 1 и 2, так как транзистор 23 в полустатическом С-элементе (Фиг. 4) и транзистор 24 в статическом С-элементе (Фиг. 5) закрыты. Индикаторный элемент "равнозначность" 3 проиндицирует анти-спейсер на выходе разряда регистра хранения как спейсер (O9=1), запретит источнику информационного входа регистра переключать информационный вход в единичный спейсер I4=I5=1, и запретит источнику сигнала управления переключать его в спейсер I6=1. По окончании логического сбоя информационный вход разряда регистра хранения вернется в исходное рабочее состояние I4=0, I5=1, транзистор 23 в полустатическом С-элементе 2 (Фиг. 2) (или транзистор 24 в статическом С-элементе 2 (Фиг. 3)) откроется, транзистор 20 в полустатическом С-элементе 2 (или транзистор 21 в статическом С-элементе 2 (Фиг. 3)) закроется и инверсный выход С-элемента 2 перейдет в низкий уровень (логический ноль), поскольку в полустатическом С-элементе размеры КМОП транзисторов 19 и 22 на Фиг. 4 выбираются достаточно маленькими, чтобы не мешать переключению инвертора на транзисторах 21 и 25 в инверсное состояние.

В результате информационный выход устройства сбоеустойчивого разряда регистра хранения переключится в рабочее состояние О7=0, O8=1 и индикаторный элемент 3 подтвердит низким уровнем своего выхода 9 переключение разряда регистра хранения в рабочее состояние. Таким образом, логический сбой оказывается замаскированным и не приводит к критической ошибке в работе схемы.

Отличительные особенности данной схемы по сравнению с прототипом состоят в следующих конструктивных особенностях.

С-элементы, составляющие основу устройства сбоеустойчивого разряда регистра хранения, имеют третий вход и инверсный выход, третий вход одного С-элемента подключен к инверсному выходу другого С-элемента этого же разряда регистра. Использование элемента «равнозначность» или «неравнозначность» в качестве формирователя индикаторного выхода разряда регистра обеспечивает восприятие запрещенного «анти-спейсерного» состояния входного парафазного сигнала как спейсерного, предотвращая хранение и передачу его как некорректного рабочего состояния. По окончании логического сбоя и возврата входного парафазного сигнала в корректное рабочее состояние разряд регистра за счет введенных перекрестных связей между С-элементами переключается из «анти-спейсера» в рабочее состояние, соответствующее рабочему состоянию информационного входа.

Таким образом, предлагаемое устройство обеспечивает повышение сбоеустойчивости разряда самосинхронного регистра хранения с нулевым или единичным спейсером за счет индикации его состояния, противоположного спейсеру, как спейсерного и самостоятельного переключения разряда регистра из этого сбойного состояния в корректное рабочее состояние после окончания логического сбоя. Цель изобретения достигнута.

Источники:

[1] Варшавский В.И., Кишиневский М.А., Мараховский В.Б. и др. Автоматное управление асинхронными процессами в ЭВМ и дискретных системах / Под ред. В.И.Варшавского. - М.: Наука. Гл. ред. физ.-мат.лит., 1986. - 400 с.

[2] Степченков Ю.А., Дьяченко Ю.Г., Рождественский Ю.В., Морозов Н.В., Степченков Д.Ю., Рождественскене А.В., Сурков А.В. 2014. Самосинхронный умножитель с накоплением: варианты реализации. / «Системы и средства информатики», вып. 24, №3. - М,: изд-во «Торус Пресс», С. 63-77.

[3] Stepchenkov Y.A., Zakharov V.N., Rogdestvenski Y.V., Diachenko Y.G., Morozov N.V., Stepchenkov D.Y. Speed-Independent Floating Point Coprocessor / IEEE Eeast-West Design and Test Symposium, Batumi, Georgia, September 26-29, 2015. P. 111-114.

[4] Кармазинский A.H. Синтез принципиальных схем цифровых элементов на МДП-транзисторах. - М.: Радио и связь, 1983, 256 с.

[5] I.A. Danilov, М.S. Gorbunov, A.I. Shnaider, А.О. Balbekov, Y.В. Rogatkin, and S.G. Bobkov, "DICE-based Muller C-elements for Soft Error Tolerant Asynchronous ICs," in 2016 16th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Sept 2016, pp. 1-4. DOI: 10.1109/RADECS.2016.8093145.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2019 |

|

RU2725778C1 |

| Г-ТРИГГЕР | 2007 |

|

RU2371842C2 |

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 2016 |

|

RU2618192C1 |

| Способ сравнения данных в ячейке ассоциативного запоминающего устройства и модуль сравнения данных в ячейке ассоциативного запоминающего устройства | 2018 |

|

RU2680870C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2601145C1 |

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2808236C1 |

| Самосинхронный одноразрядный троичный сумматор с нулевым спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2810631C1 |

Изобретение относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных регистровых и вычислительных устройств, систем цифровой обработки информации. Технический результат - повышение сбоеустойчивости устройства разряда самосинхронного регистра хранения с нулевым или единичным спейсером. Устройство построено на основе С-элементов за счет встраивания в С-элемент дополнительного р-МОП или n-МОП транзистора, управляемого инверсным выходом другого С-элемента этого же разряда регистра, и использования элемента «равнозначность» или «неравнозначность» в качестве индикаторного элемента разряда регистра хранения, при этом в схеме устройства разряда самосинхронного регистра хранения, содержащей индикаторный элемент 2ИЛИ-НЕ или 2И-НЕ, парафазный информационный вход, вход управления, парафазный информационный выход и индикаторный выход, используются трехвходовые С-элементы, имеющие два выхода, третий вход одного С-элемента соединен со вторым выходом другого С-элемента и наоборот. 4 з.п. ф-лы, 5 ил.

1. Устройство сбоеустойчивого разряда самосинхронного регистра хранения, содержащее два С-элемента, индикаторный элемент, парафазный информационный вход, вход управления, парафазный информационный выход и индикаторный выход, причем первые входы первого и второго С-элемента подключены соответственно к прямому и инверсному компонентам парафазного входа, вторые входы первого и второго С-элемента соединены с входом управления, выход первого С-элемента подключен к прямому компоненту парафазного выхода и первому входу индикаторного элемента, выход второго С-элемента подключен к инверсному компоненту парафазного выхода и второму входу индикаторного элемента, выход которого соединен с индикаторным выходом разряда регистра хранения, каждый С-элемент содержит, по меньшей мере, четыре р-МОП транзистора и четыре n-МОП транзистора, два входа и один выход, причем первый вход подключен к затворам первых транзисторов р- и n-типа, второй вход подключен к затворам вторых транзисторов р- и n-типа, исток второго транзистора р-типа соединен с шиной питания, а его сток - с истоком первого транзистора р-типа, сток которого подключен к стоку первого транзистора n-типа, затворам третьих транзисторов р- и n-типа и стокам четвертых транзисторов р- и n-типа, исток второго транзистора n-типа соединен с шиной земли, а его сток - с истоком первого транзистора n-типа, истоки третьего и четвертого транзисторов р-типа подключены к шине питания, истоки третьего и четвертого транзисторов n-типа подключены к шине земли, стоки третьих транзисторов р- и n-типа соединены с выходом С-элемента и затворами четвертых транзисторов р- и n-типа, отличающееся тем, что в схему введены третий вход и инверсный выход в каждый С-элемент, причем третий вход первого С-элемента подключен к инверсному выходу второго С-элемента, третий вход второго С-элемента соединен с инверсным выходом первого С-элемента, а индикаторный элемент реализован самосинхронным двухвходовым элементом «равнозначность» или «неравнозначность».

2. Устройство сбоеустойчивого разряда самосинхронного регистра хранения по п. 1, отличающееся тем, что в схему каждого С-элемента введен пятый транзистор р-типа, затвор которого подключен к третьему входу, исток - к шине питания, а сток - к стоку второго транзистора р-типа, второй выход соединен с затворами третьих транзисторов р- и n-типа.

3. Устройство сбоеустойчивого разряда самосинхронного регистра хранения по п. 2, отличающееся тем, что в схему каждого С-элемента введены шестой и седьмой р-МОП транзисторы и пятый и шестой n-МОП транзисторы, причем затворы шестого транзистора р-типа и пятого транзистора n-типа подключены к первому входу разряда регистра хранения, затворы седьмого транзистора р-типа и шестого транзистора n-типа подключены ко второму входу разряда регистра, исток четвертого транзистора р-типа подключен не к шине питания, а к стокам шестого и седьмого транзисторов р-типа, истоки которых соединены с шиной питания, исток четвертого транзистора n-типа подключен не к шине земли, а к стокам пятого и шестого транзисторов n-типа, истоки которых соединены с шиной земли.

4. Устройство сбоеустойчивого разряда самосинхронного регистра хранения по п. 1, отличающееся тем, что в схему каждого С-элемента введен пятый транзистор n-типа, затвор которого подключен к третьему входу, исток - к шине земли, а сток - к стоку второго транзистора n-типа, второй выход соединен с затворами третьих транзисторов р- и n-типа.

5. Устройство сбоеустойчивого разряда самосинхронного регистра хранения по п. 4, отличающееся тем, что в схему каждого С-элемента введены пятый и шестой р-МОП транзисторы и шестой и седьмой n-МОП транзисторы, причем затворы пятого транзистора р-типа и шестого транзистора n-типа подключены к первому входу разряда регистра хранения, затворы шестого транзистора р-типа и седьмого транзистора n-типа подключены ко второму входу разряда регистра, исток четвертого транзистора р-типа подключен не к шине питания, а к стокам пятого и шестого транзисторов р-типа, истоки которых соединены с шиной питания, исток четвертого транзистора n-типа подключен не к шине земли, а к стокам шестого и седьмого транзисторов n-типа, истоки которых соединены с шиной земли.

| Асинхронный логический элемент комплементарной металл-оксид-полупроводниковой структуры | 2018 |

|

RU2693685C1 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2015 |

|

RU2616874C2 |

| САМОСИНХРОННЫЙ ТРИГГЕР С ОДНОФАЗНЫМ ИНФОРМАЦИОННЫМ ВХОДОМ | 2008 |

|

RU2405246C2 |

| Токарный резец | 1924 |

|

SU2016A1 |

| US 7554374 B2, 10.03.2016 | |||

| US 6281707B1, 28.08.2001 | |||

| US 6859071 B2, 22.02.2005. | |||

Авторы

Даты

2020-10-01—Публикация

2020-03-06—Подача